держит последовательно соединенные счетчик импульсов, преобразователь код-аналог и компаратор, вход счетчика соединен с импульсным входом блока запоминания амплитуды тока нагрузки, аналоговый выход которого соединен с выходом преобразователя код-аналог, логический выход - с вьг155063

ходом компаратора, а другой вход - с вторым входом компаратора.

4. Устройство по п. 1, о т л и.чающееся тем, что отсчетный блок содержит последовательно соединенные счетчик импульсов и цифровой индикатор, вход счетчика импульсов подключен к входу отсчетного блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения полного сопротивления цепи фаза-нуль | 1979 |

|

SU797354A1 |

| Регулируемый тиристорный преобразователь переменного напряжения (его варианты) | 1984 |

|

SU1251255A1 |

| Способ управления электрогидравлической системой и устройство для его осуществления | 1989 |

|

SU1779806A1 |

| Импульсный регулятор мощности | 1983 |

|

SU1111143A1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ЭЛЕКТРИЧЕСКОЙ МОЩНОСТИ ПЕРЕМЕННОГО ТОКА | 1993 |

|

RU2042177C1 |

| УСТРОЙСТВО ДЛЯ РЕГУЛИРОВАНИЯ ТЕМПЕРАТУРЫ | 1992 |

|

RU2032209C1 |

| ФАЗОСДВИГАЮЩЕЕ УСТРОЙСТВО | 2005 |

|

RU2288532C1 |

| МНОГОФАЗНЫЙ СЧЕТЧИК ЭЛЕКТРИЧЕСКОЙ ЭНЕРГИИ | 1994 |

|

RU2099718C1 |

| Устройство для автоматического переключения однофазных нагрузок в низковольтных распределительных сетях | 1981 |

|

SU1026234A1 |

| Дискретно-аналоговый индикатор | 1987 |

|

SU1529129A1 |

1. УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ПОЛНОГО СОПРОТИВЛЕНИЯ ЦЕПИ ФАЗА-НУЛЬ, содержащее последовательно соединенные нагрузочный резистор и тиристор, свободные выводы которых подключены соответственно к зажимам Нуль и Фаза, блок однократного отпирания тиристора, синхронизирующий вход которого подключен к тем же зажимам, а импульсный выход - к управляющему электроду тиристора, блок запоминания амплитуды тока нагрузки, один из входов которого подключен к выводам нагрузочного резистора, датчик времени нарастания тока нагрузки, блок деления, отсчетньш блок, датчик напряжения ненагруженной сети, вход ; которого подключен к зажимам Фаза и Нуль, выход - к первому входу блока деления, аналоговый выход блока запоминания амплитуды тока нагрузки соединен с вторым входом блока деления,отличающееся тем, что, с целью повьпиения точности - и упрощения настройки устройства. в него введены генератор импульсов стабильной частоты, блок распределения импульсов, счетчик импульсов и блок совпадения, причем выход генератора импульсов стабильной частоты соединен с импульсным входом блока распределения импульсов, первый, второй и третий выходы которого соединены соответственно с импульсными входами счетчика импульсов, блока деления и отсчетного блока, четвертый выход соединен с входами блока запоминания амплитуды тока нагрузки и датчика времени нарастания тока нагрузки, выход счетчика i импульсов через блок совпадения соединен с jiepBbiM логическим входом W блока распределения импульсов, второй, третий и четвертый логические входы которого соединены соответственно с выходами блока деления, блока запоминания амплитуды тока нагрузки и датчика времени нарастания тока нагрузки. СП 2.Устройство по п. 1, о т Л иел чающееся тем, что блок деления содержит последовательно соединенные счетчик импульсов, преобрасо зователь код-аналог, компаратор, вход счетчика импульсов соединен с импульсным входом блока деления, первый вход которого соединен с другим входом компаратора второй вход - с вторым входе преобразователя коданалог, а логический выход соединен с выходом компаратора. 3.Устройство по п. 1, о т л ичающееся тем, что блок запоминания амплитуды тока нагрузки со

V, .

Изобретение относится к области электрических измерений, в частности к определению полного сопротивления цепи фаза-нуль (точнее, модуля комплексного сопротивления) под рабочим напряжением сети, может быть применейо преимущественно в сетях 380/ 220 В с глухозаземленной нейтралью.

Целью изобретения является повышение точности и упрощение настройки устройства.

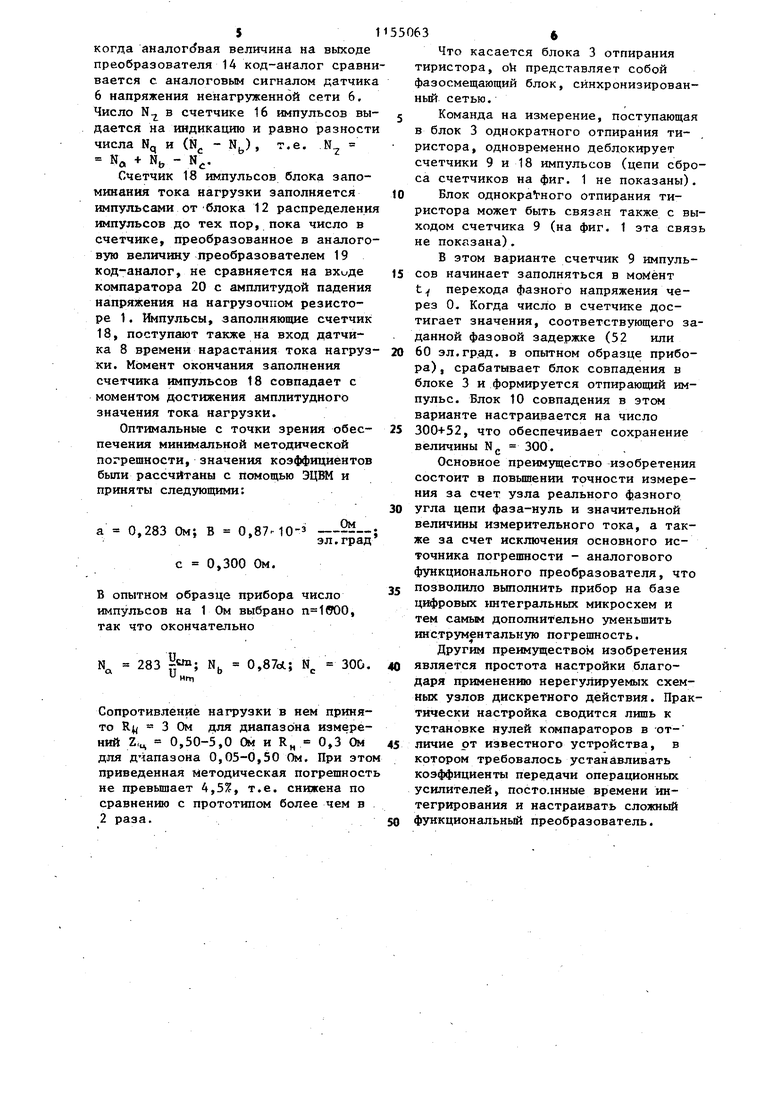

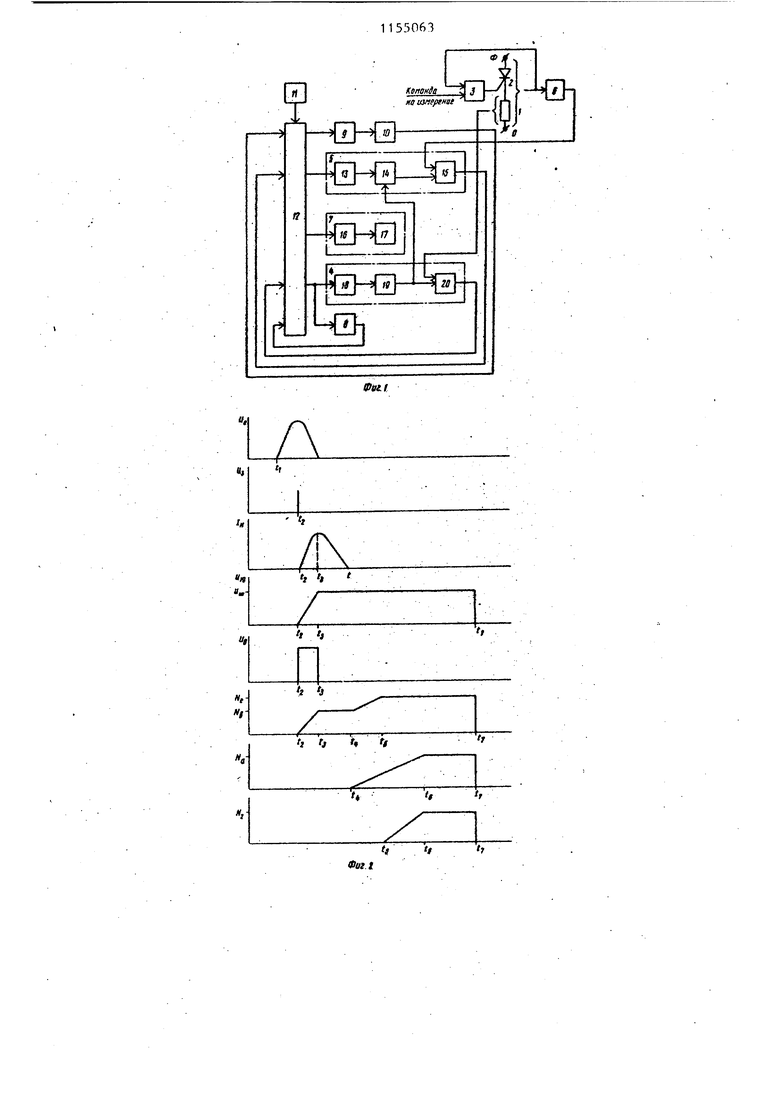

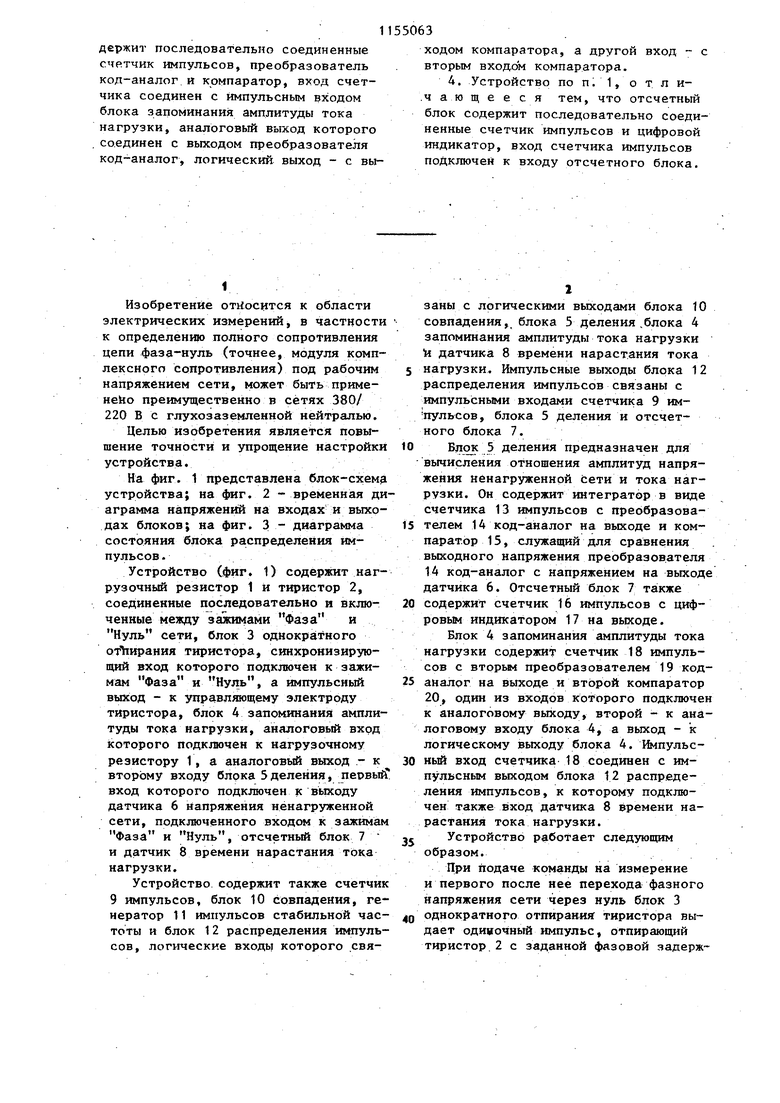

На фиг. 1 представлена блок-схемд устройства; на фиг. 2 - временная диаграмма напряжений на входах и выходах блоков; на фиг. 3 - диаграмма состояния блока распределения импульсов .

Устройство (фиг. 1) содержит нагрузочный резистор 1 и тиристор 2, соединенные последовательно и включенные между зажимами Фаза и Нуль сети, блок 3 однократного отЬирания тиристора, синхронизирующий вход которого подключен к зажимам Фаза и Нуль, а импульсный выход - к управляющему электроду тиристора, блок 4 запоминания амплитуды тока нагрузки, аналоговый вход которого подключен к нагрузочному резистору 1, а аналоговый выход - к второму входу блока 5деления, первый вход которого подключен к выходу датчика 6 Напряжения ненагруженной сети, подключенного входом к зажимам Фаза и Нуль, отсчетный блок 7 и датчик 8 времени нарастания тока нагрузки.

Устройство содержит также счетчик 9 импульсов, блок 10 совпадения, генератор 11 импульсов стабильной частоты и блок 12 распределения импульсов, логические входы которого связаны с логическими выходами блока 10 совпадения, блока 5 деления .блока 4 запоминания амплитуды тока нагрузки и датчика 8 времени нарастания тока

нагрузки. Импульсные выходы блока 12 распределения импульсов связаны с импульсными входами счетчика 9 импульсов, блока 5 деления и отсчетного блока 7.

БЛОК 5 деления предназначен для вычисления отношения амплитуд напряжения ненагруженной сети и тока нагрузки. Он содержит интегратор в виде счетчика 13 импульсов с преобразователем 14 код-аналог на выходе и компаратор 15, служащий для сравнения выходного напряжения преобразователя 14 код-аналог с напряжением на выходе датчика 6. Отсчетный блок 7 также

содержит счетчик 16 импульсов с цифровым индикатором 17 на выходе.

Блок 4 запоминания амплитуды тока нагрузки содержит счетчик 18 импульсов с вторым преобразователем 19 коданалог на выходе и второй компаратор 20, один из входов которого подключен к аналоговому выходу, второй - к аналоговому входу блока 4, а выход - к логическому выходу блока 4. Шпульсный вход счетчика 18 соединен с импульсным выходом блока 12 распределения импульсов, к которому подключен также вход датчика 8 времени нарастания тока нагрузки.

Устройство работает следующим образом.

При подаче команды на измерение и первого после нее перехода фазного напряжения сети через нуль блок 3

однократного отпираний тиристора выдает одиночный импульс, отпирающий тиристор.2 с заданной фазовой задержкой, и через нагрузочный резистор проходит одиночный импульс тока. Амплитуда его 4 иксируется в блоке 4 запоминания амплитуды тока нагрузки, а длительность его переднего фронта от начала до момента достижения амплитуды измеряется датчгхом 8 времени нарастания тока нагрузки В продолжение этого интервала счетчик 8 импульсов заполняется через блок 12 распределения импульсов (вых.. 1. фиг. 3) импульсами от гене,ратора 11 импульсов стабильной частоты. По окончании этого интервала времени появляются импульсы на втором выходе.блока 12 распределения импульсов, откуда они поступают в счетчик 13 импульсов блока 5 деления. При этом импульсы продолжают поступать и в счетчик 9. На цифрово вход преобразователя 14 код-аналог блока 5 деления поступает непрерьгон возрастающее число из счетчика 13, а на вход опорного напряжения - ана логовая величина с выхода блока 4 запоминания тока нагрузки. На выход преобразователя 14 код-аналог форми руется аналоговый сигнал, пропорциональный произведений этих величин, которьй поступает на вход компарато ра 15 блока 5 деления, где сравнивается с аналоговым сигналом датчика 6 амплитуды нагружения ненагруженной сети. , Согласно теореме об активном дву полюснике полное (комплексное) сопротивление цепи фаза-нуль может быт определено по формуле 7 - R - R ц и н н где УС - напряжение сети; и - падение напряжения на нагрузочном резисторе 1; R - сопротивление нагрузочного резистора 1. Поскольку, векторные величины труд но поддаются инструментальной обработке, в приборе вместо векторных величин Ug и UC используются их ска лярные (амплитудные) значения U и , . Это и вызывает методическую погрешность: при одном и том же модуле измеряемого сопротивления (Z,) результаты измерения могут быть разными в зависимости от величины фазного угла Чц комплексного сопротивления г„. 063 Для уменьшения этой погрешности ь основную расчетную формулу /2ц/: Кн-5 -- R« вводится угловая поправка, являющаяся нелинейной функцией двух аргументов: падения напряжения на нагрузочном резисторе 1 и времени нарастания тока нагрузки до амплитудного значения. Измеряемое сопротивление Zij; определяется как сумма числа импульсов Кд, пропорционального отнощению амплитуды напряжения сети к амплитуде тока нагрузки, и числа импульсов Ng, пропорционального времени нарастания тока нагрузки, за вычетом числа импульсов N, пропорционального некоторому постоянному коэффициенту с: N N«+Ne-N, где N па ; 4:tT. амплитуда напряжения ненагруженной сети; 1нт амплитуда тока нагрузки Nfc. -и время нарастания тока до амплитудного значения; NJ, пс; а, Ь, с- постоянные коэффициенты; п - число импульсов на . Выражение N . N + N - N, является цифровым эквивалентом эмпирической расчетной формулы вида + boL - С, олученной из основной, приведённой ьше расчетной формулы (1) добавлеием фазовой поправки Ьы, где oi. ремя нарастания тока (в электричесих градусах). В период t -yt наастания измерительного TOKsCчисло в четчике 9 возрастает до Ng, в перид tj - t- его снижения остается незменньм и далее в период t - t озрастает до числа N,, что фиксиуется блоком 10 совпадения. В этот ериод происходит также заполнение четчик 13, которое продолжается до омента tg, -когда число в счетчике 3 достигает N. В интервале t - t мпульсы поступают также в счетчик 6, заполнение которого прекращается. $ когда аналоговая величина на выходе преобразователя 14 код-аналог сравн вается с аналоговым сигналом датчик 6 напряжения ненагруженной сети 6, Число N-J в счетчике 16 импульсов вы дается на индикацию и равно разност числа Nq и (N - Nj) , т.е. N NO + Nb - N. Счетчик 18 импульсов блока запоминания тока нагрузки заполняется импульса№1И от блока 12 распределени импульсов до тех пор, пока число в счетчике, преобразованное в аналого вую величину преобразователем 19 код-аналог, не сравняется на вхиде компаратора 20 с амплитудой падения напряжения на нагрузочном резисторе 1. Шпульсы, заполняющие счетчик 18, поступают также на вход датчика 8 времени нарастания тока нагруз ки. Момент окончания заполнения счетчика импульсов 18 совпадает с моментом достижения амплитудного значения тока нагрузки. Оптимальные с точки зрения обеспечения минимальной методической погрешности, значения коэффициентов были рассчитаны с Помощью ЭЦВМ и приняты следующими: а 0,283 Ом; В 0,87 0--- эл.град с 0,300 Ом. В опытном образце прибора число импульсов на 1 Ом выбрано , так что окончательно N 283 , N 0,87о(.; N 300. Сопротивление нагрузки в нем принято R 3 Ом для диапазона измерений Z,u, 0,50-5,0 Ом и К„ 0,3 Ом для диапазона 0,05-0,50 Ом. При это приведенная методическая погрешност не превышает 4,5%, т.е. снижена по сравнению с прототипом более чем в 2 раза. 636 Что касается блока 3 отпирания тиристора, oh представляет собой фазосмещающий блок, синхронизированный сетью. Команда на измерение, поступающая в блок 3 однократного отпирания тиристора, одновременно деблокирует счетчики 9 и 18 импульсов (цепи сброса счетчиков на фиг. 1 не показаны). Блок однократного отпирания тиристора может быть связан также с выходом счетчика 9 (на фиг. 1 эта связь не показана). В этом варианте счетчик 9 импульсов начинает заполняться в момент t перехода фазного напряжения через 0. Когда число в счетчике достигает значения, соответствующего заданной фазовой задержке (52 или 60 эл.град. в опытном образце прибора) , срабатывает блок совпадения в блоке 3 и формируется отпирающий импульс. Блок 10 совпадения в этом варианте настраивается на число 300+52, что обеспечивает сохранение величины Ng 300. Основное преимущество изобретения состоит в повьшении точности измерения за счет узла реального фазного угла цепи фаза-нуль и значительной величины измерительного тока, а также за счет исключения основного источника погрешности - аналогового функционального преобразователя, что позволило вьшолнить прибор на базе цифровых 1штегральных микросхем и тем самьм дополнительно уменьшить инструментальную погрешность. Другим преимуществом изобретения является простота настройки благодаря применению нерегулируемых схемных узлов дискретного действия. Практически настройка сводится лишь к установке нулей компараторов в отличие от известного устройства, в котором требовалось устанавливать коэффициенты передачи операционных усилителей, постолнные времени интегрирования и настраивать сложный функциональньй преобразователь.

Л

«

ft V

t tj

ffxff

ft fj

Вых. I

ft ft

ВшЕ

z t.

ФыгЗ

| СПОСОБ ОСУЩЕСТВЛЕНИЯ ИС'КУССТВЕННОГО КОРОТКОГОЗАМЫКАНИЯ | 0 |

|

SU253903A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения полного сопротивления цепи фаза-нуль | 1979 |

|

SU797354A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-09-30—Публикация

1983-11-29—Подача