rep, вход которого соединен с выходом элемента ИЛИ, прямой выход - с вторым входом первогоэлемента совпадения предпоследнего блока управления и с входом сброса второго счетчика импульсов, а инверсный - с вторым входом второго элемента совпадения предпоследнего блока управления и входом сброса первого счетчика VIMпульсов, а входы записи всех счетчиков импульсов делителя частоты с переменным коэффициентом деления соединены с выходной шиной устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным переменным коэффициентом деления | 1985 |

|

SU1372615A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Делитель частоты следования импульсов с переменным дробным коэффициентом деления | 1989 |

|

SU1653155A1 |

| Делитель частоты с дробным автоматическиизМЕНяющиМСя КОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU819966A1 |

| Делитель частоты следования импульсов | 1976 |

|

SU587628A1 |

| Пересчетное устройство | 1979 |

|

SU849468A1 |

| Дробный делитель частоты следования импульсов | 1983 |

|

SU1120490A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1980 |

|

SU949821A1 |

| Устройство для измерения отношения частот двух импульсных последовательностей | 1981 |

|

SU1008667A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

ДЕЛИТЕПЬ ЧАСТОТЫ С ДРОБНЫМ ПЕРЕМЕННЫМ КОЭФФИЦИЕНТОМ ДЕЛЕНИЯ, содержащий делитель частоты с переменным коэффициентом деления, состоящий из соединенных последовательно счетчиков импульсов, счетный вход первого из которых соединен с входной шиной устройства, а выход переноса последнего - с выходной шиной устройства, информационные входа всех счетчиков импульсов соединены с выходами соответствующих матриц выбора целой части коэффициента деления, о т л и ч а ю щ и и с я тем, что, с целью повышения точности путем уменьшения величины фазовой девиации выходной импульсной последовательности, в него введены п блоков управления,.где п- кЬличество шагов разложения коэффициента деления, каждый из иерйых п-1 блоков управления содержит первый, второй и третий элементы совпадений, первые входы которых во всех, кроме первого блока управления, соединены с выходом третьего элемента совпадения предыдущего блока управления, а в первом блоке управления - с выходной шиной устройства, первый и второй счетчики импульсов, счетные входы которых соединены с выходами соответственно первого и второго элементов совпадения, первую и .вторую матрицы, выходы которых соединены с информационными входами соответственно первого и второго счетчиков импульсов, элемент ИЛИ, первый и второй входы которого соединены с выходами переноса соответственно первого и второго счетчиков импульсов, а третий - с выходом третьего элемента совпадения, и счетный триггер, вход которого соединен с выходом элемента ИЛИ, инверсный выход - с вторым входом третьего элемента сов0} падения, входами сброса первого и второго счетчиков импульсов и с вторым входом второго элемента совпадения предьщущего блока управления, .прямой выход во всех, кроме первого блока управления, - с вторым входом первого элемента совпадения предыдуСП щего блока управления, а в первом з: блоке управления - с входом управления первой матрицы выбора целой час tsD .ти коэффициента деления, при этом :л последний блок управления содержит первый и второй счетчики импульсов, счетные входы которых соединены с выходом третьего элемента совпадения предпоследнего блока управления, первую и вторую матрицу выбора, выходы которых соединены с информационными входами соответственно первого и второго счетчиков импульсов, элемент ИЛИ, первьв и второй входы которого соединены с выходами переноса соответственно первого и второго счетчиков импульсов, и счетный триг

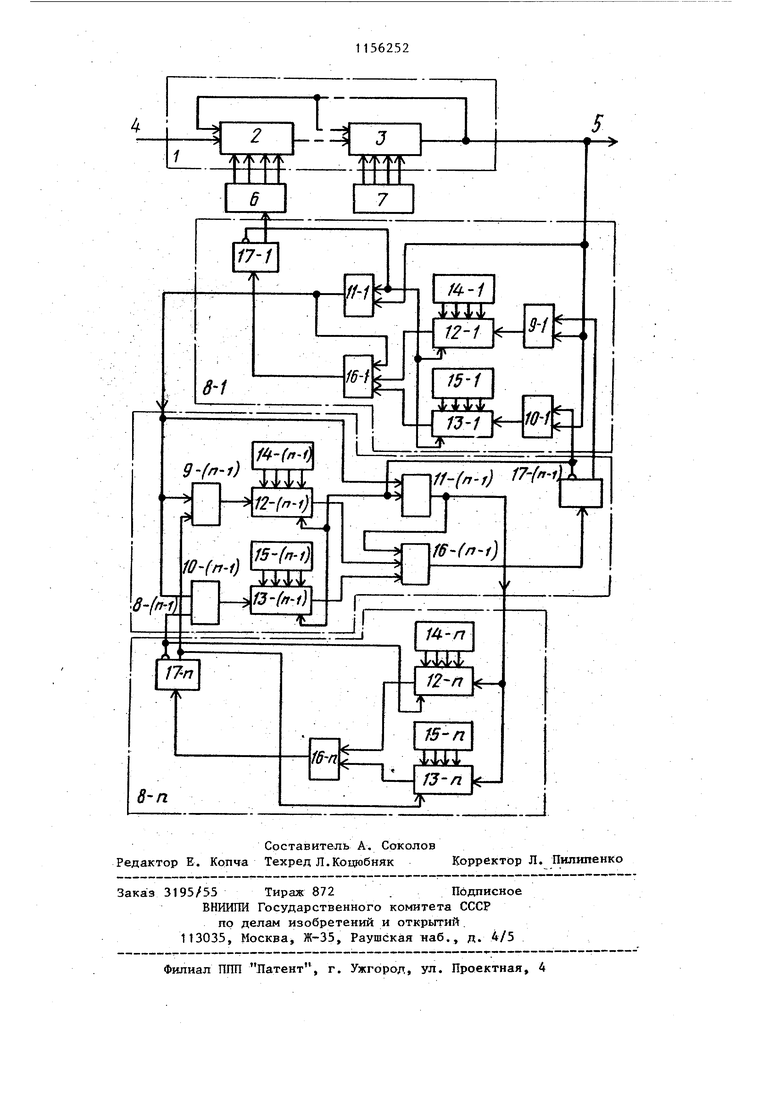

Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частот. Известен делитель частоты с дробным переменным коэффициентом деления, содержащий высокочастотный счет. чик с двумя фиксированными значениями коэффициента пересчета, элемент ИЛИ, программный счетчик младшего разряда, программный счетчик старших разрядов, блок дробных разрядов и ши ны ввода кода управления коэффициентом деления СОНедостатками известного делителя являются значительная фазовая девиация выходной импульсной последовател ности и, кроме того, низкая точность при коэ4фициентах деления, представляющих собой смешанную простую дробь Наиболее близким по технической сущности к предлагаемому является де литель частоты с дробным переменным коэффициентом деления, содержащий делитель частоты с переменным коэффициентом деленияj состоящий из соединенных последовательно счетчиков импульсов, счетный вход первого из которых соединен с входной шиной уст ройства, а выход переноса последнего - с выходной шиной устройства, ин формационные входы всех счетчиков импульсов соединены с выходами соответствующих матриц выбора целой части коэффициента деления, вход управления первой из которых соединен с выходом триггера памяти, первый и второй входы которого соединены соответственно с первым и вторым выходАми блока сравнения, первый и второй входы которого соединены с выходами блоков установки соответственно числителя и знаменателя коэффициента деления, а третий - с выходом счетчи ка дробной части коэффициента делени счетный вход которого соединен с выходной шиной устройства, а вход сброса - через формирователь импульса с первым выходом блока сравнения 2. Недостатком этого устройства является низкая точность из-за значительной фазовой девиации выходной импульсной последовательности, которая зависит от коэффициента деления. Цель изобретения - повышение точности путем уменьшения величины фазовой девиации выходной импульсной последовательности. Поставленная цель достигается тем, что в делитель частоты с дробным переменным коэффициентом деления, содержащий делитель частоты с переменным коэффициентом деления, состоящий из соединенных последовательно счетчиков импульсов, счетный вход первого из которых соединен с входной шиной устройства, а выход переноса последнего - с выходной шиной устройства, информационные входы всех счетчиков импульсов соединены с выходами соответствующих матриц выбора целой части коэффициента деления, введены п блоков управления, где п- количество шагов разложения коэффициента деления, каждый из первых ri-l блоков управления содержит первый, второй и третий элементы совпадений, первые входы которых во всех, кроме первого блока управления, соединены с выходом третьего элемента совпадения предыдущего блока управления, а в первом блоке управления - с выходной шиной устройства, первый и второй счетчики импульсов, счетные входы которых соединены с выходами соответственно первого и второго элементов совпадения, первую и вторую матрицы, выходы которых, соединены с информационными входами соответственно первого и второго счётчиков импульсов, элемент ИЛИ, первый и второй входы которого соеди нены с выходами переноса соответственно первого и второго счетчиков им пульсов, а третий - с выходом третьего элемента совпадения, и счетный триггер вход которого соединен с выходом элемента ИЛИ, инверсный выход - с вторым входом третьего элемента совпадения, входами сброса первого и второго счетчиков импульсов и с вторым входом второго элемента совпадения предыдущего блока управления, прямой выход во всех, кроме первого блока управления, - с вторьм входом первого элемента совпадения предыдущего блока управления а в первом блоке управления. - с входом управления первой матрицы выбоpa целой части коэффициента деления, при этом последний блок управления содержит первый и второй счетчики импульсов, счетные входы которых сое динены с выходом третьего элемента совпадения предпоследнего блока управления, первую и вторую вы бора, выходы которых соединены с информационными входами соответственно первого и второго счетчиков импульсов, элемент ИЛИ, первый и второ входы которого соединены с выходами переноса соответственно первого и второго счетчиков импульсов, и счетный триггер, вход которого соединен с выходом элемента ИЛИ, прямой выход с BTopbW входом первого элемента сов падения предпоследнего блока управле ния и с входом сброса второго счетчи ка импульсов, а инверсный - с вторым входом второго элемента совпадения предпоследнего блока управления и входом сброса первого счетчика импульсов, а входы записи всех счетчиков импульсов делителя частоты с пер менным коэффициентом деления сосдинё ны с вькодной шиной устройства. На чертеже изображена структурная электрическая схема делителя частоты с дробным переменным коэффициентом деления. Делитель частоты с дробным переменным коэффициентом деления содержи делитель 1 частоты с переменным коэф фициентом деления, состоящий из соединенных последоватед|ьно счетчиков 2 и 3 импульсов, счетный вход первог из которых соединен с входной шиной 4 устройства, а выход переноса пос-; леднего - с выходной шиной 5 устройства, информационные входы всех счетчиков импульсов соединены с выходами соответствующих матриц 6 и 7 выбора целой части коэффициента деления п блоков ,..., 8- (м-1), 8-h управления, где п- количество шагов разложения коэффициента деления, к да;ый из первых п-1 блоков 8-1, -;.., 8-(h-1) управления содержит первый, второй и третий элементы 9-1, ..., 9-(п-1); 10-1, ..., lO-(n-l); 11-Т, ..., 11-(п-1) совпадений соответственно, первые входы которых во всех, кроме первого блока .управления, соединены с выходом третьего элемента совпадения предыдущего блока управления, .а в nejaeoM блоке 8-1 управления . с выходной шиной 5 устройства, первый и второй счетчики 12-1, ..., 12-(п-1) и 13-1, ..., 13-(п-1) импульсов, счетные входы которых соединены с выходами относительно первого, и второго элементов 9-1 ,..., 9-(ii-1) и 10-1, ..., lO-(n-l) совпадений, первую и вторую матрицы 14-1, ..., 14-(п-1) и 15-1, ..., 15-(п-1) соответственно, выходы которых соединены с информационными входами соответственного первого и / второго счетчиков 12-1, ..., 12-(п-1) и 13-1, ..., 13-(п-1) импульсов, элемент 16-1, ..., 16-(п-1) ИЛИ, первый и второй выходы которого соединены с выходами переноса соответственно первого и второго счетчиков 12-1, ..., 12-(п-1) и 13-1, ..., 13-(h-1) импульсов, а третий - с выходом третьего элемента 11-1, ,.., 11-(п-1) совладения, и счетный триггер 17-1, ..., 17-(п-1), вход которого сое- , динен с выходом элемента 16-1, ..., 1б-(п-1) ИЛИ, инверсньв выход - с BTopbiM входом третьего элемента 11-1, ..., 11-(п-1) совпадения, входами сброса соответственно первого и втогрого счетчиков 12-1, ..., 12-(п-1) и 13-1,..., 13-(п-1) импульсов и с втр- рьм входом второго элемента совпадения предьщущего блока управления, прямой выход во всех, кроме первого блока управления - с вторьм входом первого элемента совпадения предьщу его блока управления, а в первом с входом управления 6 выбора елой части коэффициента делеиия, up этом последний блок 8-п управления одержит соответственно первый и втог ой ечётчики 12-г и 13-п юшульсов.

счетные входы которых соединены с выходом третьего элемента 11-(п-1) совпадения предпоследнего блока 8-(п-1) управления, соответственно первую и вторую матрицу 14-п и 15-п выбора, выходы которых соединены с информационными входами соответственно первого и второго 12-п и 13-п счетчиков импульсов, элемент 16-п ИЛИ, первый и второй входы которого соединен с выходами переноса соответственно первого и второго 12-п и 13-ri счетчиков импульсов, и счетный триггер 17-п, вход которого соединен с выходом элемента. 16- ИЛИ, прямой выход - с вторым входом первого элемента 9-(п-1) совпадения предпоследнего блока 8-(h-l) управления и с входом сброса второго счетчика 13-п импульсов, а инверсный - с вторым входом второго элемента 10-(п-1) совпадения предпоследнего блока 8-(п-1) управления и входом сброса первого счетчика 12-п импульсов, а входы записи всех счетчиков импульсов делителя 1 частоты с переменным коэффициентом деления соединены с выходной шиной 5 устройства.

Делитель частоты импульсов работает следующим образом.

Выходная последовательность импульсов формируется из входной последовательности за счет того, что устройство пропускает на выход лишь часть импульсов входной последовательности, интервал между выходными импульсами в процессе деления изменяется в зависимости от коэффициента деления КД.

Практически деление осуществляетс на целый коэффициент, периодически изменяющийся во времени на единицу, Если коэффициент деления Q представляет собой несократимую неправильную дробь

Q- М -Р, - Pg

: I I е

.где Р - целая часть КД Q;

m - числитель дробной части Q ; 1 - знаменатель дробной части Q то устройство делит входную частоту нсколько раз на коэффициент равный целой части Р и несколько раз на коэффициент (Р+1).

Определяют в какой последовательности должны чередоваться КД Р и (Р+1) для получения минимальной величины фазовой девиации выходной импульсной последовательности.

Представляют КД в следующем виде

р т- (.P- iiT - PCe-m)

г

Отсюда ввдно, что КД Р будет повторяться с(-т) раз, а КД (Р+1) m раз.

1-й шаг. Рассматривают как соотносятся между собой коэффициенты повторения с и т,Если от, то расс

сматрииают дробь - , если ,

m

то - -- . с

Пусть ога,тогда дробь можно представить в виде

k ((

ITS ГПП

Отсюда видно, что КД (Р+О будет повторяться k раз через (F+1) КД Р d(m-k) раз через F КД Р,

2-й шаг. Рассматривают как соотносятся между собой коэффициент повторения k и d.

Пусть , тогда

L N JL (- ьчg-ь)N

d d с/, ,

и так далее до тех пор, пока числитель рассматриваемой дроби или разность между знаменателем и числителем равна единице.

Если , то первоначальной установкой КД,делителя 1 устанавливается равным Р, если , то (Р+1). Коэффициенты деления счетчиков 12-1 и 13-1 первого блока 8-1 управления равны F и (F+1). КД счет чиков импульсов остальных блоков управления определяются аналогично в процессе разложения дроби. Количество п блоков управления равно количеству шагов разложения, а КД счетчиков импульсов последнего блока управления равны числителю и разности между знаменателем и числителем последней дроби разложения.

Колчество блоков, управления можн сократить в зависимости от требуемой точности, прервав процесс разло жения исходной дроби на любом шаге.

Пример. Пусть КД равен или 3 -rj . Тогда КД 4 делителя

1 будет повторяться 13 раз, а КД 3 делителя 1 - 30 раз за один цикл счета, равный 142 периодам входных импульсов. С помощью матриц 6 и 7(реализов ных, например, при помощи последов тельно параллельного регистра) уст навливают КД делителя 1, равный 3, Если дальше не раскладывать КД, то имеется один блок управления с коэффициентом деления 30 и 13, и КД делителя 1 за один цикл будет меня ся следующим образом: 3-4-4 13 Рассматривают дробь 1-й шаг, 30 2 с разложением 9 13 Если прекратить разложение на этом шаге, то КД будет меняться ел дунмцим образом: В этом случае имеется один блок управления с коэффициентами деления 2 и 3 и один блок управления с коэф фициентами деления 9 и 4. Продолжают разложение, 2-й шаг. с разложением В результяте получают в числителе дроби единицу, и. процесс разложения закончен. В этом случае имеют два блока уп равления с коэффициентами деления 2,3 и 2,3 и последний блок управления с коэффициентом деления счетчиков 3 и 1. Коэффициенты деления сче чиков импульсов блоков управления у танавливаются соответствующими матр цами. КД делителя 1 в конечном ввде бу меняться следующим образом: 334 334 3334 .... 334 334 334 3334. 1 Обозначают коэффициенты деления счетчиков 12-1, tS-t, 12-(п-1), 1 8 13-(п-1), 12-п и 13-п соответственно через k-, k, , k,, k.., k и k, 1 2 3 5 i Проверяют правильность установки КД счетчиков по формулам (k,-H)(k3-k5H-k -k)-i-(k2+1)(ky+k) - знаменатель (kj+Ok; +()-kj - числитель. Тогда (2+1)(2-3+3-1) + (3-И)(3-|-1)43, (2+1) О + (З+О- 1 13. В этих формулах к КД прибавляется единица за счет того, что часть выходных импульсов проходит не через счетчики, а через элементы 11-1, ,.., ll-(n-I) совпаде П1Я. Работа устройства начинается с установки в исходное состояние всех триггеров 17-117-п так, чтобы на прямых выходах была логическая единица, и с установки значений коэффициентом дробного делителя. Целая часть коэффициента деления задается матрицами 6 и 7. ,5, Причем, если и,Ь то устанавливается значение (Р+1), если ,5, то устанавливается значение Р. Коэффициенты деления счетчиков 12-1, ..., 12-п и 13-1, ..., 13-п задаются соответственно матрицами 14-1, ..., 14-п и 15-115-,t. Импульсы входной частоты поступают на шину 4 и вход делителя 1. Импульсы с выхода делителя 1 поступают на шину 5, на входы предварительной записи счетчиков 2 и 3 и на первые входы элементов 9-1, 10-1, 11-1. Однако импульсы через элементы 10-1 и 11-1 не проходят, так как они заперты сигналами триггеров 17-(п-1) и 17-. Элемент 9-1 открыт, и его выход-, ные Сигналы поступают на счетчик 12-1. Когда в счетчике 12-1 накапливается количество импульсов, заданное матрицей 14-1, йа его выходе переноса появляется импульс, который, пройдя через элемент 16-1, изменяет состояние триггера 17-1. При этом изменяется на единицу коэффициент деления делителя 1, обнуляются счетчики 12-1 и 13-1, и открывается элемент 11-1. Следующий импульс с выхода деителя 1, пройдя через элементы П-1 и 9-(п;-1), регистрируется счетчиком 12-(.Н-1), кроме того, импульс с выхода элемента 11-1 проходит через элемент 16-1 и переводит триггер

17-1 в исходное состояние. Триггер 17-1 изменяет коэффициент делителя 1, запирает элемент 11-1 и разрешает ч счет счетчикам 12-1 и 13-1. счетчик 12-(Vi-1) накапливает количество импульсов, заданное матрицей 14-(), на его выходе переноса появляется импульс, который, пройдя через элемент 16-(п-1), перебрасывает триггер 17-(п-1). При этом рткрываются элементы 10-1 и 11-(п-1), закрывается элемент.9-1, а счетчики 12-(п-1) и 13-(rt-1) будут обнулены. Когда в счетчике 13-1 накапливается количество импульсов, заданное матри цей IS-I, на его выходе nepeiioca появляется импульс, который, пройдя через элемент 16-1, перебрасывает триггер 17-1. Следующий импульс с выхода делителя 1 проходит через

элементы 11-1 и 11-(п-1), при этом перебрасываются триггеры 17-1 и 17-(п-1), импульс с выхода элемента 11-1 поступает на вход счётчика 12-п Процесс деления происходит до тех пор, пока на выходе переноса счетчика 13-г появитсй импульс. При этом триггер 17-п возвращается в исходное состояние. Триггеры 17-1 и 17-(п-1) уже находятся в исходном состоянии.

Таким образом, цикл деления частоты заканчивается.

В предлагаемом устройстве точност (стационарная) выше, так как величина фазовой девиации выходной импульсной последовательности в предлагаемом устройстве не превышает одного периода входной частоты при любом коэффициенте деления.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Авторское свидетельство | |||

| СССР .№ 913600, М., кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Делитель частоты следования импульсов с дробным переменным коэффициентом деления | 1981 |

|

SU951713A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-05-15—Публикация

1983-10-10—Подача