Устройство работает следующим образом.

Выходная последовательность импульсов формируется из входной последовательности за счет того, что устройство пропускает на выход лишь часть импульсов входной последовательности, интервал между выходными импульсами в процессе деления изменяется в зависимости от КД.

( 1)(Р + 1)...(Р+ 1)

50

m

55

Шаг 1. Рассматривают как соотносятся ,между собой коэффициенты повторения си т. Если с т, то рассматривают

сm

дрибь -, если с : т, то -. mс

Пусть с т, тогда дробь можно представить в виде

F

m m

. i( k)F

13726154

Отсюда видно, что КД (Р -t- 1) пов(F + 1) КД Р ез F КД Р, т.е.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с дробным переменным коэффициентом деления | 1983 |

|

SU1156252A1 |

| Устройство для преобразования двоичной последовательности в балансный троичный код | 1991 |

|

SU1807561A1 |

| Дискретное фазосдвигающее устройство | 1986 |

|

SU1406748A1 |

| Устройство для отображения информации | 1983 |

|

SU1152026A1 |

| Устройство фазоимпульсной модуляции | 1985 |

|

SU1411958A1 |

| Цифроаналоговый преобразователь | 1990 |

|

SU1750060A1 |

| ЦИФРОВОЙ МНОГОКАНАЛЬНЫЙ СИНТЕЗАТОР СЕТКИ ЧАСТОТ | 1995 |

|

RU2108655C1 |

| Делитель частоты следования импульсов | 1982 |

|

SU1150755A1 |

| Устройство для обработки и передачи информации учета товарной нефти | 1983 |

|

SU1129625A1 |

| Устройство для обработки изображений | 1991 |

|

SU1836693A3 |

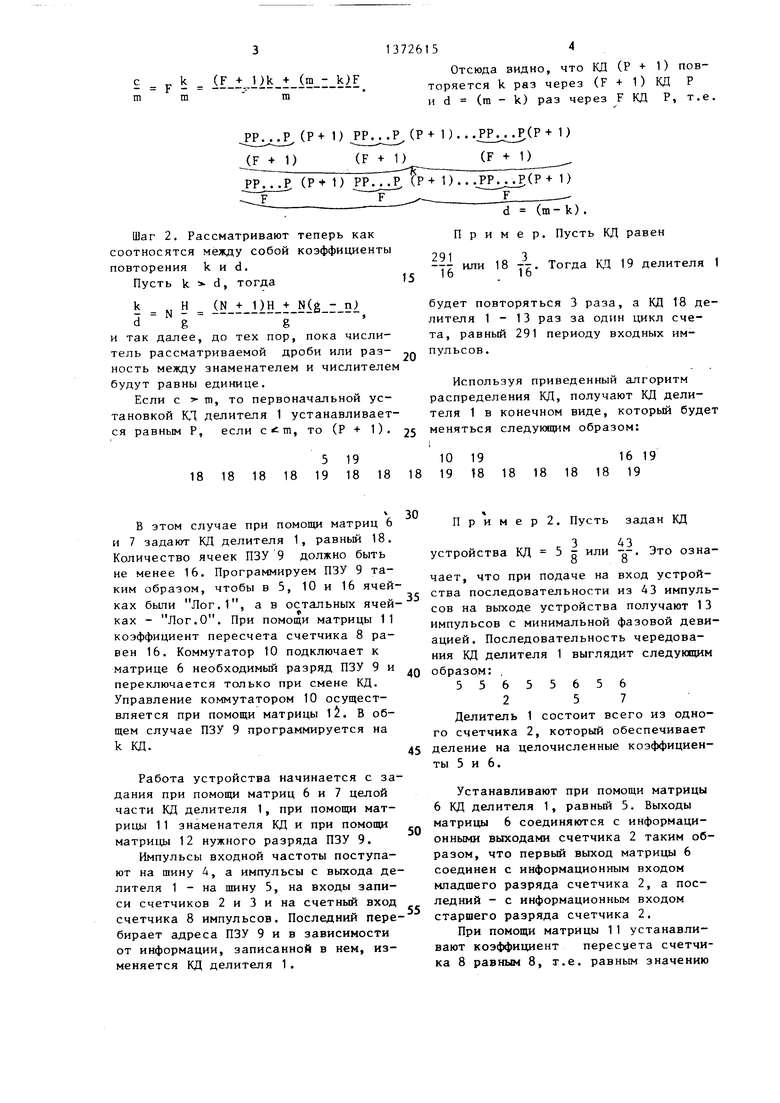

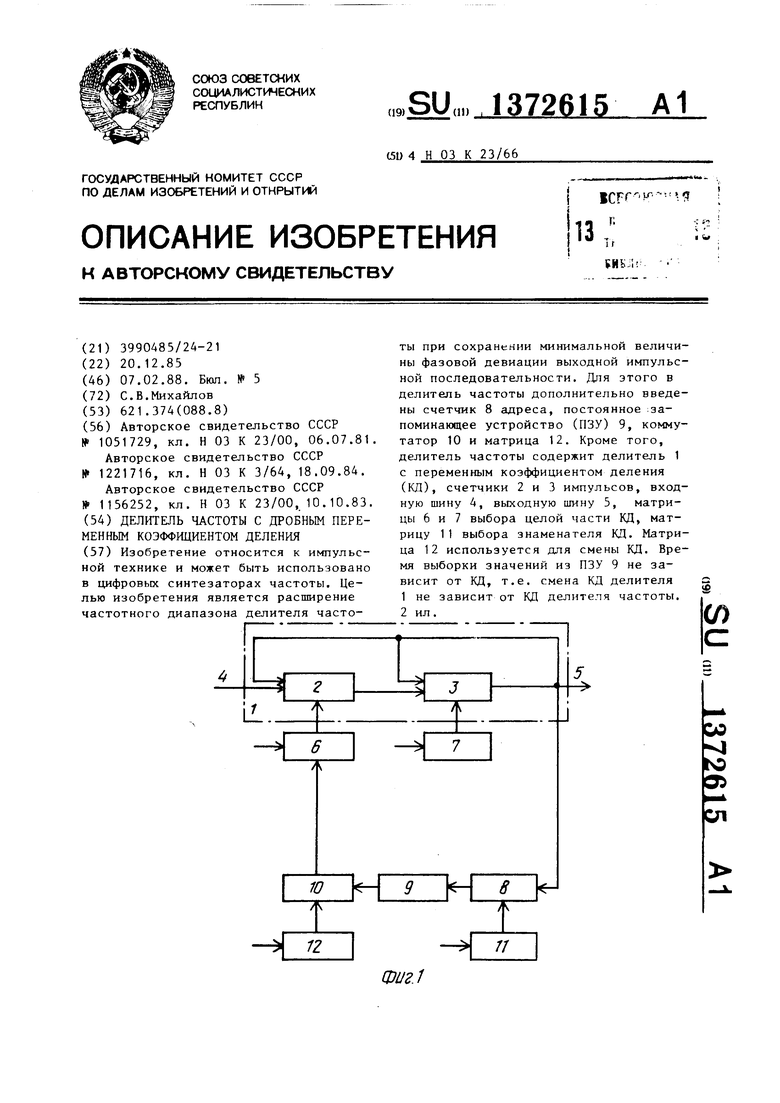

Изобретение относится к импульсной технике и может быть использовано в цифровьк синтезаторах частоты. Целью изобретения является расширение частотного диапазона делителя частоты при сохранении минимальной величины фазовой девиации выходной импульсной последовательности. Для этого в делитель частоты дополнительно введены счетчик 8 адреса, постоянное ;эа- поминающее устройство (ПЗУ) 9, коммутатор 10 и матрица 12. Кроме того, делитель частоты содержит делитель 1 с переменным коэффициентом деления (КД), счетчики 2 и 3 импульсов, входную шину 4, выходную шину 5, матрицы 6 и 7 выбора целой части КД, матрицу 11 выбора знаменателя КД. Матрица 12 используется для смены КД. Время выборки значений из ПЗУ 9 не зависит от КД, т.е. смена КД делителя 1не зависит от КД делителя частоты. 2ил. i (Л

Шаг 2. Рассматривают теперь как соотносятся между собой коэффициенты повторения k и d.

Пусть k d, тогда

k Н (N + 1)Н + N(g - п)

«. : f - 3 ......«

di4

gg

и так далее, до тех пор, пока числитель рассматриваемой дроби или разность между знаменателем и числителе будут равны единице.

Если с т, то первоначальной установкой КД делителя 1 устанавливается равным Р, если с « т, то (Р 1) .

5 19 18 18 18 18 19 18 18

В этом случае при помощи матриц 6 и 7 задают КД делителя 1, равньй 18. Количество ячеек ПЗУ 9 должно быть не менее 16. Программируем ПЗУ 9 таким образом, чтобы в 5, 10 и 16 ячейках были Лог.1, а в остальных ячейках - Лог.О. При помощи матрицы 11 коэффициент пересчета счетчика 8 равен 16. Коммутатор 10 подключает к матрице 6 необходимый разряд ПЗУ 9 и переключается только при смене КД. Управление коммутатором 10 осуществляется при помощи матрицы li. В общем случае ПЗУ 9 программируется на k КД.

Работа устройства начинается с задания при помощи матриц 6 и 7 целой части КД делителя 1, при помощи матрицы 11 знаменателя КД и при помощи матрицы 12 нужного разряда ПЗУ 9.

Импульсы входной частоты поступают на шину 4, а импульсы с выхода делителя 1 - на щину 5, на входы записи счетчиков 2 и 3 и на счетный вход счетчика 8 импульсов. Последний перебирает адреса ПЗУ 9 и в зависимости от информации, записанной в нем, изменяется КД делителя 1.

Пример. Пусть КД равен

291 3

-77 или 18 77- Тогда КД 19 делителя 1 ID ID

будет повторяться 3 раза, а КД 18 делителя 1-13 раз за один цикл счета, равный 291 периоду входных импульсов.

Используя приведенный алгоритм распределения КД, получают КД делителя 1 в конечном виде, который будет меняться следуюпщм образом: I

10 1916 19

19 18 18 18 18 18 19

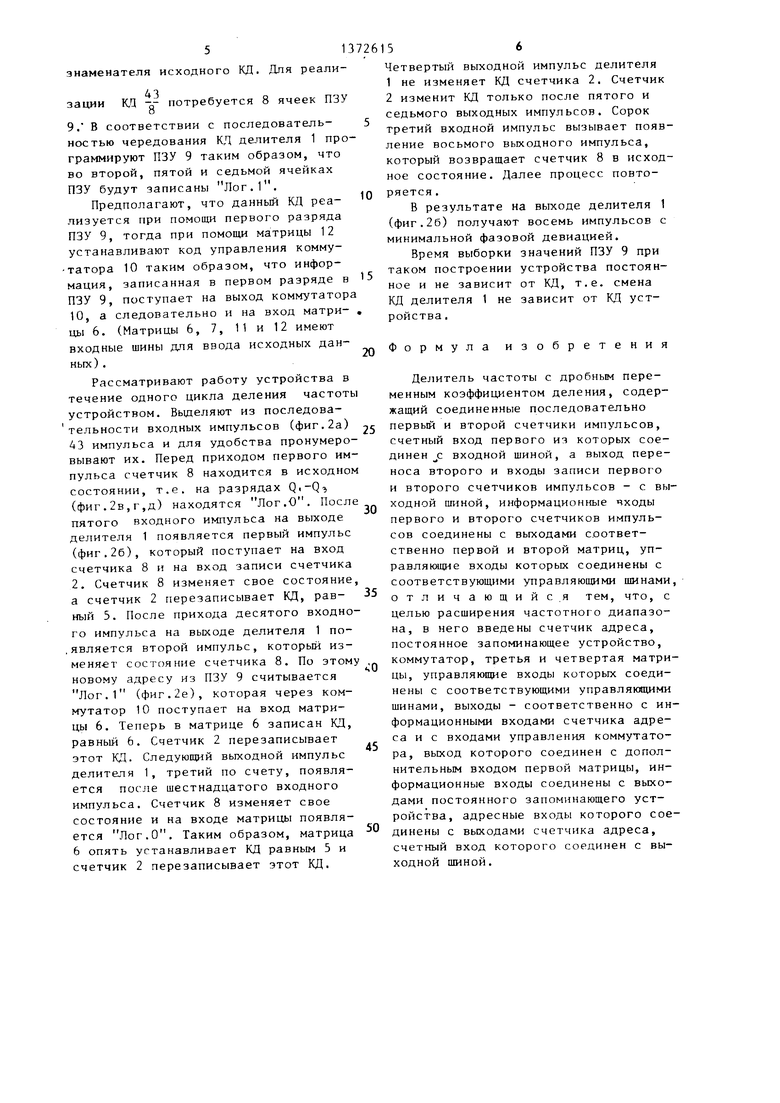

П Р и м е Р 2. Пусть задан КД

3 43 устройства КД 5 о или --. Это озна0 в

чает, что при подаче на вход устрой- ства последовательности из 43 импульсов на выходе устройства получают 13 импульсов с минимальной фазовой девиацией. Последовательность чередования КД делителя 1 выглядит слец.укщкн образом: .

55655656 2 57

Делитель 1 состоит всего из одного счетчика 2, который обеспечивает деление на целочисленные коэффициенты 5 и 6.

Устанавливают при помощи матрицы 6 КД делителя 1, равный 5. Выходы матрицы 6 соединяются с информационными выходами счетчика 2 таким образом, что первый выход матрицы 6 соединен с информационным входом младшего разряда счетчика 2, а последний - с информационным входом старшего разряда счетчика 2.

При помощи матрицы 11 устанавливают коэффициент пересуета счетчика 8 равным 8, т.е. равным значению

,- 10

20

513726

знаменателя исходного КД. Для реали43зации ВД -„- потребуется 8 ячеек ПЗУ

о

Предполагают, что данный КД pea лизуется при помощи первого разряда ПЗУ 9, тогда при помощи матрицы 12 устанавливают код управления коммутатора 10 таким образом, что информация, записанная в первом разряде в ПЗУ 9, поступает на выход коммутатора 10, а следовательно и на вход матрицы 6. (Матрицы 6, 7, 11 и 12 имеют входные шины для ввода исходных данных) .

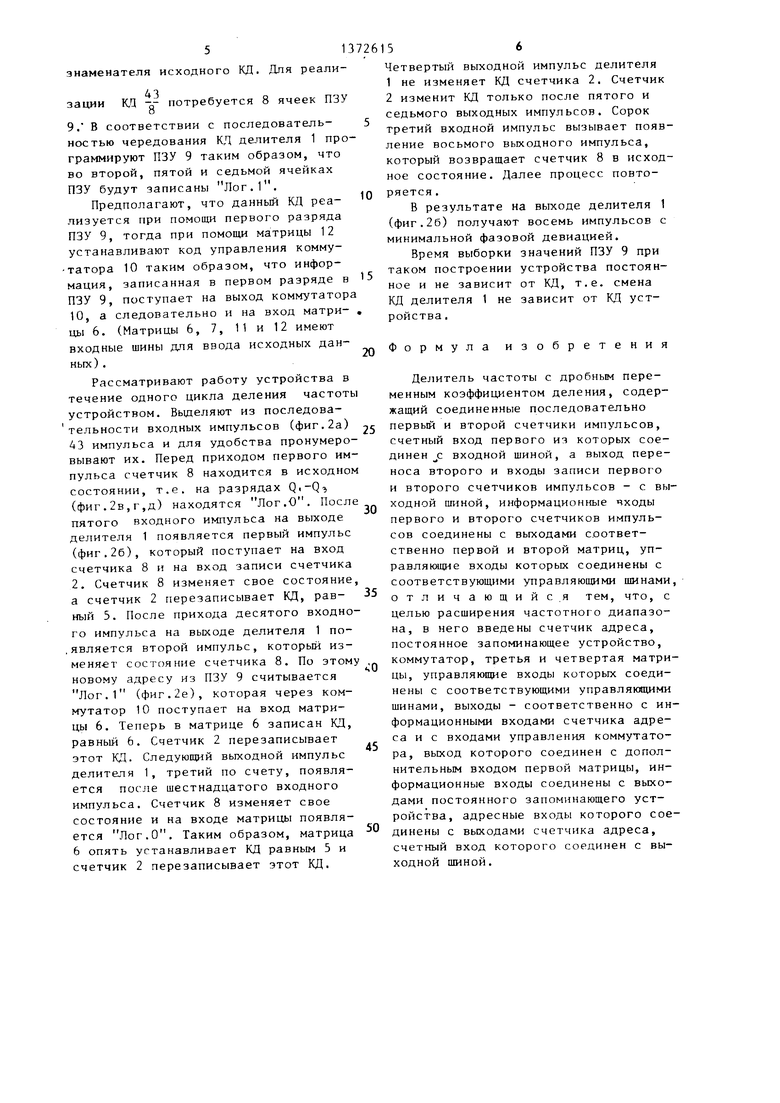

Рассматривают работу устройства в течение одного цикла деления частоты устройством. Выделяют из последовательности входных импульсов (фиг.2а) 25 43 импульса и для удобства пронумеровывают их. Перед приходом первого импульса счетчик 8 находится в исходном состоянии, т.е. на разрядах Qi-Q-i (фиг.2в,г,д) находятся Лог.О. После пятого входного импульса на выходе делителя 1 появляется первый импульс (фиг.2б), который поступает на вход счетчика 8 и на вход записи счетчика 2. Счетчик 8 изменяет свое состояние, а счетчик 2 перезаписывает КД, рав- 35 ный 5. После прихода десятого входного импульса на выходе делителя 1 появляется второй импульс, который изменяет состояние счетчика 8. По этому ,.. новому адресу из ПЗУ 9 считывается Лог.1 (фиг.2е), которая через коммутатор 10 поступает на вход матрицы 6. Теперь в матрице 6 записан КД, равный 6. Счетчик 2 перезаписывает этот КД. Следующий выходной импульс елителя 1, третий по счету, появляется после шестнадцатого входного импульса. Счетчик 8 изменяет свое состояние и на входе матрицы появлятся Лог.О. Таким образом, матрица 6 опять устанавливает КД равным 5 и счетчик 2 перезаписывает этот КД.

45

0

0

26

5

5 5

..

5

156

Четвертый выходной импульс делителя

1не изменяет КД счетчика 2. Счетчик

2изменит КД только после пятого и седьмого выходных импульсов. Сорок третий входной импульс вызывает появление восьмого выходного импульса, который возвращает счетчик В в исходное состояние. Далее процесс повторяется .

В результате на выходе делителя 1 (фиг.2б) получают восемь импульсов с минимальной фазовой девиацией.

Время выборки значений ПЗУ 9 при таком построении устройства постоянное и не зависит от КД, т.е. смена КД делителя 1 не зависит от КД устройства.

Формула изобретения

Делитель частоты с дробным переменным коэффициентом деления, содержащий соединенные последовательно первый и второй счетчики импульсов, счетный вход первого из которых соединен с входной шиной, а выход переноса второго и входы записи первого и второго счетчиков импульсов - с выходной шиной, информационные чходы первого и второго счетчиков импульсов соединены с выходами соответственно первой и второй матриц, уп- равляюш 1е входы которых соединены с соответствующими управляющими шинами, отличающийс.я тем, что, с целью расширения частотного диапазона, в него введены счетчик адреса, постоянное запоминающее устройство, коммутатор, третья и четвертая матрицы, управляющие входы которых соединены с соответствующими управляющими шинами, выходы - соответственно с информационными входами счетчика адреса и с входами управления коммутатора, выход которого соединен с дополнительным входом первой матрицы, информационные входы соединены с выходами постоянного запоминающего устройства, адресные входы которого соединены с вькодами счетчика адреса, счетный вход которого соединен с выходной шиной.

„431 5 10 15 20 25 30 35 0 «J/ 5 о I I I I I I I I I I I I I I 11 I I I I I I I I I I I I I I I I I I I I I I I I I I 11 I I I I I 11

Фиг. 2

| Делитель частоты с дробным коэффициентом деления | 1981 |

|

SU1051729A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для формирования импульсных последовательностей | 1984 |

|

SU1221716A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Делитель частоты с дробным переменным коэффициентом деления | 1983 |

|

SU1156252A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-02-07—Публикация

1985-12-20—Подача