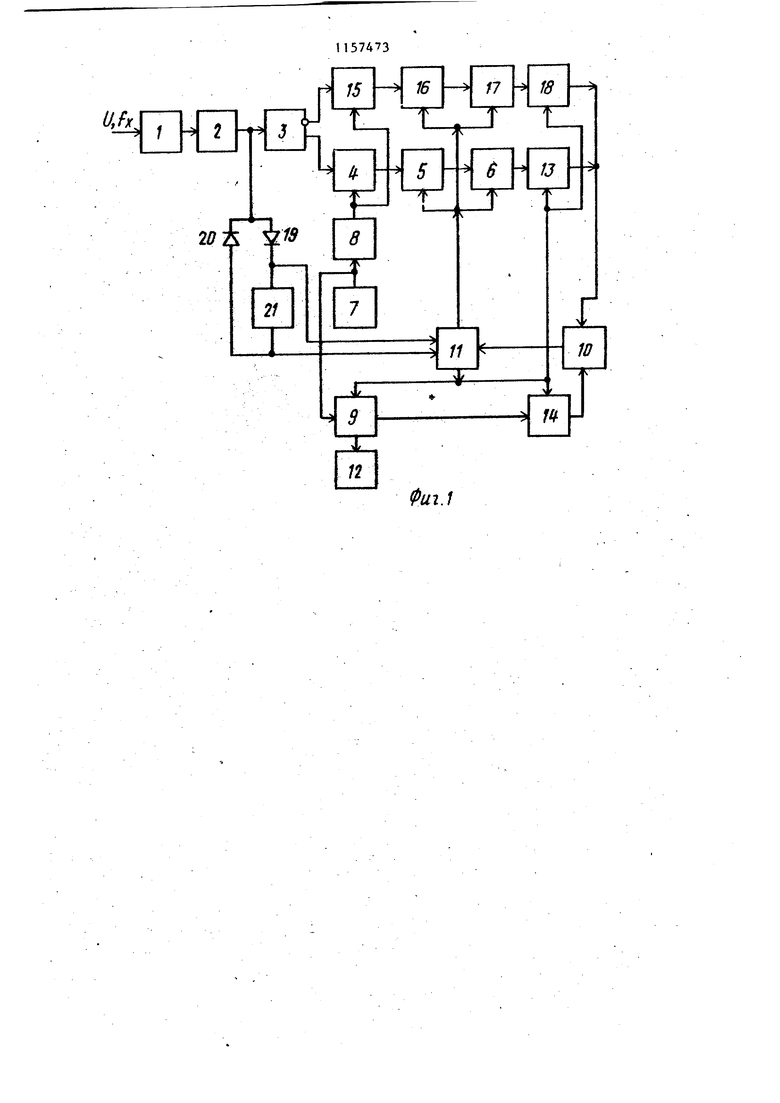

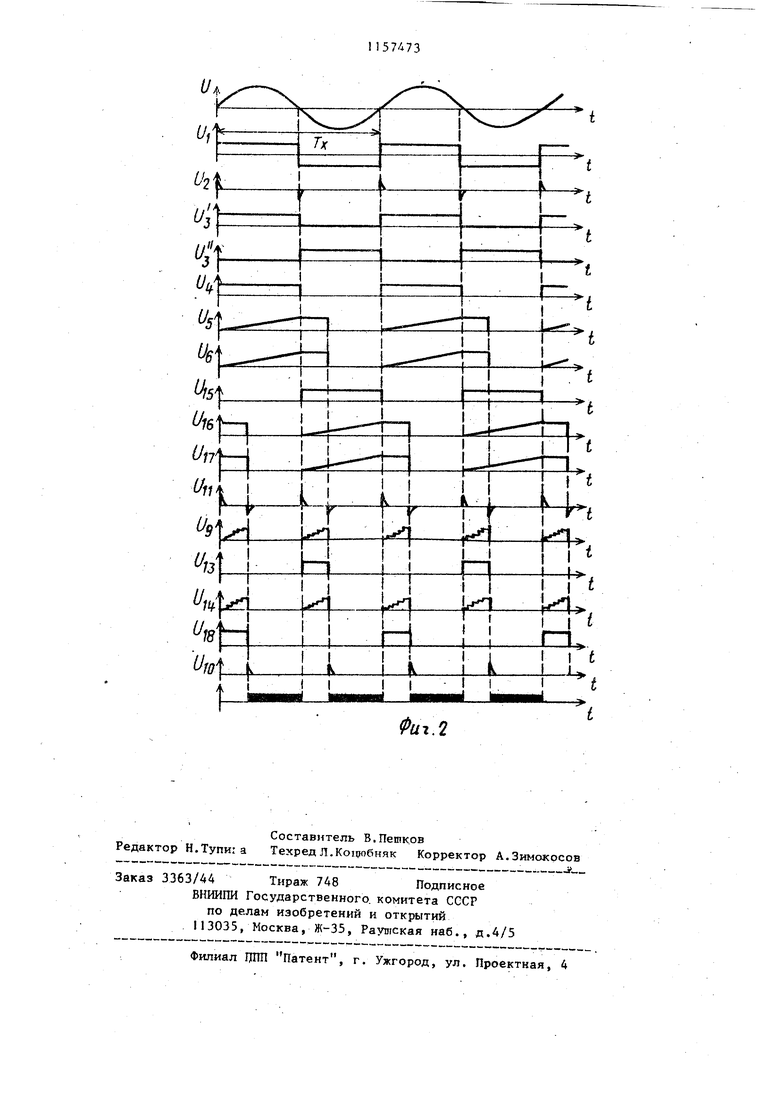

I Изобретение относится к цифровым частотомерам инфранизкой частоты и может быть использовано при исследо вании, наладке и настройке автомати ческих систем управления и их отдел ных звеньев. . Известно устройство преобразования измеряемой частоты в пропорциональное напряжение постоянного тока содержащее последовательно соединен ные формирователь входного сигнала, блок дозирования и фильтр 1. Недостатком данного устройства является низкое быстродействие. Наиболее близким к изобретению Авляется измеритель инфранизкой час тоты, содержащий усилитель-ограничи тель, дифференцирующую цепь, тригге три селектора, интегратор, аналоговую ячейку памяти, источник опорног напряжения, делитель напряжения, дискретный делитель напряжения, блок сравнения, блок управления и узел индикации, причем усилительограничитель, дифференцирующая цепь и триггер соединены последовательно, выход триггера соединен с управляющим входом первого селектора, выход источника опорного напряжения подключен непосредственно к первому входу дискретного делителя напряжения и через делитель напряжения и первый селектор к входу интегратора, выход которого соедине с входом аналоговой ячейки памяти, первый выход дискретного делителя напряжения соединен с узлом индикации, а второй выход через второй селектор соединен с первым входом блока сравнения, к второму входу которого через третий селектор подключен выход аналоговой ячейки памяти, выход блока сравнения .подключен к третьему входу блока управ ления, первый выход которого соединен с вторым входом дискретного делителя напряжения и с управляющим входами второго и третьего селекторов, второй выход блока управления соединен с обнуляющими входами инте ратора и аналоговой ячейки памятиС2 Однако в известном измерителе формирование информации о значении измеряемой частоты происходит тольк в положительные полупериоды исследу мого сигнала, т.е. быстродействие ограничено одним измерением в период, а максимальное время получе ния первоначального значения измеря 732 емой частоты равно периоду исследуемого сигнала и при инфранизких частотах достигает больших значений. Эти недостатки ограничивают применение известного измерителя инфранизкой частоты при исследовании и наладке автоматических систем с,переменными параметрами. Цель изобретения - повышение быстродействия за счет уменьшения в два раза времени получения первоначальной информации об измеряемой частоте и увеличения в два раза быстродействия измерения переменной частоты. Поставленная цель достигается тем, что в измеритель инфранизкой частоты, содержащий последовательно соединенные усилитель-ограничитель, дифференцирующую цепь и риггер, а также три селектора, интегратор, аналоговую ячейку памяти, источник опорного напряжения, делитель напряжения, дискретный делитель напряжения, блок сравнения, блок управления и узел индикации, выход триггера соединен с управляющим входом первого селектора, выход источника опорного напряжения подключен непосредственно к первому входу дискретного делителя напряжения и череэ делитель напряжения и первый селекто к входу интегратора, выход которого соединен с входом аналоговой ячейки памяти, первый выход дискретного делителя напряжения соединен с входом узла индикации, а второй выход через второй селектор - с первым входом блока сравнения, к второму входу которого через третий селектор подключен выход аналоговой ячейки памяти, выход блока сравнения подключен к первому входу блока управ-, ления, первый выход которого соединен с вторым входом дискретного делителя напряжения и с управлякйцими входами второго и третьего селекторов , второй выход блока управления соединен с обнуляющими входами интегратора и аналоговой ячейки памяти, введены два дополнительных селектор1а, дополнительные интегратор и аналоговая ячейка памяти, два диода и инвертор, причем первый вход первого дополнительного селектора подключен к инверсному выходу триг гера, второй вход - к выходу делителя напряжения, а выход - к входу дополнительного интегратора, выход 3 которого соединен с входом дополнительной аналоговой ячейки памяти, выход которой через второй дополнител ьный селектор подключен к втором входу блока сравнения, управляющий вход второго дополнительного селектора соединен с первьгм выходом блок управления, второй выход блока упра ления соединен с обнуляющими входам дополнительных интегратора и аналог вой ячейки памяти, анод первого и катод второго диода объединены и подключены к выходу дифференцирующе цепи, катод первого диода через инвертор объединен с анодом второго диода и подключены к второму входу блока управления, к третьему входу которого подключен .катод первого диода. На. фиг. I представлена функциональная схема устройства; на фиг.2 временные диаграммы работы. Измеритель инфранизкой частоты содержит усилитель-ограничитель 1, дифференцирук в(ую цепь 2, триггер 3 селектор 4, интегратор 5, аналоговую ячейку 6 памяти, источник 7 опорного напряжения, делитель 8 напряжения, дискретный делитель 9 напряжения , блок 10 сравнения, блок П управления, узел 12 индикации, селекторы 3 и 14, дополнительные: селектор 15, интегратор 16, аналого вая ячейка 17 памяти и селектор 8, а также два диода 19 и 20 и инвертор 21. Блоки 1 - 3 соединены последовательно, прямой выход триггера 3 соединен с управляющим входом пер вого селектора 4, выход источника 7 опорного напряжения подключен к первому входу дискретного делителя 9 и череэ делитель 8 и первый селе тор 4 к входу интегратора 5, выход которого соединен с входом аналоговой ячейки 6, выходы дискретного делителя 9 соединены с узлом I2 и через второй селектор 14 с блоком 10, к второму входу которого через третий селектор I8 подключен выход аналоговой ячейки 6, выход блока 10 подключен к первому входу блока II, первый выход которого соединен с вторым входом дискретного делителя 9 и с управляющими входами селекторов 13 и 14, второй выход блока И соединен с обнуляющими входами интегратора 5 и аналоговой ячейки 6 управляю1зий вход дополнительного селектора 15 подключен к инверсному 34 выходу триггера 3, второй вход - к выходу делителя 8 напряжения, выход - к входу дополнительного интегратора 16. выход .которого соединен с входом Дополнительной аналоговой ячейки 17 памяти, выход которой через дополнительный селектор 18 подключен к второму входу блока 10 сравнения, управляющий вход дополнительного . селектора 18 соединен с первым выходом блока 11 управления, второй выход которого соединен с обнуляющими входами дополнительных интегратора 16 и аналоговой ячейки 17 памяти, анод диода 19 и катод диода 20 объединены и подключены к выходу ; дифференцирующей цепи 2, катод диода 19 через инвертор 21 объединен с анодом диода 20 и подключены к первому входу блока 11 управления, к второму входу которого подключен катод диода 19. Устройство работает следующим образом. Напряжение U измеряемой частоты f преобразуется в усилителе-ограничителе 1 в напряжение U., прямоугольной формы. Дифференцирукщая цепь 2 формирует положительные и отрицательные импульсы Uj, управляющие работой триггера 3 и блока I управления (фиг. 2). Триггер 3 формирует на прямом и инверсном выходах сдвинутые один относительно другого по времени на т строб-импульсы Uj и и длительТГностью -Х-, где Т -г- - период ис ) следуемого сигнала. На время действия строб-импульса 0 открывается селектор 4, а на время действия строб-импульса и - селектор 15. В результате селекторы 4 и 15 открываются поочередно первый - на время длительности положительного полупериода напряжения U измеряемой частоты, второй - на время длительности его отрицательного полупериода. При открытых селекторах 4 и 15 на входы интеграторов 5 и 16 через делитель 8 напряжения подается стабильное напряжение V источника 7 опорного напряжения. На выходе интеграторов 5 и 16 формируются напряжения коэффициент передачи интеграторов 5 и 16; - коэффициент деления делителя 8, Эти напряжения запоминаются аналоговыми ячейками 6 и 17 памяти, т.е. на выходе ячейки 6 памяти напряжение (- равно напряжению на выходе интегратора 5 ((. -Is « я на выходе ячейки 17 памяти напряжение Ц равно напряжению на выходе интегратора 16 (U - 0 ) . Управление процессом уравновешивания напряжений U и ,напряжением дискретного делителя 9.напряжения осуществляется блоком II управления При поступлении отрицательного и пульса Uj , сигнализирующего об окончании строб-импульса U, , с выхода дифференцирующей цепи 2 чере диод 20 на первый вход блока 1 управления, последний открывает сел торы 13 и 14 и подает команду на дискретный делитель 9 напряжения, п которой в блоке 10 сравнения начина ется процесс уравновешивания напряжения Ug . При открытых селекторах 13 и 14 на один вход блока 10 сравнения поступает напряжение (J с яче ки 6 памяти, а на другой вход - напряжение с дискретного делителя 9 напряжения , коэффициент деления дели теля 9 напряжения. При наступлении равенства блок 10 сравнения вьдает сигнал на третий вход блока 1 управления. По этому сигналу блок II управлени вьщает команду на дискретный делитель 9 напряжения для прекращения процесса уравновешивания напряжени U; и обнуляет выходы интегратора 5 и аналоговой ячейки 6 памяти, готовя их тем самым к работе в следующем цикле. Положительный импульс U, сигнал зирующий об окончании строб-импуль и, , с выхода дифференцирующей це 2 поступает через диод 19 на второ вход блока I1 управ ения и одновре менно на вход инвертора 21. В инве торе 21 положительный импульс прео разуется в отрицательный импульс, который поступает на первый вход блока 11 управления. При одновременной подаче отрицательного импульса на первый вход и положительного импупьса на второй вход блока 11 управления, в нем вырабатывается сигнал, который открьтает селекторы 18 и 1А и подает команду на дискретньгй делитель 9 напряжения, по которой в блоке 10 сравнения начинается процесс уравновешивания чапряжения U,. напряжением t9 делителя 9 напряжения. При наступлении равенства и, из блок to сравнения вьдает сигнал на третий вход блока П управления, который вырабатывает команду на дискретный делитель 9 напряжения для прекращени.; процесса уравновешивания напряжения (}„ и обнуляет на этот раз выходы интегратора 16 и аналоговой ячейки 17 памяти, готовя их тем самым к работе в следукицем цикле, Из равенства напряжений U.Uj-17 9 КЛо ААН откуда следует, что частота г ДДН k пропорциональна коэффициенту. Адн дискретного делителя 9 напряжения. Значение коэффициента Кд.„ в виде кода поступает на узел 12 индикации, который индицирует значение измеряемой частоты f . Таким образом, введение двух селекторов, интегратора, аналоговой ячейки памяти, двух диодов и инвертора обеспечивает выработку информации о значении измеряемой частоты в каждый полупериод исследуемого сигнала, а следовательно, увеличение быстродействия измерителя в два раза и, что особенно важно, уменьшает максимальное время пол -чения первого значения измеряемой частоты от одного периода до половины периода исследуемого сигнала после подачи его на вход. Создание предлагаемого измерителя инфранизкой частоты на базе известного измерителя не представляет сложности и не требует больших экономических затрат.

| название | год | авторы | номер документа |

|---|---|---|---|

| Измеритель инфранизкой частоты | 1979 |

|

SU866492A1 |

| Цифровой инфранизкочастотный измеритель разности фаз | 1981 |

|

SU1010571A1 |

| Устройство для измерения напряжения инфранизкой частоты | 1989 |

|

SU1673997A1 |

| Способ управления процессом обработки | 1986 |

|

SU1437168A1 |

| Измеритель коэффициента нелинейных искажений | 1976 |

|

SU567147A1 |

| УСТРОЙСТВО АКТИВНОЙ ЗАЩИТЫ И ОБЕСПЕЧЕНИЯ ТЕХНИЧЕСКОЙ ГОТОВНОСТИ ЭЛЕМЕНТОВ РАСПРЕДЕЛЕННОЙ ЛОКАЛЬНОЙ ВЫЧИСЛИТЕЛЬНОЙ СЕТИ В УСЛОВИЯХ ВНЕШНИХ ДЕСТРУКТИВНЫХ ВОЗДЕЙСТВИЙ | 2006 |

|

RU2316810C2 |

| Устройство для определения временного положения импульсных сигналов | 1984 |

|

SU1206829A2 |

| АНАЛИЗАТОР ПАРАМЕТРИЧЕСКИХ ОТКАЗОВ И СБОЕВ | 2004 |

|

RU2270470C2 |

| Цифровой измеритель частоты заполнения радиоимпульсов | 1981 |

|

SU945819A1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

ИЗМЕРИТЕЛЬ ИНФРАНИЗКОЙ ЧАС-. ТОТЫ, содержащий последовательно соединенные усилитель-ограничитель, дифференцирующую цепь и триггер, а также три селектора, интегратор, аналоговую ячейку памяти, источник опорного напряжения, целитель напря-жейия, дискретньй делитель напряжения, блок сравнения, блок управления и узел индикации, выход триггера соединен с управляющим входом первого селектора. Выход источника опорного напряжения подключен непосредственно к первому входу дискретного делителя напряжения и через делитель напряжения и первый селектор к входу интегратора, выход, которого соединен с входом аналоговой ячейки памяти, первый выход дискрет ного делителя напряжения соединен с входом узла индикации, а второй выход через второй селектор - с первым входом блока сравнения, к второму входу которого через третий certeKTop подключен выход аналоговой ячейки памяти, выход блока сравнения подключен к первому входу блока управления, первый выход которого соединен с вторым входом дискретного делителя напряжения и с управляю щими входами второго и третьего селекторов, а второй выход блока управления соединен с обнуляющими входами интегратора и аналоговой ячейки памяти, отличающийс я тем, что, с целью повышения быстродействия, в него введены два дополнительных селектора, дополнительные интегратор и аналоговая ячейка памяти, два диода и инвертор, причем первый вход первого дополнительного селектора подключен к инверсному выходу триггера, второй (Л вход - к выходу.делителя напряжения, а выход - к входу дополнительного интегратора, выход которого соединен с входом дополнительной аналоговой ячейки памяти, выход которой через второй дополнительный селектор подключен к второму входу блока сравнения, управляющий вход второго СП дополнительного селектора соединен с первым выходом блока управления, s| второй выход блока управления соеди4 1 нен с обнуляющими входами дополнитель ных интегратора и аналоговой ячейки СО памяти, анод первого и катод второго диода объединены и подключены к выходу дифференцирующей цепи, катод первого диода через инвертор об1 единен с анодом второго диода и подключены к второму входу блока управле- . ния, к третьему входу которого подключен катод-первого диода.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Баранов Л .А | |||

| и др | |||

| Конденсаторные преобразователи в автоматике и системах управления | |||

| М.,Энергия, 1969, с | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| I, 2 | |||

| Измеритель инфранизкой частоты | 1979 |

|

SU866492A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-05-23—Публикация

1983-05-05—Подача