/одноименного разряда входного кода устройства, инверсные входы разрядов входного кода которого соединены с вторыми входами элементов И первой группы и с первыми входами одноименных элементов И остальных групп, выходы элементов ИЛИ каждой i-й группы (i 1п-1) соединены с входами одноименных- элементов НЕ первой группы i-ro блока выделения старшего разряда группы, выходы элементов И первой группы каждого блока выделения старшего разряда группы соединены с входами одноименного шифратора группы, группа выходов каждого шифратора группы является соответствующей группой выходов устройства, выход каждого элемента И второй группы каждого

64707

i-ro блока выделения старшего раз. ряда группы (i 1,...,п-1) соединен с первым входом одноименного элемента ИЛИ (1+1)-й группы, выход элемента ИЛИ-НЕ i-ro (,..,,п) блока выделения старшего разряда группы соединен с вторыми входами элементов И (i+1)-ft группы, выход первого элемента И i-й группы (i 2,...,п) соединен с входом первого элемента НЕ первой группы (i+1)-ro блока выделения старшего разряда группы, выход i-го элемента И (,...,п) j-й группы (J 1,.,.,п-1) соединен с вторым входом 1-го элемента ИЛИ j-й группы, выход элемента ИЛИ является сигнальным выходом устройст - ва.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения старшего значащего разряда | 1985 |

|

SU1260957A2 |

| Устройство для определения старшего значащего разряда | 1983 |

|

SU1137469A2 |

| Устройство для выделения значащих разрядов из последовательности многоразрядных двоичных кодов | 1982 |

|

SU1038935A1 |

| Устройство для определения старшего значащего разряда | 1980 |

|

SU1067501A1 |

| Устройство ассоциативного кодирования и объемного сжатия информации | 1987 |

|

SU1441484A1 |

| Устройство для сортировки чисел | 1986 |

|

SU1310803A1 |

| Устройство для определения старшего значащего разряда | 1986 |

|

SU1310822A1 |

| Устройство для определения старшего значащего разряда | 1984 |

|

SU1252778A2 |

| Устройство для упорядочивания @ чисел | 1986 |

|

SU1339548A1 |

| Цифровое логарифмирующее устройство | 1985 |

|

SU1262490A1 |

УСТРОЙСТВО ДЛЯ ОПРВДЕПЕНИЯ СТАРШЕГО ЗНАЧАЩЕГО РАЗРЯДА, содержащее группу из п блоков вьзделения старшего разряда (п - число . разрядов входного кода), причем каяфзый блок выделения старшего разряда группы содержит две ; группы элементов И, две группы элементов НЕ, группу элементов И-НЕ, причем в каждом блоке вьщеления старшего разряда группы первый вход каждого i-ro элемента И-НЕ группы

1

Изобретение относится к вычислительной технике, может быть использовано в цифровых вычислительных устройствах, а также в устройствах приема и передачи информации.

Известно устройство для определения старшего з.начащего разряда, содержащее п-разрядный регистр,, ri-1 элементов И-НЕ, п-1 элементов И и п-2 элементов НЕ lj .

Недостаток известного устройства - ограниченные функциональные возможности.

. Наиболее близким техническим решением к изобретению является устройство для определения старшего значащего разряда, содержащее п-разрядный регистр, п-1 элементов И-НЕ, две группы элементов И по п-Т элемент в каждой, п-1 элемент НЕ и элемент ИЛИ, прямой выход первого разряда регистра .соединен с первой выходной шиной, инверсный выход первого разряда регистра соединен с первым входом первого элемента И первой группы инверсньА выход каждого i-ro разряда регистра (1 2,3,...,п) соединен с первым входом (i-l)-ro элемента И-НЕ, выход каждого j-го элемента И-НЕ

(j 1,2,...,п-2) подключен через j-и элемент НЕ к первому входу (j+1)-ro элемента И первой группы, выход каждого К-го элемента И соединен с (К+1)-й шиной первых выходньгх шин, выход каждого j-ro элемента И-НЕ соединен с вторым входом j-ro элемента И, выход Р-го элемента НЕ, где Р 1,2,...,п-2, подключен.к второму вхоДу (Р+1)-го элемелта И-НЕ; инверсный выход первого разряда регистра соединен с вторым входом первого элемента И-НЕ, выход (п-1)-го элементна И-НЕ подключен к второму входу (п-1)-го элемента И, первый вход К-го элемента И второй группы (К 1,...,п-1) подключен к прямому вьгх:оду (К+1)-го разряда п-разрядного регистра, второй вход т-г.о элемента И (т 2,...,

п-1) второй группы подключен к выходу (m-l)-ro элемента И-НЕ, а выход К-го элемента И второй группы подключен к К-му входу элемента ИЛИ,

выход которого является вторым выходом устройства, прямой выход первого разряда п-разрядног,о регистра подключен квторому входу первого элемента И второй группы, вход п-го элемента НЕ подключен к выходу (n-l)-ro элемента И-НЕ, а вьгход по ключей к выходу устройства 2j. Однако и данное устройство имее ограниченные функциональные возмож .ности, так как не решает задачу одновременной шифрации единиц и нулей в п-разрядном двоичном коде. Целью изобретения является распшрение функциональных возможностей за счет одновременной шифрации единиц и нулей входного кода Поставленная цель достигается тем, что в устройство для определения старшего значащего разряда, содержащее группу из п блоков выделения старшего разряда, (п число разрядов входного кода), причем.каждый блок выделения старш го, разряда группы содержит две гру пы элементов И, две группы злементов НЕ и группу элементов И-НЕ,при чем в каждом блоке вьщеления старщего разряда группы первый вход каждого i-ro элемента И-НЕ группы (i 2,...,п) соединен с вькодом (i-H)-ro элемента НЕ первой группы первый и второй входы первого элемента И-НЕ группы соединены с выходами соответственно первого и второгр элементов НЕ первой группы вьпсод i-ro элемента И-НЕ группы (i 1,...,п) через i-й элемент НЕ второй группы соединен с вторым входом (i+t)-ro элемента И-НЕ груп пы, выход i-ro элемента НЕ второй группы (i 1,...,п-1) соединен с первым входом i-ro элемента И первой группы (i 2,...,п), первый вход первого элемента И первой группы соединен с выходом первого элемента НЕ первой группы, вторые входы элементов И первой группы соединены с выходами одноименных элементов И-НЕ группы, первый и второй входы первого элемента И второй группы соединены соответственно с входом первого элемента НЕ первой группы и с входом вто рого элемента НЕ цервой группы, первый вход каждого К-го элемента И второй группы (к 2,...,п) соединен с входом L-ro элемента НЕ первой группы (L 3,...,nJ, второй вход каждого К-го элемента И второй группы соединен с выходом i-ro элемента И-НЕ группы (i 1, ...,п), введены элемент ИЛИ, элемент НЕ,п групп из п элементов И, 074 п групп элементов ИЛИ и группу из п шифраторов, причем каждая группа элементов ИЛИ, кроме первой содер- жит элементов ИЛИ, первая группа элементов ИЛИ содержит п элементов ИЛИ, в каждый блок вьделения старшего разряда группы введен элемент ИЛИ-НЕ, входы которого соединены с выходами элеменов И второй группы своего блока выделения старшего разряда группы, прямые входы разрядов входного кода устройства соединены с входами элемента ИЛИ, выход которого через элемент НЕ соединен с первыми входами элементов И первой группы, выходы которых соединены с первыми входами одноименных элементов ИЛИ первой группы, второй вход каждого из ко- торых соединен с прямым входом одноименного разряда входного кода устройства, инверсные входы разрядов входного кода которого соединены с вторыми входами элементов И первой группы и с первыми входами одноименных элементов И остальных групп, выходы элементов ИЛИ казкдой i-й группы (i 1,...,п-1) соединены с входами одноименных элементов НЕ первой группы i-ro блока выделения старшего разряда группы, выходы элементов И.первой группы каждого блока вьщеления старшего разряда группы соединены с входами одноименного шифратора группы, группа выходов каждого шифратора является соответствующей группой выходов устройства, выход каждого элемента И второй группы каждого i-ro блока выделения старшего разряда (i 1,...,п-1) группы соединен с первым входом одноименного элемента ИЛИ (i+1)-й группы, выход элемента ИЛИ-НЕ i-ro (i 1,...,п) блока ььщеления. старшего разряда группы соединен с вторыми входами элементов И (i+1)-й группы, выход первого элемента И i-й группы (i 2,...,п) соединен с входом первого элемента НЕ первой группы (i+1)-ro блока вьщеления старшего разряда группы, выход i-rb элемента И (i 2,...,п) j-й группы (jsil,... ,п-1) соединен с вторым входом i-ro элемента ИЛИ j-ой группы , выход элемента ИЛИ является сигнальным выходом устройст ва.

5

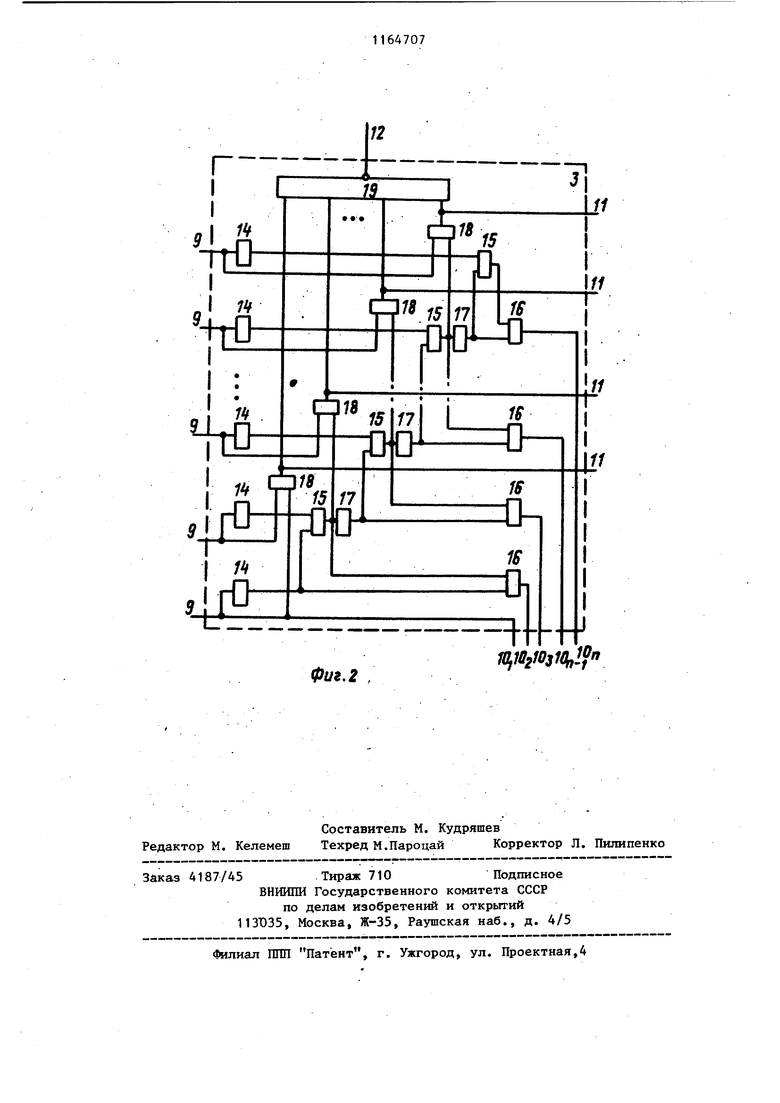

На фиг.1 приведена структурная схема устройства; на фиг.2 --то же, блок выделения старшего разряда.

Устройство содержит элемент РШИ элемент НЕ 2, блоки 3,-3 вьщеления старшего разряда, группы элементов ИЛИ 4, группь элементов И 5, сигнальный выход 6 устройства, прямые и инверсные разряды 7 входного кода, шифраторы , выходы, 9 элементов ИЛИ 4, выходы 10,-IOn, 11 и 12, блоков 3, выходы 13 устройства. Блок.З (фиг.2) содержит элементы НЕ 1,4, элементы И-НЕ 15, элементы И 16, элементы НЕ 17, элементы И 18, элемент ИЛИ-НЕ 19. Устройство работает следующим образом.

Прямые и инверсные выходы разрядов анализируемого двоичного кода А подаются на входы 7 устройства. Возможны три случая: во всех разрядах кода записаны нули, во всех разрядах кода записаны единиць и количество разрядов, в которые записаны единицы, меньше п..

В первом случае на выходе элемента ИЛИ 1 нулевой потенциал, на вторых входах элементов И 5 первой группы разрешающий потенциа Инверсный анализируемый код А через открытые элементы И 5, элементы ИЛИ 4 поступает на входы 9 блок 3 выделения старшего разряда. В блоке 3 вьщеляется старший значащи разряд. Сигнал, равный единице,будет на выходе 10|, так как на всех входах 9 присутствуют единицы, а н всех остальных выходах 10 должен быть нуль.

На выходах 13 шифратора 8 буде двоичньй код, соответствутощий номеру старшего разряда (в данном случае ... 001). С выходов 11 анали3HpyeNibrti код А с исключенной старшей единицей поступает на следуюпщй блок 3. вьщеления старшего разряда через элементы ИЛИ 4 второй группы. Нулгзой сигнал на выходе 12 блока 3 выделения старшего разряда будет в случае, если количество единиц на входах 9 данного блока более одной. Следовательно, в данном случае на выходе 12 блока 3, нулевой сигнал, а на элементах И 5 второй группы запрещающий потенциал. В следующем блоке

3„.у выделения- старшего разряда выI деляется старший значащий разряд из остатка анализируемого кода определяется условие -. количество единиц

5 больше одной или меньше, исключа- . ется старший значащий .разряд. Сигнал единицы будет на,выходе lOj, на выходе 12. На выходе шифратора 8. двоичный код номера разряда (...010). Далее, схема работает аналогично.

На выходах шифраторов 8. -8 j будут последовательно расположенные двоичные коды номеров разря5

дов анализируемого кода, находящихся в нуле (...001,...010...011, ...111).

Во втором случае, когда во всех разрядах анализируемого кода запиW саны единицы, на выходе элемента ИЛИ 1 будет единичный потенциал, а на вторых входах элементов И 5 первой группы - запрещающий потенциал. Прямой код А через элементы

. РШИ поступает на входы 9 блока 3, вьщёления старшегоразряда. Дальнейшая работа устройства аналогична описанной в первом случае. На выходах шифраторов 8,-8р, будут

30 последовательно расположенные двоич,ные коды номе.ров разрядов анализируемого кода, находящихся в единице (...000,...010,...011...111).

. В третьем случае, когда в К разрядов анализируемого кода записа ны единицы, на выходе элемента HJIHI будет единичный потенциал, а на вторых входах элементов И первой группы - запрещающий потенциал. Прямой анализируемый код А через элементы. ИЛИ поступает, на вход 9 блока 3.

В блоке 3 вьщеляется старший значащий разряд, в котором записана единица. С выходов 11 передается на следующий блок 3,| анализируемый код А с исключенной старшей единицей. Единичный сигнал будет на выходе 10, -номер которого соотS ветствует номеру разряда, в который была записана старшая единица, а на выходе шифратора г соответствующий ему двоичный код. На выходах 10 К-го блока 3 выделения

старшего разряда будет единичный сигнал, соответствующий номеру разряда-, в которьй была записаиа последняя единица, а на выходе шифратора 8j - соответствующий ему даоичный код. На выходе 12 блока Зх единичный потенциал, так как на входы 9 этого блока поступил код, в котором единица, записана только в одном разряде, на вторых входах элементов И 5 разрешающий потенциал. На входы 9 блока 3 , через открытые элементы И 5, элементы ИЛИ А поступит инверсный анализируемый код А. Единичный сигнал будет на выходе 10, номер которого соответствует номеру старшего разряда кода А, в котором записан нуль, а на выходе шифратора 8 . - соответствукнций ему двончньтй код. Далее схема работает аналогично рпи санному в первом случае. На выходах шифратора 8;|-8 ц будут последовательно расположенные двоичные коды номеров разрядов, в которых записаны единицы, а на выходах шифраторов . 8к.. -8„ - номера разрядов, нахоадщихся в нуле.

Блок 3 выделения старшего разряда работает следующим образом.

Анализируемый код поступает на входы 9. Элементы И-НЕ 15, НЕ 17 и И 16 служат для выделения старшего значащего разряда, поступившего на входы 9, Схема распределяет потенциалы таким образом, что единицы

078

старшего разряда, распространяясь на значащие младшие разряды, запрещают прохождение сигналов значащих цифр на выходы 10 младших разрядов блока независимо от того, какое число записано в пределах разрядности. Сигнал, равный единице, будет на том выходе 10, номер которого соответствует входу 9, на котором

присутствует старшая единица,на всех остальных выходах 10 должен быть нуль независимо от состояний остальных входов 9. .

Когда число единиц в анализируемом коде больше одной, сигнал равный нулю, будет на выходе элемен-та ИЛИ-НЕ и выходе 12. Единица старшего разряда кода, распространяясь по цепочке элементов И-НЕ 15 и элементов НЕ 17, дает разрешение на одни входы элементов И 18, другие входь которьк подключены к входам блока 9 младших разрядов. Единица любого младшего разряда через элемент И 18, элемент ИЛИ-НЕ поступает на выход 12, а на выходы VI разряды анализируемого кода с исключенной старшей единицей.

Применение изобретения .позволяет расширить функциональные возмож-; ности устройства. .

rOnJt

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения старшего значащего разряда | 1978 |

|

SU723573A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское | |||

| Устройство для определения старшего значащего разряда | 1980 |

|

SU898432A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| : | |||

Авторы

Даты

1985-06-30—Публикация

1983-07-06—Подача