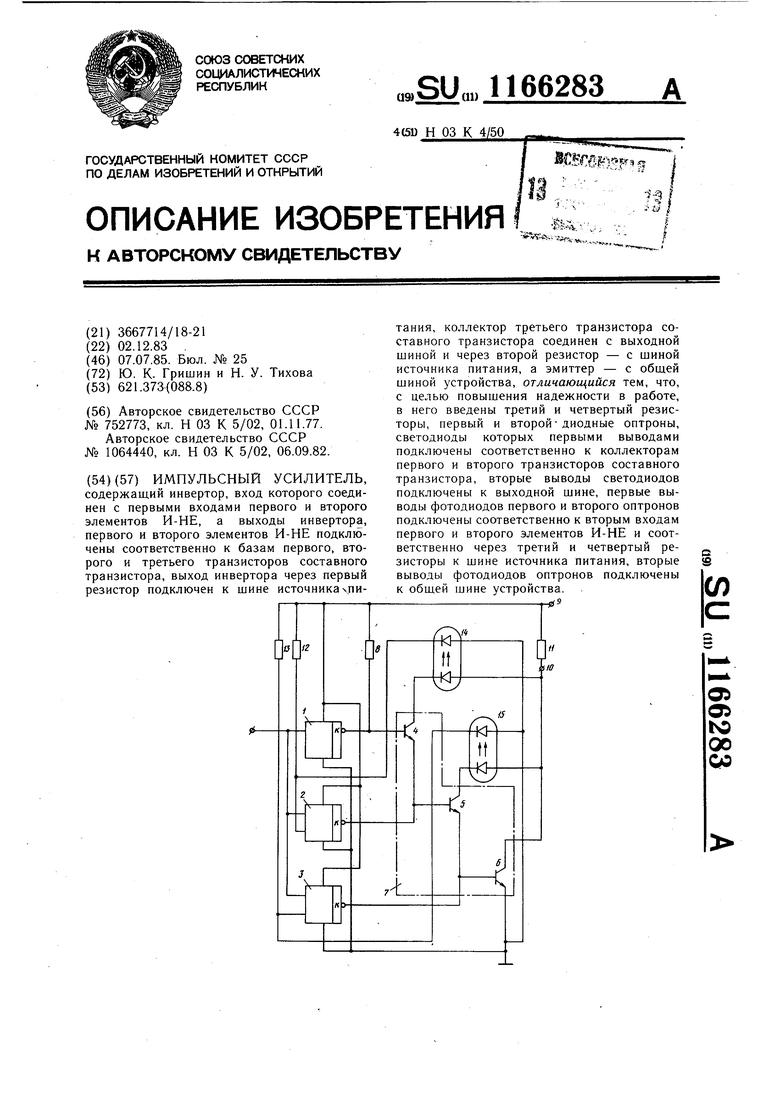

Изобретение относится к импульсной технике и может быть использовано в усилителях, работающих в ключевом режиме. Целью изобретения является повышение надежности работы. На чертеже представлена принципиальная электрическая схема импульсного усилител я. Импульсный усилитель содержит инвертор 1, вход которого соединен с первыми входами первого 2 и второго 3 элементов И-НЕ, выходы инвертора 1 первого 2 и второго 3 элементов Й-НЕ подключены соответственно к базам первого 4, второго 5 и третьего 6 транзисторов составного транзистора 7, выход инвертора 1 через первый резистор 8 соединен с шиной 9 источника питания, коллектор третьего транзистора 6 соединен с выходной шиной 10 и через второй резистор 11 с шиной 9 источника питания, а эмиттер подключен к обшей шине, третий 12 и четвертый 13 резисторы, первый 14 и второй 15 диодные оптроны, светодиоды KOTOpbix первыми выводами подключены соответственно к коллекторам первого 4 и второго 5 транзисторов составного транзистора 7, вторые выводы светодиодов подключены к выходной шине 10, первые выводы фотодиодов первого 14 и второго 15 оптронов подключены соответственно к вторым входам первого 2 и второго 3 элементов И-НЕ и соответственно через третий 12 и четвертый 13 резисторы к шине 9 источника питания, вторые выводы фотодиодов оптронов 14 и 15 подключены к обш.ей шине устройства. Импульсный усилитель работает следуюшим образом. Если на вход импульсного усилителя поступает сигнал логического нуля, инвертор 1 и элементы И-НЕ 2 и 3 закрыты, через резистор 8 в базу транзистора 4 поступает ток, который обеспечивает открытое состояние транзистора 4, в результате чего открыты транзисторы 5 и 6, а через резистор 11 в выходной шине 10 протекает ток нагрузки (в это время закрытые элементы И-НЕ 2 и 3 исключают шунтирование базовых цепей транзисторов 5 и 6, обеспечивая при этом максимальный коэффициент усиления составного транзистора). Открытое соетояние транзисторов 4 и 5 обеспечивает протекание тока через светодиоды оптронов 14 и 15, в результате чего в цепях фотодиодов этих оптронов также протекает ток от шины 9 питания через резисторы 12 и 13. Величина сопротивлений резисторов 12 и 13 выбираются таким образом, чтобы фотодиоды оптронов 14 и 15 работали в вентильном режиме (т. е. в режиме генерации фото-ЭДС), поэтому при включенных транзисторах 4 и 5 на вторых входах элементов И-НЕ 2 и 3 присутствует потенциал, близкий к уровню логического «О {ниже уровня логического «О). При поступлении на вход импульсного усилителя логической единицы инвертор 1 включается и прекраш,ает поступление тока в базу транзистора 4, в результате чего транзистор 4 начинает выключаться. Несмотря на то, что на первом входе элемента И-НЕ 2 в это время присутствует уровень логической «1, элемент И-НЕ 2 по-прежнему выключен за счет наличия на его втором входе уровня логического «О, обусловленного работой фотодиода оптрона 14 в вентильном режиме. Уровень логического «О на втором входе элемента И-НЕ 2 присутствует до тех пор, пока полностью не выключается тралзистор 4, и в его коллекторной цепи, а значит, и в цепи светодиода оптрона 14 прекращается ток. После полного выключения транзистора 4 прекращается ток и в цепи фотодиода оптрона 14, в результате чего и на втором входе элемента И-НЕ 2 устанавливается уровень логической «1, что приводит к включению элемента И-НЕ 2 и шунтированию базовой цепи транзистора 5. После выключения транзистора 4 и элемента И-НЕ 2 прекращается поступление тока в базу тразистора 5, в результате чего транзистор 5 начинает выключаться. Несмотря на то, что на первом входе элемента И-НЕ 3 в это время уровень логической «1, элемент И-НЕ 3 по-прежнему выключен за счет наличия на его втором вхбде уровня логического «О, обусловленного работой фотодиода оптрона 15 в вентильном режиме. Уровень логического «О на втором входе элемента И-НЕ 3 будет до тех пор, пока полностью не выключится транзистор 5 и в его коллекторной цепи, а значит, и в цепи светодиода оптрона 15 прекратится ток. После полного выключения транзистора 5 прекращается ток и в цепи фотодиода оптрона 15, в результате чего и на втором входе элемента И-НЕ 3 устанавливается уровень логической «1, что приводит к включению элемента И-НЕ 3 и шунтированию базовой цепи транзистора 6. Транзистор 6 закрывается, и ток через резистор 11 и выходную шину 10 прекращается. Таким образом, в усилителе включение элемента И-НЕ 2 возможно только после полного выключения транзистора 4, а включение элемента И-НЕ 3 возможно только после полного выключения транзистора 5, что исключает возможность перегрузки элементов И-НЕ 2 и И-НЕ 3 сквозными токами при любых изменениях времени выключения транзисторов 4 и 5. При этом полностью исключается возможность работы транзисторов 5 и 6 с «оборванными базами. Предлагаемый импульсный усилитель может найти щирокое применение в усилительной технике, так как в отличие от известного исключение из него элементов задержки позволяет создать более технологичную схему усилителя, которая может быть 34

проще реализована в микроминиатюрном надежность работы усилителя при действии исполнении, например, в виде микросборки. дестабилизирующих факторов и в более При этом обеспечивается более высокая широком диапазоне частот.

1166283

| название | год | авторы | номер документа |

|---|---|---|---|

| Эмиттерный повторитель | 1985 |

|

SU1256149A1 |

| Транзисторный ключ | 1986 |

|

SU1378040A1 |

| Усилитель-инвертор | 1987 |

|

SU1429310A1 |

| Эмиттерный повторитель | 1983 |

|

SU1084967A1 |

| Оптоэлектронный ключ | 1978 |

|

SU790317A1 |

| ТРАНЗИСТОРНЫЙ КЛЮЧ (ВАРИАНТЫ) | 1994 |

|

RU2076441C1 |

| Устройство для передачи телеграфного сигнала | 1980 |

|

SU1202067A1 |

| Транзисторный ключ | 1985 |

|

SU1264332A2 |

| ОПТОЭЛЕКТРОННЫЙ КЛЮЧ | 1996 |

|

RU2134484C1 |

| Транзисторный ключ с защитой от перегрузки | 1986 |

|

SU1348993A1 |

ИМПУЛЬСНЫЙ УСИЛИТЕЛЬ, содержащий инвертор, вход которого соединен с первыми входами первого и второго элементов И-НЕ, а выходы инвертора, первого и второго элементов И-НЕ подключены соответственно к базам первого, второго и третьего транзисторов составного транзистора, выход инвертора через первый резистор подключен к шине источника питания, коллектор третьего транзистора составного транзистора соединен с выходной шиной и через второй резистор - с шиной источника питания, а эмиттер - с общей шиной устройства, отличающийся тем, что, с целью повышения надежности в работе, в него введены третий и четвертый резисторы, первый и второй- диодные оптроны, светодиоды которых первыми выводами подключены соответственно к коллекторам первого и второго транзисторов составного транзистора, вторые выводы светодиодов подключены к выходной шине, первые выводы фотодиодов первого и второго оптронов подключены соответственно к вторым входам первого и второго элементов И-НЕ и соответственно через третий и четвертый резисторы к шине источника питания, вторые выводы фотодиодов оптронов подключены к обшей шине устройства.

| Авторское свидетельство СССР № 752773, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Импульсный усилитель | 1982 |

|

SU1064440A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1985-07-07—Публикация

1983-12-02—Подача