и пятым входами канала контроля длительности, второй вход триггера 1167520 является третьим входом канала контроля длительности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля исправности систем импульсно-фазового управления преобразователей | 1983 |

|

SU1100708A1 |

| Устройство для диагностирования систем импульсно-фазового управления тиристорным преобразователем | 1988 |

|

SU1598031A1 |

| Устройство для контроля системы управления тиристорным преобразователем | 1983 |

|

SU1166214A1 |

| Многоканальный фазометр | 1989 |

|

SU1720028A1 |

| Устройство для измерения сдвига фаз | 1986 |

|

SU1465806A1 |

| Вибрационный источник сейсмических сигналов | 1985 |

|

SU1277034A1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ ВЛАЖНОСТИ | 2009 |

|

RU2399039C1 |

| Способ виброобработки конструкции для снижения остаточных напряжений и устройство для его осуществления | 1987 |

|

SU1421784A1 |

| Способ определения мгновенных значений фазового сдвига электрических сигналов | 1988 |

|

SU1559308A1 |

| Измеритель электропроводности | 1983 |

|

SU1149157A1 |

УСТРОЙСТВО КОНТРОЛЯ ИМПУЛЬС Н(Й1 ПОСЛЕДОВАТЕЛЬНОСТИ, содержащее генератор импульсов эталонной частоты, выход которого соединен с входом делителя частоты, блок индикации, канал контроля длительности импульсов, включающий в себя первый триггер и первый счетчик длительности импульсов, канал контроля частоты и периода, включающий в себя второй, третий и четвертый триггеры, отличающееся тем, что, с цепью расширения функциональных возможностей за счет обеспечения контроля фазового сдвига и амплитуды, а также возможности автоматического контроля параметров, в него введены блок управления, формирователь тестовых комбинаций, канал контроля фазового сдвига и канал контроля амплитуды, при этом вход делителя частоты соединен с входом формирователя тестовых комбинаций, выходы которого соединены с входами контролируемого блока, выходы которого являются входами блока управления, первые выходы которого соединены с первыми входами блока индикации, вторые входы которого соединены с выходами соответственно канала контроля частоты и периода, канала контроля амплитуды, канала контроля фазового сдвига и канала контроля длительности импульсов, первый вход которого соединен с первыми входами соответственно канала контроля частоты и периода, канала контроля фазового сдвига и с вторым выходом блока управления, третий выход которого соединен с первым входом канала контроля амплитуды и вторыми входами соответственно канала контроля длительности импульсов, канала контроля частоты .и периода и канала контроля фазового сдвига, четвертый выход блока управлеСД ния соединен с вторым вхрдом соответственно канала контроля амплитуды и третьим входом канала контроля фазового сдвига и с третьим и четвертым ; входам; канала- контроля длительности импульсов, пятый выход которого соединен с первь выходом канала контроля амплитуды, пятый выход блока отравления соединен с входом импульсного генератора эталонной частоты, второй вход блока управления соединен с входной шиной Контроль, выходы делителя частоты соединены соответственно с четверTbw входом канала контроля фазового сдвига и седьмым входом канала контроля длительности импульсов, содержащего первый формирователь импульсов, выход которого соединен с пер,вым входом первого триггера, а первый вход формирователя импульсов соединен с выходом первого элемента ИЛИ, первый и второй входы которого соединены соответственно с вторым

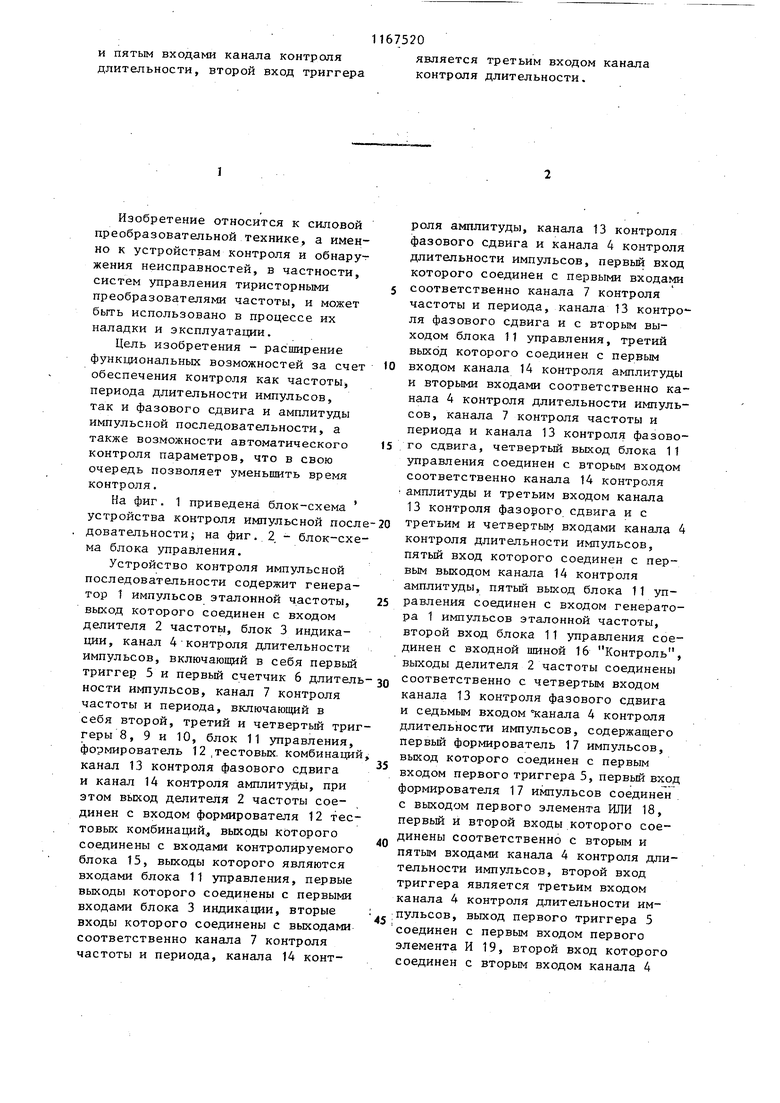

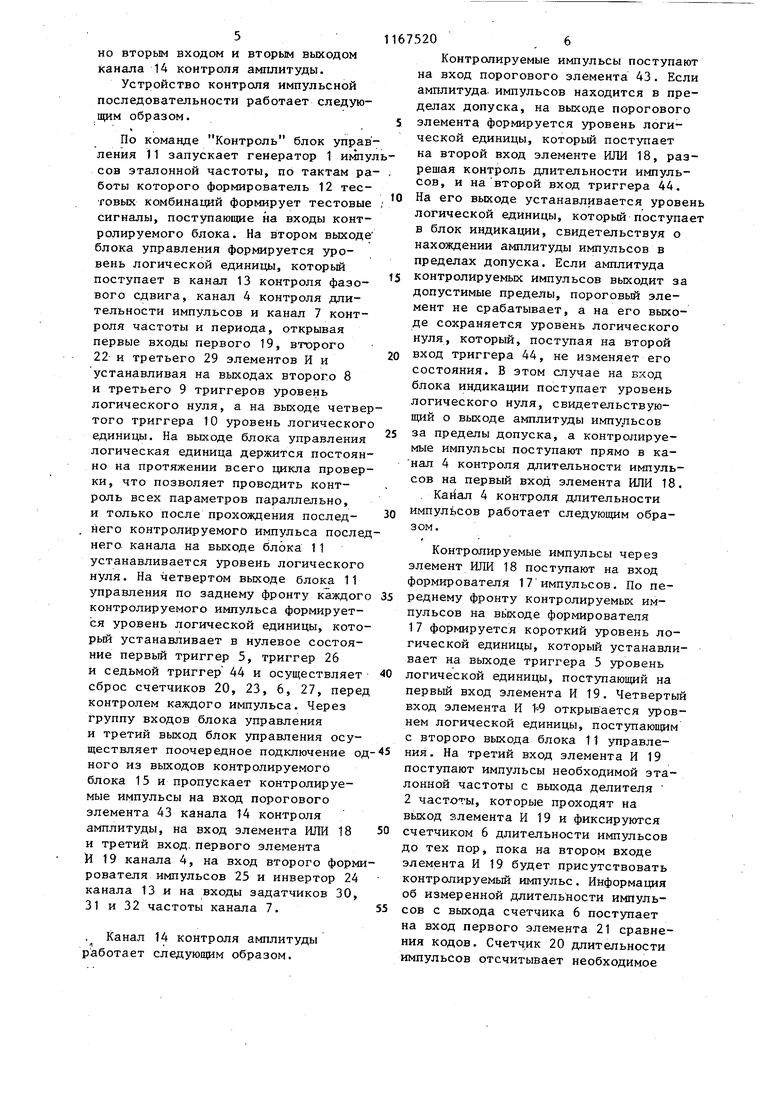

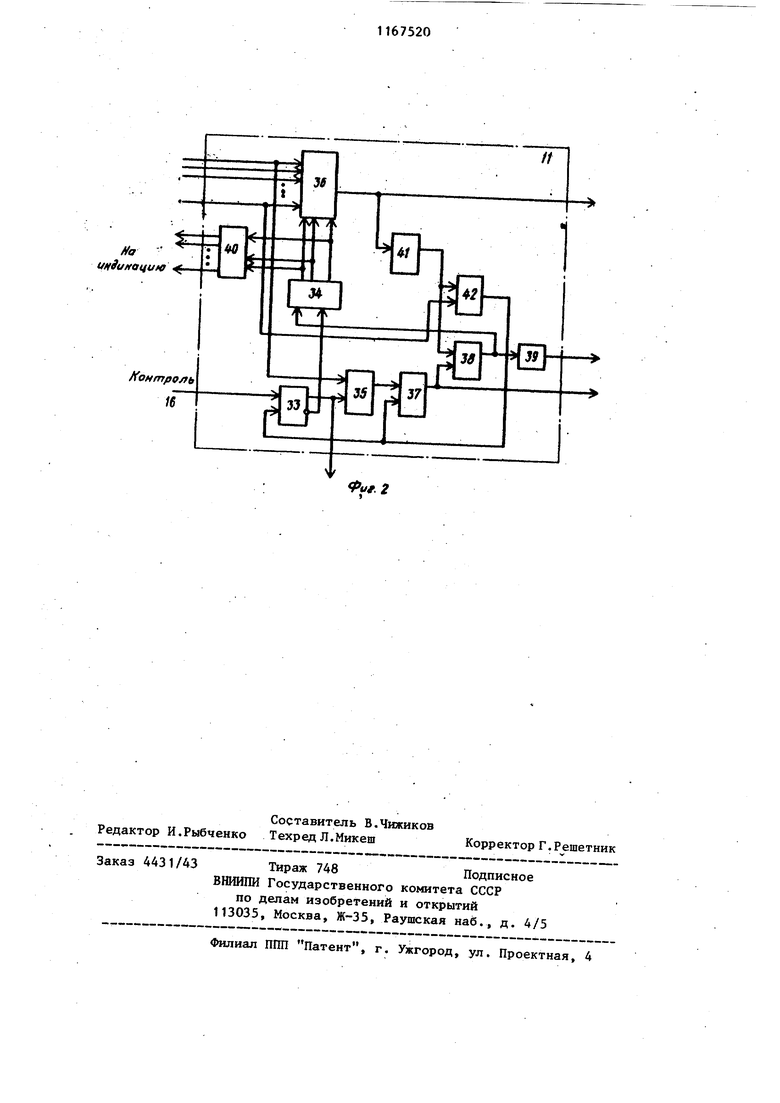

Изобретение относится к силовой преобразовательной технике, а именно к устройствам контроля и обнарут жения неисправностей, в частности, систем управления тиристорными преобразователями частоты, и может быть использовано в процессе их наладки и эксплуатации. Цель изобретения - расширение функциональных возможностей за счет обеспечения контроля как частоты периода длительности импульсов, так и фазового сдвига и амплитуды импульсной последовательности, а также возможности автоматического контроля параметров, что в свою очередь позволяет уменьшить время контроля. На фиг. 1 приведена блок-схема устройства контроля импульсной посл довательности; на фиг. 2 - блок-схе ма блока управления. Устройство контроля импульсной последовательности содержит генератор t импульсов эталонной частоты, выход которого соединен с входом делителя 2 частоты, блок 3 индикации, канал 4Контроля длительности импульсов, включающий в себя первый триггер 5 и первый счетчик 6 длител ности импульсов, канал 7 контроля частоты и периода, включающий в себя второй, третий и четвертый три геры 8, 9 и 10, блок 11 управления, формирователь 12 тестовых, комбинаци канал 13 контроля фазового сдвига и канал 14 контроля амплитуды, при этом выход делителя 2 частоты соединен с входом формирователя 12 тес товых комбинаций, выходы которого соединены с входами контролируемого блока 15, выходы которого являются входами блока 11 управления, первые выходы которого соединены с первыми входами блока 3 индикации, вторые входы которого соединены с выходами соответственно канала 7 контроля частоты и периода, канала 14 контроля амплитуды, канала 13 контроля фазового сдвига и канала 4 контроля длительности импульсов, первый вход которого соединен с первыми входами соответственно канала 7 контроля частоты и периода, канала 13 контроля фазового сдвига и с вторым выходом блока 11 управления, третий выход которого соединен с первым входом канала 14 контроля амплитуды и вторыми входами соответственно канала 4 контроля длительности импульсов, канала 7 контроля частоты и периода и канала 13 контроля фазового сдвига, четвертый выход блока 11 управления соединен с вторым входом соответственно канала 14 контроля амплитуды и третьим входом канала 13 контроля фазорого сдвига и с третьим и четвертым входами канала 4 контроля длительности импульсов, пятый вход которого соединен с первым выходом канала 14 контроля амплитуды, пятый выход блока 11 управления соединен с входом генератора 1 импульсов эталонной частоты, второй вход блока 11 управления соединен с входной шиной 16 Контроль, выходы делителя 2 частоты соединены соответственно с четвертым входом канала 13 контроля фазового сдвига и седьмым входом канала 4 контроля длительности импульсов, содержащего первый формирователь 17 импульсов, выход которого соединен с первым входом первого триггера 5, первьй вход формирователя 17 импульсов соединен с выходом первого элемента ИЛИ 18, первьй и второй входы которого соединены соответственно с вторым и пятым входами канала 4 контроля длительности импульсов, второй вход триггера является третьим входом канала 4 контроля длительности импульсов, выход первого триггера 5 соединен с первым входом первого элемента И 19, второй вход которого соединен с вторым входом канала 4 контроля длительности импульсов, третий вход первого элемента И 19 соединен соответственно с седьмым входом канала А контроля длительнос ти импульсов и счетным входом второ го счетчика 20, четвертый вход первого- элемента И соединен с первьм входом канала 4 контроля длительности импульсов, выход элемента И 19 соединен с счетным входом первого счетчика 6, входы установки нуля первого и второго счетчиков 6 и 20 соединены с четвертым входом канала 4 контроля длительности импульсов, выходы счетчиков 6 и 20 по соединены к первому и второму входам первого элемента 21 сравнения кодов, выход которого является выходом канала 4 контроля длительности импульсов. Канал13 контроля фазового сдвиг содержит второй элемент И 22, первый вход которого соединен с пер вым входом канала 13 контроля фазового сдвига, второй вход соединен со счетным входом третьего счетчика 23 и с четвертым входом канала 13 контроля фазового сдвига, третий вход второго элемента И 22 соединен через инвертор 24 с вторым входом канала 13 контроля фазового сдвига и с входом второго формирователя 25 импульсов, выход которого соединен с первым входом триггера 26, второй вход которого соединён с третьим входом канала 13 контроля ф зового сдвига, выход триггера соеди нен с четвертым входом второго элемента И 22, выход которого подключен к счетному входу четвертого счетчика 27, входы установки нуля четвертого и третьего счетчиков соединены с третьим входом канала 13 контроля фазового сдвига, выходы третьего и четвертого счетчиков через второй элемент 28 сравнения кодов соединены с выходом кана7 ла J3 контроля фазового сдвига. Канал 7 контроля частоты и перио да содержит третий элемент И 29, выход которого соединен с выходом канала 7 контроля частоты и периода а вторые входы третьего элемента И 29 соединены с выходами второго, третьего и четвертого триггеров 8, 9 и 10, первые входы второго, треть го и четвертого триггеров соединены с первым входом канала 7 контроля 0-4 частоты и периода и с первым входом третьего элемента И 29, вторые входы второго, третьего и четвертого триггеров соединены соответственно с выходами первого, второго и третьего 32 датчиков 30, 31 и.32 частоты, входы которых соединены с вторым входом канала 7 контроля частоты и периода. Блок 11 управления состоит из пятого триггера 33, единичный вход которого соединен с вторым входом блока 11 управления, инверсный выход пятого триггера 33 соединен с входом установки нуля пятого счетчика 34, а прямой выход является пятым выходом блока 11 управления и соединен с первым входом четвертого элемента И 35, второй вход которого соединен с первым информационным входом мультиплексора 36, а выход четвертого элемента И 35 соединен с входом установки 1 шестого триггера 37, выход которого является вторьм выходом блока 11 управления и подключен к первому входу элемента И-НЕ 38, выход которого соединен через второй инвертор 39 с четвертым выходом блока 11 управления и со счетным входом пятого счетчика 34, выходы которого подсоединены к первым входам дешифратора 40, выходы которого являются первыми выходами блока 11 управления, выходы пятого счетчика 34 подключены к управляющим входам мультиплексора 36, информационные входы которого соединены с первыми входами блока 11 управления, выход мультиплексора 36 подключен к третьему выходу блока 11 управления и через третий формирователь 41 импульсов; к первым входам элемента И-НЕ 38 и пятого элемента И 42, второй вход которого соединен с входом последнего разряда мультиплексора 36, а выход пятого элемента И 42 соединен с входами установки нуля пятого и шестого триггеров 33 и 37. Канал 14 контроля амплитуды построен на пороговом элементе 43, выход и вход которого являются соответственно первым входом и первым выходом канала 14 контроля амплитуды, выход порогового элемента соединен также с первым входом седьмого триггера 44, второй вход и выход которого.являются соответственно вторым входом и вторым выходом канала 14 контроля амплитуды. Устройство контроля импульсной последовательности работает следующим образом. По команде Контроль блок ления 11 запускает генератор 1 импу сов эталонной частоты, по тактам ра боты которого формирователь 12 тестовых комбинаций формирует тестовые сигналы, поступающие на входы контролируемого блока. На втором выходе блока управления формируется уровень логической единицы, который поступает в канал 13 контроля фазового сдвига, канал 4 контроля длительности импульсов и канал 7 контроля частоты и периода, открывая первые входы первого 19, второго 22 и третьего 29 элементов И и устанавливая на выходах второго 8 и третьего 9 триггеров уровень логического нуля, а на выходе четве того триггера 10 уровень логическог единицы. На выходе блока управления логическая единица держится постоян но на протяжении всего цикла провер ки, что позволяет проводить контроль всех параметров параллельно, и только после прохождения последнего контролируемого импульса послед него, канала на выходе блока 11 устанавливается уровень логического нуля. На четвертом выходе блока 11 управления по заднему фронту каждог контролируемого импульса формируется уровень логической единицы, кото рый устанавливает в нулевое состояние первьй триггер 5, триггер 26 и седьмой триггер 44 и осуществляет сброс счетчиков 20, 23, 6, 27, пере контролем каждого импульса. Через группу входов блока управления и третий выход блок управления осуществляет поочередное подключение о ного из выходов контролируемого блока 15 и пропускает контролируемые импульсы на вход порогового элемента 43 канала 14 контроля амплитуды, на вход элемента ИЖ 18 и третий вход, первого элемента И 19 канала 4, на вход второго форм рователя импульсов 25 и инвертор 24 канала 13 и на входы задатчиков 30, 31 и 32 частоты канала 7. Канал 14 контроля амплитуды работает следующим образом. Контролируемые импульсы поступают на вход порогового элемента 43. Если амплитуда, импульсов находится в пределах допуска, на выходе порогового элемента формируется уровень логической единицы, который поступает на второй вход элементе ИЛИ 18, разрешая контроль длительности импульсов, и навторой вход триггера 44. На его выходе устанавливается уровень логической единицы, которьш поступает в блок индикации, свидетельствуя о нахождении амплитуды импульсов в пределах допуска. Если амплитуда контролируемых импульсов выходит за допустимые пределы, пороговый элемент не срабатывает, а на его выходе сохраняется уровень логического нуля, который, поступая на второй вход триггера 44, не изменяет его состояния. В этом случае на вход блока индикации поступает уровень логического нуля, свидетельствующий о выходе амплитуды импульсов за пределы допуска, а контролируемые импульсы поступают прямо в канал 4 контроля длительности импульсов на первый вход элемента ИЛИ 18. . Кайал 4 контроля длительности импульсов работает следующим образом. Контролируемые импульсы через элемент ИЛИ 18 поступают на вход формирователя 17 импульсов. По переднему фронту контролируемых импульсов на вькоде формирователя 17 формируется короткий уровень логической единицы, который устанавливает на выходе триггера 5 уровень логической единицы, постзшающий на первый вход элемента И 19. Четвертый вход элемента И открывается уровнем логической единицы, поступающим с второго выхода блока 11 управления. На третий вход элемента И 19 поступают импульсы необходимой эталонной частоты с выхода делителя 2 частоты, которые проходят на вькод элемента И 19 и фиксируются счетчиком 6 длительности импульсов до тех пор, пока на втором входе элемента И 19 будет присутствовать контролируемьй импульс. Информация об измеренной длительности импульсов с выхода счетчика 6 поступает на вход первого элемента 21 сравнения кодов. Счетч,ик 20 длительности импульсов отсчитывает необходимое 7 (заданное) количество импульсов делится частоты, а сигнал переполне ния счетчика поступает на второй вход элемента 21 сравнения кодов. Если измеренная длительность импульсов совпадает с эталонной длительностью импульсов (показания сче чиков 20 и 6 равны), то на выходе элемента 21 формируется уровень логической единицы, который поступает ю в блок индикации. Если показания счетчиков 20 и 6 не совпадают, то на выходе элемента 21 формируется , уровень логического нуля, свидетельс вующий о появлении неисправности. Канал 13 контроля фазового сдвига работает следующим образом. Уровень логической единицы с вто рого выхода блока 11 управления открывает первый вход элемента И 22 На второй вход элемента И 22 поступают импульсы эталонной частоты делителя 2 частоты. Эти же импульсы поступают на счетньй вход счетчика 23 эталонного фазового сдвига, который отсчитывает определенное коли чество импульсов, а сигнал переполнения счетчика 23 поступает на второй элемент 28 сравнения кодов. Контролируемые импульсы поступают на входы инвертора 24 и формирователя 25 импульсов. По заднему фронт |этих импульсов на выходе формирователя 25 формируется короткий уровень логической единицы, которьй устанавливает на выходе триггера 26 уровень логической единицы, поступа ющий на четвертый-вход элемента И 2 а на третьем входе элемента И 22 . устанавливается логическая единица с выхода инвертора 24 по фр ту контролируемого импульса. Сигнал с выхода элемента И 22 фиксируются счетчиком 27 до тех пор, пока на третьем входе этого элемента присут ствует уровень логической единицы. Информация об измеренном фазовом . сдвиге поступает на вход элемента 28 сравнения кодов. Результат сравнения поступает в блок индикации. Канал 7 контроля частоты и перио да осуществляет контроль линейного нарастания частоты в заданном диапа зоне измененная частот. Диапазон изменения частот устанавливается зада тчиками 30, 31 и 32 частоты, каждый из которых содержит дифференцирующую цепочку, на вход которой 20 поступает контролируемый импульс, одновибратор, запускаемый сигналом дифференцирующей цепочки, и D-триггер. Диапазон изменения частоты равен периоду следования импульсов. С второго выхода &лока 11 управления уровень логической единицы поступает на первый вход элемента И 29 и устанавливает на выходах триггеров 8 и 9 уровень логического нуля, а на выходе триггера 10 уровень логической единицы. Первьй задатчик 30 частоты срабатывает при достижении минимально допустимой частоты, второй задатчик 31 частоты срабатывает при достижении максимально допустимой .частоты. Третий задатчик 32 частоты настроен на частоту, превьшающую максимально.допустимую. ЕСЛИ линейное нарастание частоты происходит на всем заданном диапазоне частот, то срабатывают только два задатчика 30 и 31 частоты, при этом на выходах триггеров 8 и 9 устанавливается уровень логической единицы. Появление логической единицы на выходе третьего элемента И 29 свидетельствует об исправной работе канала частоты системы управления. Если линейное нарастание частоты выходит за максимально допустимьй предел, то срабатывает третий задатчик 32 частоты, устанавливая на выходе триггера 10 уровень логического нуля, а появление логического нуля на выходе третьего элемента И 29 свидетельствует о необходимости подстройки канала частоты системы управления преоб{)азователем. Если линейное нарастание частоты происходит не на всем заданном диапазоне частот, то не срабатывают второй и третий.задатчики 31 и 32 ча€.тоты. На выходе элемента И 29 также устанавливается уровень логического нуля, свидетельствукщий о возникшей неисправности в канале частоты системы управления. Результат контроля поступает в блок индикации. Информация о контроле с выходов первого и второго элементов 21- и 28 сравнения кодов седьмого триггера 44 и третьего элемента И 29 через вторую группу входов поступает в блок индикации. Блок индикации содержит элементы памяти и табло. На табло индикации высвечивается номер контролируемого канала и вид неисправности 9 Блок управления работает следующим образом. По команде Контроль на выходе пятого триггера 33 устанавливается уровень логической единицы, который поступает на первый вход четвертого элемента И 35 и через пятый выход блока 11 управления запускает генер тор 1 импульсов эталонной частоты, а уровень логического нуля с инверс ного выхода триггера 33 поступает на вход установки нуля счетчика 34. Мультиплексор 36 через группу входов и третий выход блока 11 управления осуществляет поочередное подкл чение контролируемых каналов к вход порогового элемента. Проверка начинается с первого канала. Появление кoнтpoлиpyieмoгo импульса на первом информационном входе селектора-муль типлексора устанавливает на выходе четвертого элемента И 35 уровень логической единицы, который устанав ливает на выходе шестого триггера 37 уровень логической единицы, поступающий на первый вход элемента И-НЕ 38 и через второй выход блока 11 управления - в каналы контроля длительности, фазового, сдвига, частоты и периода. По заднему фронту контролируемого импульса формирователь 41 импульсов формирует уровень логическойединицы, которьй воздействует на- первый вход элемента И-НЕ 38. На выходе элемента И-НЕ 38 появляется уровень логического нуля, который поступает на счетный вход счетчика 34 и изменяет код на его выходах, а через инвертор 39 и четвертый выход блока 11 управ ления инвертированный уровень 20 .10 ческого нуля (т.е. логическая единица) поступает в каналы контроля амплитуды, длительности и фазового сдвига. При изменении кода на выходах счетчика происходит переключение контролируемых каналов, а дещифратор 40 расшифровывает состояния счетчика и посьшает информацию о номере контролируемого канала в блок индикации. Появление крнтролируемого импульса на последнем информационном входе мультиплексора 36 через инверсный вход элемента И 42 устанавливает на выходе этого элемента уровень логической единицы, которьй осуществляет установку в нулевое состояние пятого 33 и- шестого 37 триггеров. На этом контроль заканчивается. Для повторной проверки необходимо повторить команду Контроль. Формирователь 12 тестовых комбинаций додержит счетчик и блок памяти. Под действием сигналов с выхода генератора импульсов эталонной частоты счетчик изменяет свое состояние. Код на его выходах увеличивается на единицу и подается на адресные входы блока памяти. С выхода блока памяти считывается число, записанное в ячейке с разным адресом, и подается на входы контролируемого блока. В зависимости от этого числа подключается определенный вход контролируемого блока 15, а на его выходах .формируются импульсы, которые через группу входов и четвертый выход блока 11 управления поступают в каналы контроля амплитуды, длительности и фазового сдвига.

ffa tfniuнацию

fiuf.2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля и обнаружения неисправностей систем управления тиристорными преобразователями | 1979 |

|

SU864194A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для измерения временныхпАРАМЕТРОВ | 1978 |

|

SU805194A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1985-07-15—Публикация

1983-06-17—Подача