Изобретение относится к преобразовательной технике и может быть использовано при разработке устройств электропитания постоянного напряжения.

Цель изобретения - повышение точности стабилизации устранения сквозных токов и повышение надежности работы конвертора путем устранения сквозных токов.

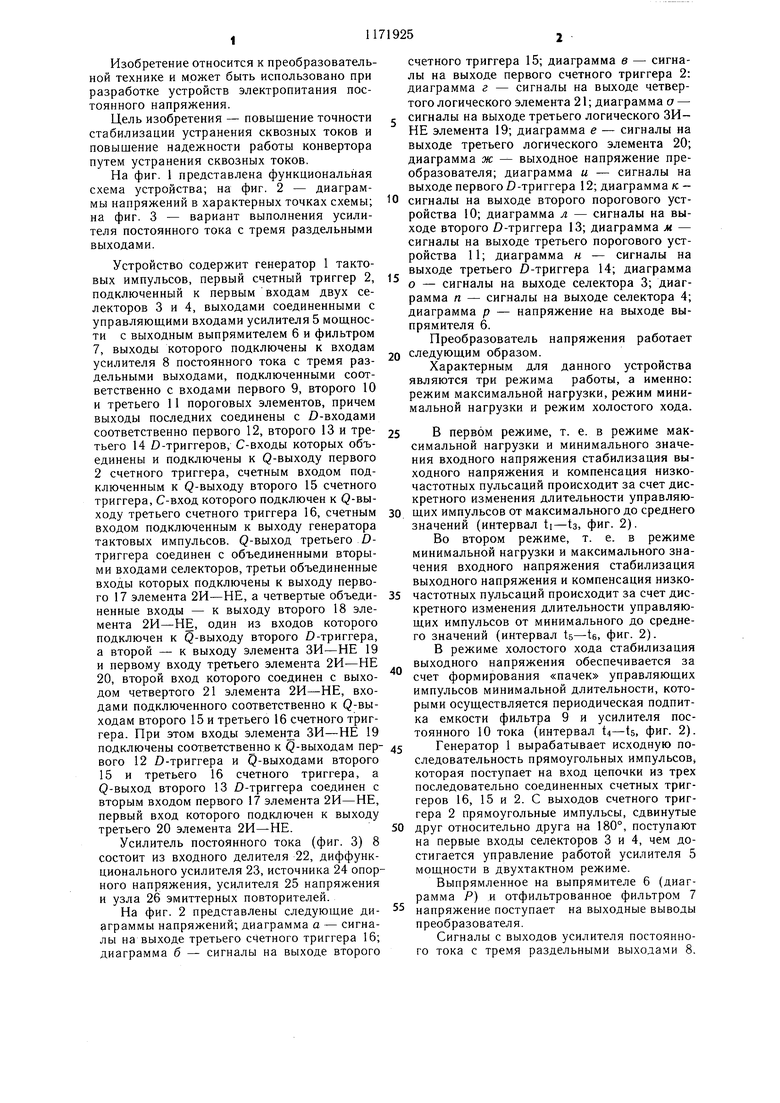

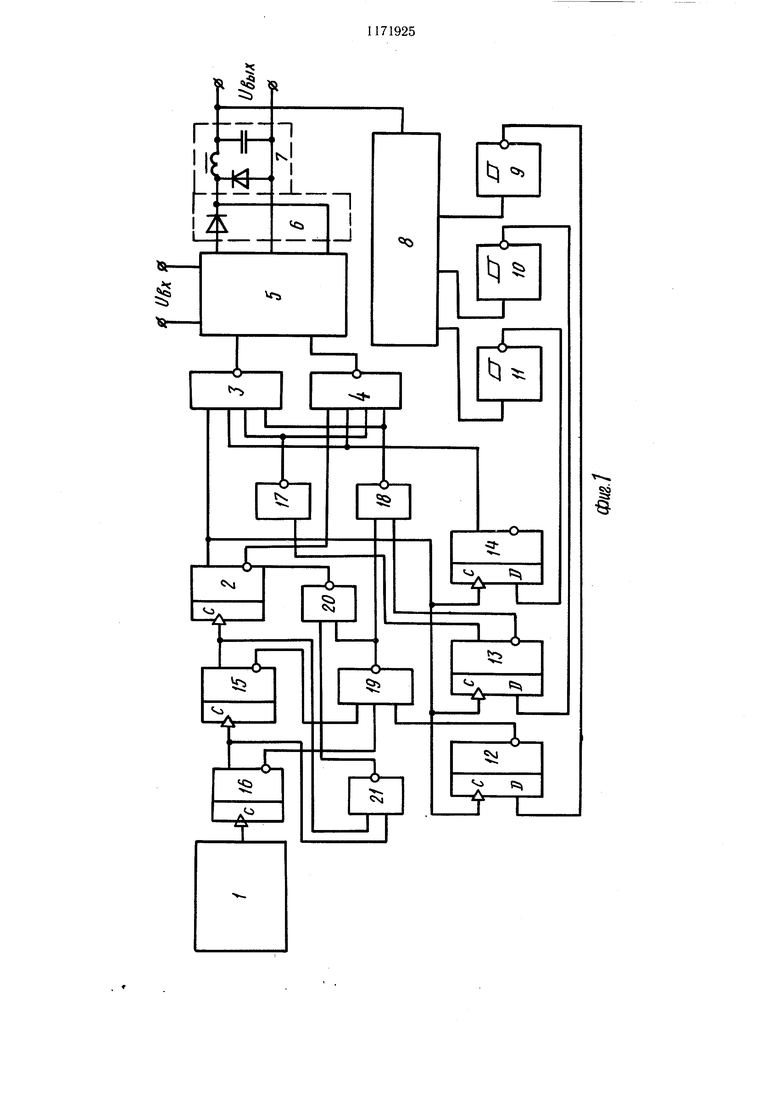

На фиг. 1 представлена функциональная схема устройства; на фиг. 2 - диаграммы напряжений в характерных точках схемы; на фиг. 3 - вариант выполнения усилителя постоянного тока с тремя раздельными выходами.

Устройство содержит генератор 1 тактовых импульсов, первый счетный триггер 2, подключенный к первым входам двух селекторов 3 и 4, выходами соединенными с управляющими входами усилителя 5 мош,ности с выходным выпрямителем 6 и фильтром 7, выходы которого подключены к входам усилителя 8 постоянного тока с тремя раздельными выходами, подключенными соответственно с входами первого 9, второго 10 и третьего 11 пороговых элементов, причем выходы последних соединены с D-входами соответственно первого 12, второго 13 и третьего 14 D-триггеров, С-входы которых объединены и подключены к Q-выходу первого 2 счетного триггера, счетным входом подключенным к Q-выходу второго 15 счетного триггера, С-вход которого подключен к Q-выходу третьего счетного триггера 16, счетным входом подключенным к выходу генератора тактовых импульсов. Q-выход третьего Dтриггера соединен с объединенными вторыми входами селекторов, третьи объединенные входы которых подключены к выходу первого 17 элемента 2И-НЕ, а четвертые объединенные входы - к выходу второго 18 элемента 2И-НЕ, один из входов которого подключен к Q-выходу второго D-триггера, а второй - к выходу элемента ЗИ-НЕ 19 и первому входу третьего элемента 2И-НЕ 20, второй вход которого соединен с выходом четвертого 21 элемента 2И-НЕ, входами подключенного соответственно к Q-выходам второго 15 и третьего 16 счетного триггера. При этом входы элемент;а ЗИ-НЕ 19 подключены соответственно к Q-выходам первого 12 D-триггера и Q-выходами второго 15 и третьего 16 счетного триггера, а Q-выход второго 13 )-триггера соединен с вторым входом первого 17 элемента 2И-НЕ, первый вход которого подключен к выходу третьего 20 элемента 2И-НЕ.

Усилитель постоянного тока (фиг. 3) 8 состоит из входного делителя 22, диффункционального усилителя 23, источника 24 опорного напряжения, усилителя 25 напряжения и узла 26 эмиттерных повторителей.

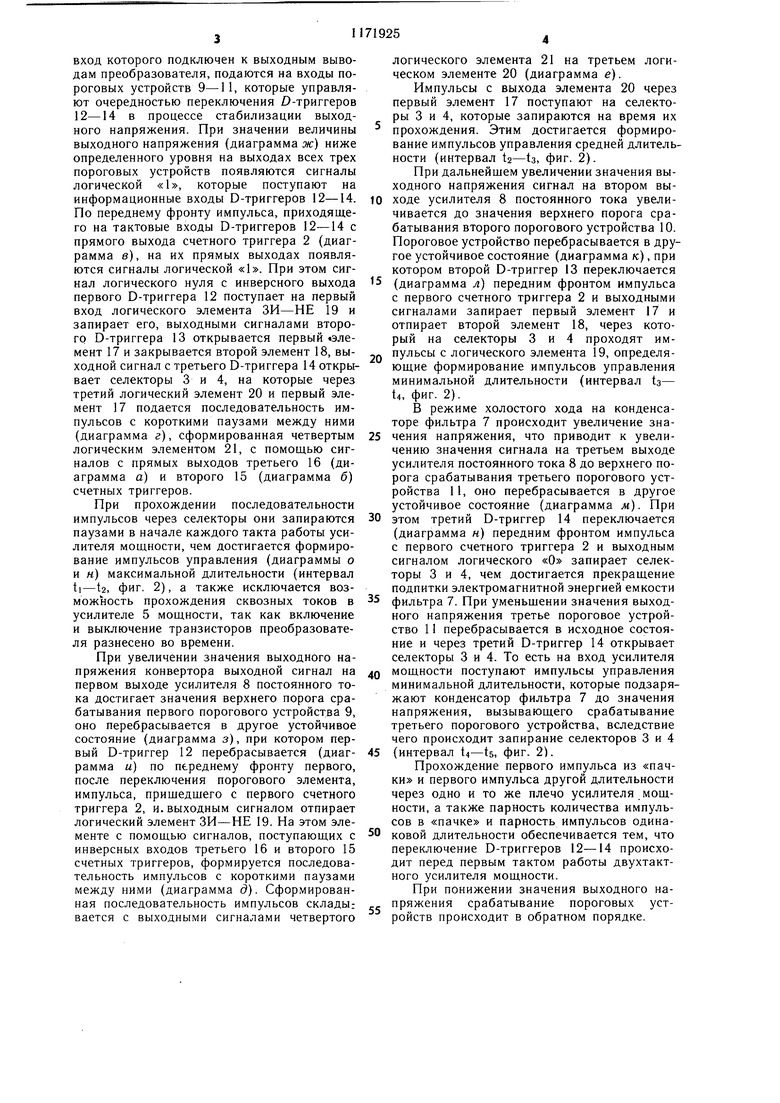

На фиг. 2 представлены следующие диаграммы напряжений; диаграмма а - сигналы на выходе третьего счетного триггера 16; диаграмма б - сигналы на выходе второго

счетного триггера 15; диаграмма в - сигналы на выходе первого счетного триггера 2: диаграмма г - сигналы на выходе четвертого логического элемента 21; диаграмма о - сигналы на выходе третьего логического ЗИНЕ элемента 19; диаграмма е - сигналы на выходе третьего логического элемента 20; диаграмма ж - выходное напряжение преобразователя; диаграмма и - сигналы на выходе первого D-триггера 12; диаграмма к 0 сигналы на выходе второго порогового устройства 10; диаграмма л - сигналы на выходе второго )-триггера 13; диаграмма м - сигналы на выходе третьего порогового устройства 11; диаграмма н - сигналы на выходе третьего D-триггера 14; диаграмма о - сигналы на выходе селектора 3; диаграмма п - сигналы на выходе селектора 4; диаграмма р - напряжение на выходе выпрямителя 6.

Преобразователь напряжения работает

0 следующим образом.

Характерным для данного устройства являются три режима работы, а именно: режим максимальной нагрузки, режим минимальной нагрузки и режим холостого хода.

5 В первом режиме, т. е. в режиме максимальной нагрузки и минимального значения входного напряжения стабилизация выходного напряжения и компенсация низкочастотных пульсаций происходит за счет дискретного изменения длительности управляющих импульсов от максимального до среднего значений (интервал ti-1з, фиг. 2).

Во втором режиме, т. е. в режиме минимальной нагрузки и максимального значения входного напряжения стабилизация выходного напряжения и компенсация низкочастотных пульсаций происходит за счет дискретного изменения длительности управляющих импульсов от минимального до среднего значений (интервал ts-te, фиг. 2).

В режиме холостого хода стабилизация выходного напряжения обеспечивается за счет формирования «пачек управляющих импульсов минимальной длительности, которыми осуществляется периодическая подпитка емкости фильтра 9 и усилителя постоянного 10 тока (интервал t4-ts, фиг. 2).

5 Генератор 1 вырабатывает исходную последовательность прямоугольных импульсов которая поступает на вход цепочки из трех последовательно соединенных счетных триггеров 16, 15 и 2. С выходов счетного триггера 2 прямоугольные импульсы, сдвинутые

0 друг относительно друга на 180°, поступают на первые входы селекторов 3 и 4, чем достигается управление работой усилителя 5 мощности в двухтактном режиме.

Выпрямленное на выпрямителе 6 (диаграмма Я) и отфильтрованное фильтром 7 напряжение поступает на выходные выводы преобразователя.

Сигналы с выходов усилителя постоянного тока с тремя раздельными выходами 8.

вход которого подключен к выходным выводам преобразователя, подаются на входы пороговых устройств 9-11, которые управляют очередностью переключення D-триггеров 12-14 в процессе стабилизации выходного напряжения. При значении величины выходного напряжения (диаграмма ж) ниже определенного уровня на выходах всех трех пороговых устройств появляются сигналы логической «1, которые поступают на информационные входы D-триггеров 12-14. По переднему фронту импульса, приходящего на тактовые входы D-триггеров 12-14 с прямого выхода счетного триггера 2 (диаграмма в), на их прямых выходах появляются сигналы логической «1. При этом сигнал логического нуля с инверсного выхода первого D-триггера 12 поступает на первый вход логического элемента ЗИ-НЕ 19 и запирает его, выходными сигналами второго D-триггера 13 открывается первый «элемент 17 и закрывается второй элемент 18, выходной сигнал с третьего D-триггера 14 открывает селекторы 3 и 4, на которые через третий логический элемент 20 и первый элемент 17 подается последовательность импульсов с короткими паузами между ними (диаграмма г), сформированная четвертым логическим элементом 21, с помощью сигналов с прямых выходов третьего 16 (диаграмма а) и второго 15 (диаграмма б) счетных триггеров.

При прохождении последовательности импульсов через селекторы они запираются паузами в начале каждого такта работы усилителя мощности, чем достигается формирование импульсов управления (диаграммы о и я) максимальной длительности (интервал ti-12, фиг. 2), а также исключается возможность прохождения сквозных токов в усилителе 5 мощности, так как включение и выключение транзисторов преобразователя разнесено во времени.

При увеличении значения выходного напряжения конвертора выходной сигнал на первом выходе усилителя 8 постоянного тока достигает значения верхнего порога срабатывания первого порогового устройства 9, оно перебрасывается в другое устойчивое состояние (диаграмма з), при котором первый D-триггер 12 перебрасывается (диаграмма и) по переднему фронту первого, после переключения порогового элемента, импульса, прищедщего с первого счетного триггера 2, и. выходным сигналом отпирает логический элемент ЗИ-НЕ 19. На этом элементе с помощью сигналов, поступающих с инверсных входов третьего 16 и второго 15 счетных триггеров, формируется последовательность импульсов с короткими паузами между ними (диаграмма д). Сформированная последовательность импульсов склады: вается с выходными сигналами четвертого

логического элемента 21 на третьем логическом элементе 20 (диаграмма е).

Импульсы с выхода элемента 20 через первый элемент 17 поступают на селекторы 3 и 4, которые запираются на время их прохождения. Этим достигается формирование импульсов управления средней длительности (интервал t2-ts, фиг. 2).

При дальнейшем увеличении значения выходного напряжения сигнал на втором выходе усилителя 8 постоянного тока увеличивается до значения верхнего порога срабатывания второго порогового устройства 10. Пороговое устройство перебрасывается в другое устойчивое состояние (диаграмма к), при котором второй D-триггер 13 переключается

5 (диаграмма л) передним фронтом импульса с первого счетного триггера 2 и выходными сигналами запирает первый элемент 17 и отпирает второй элемент 18, через который на селекторы 3 и 4 проходят имQ пульсы с логического элемента 19, определяющие формирование импульсов управления минимальной длительности (интервал ta- t4, фиг. 2).

В режиме холостого хода на конденсаторе фильтра 7 происходит увеличение значения напряжения, что приводит к увеличению значения сигнала на третьем выходе усилителя постоянного тока 8 до верхнего порога срабатывания третьего порогового устройства 11, оно перебрасывается в другое устойчивое состояние (диаграмма м). При

0 этом третий D-триггер 14 переключается (диаграмма н) передним фронтом импульса с первого счетного триггера 2 и выходным сигналом логического «О запирает селекторы 3 и 4, чем достигается прекращение подпитки электромагнитной энергией емкости

фильтра 7. При уменьшении значения выходного напряжения третье пороговое устройство 11 перебрасывается в исходное состояние и через третий D-триггер 14 открывает селекторы 3 и 4. То есть на вход усилителя

мощности поступают импульсы управления минимальной длительности, которые подзаряжают конденсатор фильтра 7 до значения напряжения, вызывающего срабатывание третьего порогового устройства, вследствие чего происходит запирание селекторов 3 и 4

5 (интервал t4-ts, фиг. 2).

Прохождение первого импульса из «пачки и первого импульса другой длительности через одно и то же плечо усилителя мощности, а также парность количества импульсов в «пачке и парность импульсов одинаковой длительности обеспечивается тем, что переключение D-триггеров 12-14 происходит перед первым тактом работы двухтактного усилителя мощности.

При понижении значения выходного напряжения срабатывание пороговых устройств происходит в обратном порядке.

s

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления стабилизированным преобразователем постоянного напряжения в постоянное | 1986 |

|

SU1365291A1 |

| Стабилизированный преобразователь напряжения | 1988 |

|

SU1614007A1 |

| Преобразователь активной мощности трехфазной электрической цепи в цифровой код | 1987 |

|

SU1597759A1 |

| Стабилизированный многофазный импульсный преобразователь постоянного напряжения | 1986 |

|

SU1355965A1 |

| Стабилизирующий преобразователь постоянного напряжения | 1987 |

|

SU1436233A1 |

| Преобразователь постоянного напряжения в трехфазное | 1985 |

|

SU1288870A1 |

| Стабилизированный источник постоянного напряжения | 1985 |

|

SU1309012A1 |

| Устройство для управления преобразователем постоянного напряжения в квазисинусоидальное с ШИМ | 1983 |

|

SU1358055A1 |

| Устройство для регистрации информации | 1985 |

|

SU1308839A1 |

| Устройство управления процессом электроосаждения | 1989 |

|

SU1654385A1 |

СТАБИЛИЗИРУЮЩИЙ ПРЕОБРАЗОВАТЕЛЬ ПОСТОЯННОГО НАПРЯЖЕНИЯ, содержащий генератор тактовых импульсов, первый счетный триггер, выходы которого подключены к первым входам двух селекторов, выходами соединенных с управляющими входами усилителя мощности с выходным выпрямителем и фильтром, при этом выходы последнего подключены к входам усилителя постоянного тока, первым выходом подключенного к входу первого порогового элемента, отличающийся тем, что, с целью повышения точности стабилизации и надежности путем устранения сквозных токов, в него введены второй и третий пороговые элементы, три D-триггера, четыре логических элемента 2И-НЕ, логический элемент ЗИ-НЕ и второй и третий счетные триггеры, а усилитель тока выполнен с двумя дополнительными, раздельными от первого, выходами, которые подключены к входам второго и третьего пороговых элементов, причем выходы пороговых элементов соединены соответственно с D-входами D-триггеров, С-входы которых объединены и подключены к Q-выходу первого счетного триггера, С-входом подключенного к Q-выходу второго счетного триггера, С-вход которого подключен к (-выходу третьего счетного триггера, С-входом подключенного к выходу генератора тактовых импульсов, Q-выход третьего D-триггера соединен с объединенными входами селекторов, третьи объединенные входы которых подключены к выходу первого логического элемента 2И-НЕ, а четвертые объединенные входы - к выходу второго логического элемента 2И-НЕ, один из входов которого подключен к Q-выходу € второго / -триггера, а другой - к выходу СО логического элемента ЗИ-НЕ и первому входу третьего логического элемента 2И-НЕ, второй вход которого подключен к выходу четвертого логического элемента 2И-НЕ, входами соединенного соответственно с Q-выходами второго и третьего счетных триггеров, при этом входы логического эле.мента ЗИ-НЕ подключены соответственно к Q-выходу первого D-триггера и Q-выходам второго и третьего счетных триггеров, Q-выход второго D-триггера соединен с вторым со входом первого логического элемента 2И- ND НЕ, первый вход которого соединен с выходом третьего логического элемента 2И-НЕ. сл

| Стабилизированный конвертор | 1977 |

|

SU736291A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Стабилизированный конвертор | 1981 |

|

SU974361A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1985-08-07—Публикация

1984-01-17—Подача