1

4 ширины ИМПУЛЬСИП второго ГзОГЯЧСского элемента 2H-FIE 24, при этом один из входов указанного логического элемента подключен к прямому выходу формирователя 22 импульсов сброса, другой вход - через элемент 23 задержки к прямому выходу D-триг- гера 20 управления следующего формирователя 4 ширины импульсов, а выход - к R-входу D-триггера 21 готовности. В каждом из N формирователей 4 ширины импульсов прямой выход D- триггера 20 управления подключен через элемент 23 задержки к первому

Изобретение относится к электротехнике и может быть использовгано в устройствах электропитания радиоэлектронных приборов, систем автоматики, в частности, с многофазными импульсными стабилизаторами, содержащими N силовых каналов, выполненных по любой из известных однофазных схем импульсного преобразования и регулирования электрической энергии, выходные и входные цепи которых подключены параллельно или последовательно к источнику питания и нагрузке соответственно.

Цель изобретения - улучшение качества процесса регулирования.

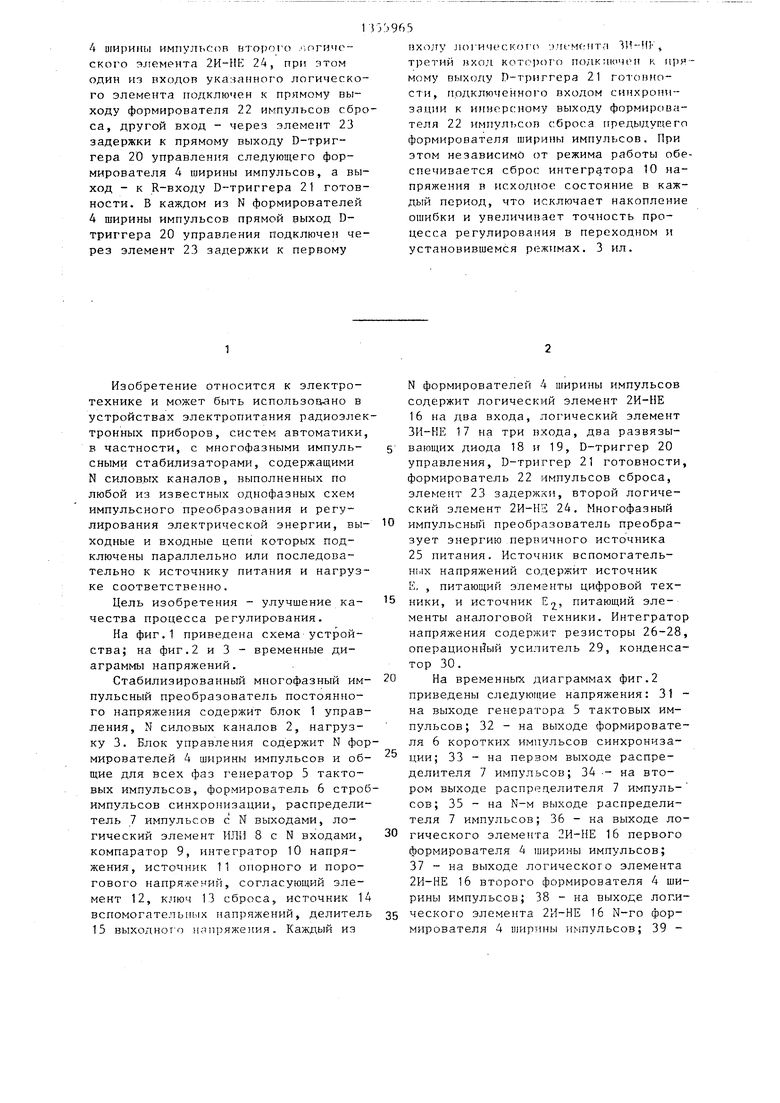

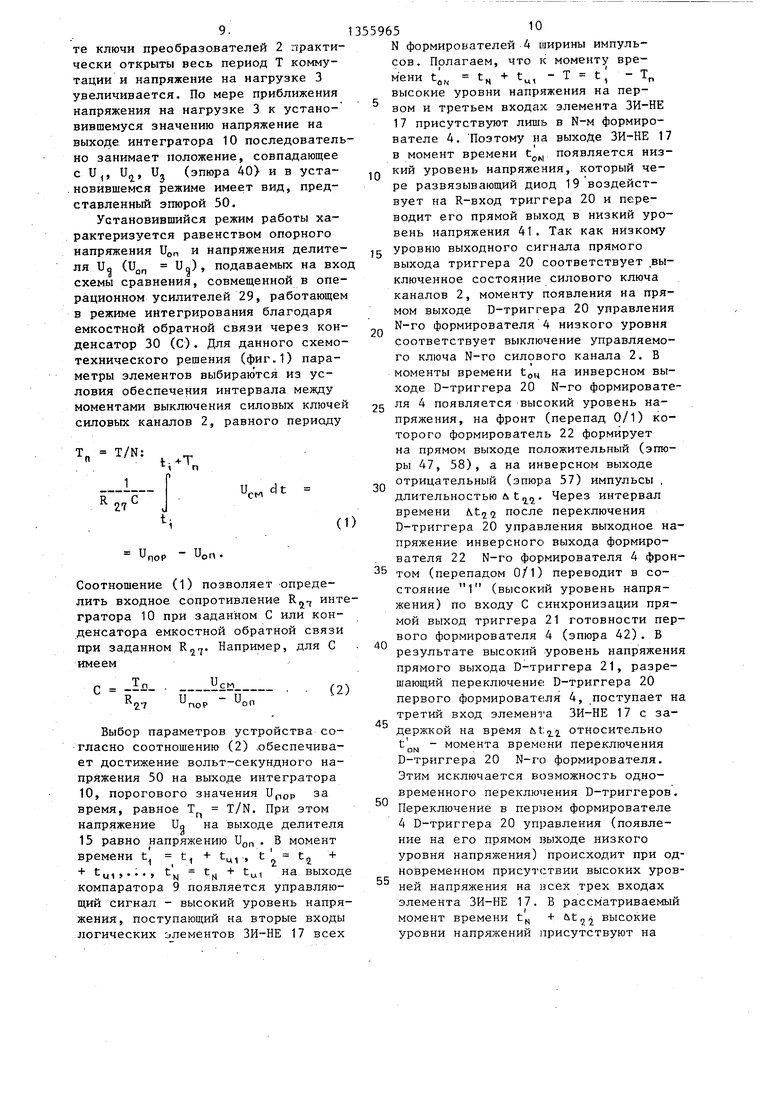

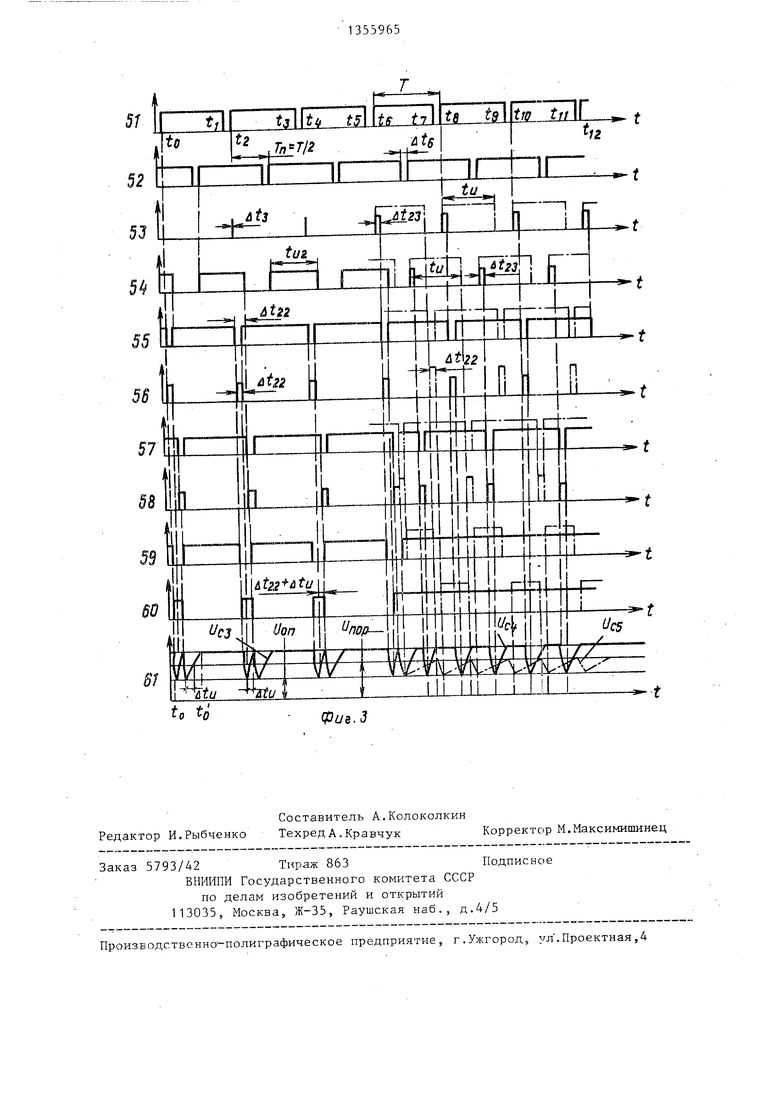

На фиг.1 приведена схема устрой- CTBaj на фиг.2 и 3 - временные диаграммы напряжений.

Стабилизированный многофазный импульсный преобразователь постоянного напряжения содержит блок 1 управления, N силовых каналов 2, нагрузку 3. Блок управления содержит N формирователей 4 ширины импульсов и общие для всех фаз г енератор 5 тактовых импульсов, формирователь 6 строб импульсов синхронизации, распределитель 7 импульсов с N выходами, логический элемент ИЛИ 8 с N входами, компаратор 9, интегратор 10 напряжения, источник 11 опорного и поро- говог о напряжений, согласующий элемент 12, ключ 13 сброса, источник 14 вспомогательных напряжений, делитель 15 выходнот о напряжения. Каждый из

963

ихолу логическот о :)Л1 Мо та ЗИ--(-,

третий вход KOTOl OT O ПОДКИЮЧ(М к (11)Ямому выходу D-триггера 21 готовности, подключенного входом синхронизации к иннерсному выходу формирователя 22 импулт.сов сброса предыдущего формирователя ширины импульсов. При этом независимо от режима работы обеспечивается сброс интегратора 10 напряжения в исходное состояние в каждый период, что исключает накопление ошибки и увеличивает точность процесса регулирования в переходном и установившемся режимах. 3 ил.

N формирователей 4 ширины импульсов содержит логический элемент 2И-НЕ 16 на два входа, логический элемент ЗИ-НЕ 17 на три входа, два развязы- вающих диода 18 и 19, D-триггер 20 управления, D-триггер 21 готовности, формирователь 22 импульсов сброса, элемент 23 задержки, второй логический элемент 2И-НЕ 24. Многофазный

импульсный преобразователь преобразует энергию первичного источника 25 питания. Источник вспомогательных напряжений содержит источник Е, , питающий элементы цифровой техНИКИ, и источник V., питающий элементы аналоговой техники. Интегратор напряжения содержит резисторы 26-28, операционный усилитель 29, конденсатор 30.

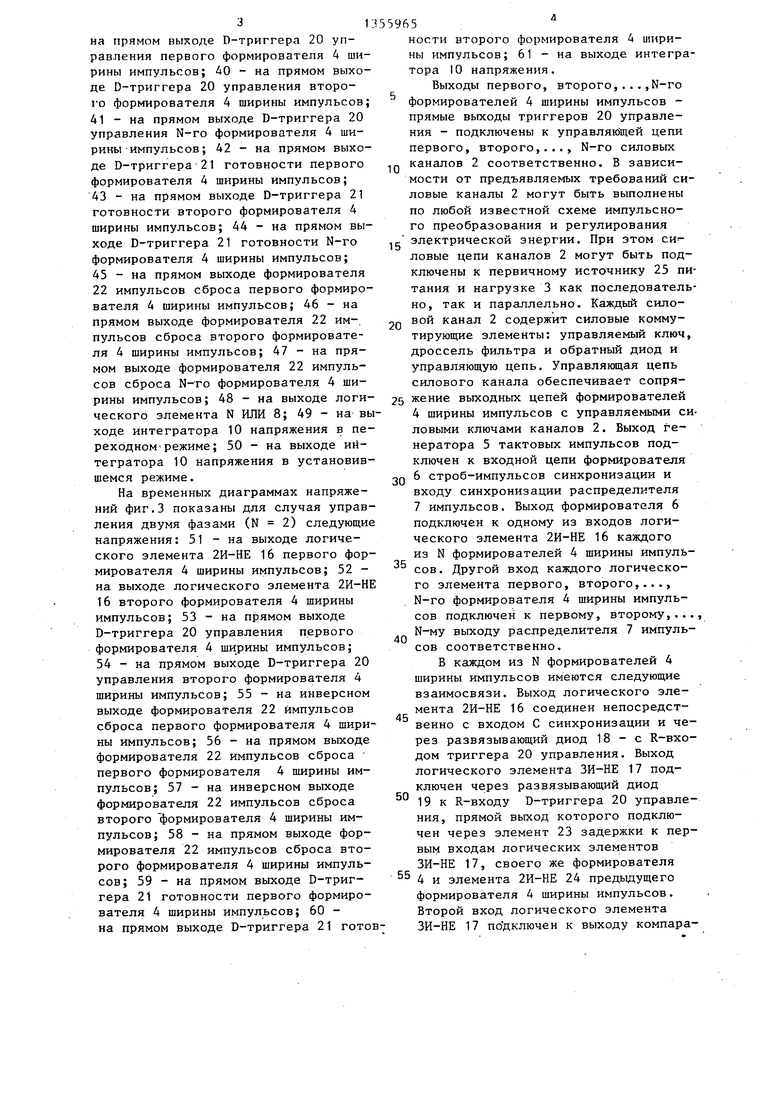

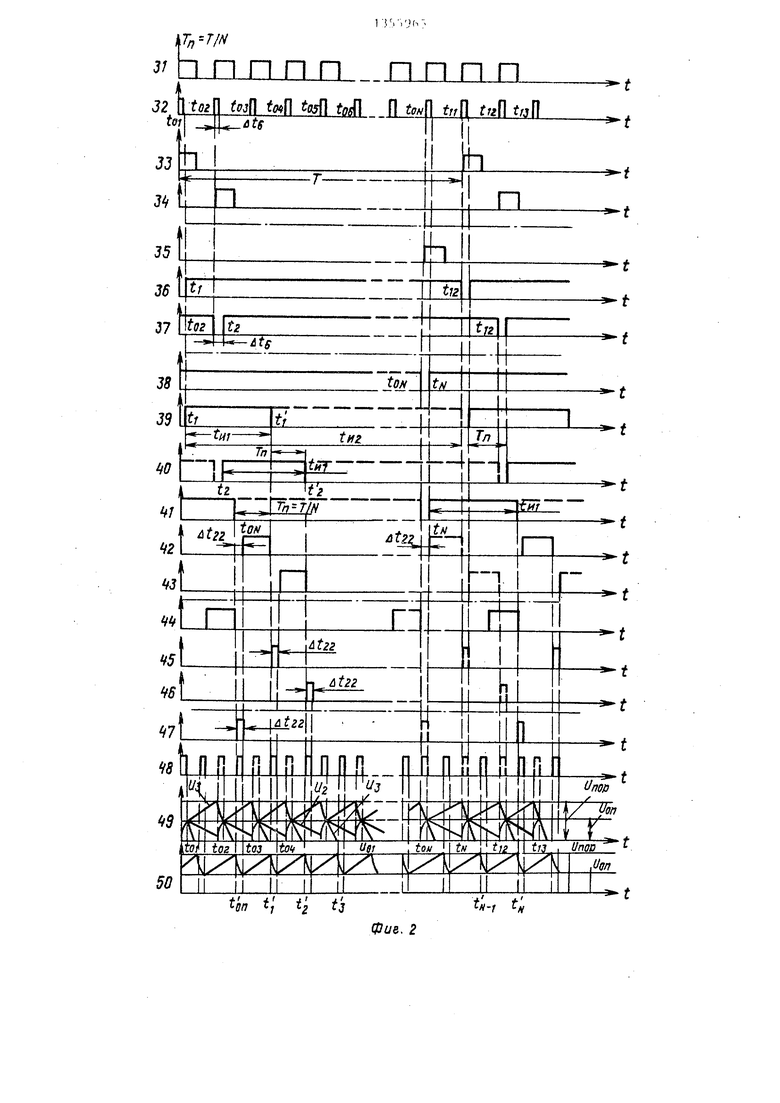

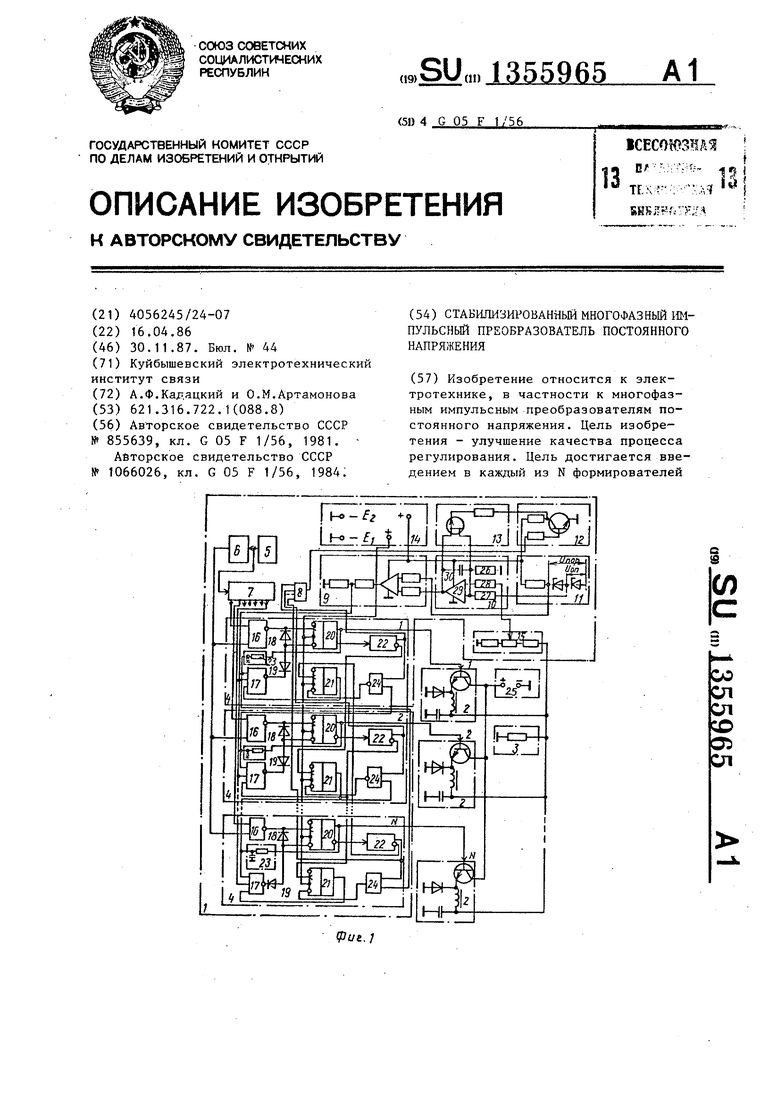

На временных диаграммах фиг.2

приведены следующие напряжения: 31 - на выходе генератора 5 тактовых импульсов; 32 - на выходе формирователя 6 коротких импульсов синхронизации; 33 - на первом выходе распределителя 7 импульсов; 34 - на втором выходе распределителя 7 импуль- сов; 35 - на N-M выходе распределителя 7 импульсов; 36 - на выходе логического элемента 2И-НЕ 16 первого формирователя 4 ширины импульсов; 37 - на выходе логического элемента 2И-НЕ 16 второго формирователя 4 ширины импульсов; 38 - на выходе лопического элемента 2И-НЕ 16 N-ro формирователя 4 ширины импульсов; 39 31

на прямом выходе D-триггера 20 управления первого формирователя 4 ширины импульсов; 40 - на прямом выходе D-триггера 20 управления второго формирователя 4 ширины импульсов; 41 - на прямом выходе D-триггера 20 управления N-ro формирователя 4 ширины -импульсов; 42 - на прямом выходе D-триггера 21 готовности первого формирователя 4 ширины импульсов; 43 - на прямом выходе D-триггера 21 готовности второго формирователя 4 ширины импульсов; 44 - на прямом выходе D-триггера 21 готовности N-ro формирователя 4 ширины импульсов; 45 - на прямом выходе формирователя 22 импульсов сброса первого формирователя 4 ширины импульсов; 46 - на прямом выходе формирователя 22 им-, пульсов сброса второго формирователя 4 ширины импульсов; 47 - на прямом выходе формирователя 22 импульсов сброса N-TO формирователя 4 ширины импульсов; 48 - на выходе логического элемента N ИЛИ 8; 49 - на вы ходе интегратора 10 напряжения в переходном -режиме; 50 - на выходе интегратора 10 напряжения в установившемся режиме.

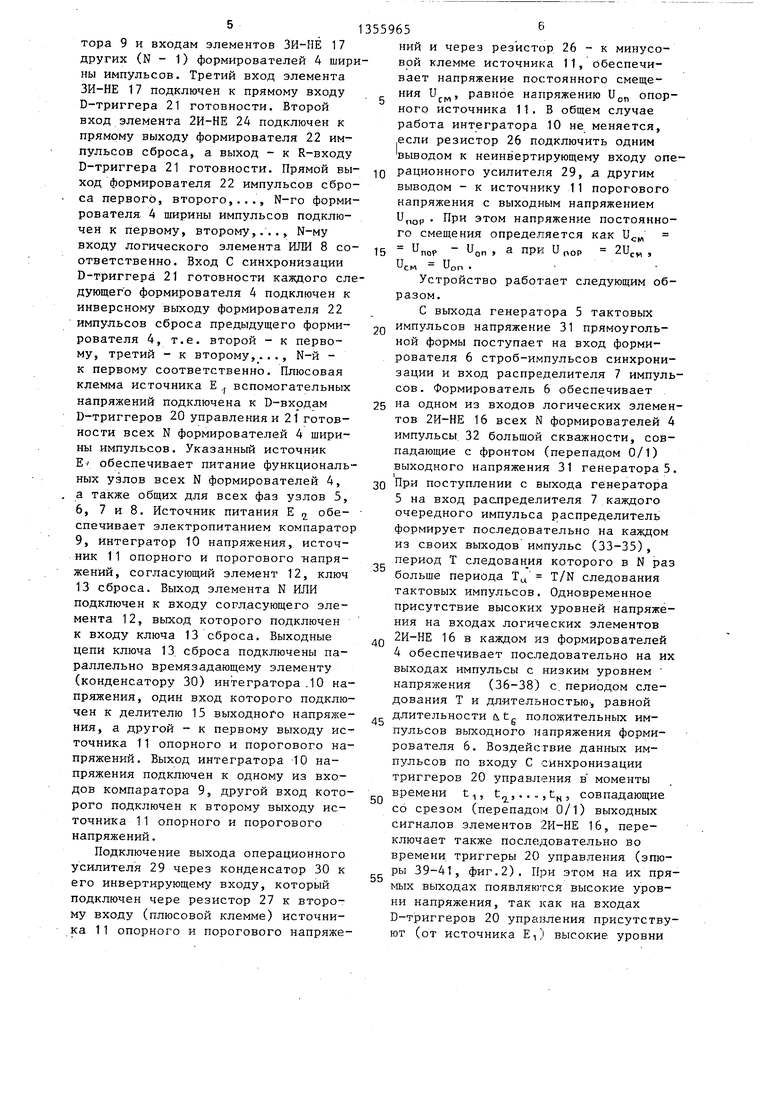

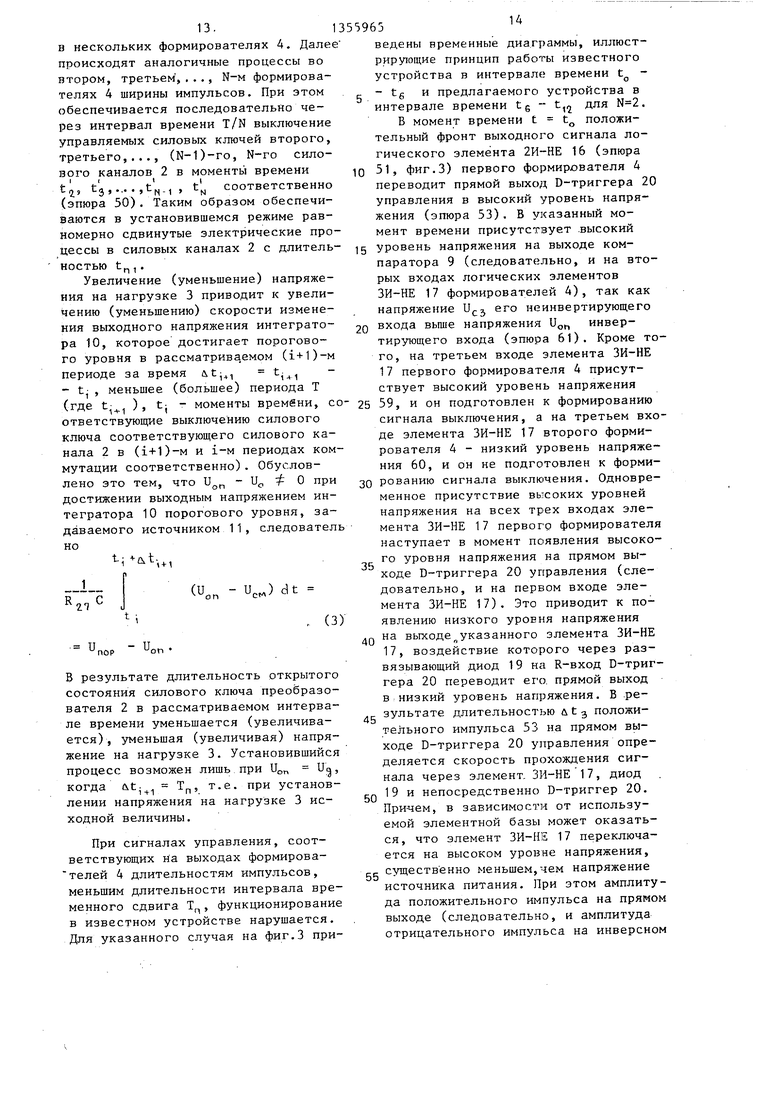

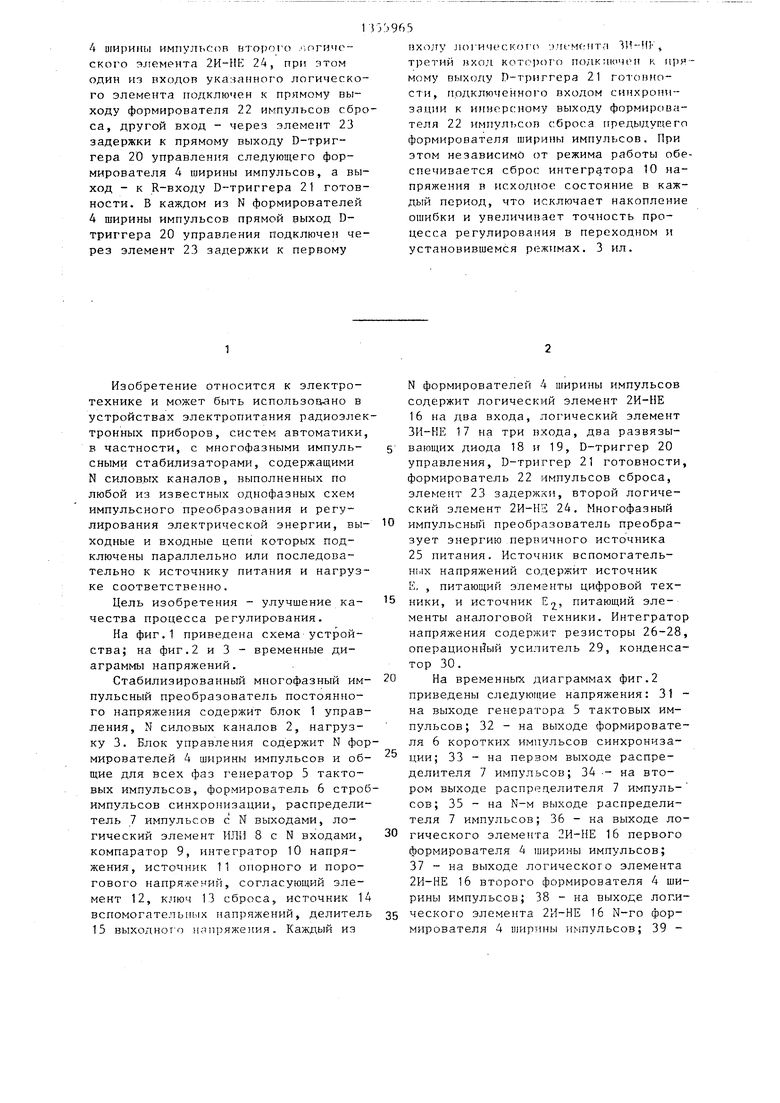

На временных диаграммах напряжений фиг.З показаны для случая управления двумя фазами (N 2) следующие напряжения: 51 - на выходе логического элемента 2И-НЕ 16 первого формирователя 4 ширины импульсов; 52 - на выходе логического элемента 2И-НЕ 16 второго формирователя 4 ширины импульсов; 53 - на прямом выходе D-триггера 20 управления первого формирователя 4 ширины импульсов; 54 - на прямом выходе D-триггера 20 управления второго формирователя 4 ширины импульсов; 55 - на инверсном выходе формирователя 22 импульсов сброса первого формирователя 4 ширины импульсов; 56 - на прямом выходе формирователя 22 импульсов сброса первого формирователя 4 ширины импульсов; 57 - на инверсном выходе формирователя 22 импульсов сброса второго формирователя 4 ширины импульсов; 58 - на прямом выходе формирователя 22 импульсов сброса второго формирователя 4 ширины импульсов; 59 - на прямом выходе D-триггера 21 готовности первого формирователя 4 ширины импульсов; 60 - на прямом выходе D-триггера 21 готов

55965 .

кости второго формирователя 4 ширины импульсов; 61 - на выходе интегратора 10 напряжения.

Выходы первого, второго,...,N-ro формирователей 4 ширины импульсов - прямые выходы триггеров 20 управления - подключены к управляющей цепи первого, второго,..., N-ro силовых

Q каналов 2 соответственно. В зависимости от предъявляемых требований силовые каналы 2 могут быть выполнены по любой известной схеме импульсного преобразования и регулирования

-g электрической энергии. При этом силовые цепи каналов 2 могут быть подключены к первичному источнику 25 питания и нагрузке 3 как последовательно, так и параллельно. Каждый сило2Q вой канал 2 содержит силовые коммутирующие элементы: управляемый ключ, дроссель фильтра и обратный диод и управляющую цепь. Управляющая цепь силового канала обеспечивает сопря25 жение выходных цепей формирователей 4 ширины импульсов с управляемыми силовыми ключами каналов 2. Выход генератора 5 тактовых импульсов подключен к входной цепи формирователя

2Q 6 строб-импульсов синхронизации и входу синхронизации распределителя 7 импульсов. Выход формирователя 6 подключен к одному из входов логического элемента 2И-НЕ 16 каждого из N формирователей 4 ширины импульсов . Другой вход каждого логического элемента первого, второго,..., N-ro формирователя 4 ширины импульсов подключен к первому, второму,..., N-му выходу распределителя 7 импульсов соответственно.

В каждом из N формирователей 4 ширины импульсов имеются следующие взаимосвязи. Выход логического элемента 2И-НЕ 16 соединен непосредственно с входом С синхронизации и через развязывающий диод 18 - с R-BXO- дом триггера 20 управления. Выход логического элемента ЗИ-НЕ 17 подключен через развязывающий диод 19 к R-входу D-триггера 20 управления, прямой выход которого подключен через элемент 23 задержки к первым входам логических элементов ЗИ-НЕ 17, своего же формирователя

4 и элемента 2И-НЕ 24 предыдущего формирователя 4 ширины импульсов. Второй вход логического элемента ЗИ-НЕ 17 по дключен к выходу компара35

40

45

50

5

тора 9 и входам элементов ЗИ-НЁ 17 других (N - 1) формирователей 4 ширины импульсов. Третий вход элемента ЗИ-НЕ 17 подключен к прямому входу D-триггера 21 готовности. Второй вход элемента 2И-НЕ 24 подключен к прямому выходу формирователя 22 импульсов сброса, а выход - к R-БХОДУ D-триггера 21 готовности. Прямой выход формирователя 22 импульсов сброса первого, второго,..., N-ro формирователя 4 ширины импульсов подключен к первому, второму,..., N-му входу логического элемента ИЛИ 8 соответственно. Вход С синхронизации D-триггера 21 готовности каждого следующего формирователя 4 подключен к инверсному выходу формирователя 22 импульсов сброса предыдущего формирователя 4, т.е. второй - к первому, третий - к второму,..., N-й - к первому соответственно. Плюсовая клемма источника Е ,, вспомогательных напряжений подключена к D-вхрдам D-триггеров 20 управления и 21 готовности всех N формирователей 4 ширины импульсов. Указанный источник Е обеспечивает питание функциональных узлов всех N формирователей 4, а также общих для всех фаз узлов 5, 6, 7 и 8. Источник питания Е обе- спечивает электропитанием компаратор 9, интегратор 10 напряжения, источник 11 опорного и порогового напряжений, согласующий элемент 12, ключ 13 сброса. Выход элемента N ИЛИ подключен к входу согласующего элемента 12, выход которого подключен к входу ключа 13 сброса. Выходные цепи ключа 13. сброса подключены параллельно времязадающему элементу (конденсатору 30) интегратора .10 напряжения, один вход которого подключен к делителю 15 выходного напряжения, а другой - к первому выходу источника 11 опорного и порогового напряжений. Выход интегратора 10 напряжения подключен к одному из входов компаратора 9, другой вход которого подключен к второму выходу источника 11 опорного и порогового напряжений.

Подключение выхода операционного усилителя 29 через конденсатор 30 к его инвертирующему входу, который подключен чере резистор 27 к второму входу (плюсовой клемме) источника 11 опорного и порогового напряже

55965

НИИ и через резистор 26 - к минусовой клемме источника 11, обеспечивает напряжение постоянного смещения и , равное напряжению Uo опорного источника 11. В общем случае работа интегратора 10 не меняется, |если резистор 26 подключить одним выводом к неинвертирующему входу опе- 1Q рационного усилителя 29, а другим выводом - к источнику 11 порогового напряжения с выходным напряжением

и

ПОР

При ЭТОМ напряжение постоянно

го смещения определяется как U,. - U-n , а при и POP 2U,.

и

и

0

5

пор

и

5

он см - Jon .

Устройство работает следующим образом.

С выхода генератора 5 тактовых импульсов напряжение 31 прямоугольной формы поступает на вход формирователя 6 строб-импульсов синхронизации и вход распределителя 7 импульсов. Формирователь 6 обеспечивает

5 на одном из входов логических элементов 2И-НЕ 16 всех N формирователей 4 импульсы 32 большой скважности, совпадающие с фронтом (перепадом 0/1) выходного напряжения 31 генератора 5.

0 При поступлении с выхода генератора 5 на вход распределителя 7 каждого очередного импульса распределитель формирует последовательно на каждом из своих выходов импульс (33-35), период Т следования которого в N раз больше периода Тц T/N следования тактовых импульсов. Одновременное присутствие высоких уровней напряжения на входах логических элементов 2И-НЕ 16 в каждом из формирователей 4 обеспечивает последовательно на их выходах импульсы с низким уровнем напряжения (36-38) с. периодом следования Т и длительностью-, равной

. длительности at.- положительных им- 5ь,

пульсов выходного напряжения формирователя 6. Воздействие данных импульсов по входу С синхронизации триггеров 20 управления в моменты времени t, t,..,,t, совпадающие со срезом (перепадом 0/1) выходных сигналов элементов 2И-НЕ 16, переключает также последовательно во времени триггеры 20 управления (эпюры 39-41, фиг.2). При этом на их прямых выходах появляются высокие уровни напряжения, так как на входах D-триггеров 20 управления присутствуют (от источника EI) высокие уровни

0

71

напряжения. Поскольку прямые выходы D-триггеров 20 управления непосредственно подключены к входам управляемых ключей силовых каналов 2, обеспечивается независимо от режима работы включение силовых каналов, например, первого в момент времени t, второго - в момент времени t,...,N- го - в момент времени t . Отключение силовых каналов 2 обеспечивается низкими уровнями напряжения на прямых выходах триггеров 20 управления. Появление последних зависит от режима работы и определяется моментами появления низких уровней напряжения на входах R триггеров 20 управления, поступающих через диоды 18, 19 соответственно или с выхода логического элемента 2И-НЕ 16, или с выхода элемента ЗИ-НЕ 17.

Рассмотрим случай, когда управляющий сигнал на выходе компаратора 9 отсутствует (это происходит или при включении преобразователя, или при возмущающих воздействиях, отклоняющих напряжение на нагрузке значительно ниже требуемого). Например, при подключении источника 25 питания к силовым каналам 2 напряжение на нагрузке 3 равно нулю. Считаем, что источникиЕ,, Е (фиг.1) источника 14 вспомогательных напряжений включаются или раньше, или одновременно с источником 25. Напряжение, подаваемое на инвертирующий вход one рационного усилителя 29, определяется соотношением резисторов 26 и 27. Для данного режима они образуют делитель напряжения .опорного источника 11. Напряжение, подаваемое на не инвертирующий вход операционного уси лителя 29 с выхода делителя 15, равно нулю, поэтому напряжение 49 (U) на выходе интегратора 10 практически совпддают с осью времени. На неинвертирующем входе компаратора 9 напряжение, поступающее с выхода интегратора 10, меньше по уровню напряжения Unop инвертирующего входа, поступающего с выхода источника 11 порогового напряжения, поэтому на его выходе управляющий сигнал отсутствует (выходное напряжение практически равно нулю). При этом наличие низкого уровня напряжения на вторых входах логических элементов ЗИ-НЕ 17 всех N формирователей 4 обеспечива55965

ет неизменность состояния (высокого уровня напряжения) на их выходах.

Однако в каждом из N формирователей 4 ширины импульсов формируются

равномерно сдвинутые на время T/N сигналы управления силовыми каналами 2 с длительностями импульсов ty Т - ut| с коэффициентом полнения, близким к единице. Обеспечивается это в каждом из N формирователей 4 низким уровнем напряжения, поступающим с выхода логического элемента 2И-НЕ 16 через раз с вязывающий диод 18 на R-вход триггера 20 управления, например, в моменты времени tg , t, t + Т,... (на выходе первого), to, t, to, + Т,... (на выходе.второго),... 20 ом. w toM + т;... (на выходе

N-ro) - эпюры 39-41, фиг.2, пунктирные линии. На инверсных выходах Q триггеров 20 в указанные моменты времени появляются высокие уровни

25 напряжения. На каждый срез (перепад 0/1) напряжения на Q выходах триггеров 20 формирователи 22 последовательно во времени с интервалом T/N формируют сигналы сброса - положительные импульсы 45-47 (пунктирные линии) длительностью ut,,. (длительность выбирается из условия обеспечения сброса интегратора 10). Сформированные, например, в моменты времени t , t,...,to, t,, , t,,j. , ... положительные импульсы 45-47 (пунктирные линии) поступают с прямых выходов формирователей 22 через .элемент ИЛИ 8 (эпюры 48,фиг.2,пунктирная линия) и согласующий элемент 12 на вход.ключа 13 сброса, открывая его. Длительность импульса сброса bt ,j формирователей 22 обеспечивает установку интегратора 10 в.исходное состояние (эпюра 49). Сброс интегратора. 10 производится ключом 13, открываемым на интервале времени utj2 сигналом, поступающим через согласующий элемент 12 с элемента Ш1И 8 с.периодом T/N. Здесь и далее будем полагать, что характер изменения напряжения на выходе первого, второго,...., N-ro силового ключа соответствующего силового канала совпадает с характером изменения напряжения на выходе соответственно первого, второго,..., N-ro формирователя 4 (прямом выходе соответствующего триггера 30). В результа30

40

45

50

55

9.

те ключи преобразователей 2 практически открыты весь период Т коммутации и напряжение на нагрузке 3 увеличивается. По мере приближения напряжения на нагрузке 3 к установившемуся значению напряжение на выходе интегратора 10 последовательно занимает положение, совпадающее с и,, Un, и (эпюра 40) и в установившемся режиме имеет вид, представленный эпюрой 50.

Установившийся режим работы характеризуется равенством опорного напряжения и напряжения делителя Uo (UQ UQ), подаваемых на вхо схемы сравнения, совмещенной в операционном усилителей 29, работающем в режиме интегрирования благодаря емкостной обратной связи через конденсатор 30 (С). Для данного схемотехнического решения (фиг.1) параметры элементов выбираются из условия обеспечения интервала между моментами выключения силовых ключей силовых каналов 2, равного периоду

.

(1)

и

ПОР

- и,

оп .

Соотношение (1) позволяет определить входное сопротивление R,j,-j интегратора 10 при заданном С или конденсатора емкостной обратной связи при заданном RQIT Например, для С имеем

R

i

и

ПОР

см

- 01

(2)

Выбор параметров устройства согласно соотношению (2) .обеспечивает достижение вольт-секундного напряжения 50 на выходе интегратора 10, порогового значения Upop за время, равное Т T/N. При этом напряжение UQ на выходе делителя 15 равно напряжению - В момент времени t t + t, ,

Ч г + + ty,,..., t t + t,i на выход

компаратора 9 появляется управляющий сигнал - высокий уровень напряжения, поступающий на вторые входы логических элементов ЗИ-НЕ 17 всех

35596510

N формирователей-4 ширины импульсов. Полагаем, что к моменту вре-

5

0

0

0

5

0

5

t« + t.

- Т t,

- Т,

-ON --N U1 n

высокие уровни напряжения на пермени t,

вом и третьем входах элемента ЗИ-НЕ 17 присутствуют лишь в N-M формирователе 4. Поэтому на выходе ЗИ-НЕ 17 в момент времени t, появляется низкий уровень напряжения, который че- ре развязывающий диод 19 воздействует на R-вход триггера 20 и переводит его прямой выход в низкий уровень напряжения 41. Так как низкому уровню выходного сигнала прямого выхода триггера 20 соответствует выключенное состояние силового ключа каналов 2, моменту появления на прямом выходе D-триггера 20 управления N-ro формирователя 4 низкого уровня соответствует выключение управляемого ключа N-ro силового канала 2. В моменты времени t(, на инверсном выходе D-триггера 20 N-ro формировате5 ля 4 появляется высокий уровень напряжения, на фронт (перепад 0/1) которого формирователь 22 формирует на прямом выходе положительный (эпюры 47, 58), а на инверсном выходе отрицательный (эпюра 57) импульсы , длительностью л t ,. Через интервал времени t после переключения D-триггера 20 управления выходное напряжение инверсного выхода формирователя 22 N-ro формирователя 4 фрон5 том (перепадом 0/1) переводит в состояние 1 (высокий уровень напряжения) по входу С синхронизации прямой выход триггера 21 готовности первого формирователя 4 (эпюра 42). В результате высокий уровень напряжения прямого выхода D-триггера 21, разрешающий переключение D-триггера 20 первого формироват€;ля 4, поступает на третий вход элемента ЗИ-НЕ 17 с задержкой на время bt относительно oN момента времени переключения D-трнггера 20 N-ro формирователя. Этим исключается возможность одновременного переключения D-триггеров. Переключение в первом формирователе 4 D-триггера 20 управления (появление на его прямом выходе низкого уровня напряжения) происходит при одновременном присутствии высоких уровней напряжения на всех трех входах элемента ЗИ-НЕ 17. В рассматриваемый момент времени t + , высокие уровни напряжений присутствуют на

11

первом и третьем входах элемента ЗИ-НЕ 17. На втором входе элемента ЗИ-НЕ 17 высокий уровень напряжени появляется через интервал времени T/N относительно момента времени t|, т.е. в момент времени t. Указанное напряжение поступает с выхода компаратора 9 и обусловлено тем что за интервал времени T/N (с момента t) напряжение на выходе интегратора 10, подаваемое на инвер

тирующий вход компаратора 9, достигает в момент времени Ц напряжения , подаваемого на инвертирующий вход компаратора 9 от источника 11 порогового напряжения (эпюра 50), Одновременное присутствие высоких уровней напряжения на трех входах элемента ЗИ-НЕ 17 первого формирователя 4 в момент времени t , приводит к появлению на его выходе низкого уровня напряжения. Указанный низкий уровень напряжения поступает через развязывающий диод 19 на вход R-три гера 20 управления и устанавливает его по прямому выходу в состояние О (низкий уровень напряжения) и по инверсному выходу - в 1 (высокий уровень напряжения). На фронт (положительный перепад напряжения 0/1) инверсного выхода D-триггера 20 управления формирователь 22 формирует импульсы сброса. Сформированный с момента t положительный импульс 45 сброса поступает с прямого выхода формирователя 22 через элемент ИЛИ 8 (эпюра 48) и согласующий элемент 12 на вход ключа 13 сброса и открывает его. Длительность импульса сброса At формирователей 22 выбирается из условия установки интегратора 10 в исходное состояние (эпюра 50). Кроме того, в момент времени t, сигнал (положительный импульс) с прямого выхода формирователя 22 поступает на один из- входов элемента 2И-НЕ 24. Если на втором входе элемента 2И-НЕ 24 присутствует также положительный уровень напряжения, подаваемый через элемента 23 задержки с прямого выход D-триггвра 20 управления второго фомирователя 4, то на выходе элемента 2И-НЕ 24 появляется низкий уровень напряжения. Для рассматриваемого режима работы в момент времени 11 н прямом выходе D-триггера 20 управления второго формирователя 4 присут

ствует высокий уровень напряжения 40. Поэтому появившийся на выходе элемента 2И-НЕ 24 низкий уровень напряжения переводит по прямому выходу D-триггер 21 готовности первого формирователя 4 в низкий уровень напряжения (состояние О). Низкий уровень напряжения, поступая с D- триггера 21 готовности на третий вход элемента ЗИ-НЕ 17, исключает с момента времени t прохождение сигнала управления через элемент ЗИ-НЕ 17 на вход R D-триггера 20 управления

5 первого формирователя 4.

Таким образом, в момент времени t в первом формирователе 4 появляется низкий уровень напряжения на прямом выходе D-триггера 20 управления

0 (и выключается управляемый силовой ключ первого силового канала 2), происходит сброс интегратора 10 напряжения в исходное состояние, формирование D-триггером 21 готовности

5 сигнала, запрещающего прохождение сигнала управления с компаратора 9 на D-триггер 20 управления. С момента времени t до момента времени t + „ на прямых выходах всех N D-триггеров 21 готовности присутствуют сигналы 42-44 (низкие уровни напряжений), запрещающие прохождение сигнала управления на входы R D-триггеров 20 управления. В момент време- t + ле„г, фронтом (перепадом 0/1)

0

5

0

5

0

5

ни

заднего фронта отрицательного импульса, поступающего с инверсного выхода формирователя 22 первого формирователя 4 на вход С синхронизации D-триггера 21 второго формирователя 4, производится перевод прямого выхода D-триггера 21 готовности из низкого уровня напряжения (состояние О) в высокий (состояние 1). Появление высокого уровня напряжения на прямом выходе D-триггера 21 управления (и на третьем входе элемента ЗИ-НЕ 17) второго формирователя 4 подготавливает формирователь 4 к формированию сигнала выключения управляемого силового ключа второго силового канала 2. Появление высоких ; уровней напряжения на прямых выходах D-триггеров 21 готовности в каждом следующем формирователе 4 относительно предыдущего обеспечивается с задержкой на время (эпюры 42-44). Этим исключается одновременное переключение D Триггеров 20 управления

13.

в нескольких формирователях 4. Дале происходят аналогичные процессы во втором, третьем,,.., N-M формирователях 4 ширины импульсов. При этом обеспечивается последовательно через интервал времени T/N выключение управляемых силовых ключей второго, третьего,..,, (N-1)-ro, N-ro сило

вого каналов 2 в моменты времени

II I I tj ,... . ,tf, , t соответственно

(эпюра 50). Таким образом обеспечиваются в установившемся режиме равномерно сдвинутые электрические процессы в силовых каналах 2 с длительностью tf,.

Увеличение (уменьшение) напряжения на нагрузке 3 приводит к увеличению (уменьшению) скорости изменения выходного напряжения интегратора 10, которое достигает порогового уровня в рассматрива.емом (1+1)-м

периоде за время &t

1 + 1

L.

1 + 1

; (где

меньшее (большее) периода Т

t,.i ).

20 входа выше напряжения и, инвертирующего входа (эпюра 61). Кроме то го, на третьем входе элемента ЗИ-НЕ 17 первого формирователя 4 присутствует высокий уровень напряжения

моменты времени, со- 25 59, и он подготовлен к формированию

ответствующие выключению силового ключа соответствующего силового канала 2 в (i+1)-M и i-M периодах коммутации соответственно). Обусловлено это тем, что и - U О при достижении выходным напряжением интегратора 10 порогового уровня, задаваемого источником 11, следователь но

.

1 + 1

1

R,C

(и.

- и,) dt

(3)

и

ПОР

- и.

в результате длительность открытого состояния силового ключа преобразователя 2 в рассматриваемом интервале времени уменьшается (увеличивается) , уменьшая (увеличивая) напряжение на нагрузке 3. Установившийся процесс возможен лишь при Uor, Un, когда ., Тр,, т.е. при установлении напряжения на нагрузке 3 исходной величины.

При сигналах управления, соответствующих на выходах формирова- телей 4 длительностям импульсов, меньшим длительности интервала временного сдвига Tj.,, функционирование в известном устройстве нарушается. Для указанного случая на фиг.З при14

ведены временные диаграммы, иллюстрирующие принцип работы известного устройства в интервале времени t - - tg и предлагаемого устройства в интервале времени tg t, для . В момент времени t t положительный фронт выходного сигнала логического элемента 2И-НЕ 16 (эпюра

51, фиг.З) первого формирователя 4 переводит прямой выход D-триггера 20 управления в высокий уровень напряжения (эпюра 53). В указанный момент времени присутствует .высокий

уровень напряжения на выходе компаратора 9 (следовательно, и на вторых входах логических элементов ЗИ-НЕ 17 формирователей 4), так как напряжение его не инвертирующего

входа выше напряжения и, инвертирующего входа (эпюра 61). Кроме того, на третьем входе элемента ЗИ-НЕ 17 первого формирователя 4 присутствует высокий уровень напряжения

5

сигнала выключения, а на третьем входе элемента ЗИ-НЕ 17 второго формирователя 4 - низкий уровень напряжения 60, и он не подготовлен к форми0 рованию сигнала выключения. Одновременное присутствие высоких уровней напряжения на всех трех входах элемента ЗИ-НЕ 17 первого формирователя наступает в момент появления высокого уровня напряжения на прямом выходе D-триггера 20 управления (следовательно, и на первом входе элемента ЗИ-НЕ 17). Это приводит к появлению низкого уровня напряжения

Q на вьгходе указанного элемента ЗИ-НЕ 17, воздействие которого через развязывающий диод 19 на R-вход D-триггера 20 переводит его. прямой выход в:низкий уровень напряжения. В .ре зультате длительностью л t положительного импульса 53 на прямом выходе D-триггера 20 управления определяется скорость прохождения сигнала через элемент. ЗИ-НЕ 17, диод

Q 19 и непосредственно D-триггер 20. Причем, в зависимости от используемой элементной базы может оказаться, что элем€ нт ЗИ-НЕ 17 переключается на высоком уровне напряжения,

g существенно меньшем,чем напряжение источника питания. При этом амплитуда положительного импульса на прямом выходе (следовательно, и амплитуда отрицательного импульса на инверсном

15

выходе) D-триггера 20 управления может оказаться существенно меньшей, чем при больших длительностях импульсов. Формирователь 22 формирует импульсы на фронт (перепад напряжения 0/1) сигнала инверсного выхода D-триггера 20 управления. Однако ,из-за указанных причин данный сигнал может оказаться недостаточен по величине, и устойчивость работы нару- 1пается. Для устранения указанного недостатка сигнал с прямых выходов D-триггеров 20 управления в каждом формирователе 4 подается на первый вход элементов ЗИ-НЕ 17 через элементы 23 задержки.

Однако полагаем, что используемая элементная база такова, что указанного нарушения в работе не происходит и формирователь 22 формирует импульсы длительностью Л t ,.,2 э инверсном выходе низкого уровня (эпюра 55) и на прямом выходе высокого уровня (эпюра 56) напряжения. Сигнал инверсного выхода формирователя 22, воздействуя на R-БХОД D-триггера готовности, переводит его прямой выход в низкий уровень напряжения 59. Указанный сигнал поступает на третий вход элемента ЗИ-НЕ 17 и запрещает формирование сигнала выключения первому формирователю 4. Но сигнал инверсного выхода D-триггера 20 фронтом (перепадом 0/1) переключает по входу С синхронизации D-триггер 21 готовности второго формирователя 4. В указанный момент времени на входы элемента ЗИ-НЕ 17 второго формирователя подаются высокие уровни напряжений: на первый вход - с прямого выхода В-триггера 20 управления (эпюра 54); на второй вход - с выхода компаратора 9. Поэтому появившийся на прямом выходе D-триггера 21 готовности высокий уровень напряжения 60 через время ut (определяемое элементом задержки) поступает на третий вход элемента ЗИ-НЕ 17 и переводит его выхода в низкий уровень Напряжения. Низкий уровень напряжения в указанный момент времени с вы хода элемента ЗИ-НЕ 17 поступает через развязывающий диод 19 на R-вход D-триггера 20 управления второго формирователя и переключает его прямой выход в низкий уровень напряжения 54. На его инверсном выходе по- является высокий уровень напряжения

55965 .

на фронт (перепад 0/1) которого переключается D-триггер 21 готовности первого формирователя 4 (на выходе появляется высокий уровень напряжения 59), и формируются импульсы 57 и 58 формирователем 22. В первом формирователе 4 положительньм уровень напряжения с выхода D-триггера

1Q 21 готовности (эпюра 59) поступает на третий вход элемента ЗИ-НЕ 17. Сформированный во втором формирователе 4 формирователем 22 положительный импульс обеспечивает сброс ин15 тегратора 10 напряжения в исходное состояние (при этом напряжение на неинвертирующем входе компаратора достигает величины эпюра 61). В момент времени t t 2&t,. +

2Q + 2uty + tg напряжение на неинвертирующем входе компаратора 9 достигает значения , что обеспечивает появление на его выходе (и на вторых входах элементов ЗИ-НЕ 17 обоих

25 формирователей 4) высокого уровня напряжения. Однако это не приводит к появлению на выходах элементов ЗИ-НЕ 17 низких уровней напряжения, так как не на всех их входах присутству30 ют высокие уровни напряжения. Низкие уровни напряжения присутствуют в первом формирователе 4 на первом вхо- входе элемента ЗИ-НЕ 17 (подается с прямого выхода D-триггера 20 управления; эпюра 53), во втором формирователе 4 - на третьем входе элемента ЗИ-НЕ 17 (подается с выхода D- триггера 21 готовности; эпюра 60) и на первом входе элемента ЗИ-НЕ 17

Q (подается с прямого выхода D-триггера 20 управления; эпюра 54).

В момент t to + Т„ (Т Т/2) во втором формирователе 4 сигнал с выхода элемента 2И-НЕ 16 фронтом (перепадом 0/1) переводит прямой выход D-триггера 20 управления в высокий уровень напряжения 54. Указанный уровень напряжения, поступая на первый вход элемента ЗИ-НЕ 17, не изменяет состояния его выходного

35

45

50

сигнала, так как на его третьем входе присутствует низкий уровень напряжения 60. В момент времени t. to + Т, . to + 21,... процессы протекают аналогично моменту t t j (эпюры 51-61). В течение последующих периодов работы процессы протекают аналогично описанному выше. В результате в известном устройстве

171

первый формирователь 4 формирует сигнал (эпюра 53) согласно сигналу управления (рассогласования), а второй формирователь 4 формирует сигнал (эпюра 54) с ошибкой (вместо длительности at о получается ) , Это приводит, с одной стороны, к погрешности процесса регулирования, с другой стороны, к перегрузке по току в силовых каналах, если не принимаются меры по ограничению сигнала рассогласования на уровне, обеспечивающем регулирование с длительностями импульсов t Т„.

Указанные недостатки устранены в предлагаемом устройстве. Временные диаграммы, иллюстрирующие принцип работы предлагаемого устройства,приведены на фиг.З с момента времени t . tg. В момент времени t tg исходное состояние элемен.тов предлагаемого устройства аналогично состоянию известного в момент времени t t, а именно: на выходе ксЯипара- ,тора 9 (а следовательно, и на вторых входах логичес ких элементов ЗИ-НЕ 17 обоих формирователей 4) присутствует высокий уровень напряжения в соответствии с наличием на его входах напряжений U j и (эпюра 61); на третьем входе элемента ЗИ-НЕ 17 первого формирователя 4 .присутствует высокий уровень напряжения, поступающий с выхода D-триггера 21 готовности (эпюра 59) ; на третьем входе элемента ЗИ-НЕ 17 второго формирователя 4 присутствует .низкий уровень напряжения, поступающий с выходу D-триггера готовности (эпюра 60).

В момент времени t tg + t на всех трех входах элемента ЗИ-НЕ 17 первого формирователя 4 присутствуют высокие уровни напряжения. Так как в момент времени t tg сигнал с выхода элемента 2И-НЕ 16 фронтом (перепадом 0/1, эпюра 51) переводит прямой выход D-триггера управления в высокий уровень напряжения (эпюра 53).

Наличие элемента.23 задержки приводит к тому, что высокий уровень напряжения с прямого выхода D-триггера 20 управления первого формирователя 4 проходит на первый вход эле мента ЗИ-НЕ 17 с задержкой (относительно времени t t) на величину At з (время Гаука), которая определяется постоянной времени эле5396518

мента 23 задержки. Поэтому лишь в момент времени t tg + на всех трех входах элемента ЗИ-НЕ 17 присутствуют высокие уровни напряжения, приводящие к появлению на его выхода низкого уровня напряжения. Последний, воздействуя через развязывающий диод 19 на R-вход D-тригге- Q pa 20 управления, переводит его прямой выход в низкий уровень напряжения 53. В момент времени t tg + + At инверсном выходе D-триггера 20 управления первого формирова- д теля 4 появляется высокий уровень напряжения, на фронт (перепад 0/1) которого формирователь 22 формирует импульсы длительностью низкого уровня (эпюра 55) на инверсном выходе и высокого уровня напряжения (эпюра 56) на прямом выходе. В интервале времени tg + t2J : t 4 tg +

20

+ 4t 25 ,22 на обоих входах элемента 2И-НЕ 24 присутствуют высо- 25 кие уровни напряжения, поступающие

с прямого выхода формирователя 22 и прямого выхода D-триггера 20 управления второго формирователя 4 (эпюра 54). Поэтому в первом формирова- 2Q теле 4 появившийся на выходе элемента 2И-НЕ 24, низкий уровень напряжения в момент времени t tg + перводит выход D-триггера 21 готовности в низкий уровень напряжения. Сигнал с прямого выхода формирователя 22 обеспечивает установку интегратора напряжения в исходное состояние, начиная с момента времени t tg и кончая моментом времени t

35

40

та времени t

tg + момен+ kt

23

+

чг

напряжение на выходе интегратора 10 напряжения (и на неинвертирующем входе компаратора 9) изменяется по линейному закону. В момент времени t tg + + t.t t, напряжение на неинвертирующем входе компаратора 9 достигает величины

и

ПОР

(эпюра 61) и на его выходе (сле

довательно, на вторьпс входах обоих элементов ЗИ-НЕ 17) появляется высокий уровень напряжения. Так как в момент времени t tg + At,4, + + . обеспечивается высокий уровень напряжения на выходе D-триггера 21 готовности за счет воздействия фронтом (перепадом О/1) поступающего с первого .формирователя 4 выходного сигнала формирователя 22,

19

Ч +

+

то в момент времени t + &t,j. + &t, на всех трех входах элемента ЗИ-НЕ 17 присутствуют высокие уровни напряжения. Поэтому появившийся на его выходе низкий уровень напряжения в указанный момент времени воздействием через развязывающий диод -19 переключает прямой выход D-триггера управления второго формирователя 4 в низкий уровень напряжения. На инверсном выходе указанного D-триггера появляется высокий уровень напряжения, на фронт (перепад напряжения 0/1) которого формируются импульсы 57 и 58 на выходе формирователя 22.. При этом обе- спечивается сброс интегратора напряжения сигналом прямого выхода формирователя и установка высокого уровня напряжения на выходе D-триггера 21 готовности первого формирователя 4 фронтом (перепадом 0/1) сигнала с инверсного выхода формирователя 22. В момент времени t tg + t +

+ 2kt,

напряжение на неин22 - .

вертирующем входе компаратора 9 до-- стигает величины и на его выходе (а также на вторых входах обоих элементов ЗИ-НЕ 17) появляется высокий уровень напряжения. Однако это не изменяет высокие уровни напряжения на выходах обоих элементов ЗИ-НЕ 17, так как в это время на их первых входах присутствуют низкие уровни напряжения, подаваемые с прямых выходов D-триггеров 20 управления (эпюры 53 и 54). Высокий уровень напряжения появляется на первом входе элемента ЗИ-НЕ 17 второго формирователя 4 в момент времени t

Ч

+ Т„ + U t

1Ъ

так как на прямом

выходе D-триггера 20 управления вто-- рого формирователя появляется высокий уровень напряжения за счет воздействия в момент времени t tg + + Tj выходного сигнала элемента 2И-НЕ 16 (эпюра 52). Это приводит во втором формирователе 4 к появлению низ.кого уровня на выходе элемента ЗИ-НЕ 17, который, воэдействуя через ди|ОД 19 на R-вход D-триггера 20 управления, переводит его прямой выход в низкий уровень напряжения. На его инверсном выходе появляется высокий уровень напряжения, на фронт (перепад напряжения 0/1) которого формирователь 22 формирует положительный импульс 58, используемый для ус35596520

тановки интегратора 10 в исходное состояние (эпюра 61), и отрицательный импульс (эпюра 57), задний фронт которого (перепад 0/1) используется при длительностях импульсов t Тр для установки высокого уровня на выходе D-триггера 21 готовности следующего (в данном случае первого) формирователя 4. В рассматриваемом

20

10

случае ty Т, и на выходе D-триггера 21 готовности первого формирователя 4 присутствует высокий уровень напряжения, поэтому воздействие

g указанного импульса не изменяет состояния D-триггера 21 готовности. Кроме того, положительный импульс формирователя 22 воздействует на один из входов элемента 2И-НЕ 24. Однако при длительностях импульсов ty Т на выходе D-триггеров 20 управления воздействие импульса формирователя 22 на элемент 2И-НЕ 24 не изменяет состояние его выходного

25 сигнала (высокого уровня напряжения, эпюра 60), так как на втором его выходе присутствует низкий уровень напряжения, поступающий с прямого выхода D-триггера 20 управления предыдущего (в данном случае первого) формирователя 4.

С момента времени t t g аналогичные процессы происходят в первом формирователе 4 (фиг.З), далее с момента t , - во втором, с момента t ) в первом и т.д.

При длительностях импульсов на вы- выходах D-триггеров 20 управления t| Т| (N 2) процессы в предлагаемом устройстве протекают аналогично описанному, выше общему случаю управления фазами (N 2). Это иллюстрируют приведенные на фиг.З.временные диаграммы (для наглядности изображены с большей амплитудой, чем в случае t „ Т) .

Таким образом, в предлагаемом устройстве обеспечивается функционирование стабилизированного многофазного импульсного преобразователя как

30

35

40

45

50

t

так и с

t« т„,

Это по55

зволяет улучшить качество процесса регулирования.. При этом улучшается как скорость обработки возмущающего воздействия, так и устойчивость электрических процессов многофазного преобразователя как системы автоматического регулирования. Этому спо21

собствует и более широкий диапазон регулировочной характеристики устройства. При этом независимо от режима работы обеспечивается сброс интегратора в исходное состояние в каждый период. Это исключает накопление ошибки, а наличие интегратора обеспечивает астатическое регулирование. При этом увеличивается точ- ность процесса регулирования в переходном и установившемся режимах. Формула изобретения Стабилизированный многофазный импульсный преобразователь постоянного напряжения, содержащий N силовых каналов с управляемыми силовыми ключами, входы и выходы указанных силовых каналов соединены соответственно с входными и выходными выводами параллельно или последовательно, и блок управления, включающий генератор тактовых импульсов, формирователь строб-импульсов синхронизации, интегратор напряжения, ключ сброса, согласующий элемент, компаратор, логический элемент ИЛИ с N входами, распределитель импульсов, N формирователей ширины импульсов, источник опорного и порогового напряжений, источник вспомогательных напряжений, делитель выходного напряжения, каждый формирователь ширины импульсов содержит D-триггер управления, формирователь импульсов сброса, логические элементы 2И-НЕ и ЗИ-НЕ, два развязывающих диода, D-триггер готовности и элемент задержки, при этом один из входов элемента 2И-НЕ каждого из N формирователей ширины импульсов подключен к одному из N выходов распределителя импульсов, другой вход указанного элемента подключен к выходу общего для всех N формирователей ширины импульсов формирователя строб-импульсов синхронизации, а выход непосредственно подключен к входу С синхронизации D- триггера управления и через развязывающий диод - к R-входу D-триггера управления, который указанным входом через другой развязывающий диод подключен к выходу элемента ЗИ-НЕ, второй вход которого подключен к выходу общего для всех N формирователей ширины импульсов компаратора, инверсный выход D-триггера управления подключен к входу формирователя импульсов сброса D-Бходы D-триггеров

10

15

335965 22

управления и готовности всех N формирователей ширинь импульсов подключён к первому выходу источника вспомогательных напряжений, прямой выход формирователя импульсов сброса каждого из N формирователей ширины импульсов подключен к соответствующему входу элемента ИЛИ, выход которого через согласующий элемент подключен к входу ключа сброса, первый вход . компаратора соединен с выходом интегратора напряжения, а второй - с первым выходом источника опорного и порогового напряжений, второй выход которого соединен с первым входом интегратора напряжения, соединенного вторым входом с выходом делителя выходного напряжения, ключ сброса подключен параллельно выходу интегратора напряжения, выход генерато- .ра тактовых импульсов подключен к входам формирователя строб-импульсов синхронизации и распределителя 25 импульсов, выходы D-триггеров управления первого, второго,..., N-ro формирователей ширины импульсов подключены к входам первого, второго,. .., N-ro силовых каналов,входы делителя выходного напряжения подключены к ВЕ 1ходным выводам, цепи

20

30

питания интегратора напряжения, компаратора и согласующего элемента подключены к второму выходу источника вспомогательных напряжений, отличающийся тем, что, с целью улучшения качества процесса регулирования, в каждый из N формирователей ширины импульсов введен второй логический элемент 2И-НЕ, при этом о дин из входов указанного логического элемента подключен к прямому выходу формирователя импульсов сброса, другой вход через элемент задержки - к прямому выходу D-триггера управления следующего формирователя ширины импульсов, а выход - к R-входу D-триггера готовности, в каждом из N формирователей ширины импульсов прямой выход D- триггера управления подключен через элемент задержки к первому входу логического элемента ЗИ-НЕ, третий вход которого подключен к прямому выходу D-триггера готовности, подключенного входом С синхронизации к инверсному выходу формирователя импульсов сброса предыдущего формирователя ширины импульсов.

5t

52 5J 5 55

Составитель А.Колоколкин Редактор И.Рыбченко Техред А.Кравчук Корректор М.Максимишинец

. ™ - -- - ------- - --- ---- - --- ------ ----..«---Заказ 5793/42 Тираж 863Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва., Ж-35, Раушская ыаб. , д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул .Проектная,4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для управления многофазным преобразователем | 1982 |

|

SU1066026A1 |

| Устройство регулирования компенсатора реактивной мощности | 1990 |

|

SU1830524A1 |

| ДИСКРЕТНЫЙ СОГЛАСОВАННЫЙ ФИЛЬТР | 2014 |

|

RU2589404C2 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265741A1 |

| Устройство для измерения механических величин | 1989 |

|

SU1737287A1 |

| Многофазный импульсный стабилизатор | 1984 |

|

SU1196830A1 |

| Многофазный импульсный стабилизатор | 1985 |

|

SU1265743A1 |

| УСИЛИТЕЛЬ МОЩНОСТИ ДЛЯ УПРАВЛЕНИЯ ИСПОЛНИТЕЛЬНЫМ ДВИГАТЕЛЕМ ПЕРЕМЕННОГО ТОКА | 1995 |

|

RU2103804C1 |

| Устройство для регулирования температуры | 1985 |

|

SU1260928A1 |

| Широтно-импульсный модулятор для управления усилителем мощности | 1989 |

|

SU1718375A1 |

Изобретение относится к электротехнике, в частности к многофазным импульсным преобразователям постоянного напряжения. Цель изобретения - улучшение качества процесса регулирования. Цель достигается введением в каждый из N формирователей -f -ЛПк (Л -Лнь§ фиг.}

| Многофазный импульсный стабилизатор постоянного напряжения | 1979 |

|

SU855639A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Устройство для управления многофазным преобразователем | 1982 |

|

SU1066026A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1987-11-30—Публикация

1986-04-16—Подача