ку фазовой синхронизации и детектору, соединенному с первым блоком квантования, формирователем сигнала рассогласования и четвертым счетчиком, подключенным к второму блоку квантования, детектору ошибок и блоку фазовой синхронизации, соединенному с детектором ошибок, вторым генератором синхроимпульсов и пятым счетчиком, подключенным к детектору .ошибок, блоку кодирования, формирователю входного сигнала и формирователю сигнала рассогласования, соединенному с детектором ошибок и шестым счетчиком, подключенным к блоку .памяти и генератору пилообразного сигнала, соединенному с первым блоком квантования, подключенным к ограничителю уровня сигнала, соединенному с вторым разделительным элементом и вторым блоком квантования, соединенным с блоком кодирования, соединенным с формирователем выходного сигнала, выход которого соединен с входом блока формирования видеосигнала, а входы формирователя выходного сигнала подключены к блоку памяти, селектору синхроимпульса, блоку разделения сигналов и детектору ошибок, соединенному с третьим блоком квантования, соединенным с ограничителем уровня сигнала, генератором пилообразного сигнала, соединенным с блоком кодирования и блоком памяти.

| название | год | авторы | номер документа |

|---|---|---|---|

| Система видеотекста | 1980 |

|

SU1172456A3 |

| Устройство для оценки контура изображения | 1981 |

|

SU1076002A3 |

| Система передачи и приема информации | 1980 |

|

SU963479A3 |

| Система асинхронной двусторонней передачи данных между передающей и приемной станциями | 1983 |

|

SU1521297A3 |

| Устройство для отображенияТЕКСТОВОй иНфОРМАции HA эКРАНЕэлТ | 1977 |

|

SU828989A3 |

| Генератор кодирующих или декодирующих байтов | 1983 |

|

SU1207407A3 |

| Устройство для формирования адресных сигналов | 1980 |

|

SU1048996A3 |

| Устройство для удвоения высоты знаков текста и их выравнивания на экране телевизионного индикатора | 1980 |

|

SU961571A3 |

| Телевизионная система | 1981 |

|

SU1306492A3 |

| Устройство воспроизведения текстовых и графических знаков на экране электронно-лучевой трубки (элт) | 1979 |

|

SU1012809A3 |

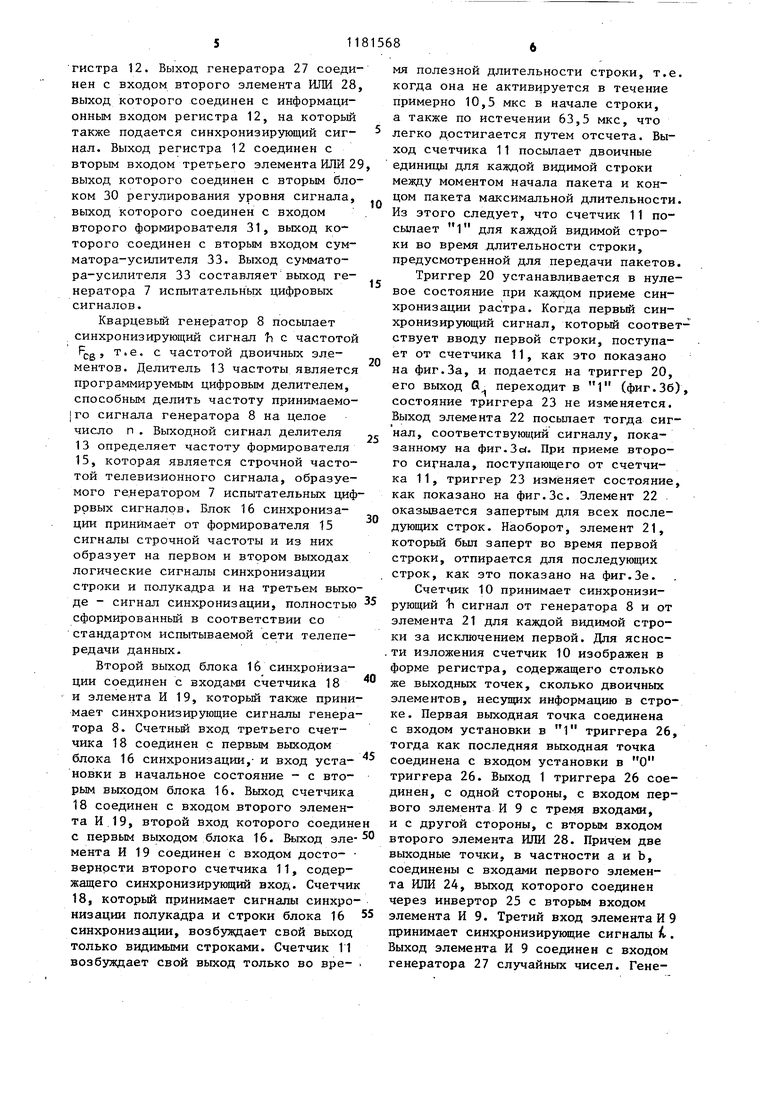

УСТРОЙСТВО ДЛЯ ОТОБРАЖЕНИЯ ТЕЛЕТЕКСТА НА ЭКРАНЕ ТЕЛЕВИЗИОННОГО ПРИЕМНИКА, содержащее демодулятор и блок формирования видеосигнала, подключенный к телевизионному приемнику, отличающееся тем, что, с целью расширения области применения устройства путем обеспечения возможности отображения глаз-диаграммы для проверки демодулятора, в него введены модулятор, генератор несущей частоты, подключенный к первому входу модулятора, преобразователь испытательных цифровых сигналов, генератор испытательных цифровых сигналов, содержащий первьй генератор синхроимпульсов, подключенный к первому элементу И, первому и второму счетчикам, сдвигающему регистру и делителю частоты, соединенному с компаратором. подключенным к первому формирователю импульсов, соединенному с блоком синхронизации, подключенным к первому блоку регулирования уровня сигнала, компаратору, третьему счетчику, второму элементу И, связанному с третьим счетчиком, первому триггеру, соединенному с третьим элементом И и элементом НЁ-И, подключенным к второму триггеру, соединенному с третьим элементом И, подключенным к второму счетчику, соединенному с вторым элементом И, и к первому счетчику, подключенному к сдвигающему регистру, третьему триггеру и первому элементу ИЛИ, соединенному через инвертор с первым элементом И, подключенным к СО третьему триггеру и генератору случайных чисел, соединенному с вторым элементом ИЛИ, связанньм с третьим триггером и сдвигающим регистром,подключенным к третьему элементу ИЛИ, подключенному к элементу НЕ-И и второму блоку регулирования уровня сиг00 нала, соединенному через второй формирователь импульсов с сумматоромО1 усилителем, подключенным к второму Од входу модулятора и первому формиро00 вателю импульсов, соединенному с первым блоком регулирования уровня сигнала, а выход модулятора подключен к входу демодулятора, преобразователь испытательных цифровых сигналов содержит первый разделительный элемент, вход которого подключен к выходу деге модулятора, а выход первого разделительного элемента подключен к видеоусилителю, соединенному с селектором синхроимпульса, вторым разделительным элементом, детектором и блоком регенерации сигналов, подключенным к бло

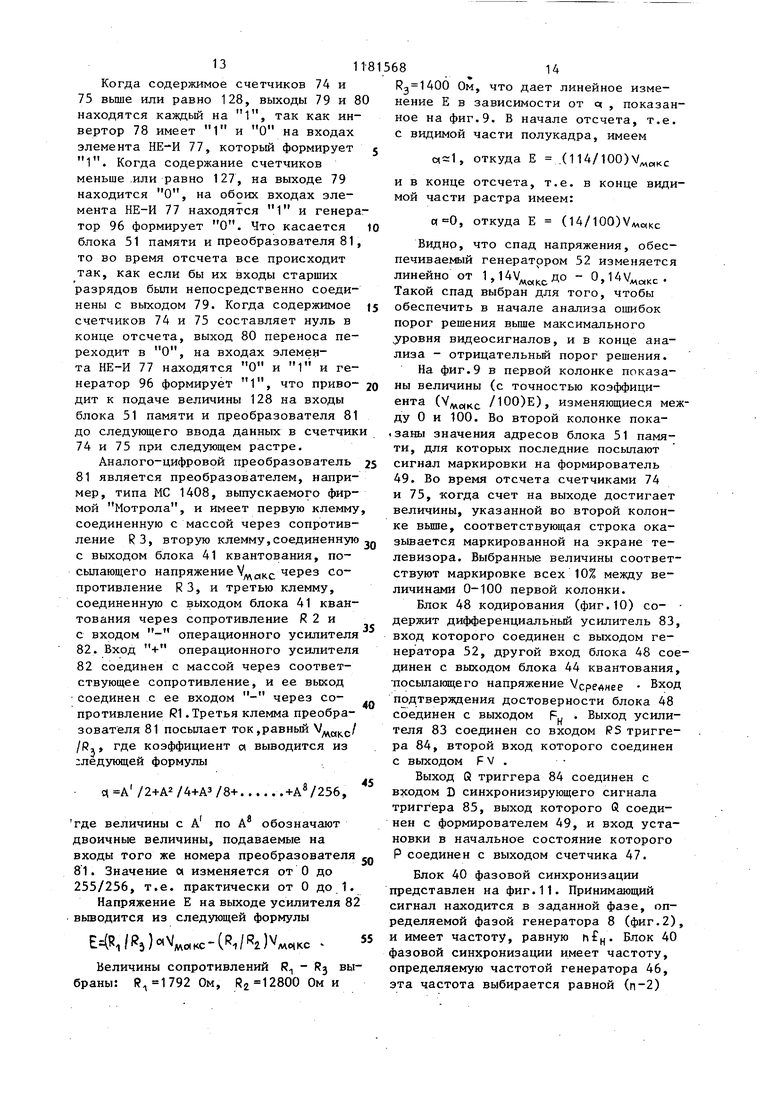

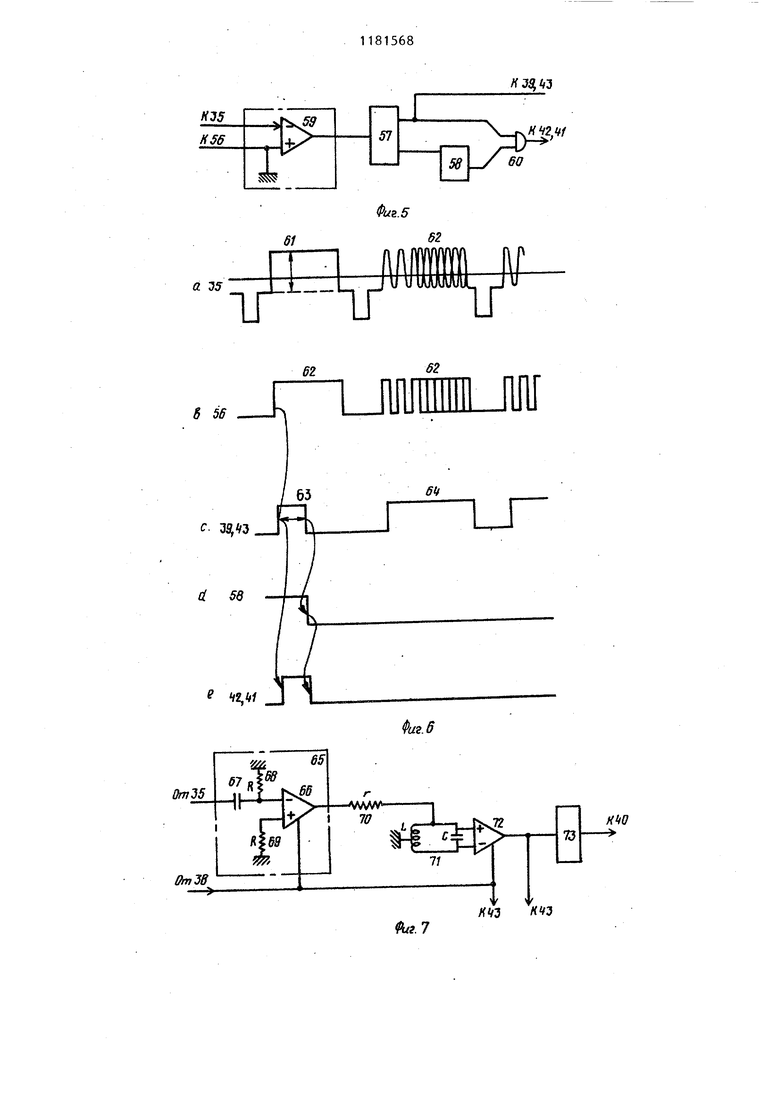

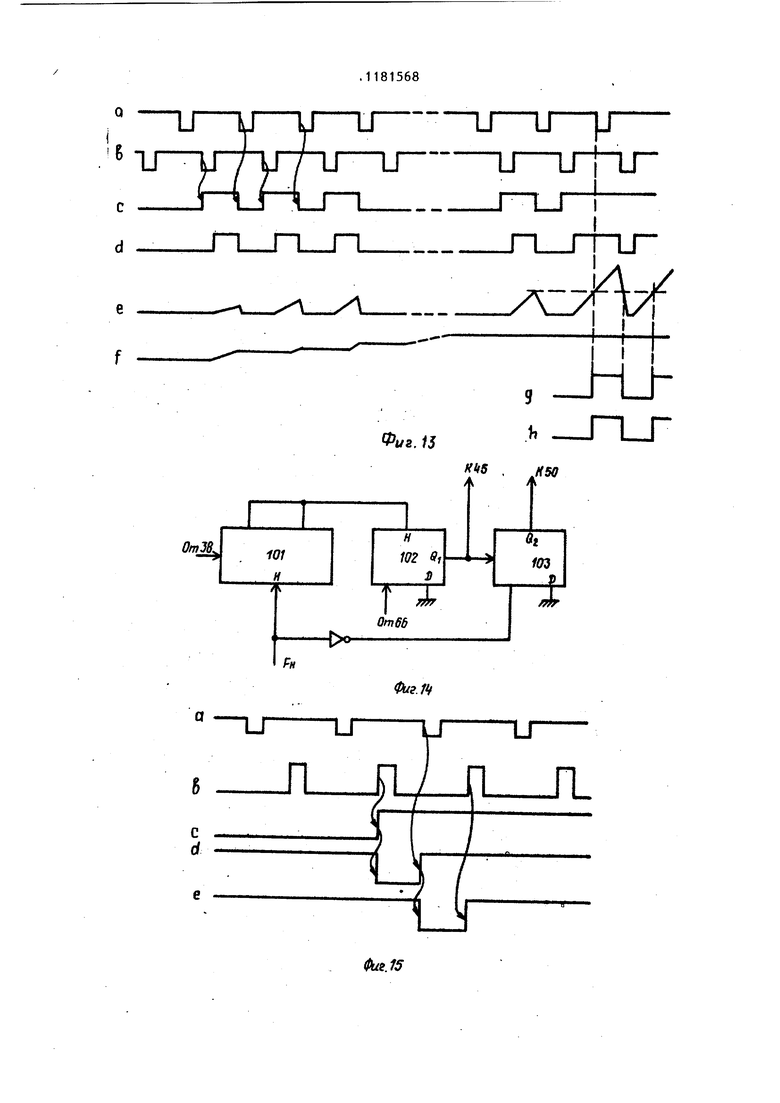

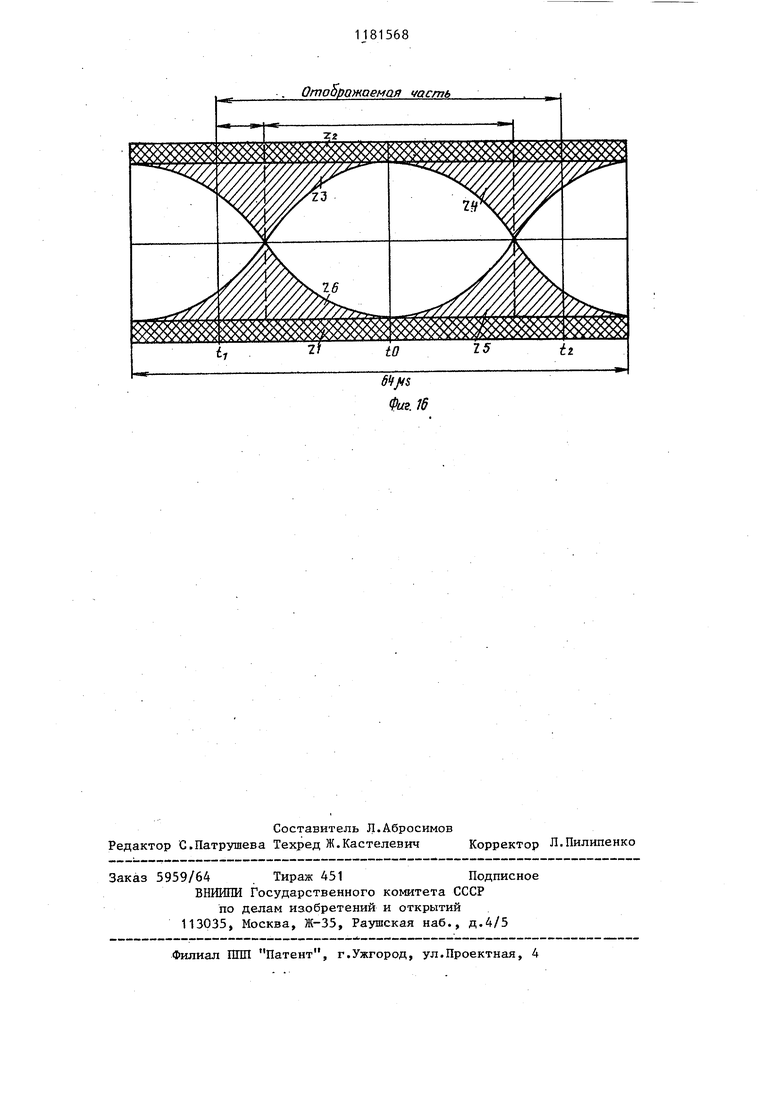

Изобретение относится к вычислительной и телевизионной технике и предоставляет собой устройство для испытания демодулятора телевизионного приемника телетекста, в котором производится индикация глаз-диаграммы на экране телевизионного приемника, что позволяет оценить качество демодулятора телевизионного приемника, так как демодуляторы составляют наиболее уязвимое звено в цепи передачи. Целью изобретения является расширение области применения устройства путем обеспечения возможности отобра жения глаз-диаграммы для проверки демодулятора. На фиг,1 представлена часть блоксхемы устройства для отображения телетекста на экране телевизионного приемника, которая участвует в формировании глаз-диаграммы; на фиг.2 блок-схема генератора испытательных цифровых сигналов; на фиг. 3 - эпюры сигналов генератора испытательньЬс цифровых сигналов; на фиг. 4 - блоксхена преобразователя ис.пытательньгх цифровых сигналов;на фиг.5 - блок-схем детектора;на фиг.6 - эпюры сигналов, соответствующих работе детектора| на фиг.7 - схема блока регенерации сигналовJ на фиг.В - схема шестого счетчика; на фиг.9 - диаграмма напряжения на выходе генератора пилообразного сигнала и его соответствия строкам телевизионного отображения; на фиг.10 - схема блока кодирования} на фиг.11 - схема блока фазовой синхронизации на фиг.12а - эпюры сигналов, поступающих на вход преобразователя испытательных цифровых сигналов-, на фиг.12в - эпюры сигналов, формируемых генератором синхроимпульсов; на фиг.13 - эпюры сигналов блока фазовой синхронизацииJ на фиг.14 схема формирователя сигнала рассогласования; на фиг.15 - эпюры сигналов формирователя сигнала рассогласования; на фиг.16 - глаз-диаграмма, отображаемая на экране телевизионного приемника. Устройство содержит телевизионньй приемник 1, демодулятор 2, блок 3 формирования видеосигнала, генератор 4 несущей частоты, модулятор 5, преобразователь 6 испытательных цифровых сигналов, генератор 7 испытательных цифровых сигналов, первый генератор 8 синхроимпульсов, первый элемент И 9, первьй счетчик 10, второй счетчик 11, сдвиганщий регистр 12, делитель 13 частоты, компаратор 14, первый формирователь 15 импульсов, блок 16 синхронизации, первый блок 17 регулирования уровня сигнала, третий счетчик 18, второй элемент И 19, первый триг31rep 20, третий элемент И 21, первый элемент НЕ-И 22, второй триггер 23, первый элемент ИЛИ 24, первьй инвертор 25, третий триггер 26, генератор 27 случайных чисел, второй элемент ИЛИ 28, третий элемент ИЛИ 29, Второй блок 30 регулирования уровня сигнала, первый формирователь 31 импульса, второй формирователь 32 импульса, сумматор-усилитель 33, первьй разделит.ельньш элемент 34, видео усилитель 35, селектор 36 синхроимпульса, второй разделительный элемент 37, детектор 38, блок 39 регенерации сигналов, блок 40 фазовой синхронизации, первьш блок 41 кванто вания, формирователь 42 сигнала рассогласования, четвертый счетчик 43, второй блок 44 квантования, селектор 45 ошибок, второй генератор 46 синхроимпульсов, пятый счетчик 47, блок 48 кодирования, формирователь 49 выходного сигнала, шестой счетчик 50, блок 51 памяти, генератор 52 пилообразного сигнала, ограничитель 53 уровня сигнала, блок 54 разделения сигналов, третий блок 55 квантования второй компаратор 56, четвертый триг гер 57, пятьй триггер 58, усилитель 59, четвертый элемент И 60, импульс 61опорной строки, полезные импульсы 62строки, импульсы 63 и 64 срабатывания триггера 57, третий компаратор 65,первьй дифференциальньй усилител 66,третий разделительньй элемент 67 резисторы 68-70,LC контур 71, второ дифференциальный усилитель 72, шесто триггер 73, первый двоичньй счетчик 74, второй двоичньй счетчик 75, пятьй элемент И 76, второй элемент НЕ-Й 77 второй 78 инвертор, выходы 79 и 80 второго двоичного счетчика 75, аналого-цифровой преобразователь 81, оп рационньй усилитель 82, третий диффе ренциальньй усилитель 83, седьмой триггер 84, восьмой триггер 85, линию 86 задержки, регистр 87, дешифра тор 88, мультиплексор 89, третий инвертор 90, третий элемент НЕ-И 91, четвертьй элемент ЙЕ-И 92, девятый триггер 93, транзистор 94, диод 95, генератор 96 тока, четвертьй компаратор 97, квантователь 98, прерьшател 99, десятьй триггер 100, седьмой счетчик 101, одиннадцатьй триггер 102, четвертый инвертор 103. Устройство для отображения телетекста содержит телевизионньй приемник 1, генератор 7 испытательных цифровых 684 сигналов, преобразователь 8 испытательных цифровых сигналов, модулятор 5 и генератор 4 несущей частоты. Видеовыход генератора 7 соединен с входом модулятора 5, несущий вход которого соединен с выходом генератора 5 несущей частоты. Высокочастотньй выход модулятора 5 соедийен с входом ВЧ испытываемого телевизионного приемника 1. Видеовыход демодулятора 2 телевизионного приемника 1 соединен с входом преобразователя 6 испытательных цифровых сигналов, выход которого соединен с видеовходом блока 3 формирования видеосигнала телевизионного приемника 1. Генератор 7 испытательных цифровых сигналов содержит кварцевый первый генератор 8 синхроимпульсов, выход которого 1i посылает синхронизирующий сигнал, который распределяется по остальным цепям генератора 7. Выход программируемого делителя 13 частоты соединен с первым входом фазового компаратора 14, выход которого соединен с управляющим входом первого формирователя 15 импульсов, выход которого соединен с входом блока 16 синхронизации. Блок 16 синхронизации имеет первый выход, которьй соединен с вторым входом фазового компаратора 14 и с входами третьего счетчика 18 и второго элемента И 19, второй выход блока 16 соединен с управляклдим входом третьего счетчика 18 и с входами двух триггеров 20 и 23, соединенных последовательно, третий выход блока 16 соединен с входом первого блока 17 регулирования уровня сигнала. Выход второго счетчика 11 соединен с входом третьего элемента И 21, выход которого соединен с входом первого счетчика 10 и с входом синхронизирующего сигнала триггеров 20 и 23. Выход первого разделительного элемента 34 соединен с первым входом сумматора-усилителя 33. Выход Q триггера 23 соединен с вторым входом третьего элемента И 21. Выход счетчика 11, выход Q Триггера 20 и выход 3 триггера 23 соответственно соединены с входами элемента НЕ-И 22, имеющего три входа, а выход элемента НЕ-И 22 соединен с входом третьего элемента ИЛИ 29. Выход первого элемента 9 соединен с входом генератора 27 случайных чисел, выход первого счетчика 10 соединен с входом установления в начальное состояние сдвигающего регистра 12. Выход генератора 27 соединен с входом второго элемента ИЛИ 28, выход которого соединен с информационным входом регистра 12, на которьй также подается синхронизирующий сиг нал. Выход регистра 12 соединен с вторым входом третьего элемента ИЛИ 29 выход которого соединен с вторым блоком 30 регулирования уровня сигнала, выход которого соединен с входом второго формирователя 31, выход которого соединен с вторым входом сумматора-усилителя 33. Выход сумматора-усилителя 33 составляет выход генератора 7 испытательньгх цифровых сигналов. Кварцевый генератор 8 посьтает синхронизирующий сигнал fi с частотой , т.е. с частотой двоичных элементов. Делитель 13 частоты является программируемым цифровым делителем, способным делить частоту принимаемоI го сигнала генератора 8 на целое число п. Выходной сигнал делителя 13 определяет частоту формирователя 15, которая является строчной частотой телевизионного сигнала, образуемого генератором 7 испытательных циф ровых сигналов. Блок 16 синхронизации принимает от формирователя 15 сигналы строчной частоты и из них образует на первом и втором выходах логические сигналы синхронизации строки и полукадра и на третьем выхо де - сигнал синхронизации, полностью сформированный в соответствии со стандартом испытываемой сети телепередачи данных. Второй выход блока 16 синхронизации соединен с входами счетчика 18 и элемента И 19, который также прини мает синхронизирующие сигналы генера тора 8. Счетньй вход третьего счетчика 18 соединен с первым выходом блока 16 синхронизации,- и вход установки в начальное состояние - с вторым выходом блока 16. Выход счетчика 18 соединен с входом второго элемента И 19, второй вход которого соедин с первым выходом блока 16, Выход эле мента И 19 соединен с входом достоверности второго счетчика 11, содержащего синхронизирующий вход. Счетчи 18, который принимает сигналы синхро низации полукадра и строки блока 16 синхронизации, возбуждает свой выход только видимыми строками. Счетчик 11 возбуждает свой выход только во время полезной длительности строки, т.е. когда она не активируется в течение примерно 10,5 МКС в начале строки, а также по истечении 63,5 мкс, что легко достигается путем отсчета. Выход счетчика 11 посылает двоичные единицы для каждой видимой строки мезвду моментом начала пакета и концом пакета максимальной длительности. Из этого следует, что счетчик 11 посылает 1 для каждой видимой строки во время длительности строки, предусмотренной для передачи пакетов. Триггер 20 устанавливается в нулевое состояние при каждом приеме синхронизации растра. Когда первый синхронизирующий сигнал, который соответствует вводу первой строки, поступает от счетчика 11, как это показано на фиг.За, и подается на триггер 20, его выход fl. переходит в 1 (фиг.36), состояние триггера 23 не изменяется. Выход элемента 22 посылает тогда сигнал, соответствующий сигналу, показанному на фиг.3с(. При приеме второго сигнала, поступающего от счетчика 11, триггер 23 изменяет состояние, как показано на фиг.3с. Элемент 22 оказьшается запертым для всех последующих строк. Наоборот, элемент 21, который был заперт во время первой строки, отпирается для последующих строк, как это показано на фиг.Зе. Счетчик 10 принимает синхронизирующий li сигнал от генератора 8 и от элемента 21 для каждой видимой строки за исключением первой. Для ясности изложения счетчик 10 изображен в форме регистра, содержащего столько же выходных точек, сколько двоичных элементов, несущих информацию в строке . Первая выходная точка соединена с входом установки в 1 триггера 26, тогда как последняя выходная точка соединена с входом установки в О триггера 26. Выход 1 триггера 26 соединен, с одной стороны, с входом первого элемента И 9 с тремя входами, и с другой стороны, с вторым входом второго элемента ИЛИ 28. Причём две вькоднью точки, в частности а и Ь, соединены с входами первого элемента ИЛИ 24, выход которого соединен через инвертор 25 с вторым входом элемента И 9. Третий вход элемента И 9 принимает синхронизирующие сигналы Л. Выход элемента И 9 соединен с входом генератора 27 случайных чисел. Генератор 27 посьшает для каждого синхро низирующего сигнала, проходящего через элемент И 9, двоичный элемент, составляющий часть случайной последо вательности. Для тактов, соответствующих выходам а и b счетчика 10, соединенным с элементом ИЛИ 24, счетчик .10 посылает тот же сигнал, что и в предшествующий момент. Перед тактом, соответ ствующим первой выходной точке, и после такта, соответствующего последней выходной точке, элемент ИЛИ 28 посылает О, так как вход элемента ИЛИ 28 соединен с выходом триггера 26, которьй вследствие этого уста навливается в нуль. В описываемом примере генератор 27 посьшает псевдослучайную последовательность из 2047 двоичных элементов,. полученных делением по модулю два многочлена единица с последующе бесконечностью нулей на многочлен Х +Х2+1. Эта последовательность не , содержится целое число раз в полукадре и дает изменяющуюся структуру. Можно фиксировать эту структуру, вно устанавливая в начальное состояние делитель в начале каждого полукадра. Сдвигающий регистр 1 2 имеет ем-: (кость два байта и содержит параллель ные входы ввода данных, соединенные поочередно с источником напряжения и массой,что позволяет вводить в него данные в виде двух октав, каждая из которых имеет следующий состав: 101010101. Начальньй вход ввода данных регистра 12 соединен с первой вы ходной точкой счетчика 10. Регистр 12, которьй принимает синхронизирующие сигналы на своем смещающем входе открьшается в сторону элемента ИЛИ 29 При каждом выходе двоичного элемента регистра 12 записывается новый двоич ньй элемент, поступающий с выхода элемента ШШ. 28, т.е. поступающий от генератора 27 или от триггера 26. Блоки 17 и 30 регулирования уровн сигнала, а также формирователи 31 и 32 являются классическими схемами в области телевидения и передачи данных. Сумматор-усилитель 33 является устройством согласования полного сопротивления. В кажцом полукадре, имея в виду видимую часть изображения, генератор 7 испытательных цифровых сигналов посьшает первую строку, полезная часть которой состоит из 1, посыпаемых триггером 23 через элемент ИЛИ 29, затем последовательность строк, полезная часть которых состоит из двух октав синхронизации двоичных элементов, затем последовательность псевдослучайных двоичных элементов. Выходной генератор 7 служит модулирующим сигналом в модуляторе 5, который посылает модулированный сигнал на вход ВЧ испытываемого телевизионного приемника 1. В последнем сигнал демодулируется в демодуляторе 2, чтобы затем подать его на вход преобразователя 6 испытательных цифровых сигналов. Преобразователь 6 содержит видеоусилитель 35, на который видеосигнал подается через первый разделительньй элемент 34, вьшолненный в виде конденсатора, и выход которого соответственно соединен с входом селектора 36 синхроимпульса, с входом второго разделительного элемента 37, выполненного в виде конденсатора С2, с входом детектора 38 и с входом блока 39 регенерации сигналов. Выход второго разделительного элемента 37 соединен с входом блока 55 квантования и с входом ограничителя 53 уровня, выход которого соединен, с входом первого блока 41 квантования и с входом второго блока 44 квантования. Выход блока 41 квантования соединен с входом генератора 52 пилообразного сигнала, выход которого соединен с управляющим входом блока 55 квантования и с управляющим вхоДОМ блока 48 кодирования. Выход блока 44 квантования соединен с входом сигнала блока 48 кодирования. Детектор 38 содержит два выхода. Первый выход детектора 38 посылает сигнал детектирования опорной строки и соединен с управлякицим входом первого блока 41 квантования и с входом установки в начальное состояние шестого счетчика 50 строк. Второй выход детектора 38 посыпает сигнал для каждой полезной строки, не считая первой, и соединен с входом установки в начальное состояние четвертого счетчика 43. Второй, выход детектора 38 также посылает сигнал достоверности и соединен с управлякнцим входом блока 39 регенерации сигналов. Четвертьм счетчик 43 содержит четыре выхода. Первьй выход счетчика 43

соединен с управляющим входом блока 4А квантования. Второй выход счетчика 43 посылает пусковой сигнал и соединен с управляющим входом селектора 45 ошибок. Третий и четвертый выходы 5 счетчика 43 посылают управляющие сигналы при различных моментах и соединены с соответствующими управляющими входами блока 40 фазовой синхронизации.О

Вход сигнала блока 40 фазовой синхронизации соединен с выходом второго генератора 46 синхроимпульсов, например кварцевого. Блок 40 фазовой синхронизации имеет еще один управляющий 15 вход, соединенный с выходом блока 39 регенерации очереди, и управляющий вход, на который подается сигнал с частотой строки F. Выход фазового блока 40 фазовой синхронизации соеди-20 нен с входом синхронизирующего сигнала селектора 45 ощибок и с входом пятого счетчика 47 двоичных элементов. Выход блока 39 регенерации сигналов также соединен с управляющим входом 25 счетчика 43

Счетчик 47 двоичных .элементов содержит три выхода. Первый выход счетчика 47 подает сигнал подтверждения 30 достоверности и соединен с управляющим входом селектора 45 ошибок и с входом установки в начальное состояние блока 48 кодирования. Второй выход счетчика 47 посылает сигнал, ука-35 зьшакщий середину строк, и соединен со схемой формирователя 42 сигнала рассогласования. Третий выход счетчика 47 соединен с входом формирователя 49 выходного сигнала, генерирую- 40 щего сигнал визуализации.

Выход селектора 36 синхроимпульса соединен с входом Формирователя 49 выходного сигнала и с входом блока 54 разделения сигналов, посьшающего на 45 свой выход сигнал с частотой строки Рц .

Выход третьего блока 55 квантова, ния соединен с информационным входом селектора 45 ощибок. Выход шестого 50 счетчика 50 строк, которьй практически содержит несколько шин, соединен с соответствукяцим входом цепи генератора 52 пилообразного сигнала и с соответствующими входами блока 55 51 памяти, выход которого соединен с входом формирователя 49 выходного сигнала.

Видеоусилитель 35 образует входно каскад, посылающий видеосигнал под очень слабым полным сопротивлением. Первьй разделительный элемент 34 видеоусилителя 35 препятствует передаче постоянной составляющей. Селектор 36 синхроимпульса выделяет из видеосигнала сигнал синхронизации, которьй вновь вводится в формирователь 49, которьй может таким образом на своем выходе формировать полньй видеосигнал для телевизионной трубки. Блок 54 разделения сигналов позволяет получать на основе полного синхросигнала сигнал с частотой строки pj , используемьй в ограничителе 53 уровня ограничения сигнала, блоке 40 фазовой синхронизации, формирователе 42 сигнала рассогласования и счетчике 50 строк.

Детектор 38 служит для детектирования первой строки, сформированной из l, а также начал пакетов. Детектор 38 (фиг.5) содержит усилитель 59, вход - которого соединен с выходом видеоусилителя 35, вход + с массой. Выход усилителя 59 соединен со входом четвертого триггера 57, выход которого Q соединен с входами блока 3 и счетчика 43 и с входом четвертого элемента И 60, выход которого соединен с входами первого блока 41 квантования и формирователя 42 сигнала рассогласования. Выход G триггера 57 соединен с входом триггера 58, выход которого U соединен с вторым входом четвертого элемента И 60.

Сигнал на фиг.ба представляет собой, образованньй в видеоусилителе 35 в момент получения опорной строки 61, сопровождаемой полезными импульсами 62 строки. Этот сигнал не содержит непрерывной составляющей.

Строка сигналов, вьщаваемая триггером 58, содержит только 1, откуда ее постоянная амплитуда. Средняя величина сигн-ала на фиг.ба обозначеня как Vf.pg,.gg . Вход + усилителя 59 находится под потенциалом массы, выход усилителя 59 формирует сигнал (фиг.бв), т.е. части сигнала, поданного вьппе средней величины. Постоянная времени триггера 57 выбирается равной нескольким микросекундам (менее 10 мкс), кроме того, триггер 57 предполагается повторно спускаемым. Из этого следует, что первая передача импульса 61 строки генерирует прямоугольньй импульс 63, длительность которого равна С постоянной времени триггера 57, однако для последующих строк триггер 57 остается в рабочем состоянии для импульсов всей строки и даже сверх того, как показывает прямоугольньй импульс 64.Задний фронт, импульса 63 деблокирует триггер 58, постоянная времени которого немного меньше длительности растра. Выходной сигнал четвер того элемента И 60 имеет вид, показанный на фиг.бе. I Блок 39 регенерации сигналов (фиг.7), содержит третий компаратор 65,состоящий из первого дифференциального усилителя 66, вход - которого соединен с выходом видеоусилителя 35 через тр,етий разделительньм элемент 67. При постоянном токе вход + соединен с массой через резистор 69, а вход - через резистор 68. Вы ход усилителя 66 соединен через резистор 70, являющийся сопротивлением связи, с .Lt контуром 71, средняя точка индуктивности L которого соединена с массой. Выводы емкости t LC контура 71 соединены соответственно с входами второго дифференциального усилителя 72. LC контур 71 настроен на 3,1 МГц для устранения составляющих шума - паразитной модуляции ширины прямоугольных сигналов. Выходы подтверждения достоверности дифференциальных усилителей 66 и 72 соединены с выходом детектора 38. Та ким образом сигнал, профильтрованный LC контуром 71, повторно квантуется в усилителе 72, выход которого соединен, с одной стороны, через шестой триггер 73 с одним устойчивым состоя нием с входом блока 40 фазовой синхронизации, и с другой стороны, к счетчику 43. Счетчик 43 представляет собой регистр сдвига с восьмью ступе нями (не показан), у которого два вы хода регистра соединены d входами элемента ИЛИ, выхой которого соединен с управляющим входом второго блока 44 квантования. Практически выход элемента ИЛИ определяет прямоугольньй сигнал времени, в течение которого блок 44 квантования определяет среднюю величину сигнала, который на нее подается в течение того же времени, третий выход регистра .счетчика 43 определяет начало ана6812лиза данных и соединен с селектором 45 ошибок. Четвертый и пятый выходы соединены с блоком 40, фазовой синхронизации. Ограничитель 53 уровня сигнала является классической схемой, позволяющей определять уровень О В для черных зон для строчных сигналов, подаваемых на блоки 41 и 44 квантования. Блок 41 квантования состоит, например, из квантователя - составителя блоков, которьй интегрирует в конденсаторе максимальную величину напряжения сигнала 61 (фиг.ба) во время длительности прямоугольного сигнала 63, который на него подается с первого выхода детектора 38. Затем блок 41 квантования подает постоянно напряжение, равное напряжению, записанному в запоминающем устройстве, в конденсаторе, т.е. максимальное напряжение . кривой 61. Блок 44 квантования содержит низкочастотный фильтр, за которым следует квантователь-составитель блоков, который приводится в действие во время прямоугольного сигнала времени, определяемое выходом первого счетчика 43. {..... Счетчик 50 строк состоит из двух двоичных счетчиков 74 и 75 с четырьмя ступенями, установленными последовательно. Входы установки в начальное состояние счетчиков соединены с выходом формирователя 42 и загружены максимально в начале каждого полукадра, т.е. для группы счетчиков в 255. Счетчик 50 также содержит пятый элемент И 76, вход которого принимает сигнал строчной частоты f и выход которого подается на вход отсчетов двоичных счетчиков 74 и 75. Выход 79 высшего разряда счетчика 75 соединен с входом инвертора 78, выход которого соединен с входом элемента НЕ-И 77, второй вход которого, как и второй вход элемента И 76, соединен с выходом 80 переноса счетчика 75. Выходы счета счетчика 74 и выходы счета счетчика 75 за исключением выхода 79 старших разрядов соединены параллельно, так что выход элемента НЕ-И 77 соединен с соответствуннцими входами блока 51 памяти и с соответствующими входами цифровых данных аналого-цифрового преобразователя 81 генератора 52 пилообразного сигнала. 131 Когда содержимое счетчиков 74 и 75 выше или равно 128, выходы 79 и 8 находятся каждый на 1, так как инвертор 78 имеет 1 и О на входах элемента НЕ-И 77, который формирует 1. Когда содержание счетчиков меньше .или равно 127, на выходе 79 находится О, на обоих входах элемента НЕ-И 77 находятся 1 и генера тор 96 формирует О. Что касается блока 51 памяти и преобразователя 81 то во время отсчета все происходит так, как если бы их входы старших разрядов были непосредственно соединены с выходом 79. Когда содержимое счетчиков 74 и 75 составляет нуль в конце отсчета, выход 80 переноса переходит в О, на входах элемента НЕ-И 77 находятся О и 1 и генератор 96 формирует 1, что приводит к подаче величины 128 на входы блока 51 памяти и преобразователя 81 до следующего ввода данных в счетчик 74 и 75 при следующем растре. Аналого-цифровой преобразователь 81является преобразователем, например, типа МС 1408, выпускаемого фирмой Мотрола, и имеет первую клемму соединенную с массой через сопротивление R3, вторую клемму,соединенную с выходом блока 41 квантования, посылающего напряжение . через сопротивление R 3, и третью клемму, соединенную с выходом блока 41 квантования через сопротивление R 2 и с входом - операционного усилителя 82. Вход + операционного усилителя 82соединен с массой через соответствующее сопротивление, и ее выход соединен с ее входом - через сопротивление R1 .Третья клемма преобразователя 81 посылает ток,равньй ,,/ /R,, где коэффициент я выводится из следующей формулы с А /2+А2 /4+Аз /8+.+AV256, ГJ) где величины с А по А обозначают двоичные величины, подаваемые на входы того же номера преобразователя 81. Значение а изменяется от О до 255/256, т.е. практически от О до 1. Напряжение Е на выходе усилителя 82 вьшодится из следующей формулы E4Ri/f 5)«VKC-(Ri/R2)VMc,KC Величины сопротивлений R - К вы браны: Ом, R2 12800 Ом и 6814 Ом, что дает линейное изменение Е в зависимости от ч , показанное на фиг.9. В начале отсчета, т.е. с видимой части полукадра, имеем с(:1, откуда Е .(114/100) и в конце отсчета, т.е. в конце видимой части растра имеем: , откуда Е (14/100)Умо,кс Видно, что спад напряжения, обеспечиваемый генератором 52 изменяется линейно от 1, - 0,14V,c. Такой спад выбран для того, чтобы обеспечить в начале анализа ошибок порог решения вьш1е максимального уровня видеосигналов, и в конце анализа - отрицательньй порог решения. На фиг.9 в первой колонке показаны величины (с точностью коэффициента (,j. /100)Е), изменяющиеся между О и 100. Во второй колонке показаны значения адресов блока 51 памяти, для которых последние посылают сигнал маркировки на формирователь 49. Во время отсчета счетчиками 74 и 75, когда счет на выходе достигает величины, указанной во второй колонке выще, соответствующая строка оказывается маркированной на экране телевизора. Выбранные величины соответствуют маркировке всех 10% между величинами 0-100 первой колонки. Блок 48 кодирования (фиг.10) со- держит дифференциальньш усилитель 83, вход которого соединен с выходом генератора 52, другой вход блока 48 соединен с выходом блока 44 квантования, посылающего напряжение Усреднее Вход подтверждения достоверности блока 48 соединен с выходом F,, . Выход усилителя 83 соединен со входом PS триггера 84, второй Вход которого соединен с выходом F V . Выход Q триггера 84 соединен с входом D синхронизирующего сигнала триггера 85, выход которого Q соединен с формирователем 49, и вход установки в начальное состояние которого Р соединен с выходом счетчика 47. Блок 40 фазовой синхронизации представлен на фиг.11. Принимающий сигнал находится в заданной фазе, определяемой фазой генератора 8 (фиг.2), и имеет частоту, равную h(. Блок 40 фазовой синхронизации имеет частоту, определяемую частотой генератора 46, эта частота выбирается равной (п-2)

. При начале передачи каждого пакета производят совмещение фазы двух импульсов, соответствующих синхронизирующим сигналам на кривых 12а, Ь, тогда имеют вдоль линии сдвиг, который изменяется линейно между двумя синхронизирующими сигналами. Назначение блока 40 фазовой синхронизации состоит в создании постоянного смещения по фазе сигналов, посьтаемых генератором 46 синхроимпульсов и блоком 39 регенерации сигналов, чтобы получать эту. начальную установку фазы. Б преобразователе 6 принимаемый сигнал подается на блоки 39 регенерации сигналов. Выход генератора 46 синхроимпульсов соединен с находящейся на входе блока 40 линией 86 задержки содержащей четыре выхода соответственно смещенных на Т/В, где Т - период генератора 46. Эти четыре выхода соответственно соединены с четырьмя входами регистра 87. Состояние этих выходов запоминается по команде, поступающей от счетчика 43, которая характёризует фазу очереди. Состояние регистра 87, декодированное дешифратором 88, адресуется мультиплексору 89, который выбирает соответствующую фазу из линии 86 задержки. Таким образом, получают предварительное фазовое смещение. Сигнал, посьшаемьй мультиплексором 89, является сигналом, фаза которого смежна с фазой очереди, по крайней мере, с точностью Т/8.

Выход мультиплексора 89 соединен с входом инвертора 90, выход которого соединен с входом элемента НЕ-И 91, выход которого соединен с входом элемента НЕ-И 92, кроме того, с вторым входом элемента НЕ-И 91 и, наконец, с входом D синхронизирующего сигнала триггера 93. Выход Q триггера 93 соединен с вторым входом элемента НЕ-И 92, вход D соединен с четвертым входом счетчика 43, вход Р установки 1 соединен с третьим входом счетчика 43 и вход RAZ соединен с выходом блока 39 регенерации сигналов. Выход элемента НЕ-И 92 соединен с базой транзистора 94, эмиттер которого соединен с массой, а коллектор соединен соответственно с анодом диода 95, с массой через конденсатор С4, с выходом гене1)атора 96 тока и входом компаратора 97. Катод диода 95 соединен с массой через конденсатор С5, с входом квантователя

98, выход которого соединен с рторым входом компаратора 97, и наконец, с контактом прерывателя 99, который управляется строчной частотой f .

Выход компаратора 97 соединен с входом одностабильного триггера 100, который посылает сигнал синхронизации приема.

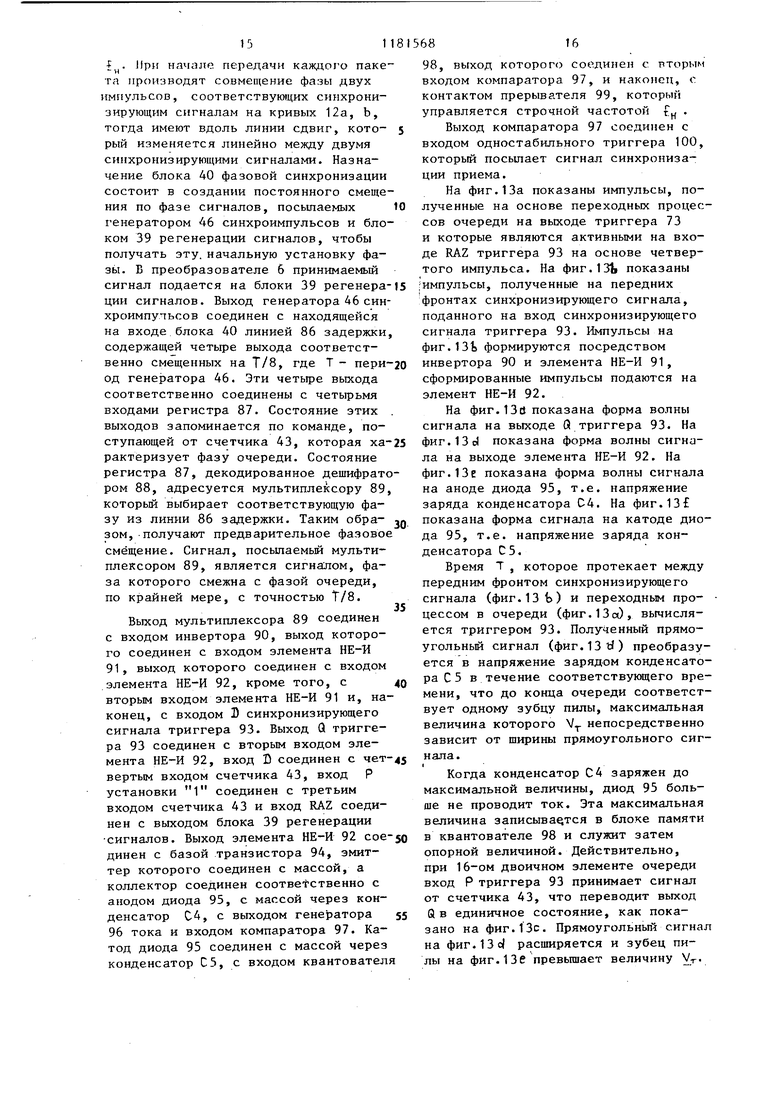

На фиг.13а показаны импульсы, полученные на основе переходных процессов очереди на выходе триггера 73 и которые являются активными на входе RAZ триггера 93 на основе четвертого импульса. На фиг.13Ь показаны .импульсы, полученные на передних фронтах синхронизирующего сигнала, поданного на вход синхронизирующего сигнала триггера 93. Импульсы на фиг.13t формируются посредством инвертора 90 и элемента НЕ-И 91, сформированные импульсы подаются на элемент НЕ-И 92.

На фиг.13а показана форма волны сигнала на выходе Q триггера 93. На фиг.13с1 показана форма волны сигнала на выходе элемента НЕ-И 92. На фиг.13Е показана форма волны сигнала на аноде диода 95, т.е. напряжение заряда конденсатора С4. На фиг.13 показана форма сигнала на катоде диода 95, т.е. напряжение заряда конденсатора С 5.

Время Т , которое протекает между передним фронтом синхронизирующего сигнала (фиг.13 fe) и переходным процессом в очереди (фиг.13о(), вычисляется триггером 93. Полученный прямоугольный сигнал (фиг.13) преобразуется в напряжение зарядом конденсатора С 5 в течение соответствующего времени, что до конца очереди соответствует одному зубцу пилы, максимальная величина которого V непосредственно зависит от ширины прямоугольного сигнала.

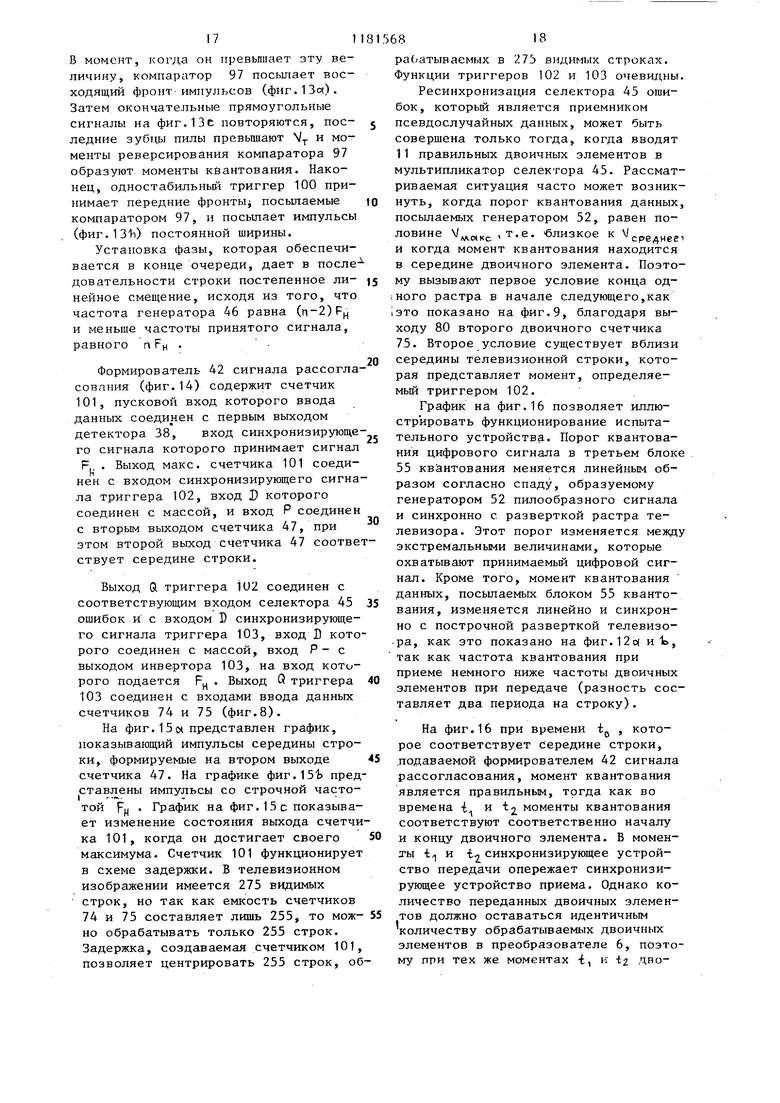

Когда конденсатор С4 заряжен до максимальной величины, диод 95 больше не проводит ток. Эта максимальная величина записывается в блоке памяти в квантователе 98 и служит затем опорной величиной. Действительно, при 16-ом двоичном элементе очереди вход Р триггера 93 принимает сигнал от счетчика 43, что переводит выход Q в единичное состояние, как показано на фиг.13с. Прямоугольньй сигнал на фиг.13с| расширяется и зубец пилы на фиг.13е превышает величину Vr171В момент, когда он превьплает эту величину, компаратор 97 посылает восходящий фронт импульсов (фиг.13о(). Затем окончательные прямоугольные сигналы на фиг.13с повторяются, последние зубцы пилы превьшагот V и моменты реверсирования компаратора 97 образуют моменты квантования. Наконец, одностабильный триггер 100 принимает передние фронты; посылаемые компаратором 97, и посьшает импульсы (фиг.ТЗЮ постоянной ширины. Установка фазы, которая обеспечивается в конце очереди, дает в после довательности строки постепенное линейное смещение, исходя из того, что частота генератора 46 равна (n-2)F, и меньше частоты принятого сигнала, равного п FH . Формирователь 42 сигнала рассогла сования (фиг.14) содержит счетчик 101, пусковой вход которого ввода данных соединен с первым выходом детектора 38, вход синхронизирующе го сигнала которого принимает сигнал F., . Выход макс, счетчика 101 соединен с входом синхронизирующего сигна ла триггера 102, вход D которого соединен с массой, и вход Р соединен с вторым выходом счетчика 47, при этом второй выход счетчика 47 соотве ствует середине строки. Выход Q триггера 102 соединен с соответствующим входом селектора 45 ошибок и с входом D синхронизирующего сигнала триггера 103, вход D кото рого соединен с массой, вход Р- с выходом инвертора 103, на вход которого подается F . Выход Q триггера 103 соединен с входами ввода данных счетчиков 74 и 75 (фиг.8). На фиг.15сч представлен график, показывающий импульсы середины строки, формируемые на втором выходе счетчика 47. На графике фиг.151 пред ставлены импульсы со строчной частотой F График на фиг.15 с показывает изменение состояния выхода счетчи ка 101, когда он достигает своего максимума. Счетчик 101 функционирует в схеме задержки. В телевизионном изображении имеется 275 видимых строк, но так как емкость счетчиков 74 и 75 составляет лишь 255, то можно обрабатывать только 255 строк. Задержка, создаваемая счетчиком 101 позволяет центрировать 255 строк, об раскатываемых в 273 видимых строках. Функции триггеров 102 и 103 очевидны. Ресинхронизация селектора 45 ошибок, который является приемником псевдослучайных данных, может быть совершена только тогда, когда вводят 11 правильных двоичных злементов в мультипликатор селектора 45. Рассматриваемая ситуация часто может возникнуть, когда порог квантования данных, посылаемых генератором 52, равен половине V. ,т.е. близкое к V АЛСТКС , СреДНве и когда момент квантования находится в середине двоичного элемента. Поэтому вызывают первое условие конца одHoro растра в начале следующего,как это показано на фиг.9, благодаря выходу 80 второго двоичного счетчика 75. Второе условие существует вблизи середины телевизионной строки, которая представляет момент, определяемый триггером 102. График на фиг.16 позволяет иллюстрировать функционирование испытательного устройства. Порог квантования цифрового сигнала в третьем блоке 55 квантования меняется линейным образом согласно спаду, образуемому генератором 52 пилообразного сигнала и синхронно с разверткой растра телевизора. Этот порог изменяется между экстремальными величинами, которые охватывают принимаемый цифровой сигнал. Кроме того, момент квантования данных, посылаемых блоком 55 квантования, изменяется линейно и синхронно с построчной разверткой телевизора, как это показано на фиг.12с( и lo, так как частота квантования при приеме немного ниже частоты двоичных элементов при передаче (разность составляет два периода на строку). На фиг.16 при времени i , которое соответствует середине строки, .подаваемой формирователем 42 сигнала рассогласования, момент квантования является правильным, тогда как во времена -t и t моменты квантования соответствуют соответственно началу и концу двоичного элемента. В моменты i К i синхронизирующее устройство передачи опережает синхронизирующее устройство приема. Однако количество переданных двоичных элементов должно оставаться идентичным количеству обрабатываемых двоичных элементов в преобразователе 6, поэтому при тех же моментах -fc, и iz дво19ичный элемент передается с двойной длительностью, что достигается элементом ШШ 24. На фиг.16.в зоне Z1, которая соответствует части спада (фиг.9) ниж О, все квантованные двоичные элемен ты очевидно равны 1, что вызывает 50% ошибок. В зоне Z2, симметрично, все квантованные элементы равны О, что также составляет 50% ошибок. В 68 зоне Z3 всегда будет присутствовать квантуемый двоичный элемент за исключением случая восходящего переходного процесса, в этом случае будет одна ошибка. В этой зоне комбинации 00, 1 1, 1 О не вызывает ошибок, .и только комбинация 01 ведет к квантованию О вместо 1. В этой зоне объем ошибок составляет 25%. Такое же положение имеет место в зонах с Z4 по Z6..

W

.г

а

II

Ни(17 -гГда134 -

i J7

S3

w

V

IT

ГЦ

г

55

45

Чв

5(

L

Ju

4«:

7

Их

Ш

с 35

и

5 5

С.

d 58

67 Hh

НVAW 7ff

Isa

т

irWi:

ffW

л

73

7Г

кчъ

кчъ

г.1

2S5

Ш Ж

J6e Пв

JOS

Ж

Ж

jW 28

MIM

о а б

K47,t(S ИТ1ПП1 1 11П1 И1111{11 ШГШЛ 1111|1ММ1и ПД ддщшдддхшд лд г./2

/MyniTf

Фиг. 15

5 , Н50

а

с d

Фие.15 . Ото5рожаемая часть М//5 Риг. 16

| СПОСОБ ОБРАБОТКИ БЕСПЛАМЕННЫМ ГОРЕНИЕМ РАДИОАКТИВНЫХ УГЛЕРОДОСОДЕРЖАЩИХ ВЕЩЕСТВ | 2008 |

|

RU2390862C2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Сплав для отливки колец для сальниковых набивок | 1922 |

|

SU1975A1 |

| Устройство для отображенияТЕКСТОВОй иНфОРМАции HA эКРАНЕэлТ | 1977 |

|

SU828989A3 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

Авторы

Даты

1985-09-23—Публикация

1980-11-21—Подача