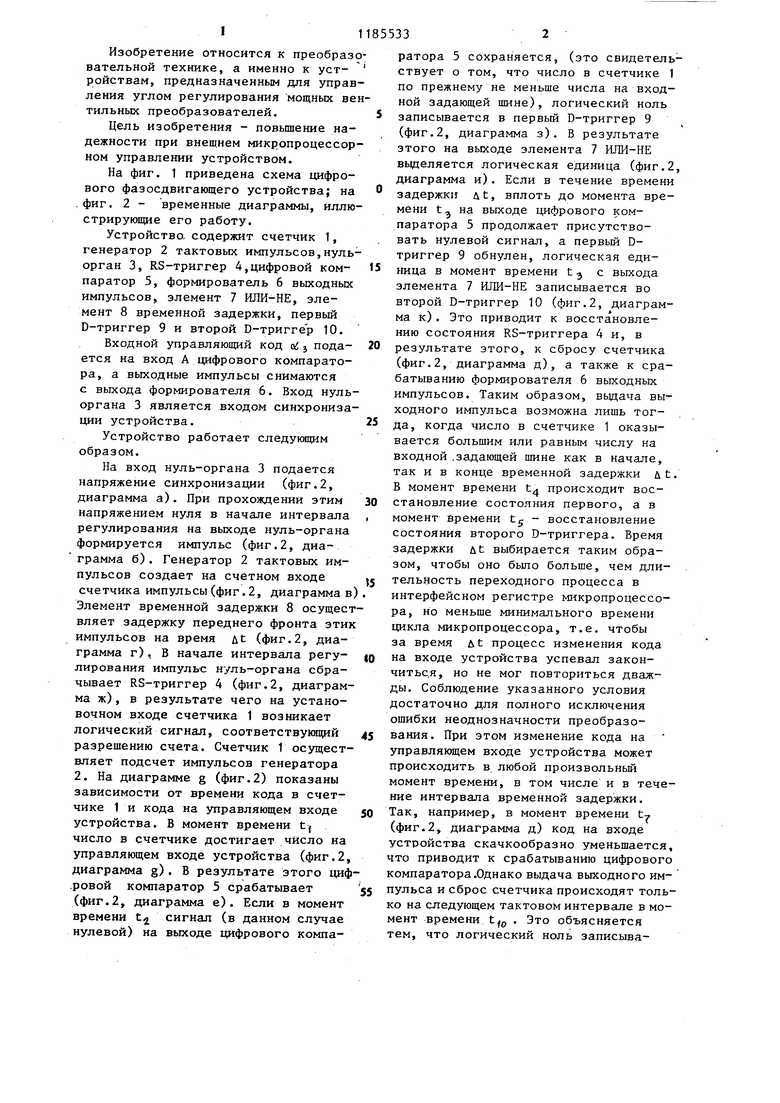

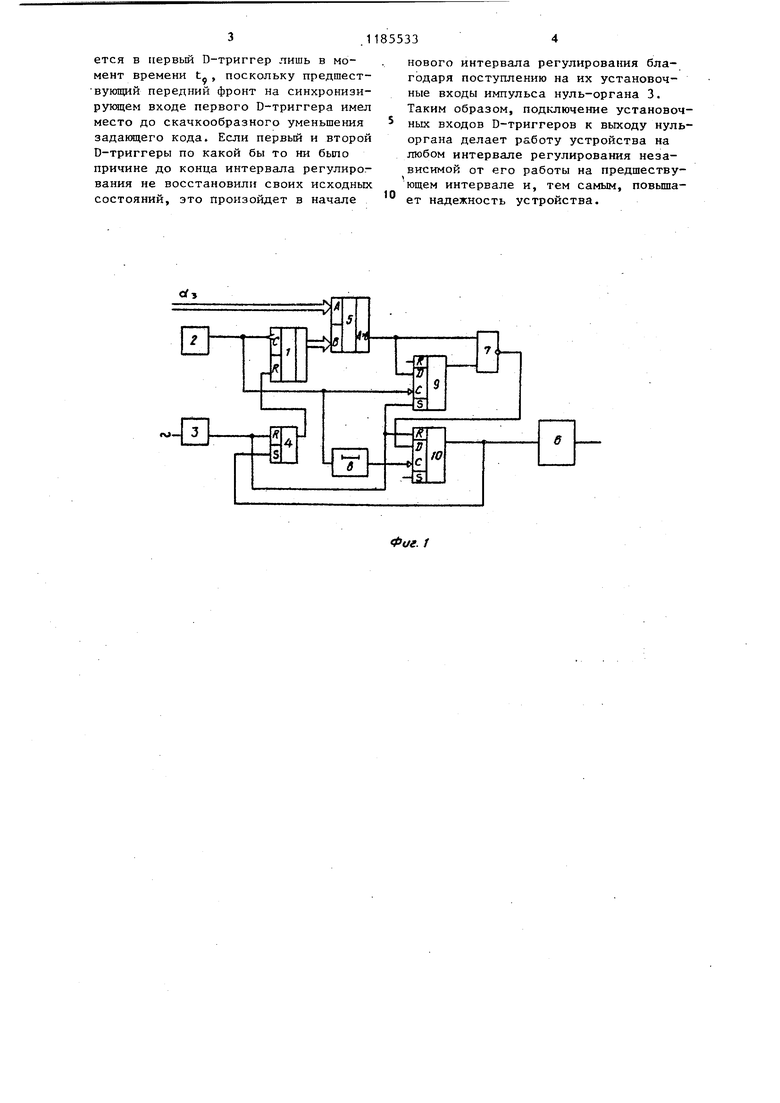

Изобретение относится к преобраз вательной технике, а именно к устройствам, предназначенным для управ ления углом регулирования мощных ве тильных преобразователей. Цель изобретения - повьппение надежности при внешнем микропроцессор ном управлении устройством. На фиг. 1 приведена схема цифрового фазосдвигающего устройства; на . фиг. 2 - временные диаграммы, иллю стрирующие его работу. Устройство, содержит счетчик 1, генератор 2 тактовьк импульсов,нуль орган 3, RS-триггер 4,цифровой компаратор 5, формирователь 6 выходных импульсов, элемент 7 ИЛИ-НЕ, элемент 8 временной задержки, первый D-триггер 9 и второй D-триггер 10. Входной управляющий код oi j подается на вход А цифрового компаратора, а выходные импульсы снимаются с выхода формирователя 6. Вход нуль органа 3 является входом синхрониза ции устройства. Устройство работает следующим образом. На вход нуль-органа 3 подается напряжение синхронизации (фиг.2, диаграмма а). При прохождении этим напряжением нуля в начале интервала регулирования на выходе нуль-органа формируется импульс (фиг.2, диаграмма б). Генератор 2 тактовых импульсов создает на счетном входе счетчика импульсы (фиг .2, диаграмма в Элемент временной задержки 8 осущес вляет задержку переднего фронта этик импульсов на время ut (фиг.2, диаграмма г).. В начале интервала регулирования импульс нуль-органа сбрачывает RS-триггер 4 (фиг.2, диаграмма ж) , в результате чего на установочном входе счетчика 1 возникает логический сигнал, соответствуклций разрешению счета. Счетчик 1 осуществляет подсчет импульсов генератора 2. На диаграмме g (фиг.2) показаны зависимости от времени кода в счетчике 1 и кода на управляющем входе устройства. В момент времени tj число в счетчике достигает число на управляющем входе устройства (фиг.2 диаграмма g). В результате этого циф .ровой компаратор 5 срабатывает (фиг.2, диаграмма е). Если в момент времени t сигнал (в данном случае нулевой) на выходе цифрового компаратора 5 сохраняется, (это свидетельствует о том, что число в счетчике 1 по прежнему не меньше числа на входной задающей шине), логический ноль записывается в первый D-триггер 9 (фиг.2, диаграмма з). В результате этого на выходе элемента 7 ИЛИ-НЕ вьщеляется логическая единица (фиг.2, диаграмма и). Если в течение времени задержки it, вплоть до момента времени t на выходе цифрового компаратора 5 продолжает присутствовать нулевой сигнал, а первый Dтриггер 9 обнулен, логическая единица в момент времени t с выхода элемента 7 ИЛИ-НЕ записывается во второй D-триггер 10 (фиг.2, диаграмма к). Это приводит к восстановлению состояния RS-триггера 4 и, в результате этого, к сбросу счетчика (фиг.2, диаграмма д), а также к срабатыванию формирователя 6 выходных импульсов. Таким образом, вьщача выходного импульса возможна лишь тогда, когда число в счетчике 1 оказывается большим или равным числу на входной .задающей шине как в начале, так и в конце временной задержки ut. В момент времени t происходит восстановление состояния первого, а в момент времени tj - восстановление состояния второго D-триггера. Время задержки ut выбирается таким образом, чтобы оно было больше, чем длительность переходного процесса в интерфейсном регистре микропроцессора, но меньше минимального времени цикла микропроцессора, т.е. чтобы за время &t процесс изменения кода на входе устройства успевал закончитьс.я, но не мог повториться дважды. Соблюдение указанного условия достаточно для полного исключения ошибки неоднозначности преобразования. При этом изменение кода на управляющем входе устройства может происходить в любой произвольньй момент времени, в том числе и в течение интервала временной задержки. Так, например, в момент времени t(фиг.2, диаграмма д) код на входе устройства скачкообразно уменьшается, что приводит к срабатыванию цифрового компаратора .Однако выдача выходного импульса и сброс счетчика происходят только на следующем тактовом интервале в момент времени . Это объясняется тем, что логический ноль записывается в первый D-триггер лишь в момент времени t-, поскольку предшествующий передний фронт на синхронизирующем входе первого D-триггера имел место до скачкообразного уменьшения задающего кода. Если первый и второй D-триггеры по какой бы то ни было причине до конца интервала регулирования не восстановили своих исходных состояний, это произойдет в начале

нового интервала регулирования благодаря поступлению на их установочные входы импульса нуль-органа 3. Таким образом, подключение установочных входов D-триггеров к выходу нульоргана делает работу устройства на любом интервале регулирования независимой от его работы на предшествующем интервале и, тем самым, повьш1ает надежность устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровое фазосдвигающее устройство | 1991 |

|

SU1787308A3 |

| АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ УГЛА | 1996 |

|

RU2115229C1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 2002 |

|

RU2252450C2 |

| Устройство для измерения характеристик сверхпроводящих образцов | 1989 |

|

SU1675789A1 |

| Аналого-цифровой преобразователь параметров диэлькометрического датчика | 1988 |

|

SU1547063A1 |

| Устройство для переключения реверсивного вентильного преобразователя | 1985 |

|

SU1374362A1 |

| ПАРАЛЛЕЛЬНЫЙ ЗНАКОВЫЙ КОРРЕЛОМЕТР | 1999 |

|

RU2174705C2 |

| СТАБИЛИЗАТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 1994 |

|

RU2072550C1 |

| ПРОТИВОУГОННАЯ СИСТЕМА | 1995 |

|

RU2093387C1 |

| Устройство для синхронизации системы управления вентилями @ -фазного преобразователя | 1986 |

|

SU1365283A1 |

ЦИФРОВОЕ ФАЗОСДВИГАЩЕЕ УСТРОЙСТВО, содержащее счетчик, цифровой компаратор, один вход которого соединен с выходом счетчика, а . другой вход является входом цифрового задания угла регулирования, генератор тактовых импульсов, выход которого соедийен со счетным входом счетчика, формирователь выходных импульсов, выход которого является выходом устройства, нуль-орган, вход которого является входом синхронизации устройства, RS-триггер, первый вход которого соединен с выходом нуль-органа, второй вход соединен с входом формирователя выходных импульсов, а выход соединен с установочным входом счетчика, и элемент ИЛИ-ИЕ, nepBbrii вход которого соединен с выходом цифрового компаратора, отличающееся тем, что, с целью повьшения надежности, в него введены первый и второй D-триггеры и элемент временной задержки, вход которого соединен с выходом генератора тактовых импульсов, а выход подключен к входу синi хронизации второго D-триггера, выход которого соединен с вторым входом (Л RS-триггера, второй вход элемента ИЛИ-НЕ соединен с выходом первого D-триггера, а выход соединен с ин- . формационным входом второго D-триггера, информационный вход первого D-триггера соединен с выходом цифрот вого компаратора, а вход синхронизации первого D-триггера подключен к выходу генератора тактовых импульсов эо причем один из установочных входов СП первого D-триггера соединен с разноел именным установочным входом второго: со D-Tpnrrejia и с выходом нуль-органа. со

Авторы

Даты

1985-10-15—Публикация

1983-12-23—Подача