Изобретение относится к измерительной технике и может быть использовано для определения характеристик сверхпроводящих образцов.

Целью изобретения является повышение точности и сокращения времени при измерении характеристик сверхпроводящих образцов.

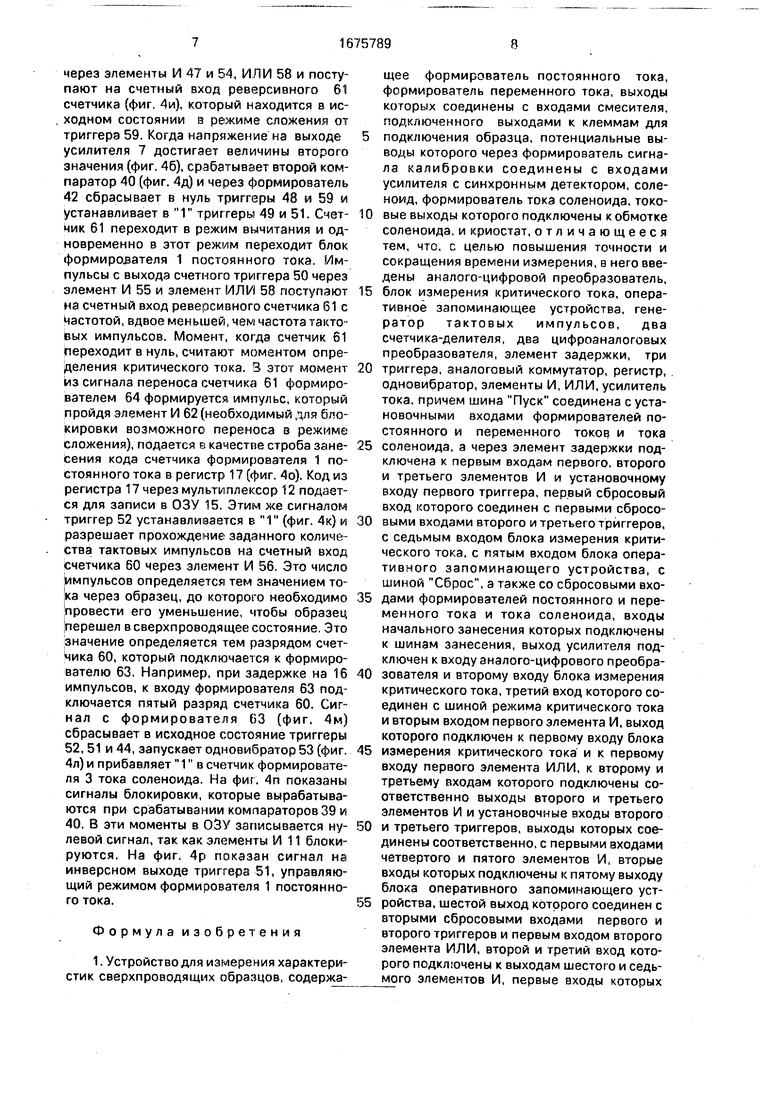

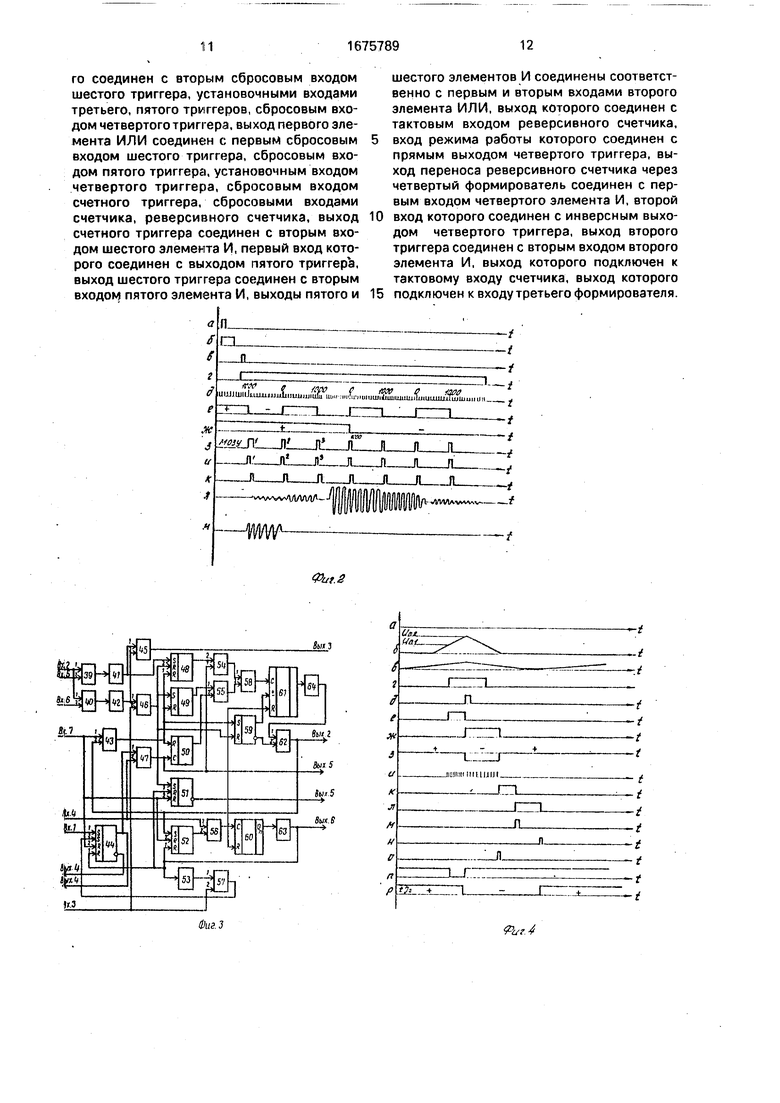

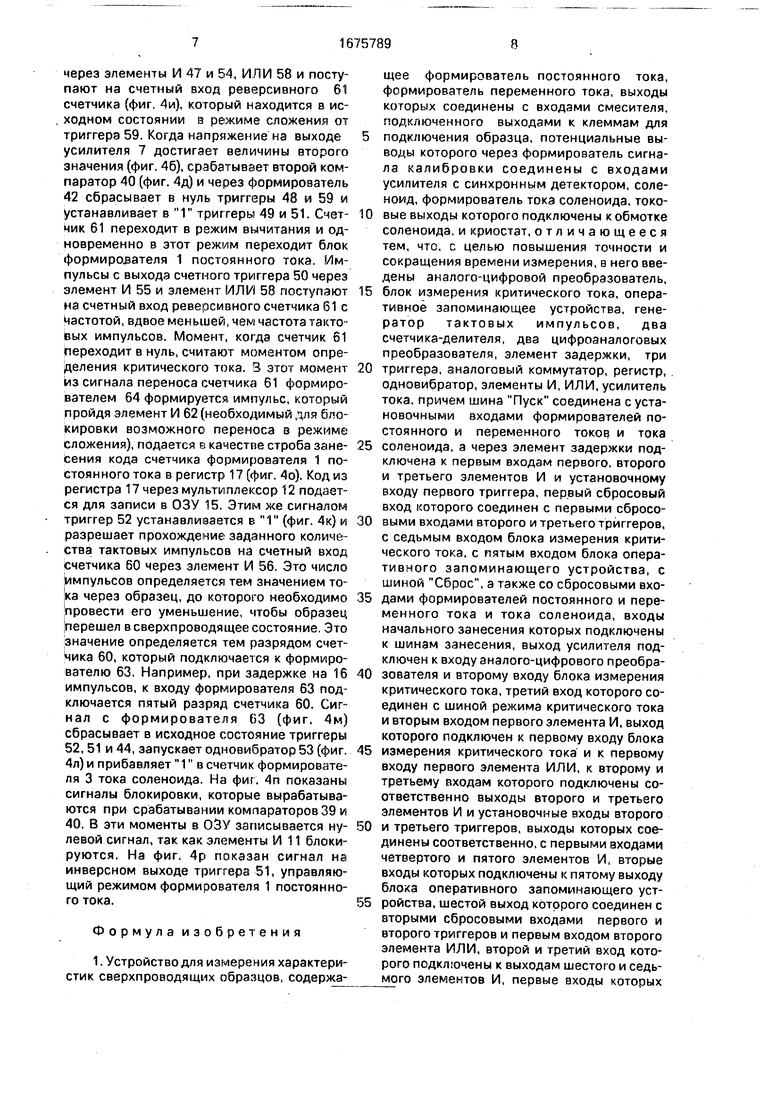

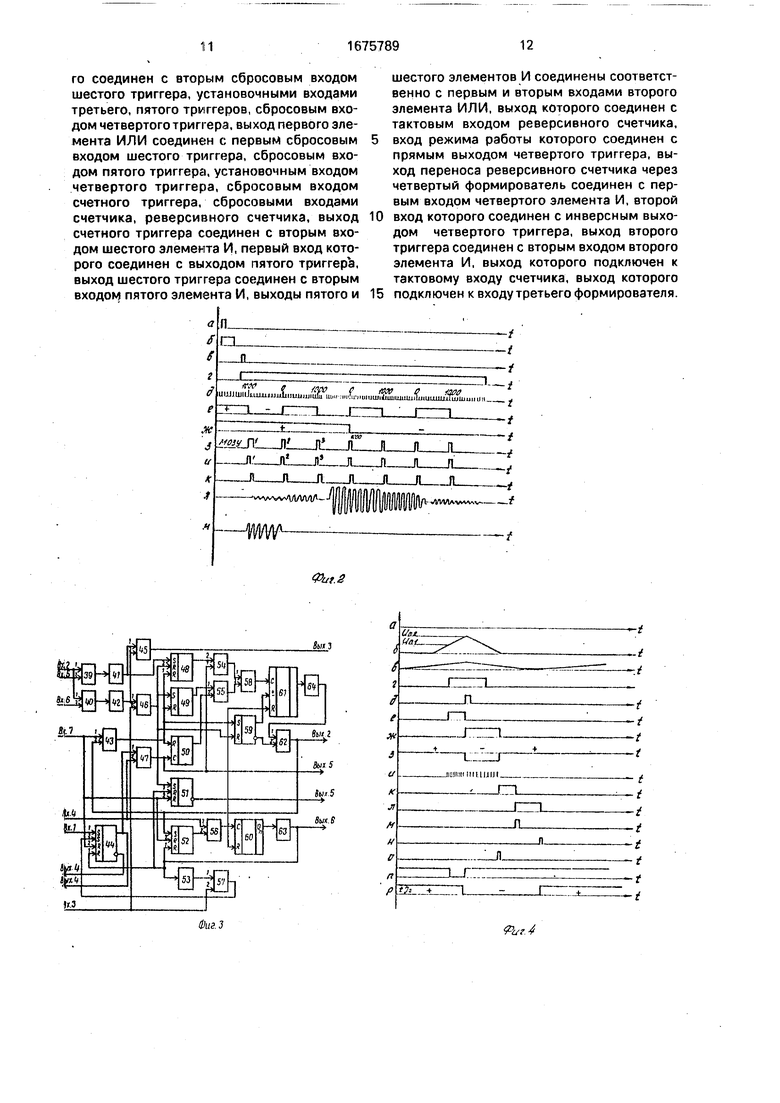

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - временные диаграммы работы устройства в режиме измерения ВАХ; на фиг. 3 - функциональная схема блока измерения критического тока; на фиг. 4 - временные диаграммы его работы; на фиг. 5 - функциональная схема оперативного запоминающего устройства.

Устройство (фиг. 1) содержит формирователь 1 постоянного тока, формирователь 2 переменного тока, формирователь 3 тока соленоида, смеситель 4, криостат 5 с образцом, формирователь 6 сигнала калибровки, усилитель 7 с синхронным детектором, аналоговый коммутатор 8, элемент И 9, аналого-цифровой преобразователь (АЦП) 10, элементы И 1Т, мультиплексор 12, цифроа- налоговые преобразователи (ЦАП) 13 и 14, оперативное запоминающее устройство (ОЗУ) 15, одновибратор 16, регистр 17, элемент ИЛИ 18, блок 19 измерения критического тока, элемент 20 задержки, элементы И 21-25, элементы ИЛИ 26 и 27, RS-триггеры 28-30, элементы И 31 и 32, счетчики-делители 33 и 34, генератор 35 тактовых импульсов, усилитель 36 тока, элемент ИЛИ 37, элемент И 38.

Блок 19 измерения критического тока (фиг. 3) содержит компараторы 39 и 40, формирователи 41 и 42, элемент ИЛИ 43, RS- триггер 44, элемент И 45, элементы ИЛИ 46 и 47, RS-триггеры 48 и 49, счетный триггер 50, RS-триггеры 51 и 52, одновибратор 53, элементы И 54-57, элемент ИЛИ 58, RS- триггер 59, счетчик 60, реверсивный счетчик 61, элемент И 62 и формирователи 63 и 64. ОЗУ 15 (фиг. 5) содержит реверсивные счетчики 65 и 66, формирователь 67, элементы И 68 и 69, RS-триггеры 70 и 71, мультиплексор 72, формирователи 73 и 74, элементы ИЛИ 75-77, матрицу 78 ОЗУ, RS-триггер 79, элемент И 80, элемент 81 задержки, регистр 82, элемент 83 задержки, RS-триггер

84, элемент ИЛИ-НЕ 85, формирователь 86, элемент 87 задержки.

Устройство работает в трех режимах: регистрация ВАХ, регистрация ВПХ и регистрация зависимости кр (Н).

Каждая из характеристик записывается и хранится в ОЗУ 15. Память ОЗУ 15 (в дан ном случае 4Кх11 разрядов) распределена на четыре блока по 1000 ячеек. В первый блок с адресами 0-999 записывается прямой ход ВАХ, во второй блок с адресами 2023-1024 - обратный ход ВАХ, в третий блок с адресами 2048-3047 записывается ВПХ, в четвертый блок с адресами 3072- 4071 - зависимость кр - (Н).

Временные диаграммы (фиг. 2) работы устройства в режиме регистрации ВАХ представляют следующие эпюры напряжений: на шине Пуск устройства (а), на выходе элемента 20 задержки (б), на выходе

элемента И 22 (в), на выходе триггера 28 - триггера ВАХ (г), на выходе элемента ИЛИ 37 (д), на инверсном выходе триггера 70 ОЗУ 15(е), на инверсном выходе триггера 71 ОЗУ 15 (ж), на выходе триггера 84 ОЗУ 15 (з), на

выходе элемента И 80 ОЗУ 15, Пуск АЦП (и), на выходе элемента 87 задержки ОЗУ 15 (к), на выходе формирователя 2 переменного тока (л) и на выходе аналогового коммутатора 8 (м).

В исходном состоянии ОЗУ находится в режиме чтения и на экране осциллографа можно наблюдать выбранную часть памяти ОЗУ (по два блока), в данном случае прямую и обратную ветви ранее записанной кривой

ВАХ, После сигнала Пуск (фиг. 2а), в первый, второй и третий формирователи тока происходит занесение начального кода, находящегося на входах D. Выходной сигнал элемента 20 задержки (фиг. 26), пройдя элемент И 22 (фиг. 2в), устанавливаете 1 триггер 28 режима ВАХ (фиг. 2г). ОЗУ 15 работает с этого момента в двух режимах:

Чтение и Запись, определяемых состоянием триггера 84 ОЗУ 15. Режим записи включается только тогда, когда при работе счетчика 65 в режиме сложения на его выходах образуется код 1000, а в режиме вычитания появляется перенос. Управление счетчиком 65 производится триггером 70 режима чтения (фиг. 2е). Этот триггер меняет направление счета счетчика 65 и, одновременно, подключает к адресной части ОЗУ старший разряд блока (п + 1). Мультиплексор 72 ОЗУ 15 подключает к адресной части либо код счетчика 65 чтения, либо код счетчика 66 записи. В исходном состоянии счетчик 66 находится в режиме сложения и сброшен в нуль (фиг. 2ж). Первый 1000 импульс чтения (фиг. 2д) устанавливает триггер 84 в 1, запускает АЦП 10 (фиг. 2и) и при получении сигнала Конец измерения АЦП сигналом с выхода элемента ИЛИ-НЕ 85 производит запись кода АЦП в первую ячейку ОЗУ (фиг. 2з), добавляя 1 в счетчик 66 записи (фиг. 2к), Одновременно на 1 увеличивается код счетчика в формирователе 2 переменного тока и его амплитуда увеличивается на 0,1% (фиг. 2л). Матрица 78 ОЗУ переходит в режим чтения второй части ОЗУ (адреса 2023-1024). При появлении импульса на выходе переноса счетчика 65 происходит запись во вторую ячейку ОЗУ, увеличение кода счетчика 66 и амплитуды формирователя 2 переменного тока. Процедура продолжается до тех пор, пока не происходит запись в 1000 ячейку ОЗУ. В этот момент триггер 71 изменяет свое состояние и переводит счетчик 66 в режим вычитания. Следующий импульс записи производит запись в ячейку с адресом 1024 + 999 2023, так как 1 с выхода триггера 71 передается через мультиплексор как (п + 1) разряд ОЗУ (для данного примера 11 разряд адреса). Одновременно происходит уменьшение тока на выходе формирователя 2 переменного тока. Последняя запись в данном режиме происходит в ячейку с адресом 1024, после чего сигналом переноса счетчика 66 сбрасываются триггеры 71, 28 и триггер 79 записи ОЗУ.

Для калибровки устройства в начале записи в первую (или несколько первых) ячейку ОЗУ записывается сигнал калибровки. В это время исследуемый образец находится в сверхпроводящем состоянии. На вход усилителя 7 от формирователя 6 сигнала калибровки, который представляет собой понижающий трансформатор с двумя равными выходными обмотками, подается известный сигнал, время действия которого определяется длительностью работы одно- вибратора 16, который разрешает прохождение напряжения с выхода формирователя 2 переменного тока на вход формирователя 6 сигналов калибровки (фиг. 2м).

Режим записи ВПХ отличается тем, что 5 значение переменного тока устанавливается при начальном занесении и в дальнейшем не изменяется. Ток через обмотку соленоида увеличивается после записи в очередную ячейку ОЗУ. Этот ток обеспечи- 10 вается формирователем 3 тока соленоида за счет того, что на тактовый вход формирователя 3 поступают импульсы с пятого выхода ОЗУ 15, предварительно прошедшие через элемент И 32 и элемент ИЛИ 18. В этом 15 режиме запись производится в ячейки с адресами 2048-3047.

Режим записи кр f(H) обеспечивается блоком 19 измерения критического тока (фиг. 3), а временные диаграммы его работы 0 (фиг. 4) представляют эпюры напряжений: на первом входе блока (а), на втором входе блока (б), ток через образец (в), на выходе компаратора 39 (г), на выходе компаратора 40 (д), на выходе триггера 48 (е), на выходе 5 триггера 49 (ж), на единичном выходе триггера 59 (з), на выходе элемента ИЛИ 58 (и), на выходе триггера 52 (к), на выходе одно- вибратора 53 (л), на шестом выходе блока (м), на выходе элемента И 57 (н), на втором 0 выходе блока (о), на третьем выходе блока (п) и на первом выходе блока (р).

Блок 19 измерения критического тока работает следующим образом.

Напряжение с выхода усилителя 7 пода- 5 ется на первые входы компараторов 39 и 40, на второй вход компаратора 39 подается напряжение первого порога, превышающее значение напряжения шумов, на второй вход компаратора 40 подается напряжение 0 такой величины, чтобы отрезки проекции ВАХ на линию абсцисс между точкой пересечения ее с линией абсцисс и первым пороговым значением и между двумя пороговыми значениями были бы равны 5 между собой.

После сигнала Пуск (фиг. 4а) и начального занесения в первый, второй и третий формирователи тока начинается подача тактовых импульсов в формирователь 1 посто- 0 янного -тока, запись информации в последнюю четверть ОЗУ, Тек через образец начинает возрастать (фиг. 4в) и на выходе усилителя 7 появляется напряжение (фиг. 46). Когда это напряжение превышает за- 5 данный уровень первого порога, компаратор 39 срабатывает и через формирователь 41 устанавливает в 1 триггер 48 первого компаратора (фиг. 4е). С этого момента так- товыз импульсы генератора 35 тактовых импульсов с четвертого входа блока проходят

через элементы И 47 и 54, ИЛИ 58 и поступают на счетный вход реверсивного 61 счетчика (фиг. 4и), который находится в исходном состоянии в режиме сложения от триггера 59, Когда напряжение на выходе усилителя 7 достигает величины второго значения (фиг. 46), срабатывает второй компаратор 40 (фиг, 4д) и через формирователь 42 сбрасывает в нуль триггеры 48 и 59 и устанавливает в 1 триггеры 49 и 51. Счетчик 61 переходит в режим вычитания и одновременно в этот режим переходит блок формирователя 1 постоянного тока. Импульсы с выхода счетного триггера 50 через элемент И 55 и элемент ИЛИ 58 поступают на счетный вход реверсивного счетчика 61 с частотой, вдвое меньшей, чем частота тактовых импульсов. Момент, когда счетчик 61 переходит в нуль, считают моментом определения критического тока. В этот момент из сигнала переноса счетчика 61 формирователем 64 формируется импульс, который пройдя элемент И 62 (необходимый для блокировки возможного переноса в режиме сложения), подается в качестве строба занесения кода счетчика формирователя 1 постоянного тока в регистр 17 (фиг. 4о). Код из регистра 17 через мультиплексор 12 подается для записи в ОЗУ 15. Этим же сигналом триггер 52 устанавливается в 1 (фиг, 4к) и разрешает прохождение заданного количества тактовых импульсов на счетный вход счетчика 60 через элемент И 56. Это число импульсов определяется тем значением тока через образец, до которого необходимо провести его уменьшение, чтобы образец перешел в сверхпроводящее состояние. Это значение определяется тем разрядом счетчика 60, который подключается к формирователю 63. Например, при задержке на 16 импульсов, к входу формирователя 63 подключается пятый разряд счетчика 60. Сигнал с формирователя 63 (фиг. 4м) сбрасывает в исходное состояние триггеры 52,51 и 44, запускает одновибратор 53 (фиг. 4л) и прибавляет 1 в счетчик формирователя 3 тока соленоида. На фиг. 4п показаны сигналы блокировки, которые вырабатываются при срабатывании компараторов 39 и 40. В эти моменты в ОЗУ записывается нулевой сигнал, так как элементы И 11 блокируются. На фиг. 4р показан сигнал на инверсном выходе триггера 51, управляющий режимом формирователя 1 постоянного тока.

Формула изобретения

1. Устройство для измерения характеристик сверхпроводящих образцов, содержащее формирователь постоянного тока, формирователь переменного тока, выходы которых соединены с входами смесителя, подключенного выходами к клеммам для

подключения образца, потенциальные выводы которого через формирователь сигнала калибровки соединены с входами усилителя с синхронным детектором, соленоид, формирователь тока соленоида, токо0 вые выходы которого подключены к обмотке соленоида, и криостат, отличающееся тем, что, с целью повышения точности и сокращения времени измерения, в него введены аналого-цифровой преобразователь,

5 блок измерения критического тока, оперативное запоминающее устройства, генератор тактовых импульсов, два счетчика-делителя, два цифроаналоговых преобразователя, элемент задержки, три

0 триггера, аналоговый коммутатор, регистр, одновибратор, элементы И, ИЛИ, усилитель тока, причем шина Пуск соединена с установочными входами формирователей постоянного и переменного токов и тока

5 соленоида, а через элемент задержки подключена к первым входам первого, второго и третьего элементов И и установочному входу первого триггера, первый сбросовый вход которого соединен с первыми сбросо0 выми входами второго и третьего триггеров, с седьмым входом блока измерения критического тока, с пятым входом блока оперативного запоминающего устройства, с шиной Сброс, а также со сбросовыми вхо5 дами формирователей постоянного и переменного тока и тока соленоида, входы начального занесения которых подключены к шинам занесения, выход усилителя подключен к входу аналого-цифрового преобра0 зователя и второму входу блока измерения критического тока, третий вход которого соединен с шиной режима критического тока и вторым входом первого элемента И, выход которого подключен к первому входу блока

5 измерения критического тока и к первому входу первого элемента ИЛИ, к второму и третьему входам которого подключены соответственно выходы второго и третьего элементов И и установочные входы второго

0 и третьего триггеров, выходы которых соединены соответственно, с первыми входами четвертого и пятого элементов И, вторые входы которых подключены к пятому выходу блока оперативного запоминающего уст5 ройства, шестой выход которого соединен с вторыми сбросовыми входами первого и второго триггеров и первым входом второго элемента ИЛИ, второй и третий вход которого подключены к выходам шестого и седь- мого элементов И, первые входы которых

подключены соответственно к шинам режимов измерения вольт-полевых характеристик и критического тока, а вторые входы соединены с вторым сбросовым входом третьего триггера и седьмым выходом оперативного запоминающего устройства, первый и второй выходы которого подключены соответствено к входам первого и второго цифро-аналоговых преобразователей, а третий выход оперативного запоминающего устройства соединен с входом Пуск АЦП, выход Конец измерения АЦП подключен к первому входу оперативного запоминающего устройства, к вторым входам которого подключены выходы мультиплексора, к первым входам которого через элемент И подсоединены выходы аналого-цифрового преобразователя, к вторым входам мультиплексора - выходы регистра, информационные входы которого подключены к кодовому выходу формирователя постоянного тока, а вход занесения соединен с вторым выходом блока измерения критического тока, шестой выход которого соединен с первым входом третьего элемента ИЛИ, второй вход которого подключен к выходу пятого элемента И, а выход третьего элемента ИЛИ соединен с тактовым входом формирователя тока соленоида, выход генератора тактовых импульсов соединен с входом первого счетчика-делителя и первым входом десятого элемента И, второй вход которого соединен с инверсным выходом первого триггера, а выход подключен к первому входу четвертого элемента ИЛИ, выход первого счетчика-делителя подключен к четвертому входу блока измерения критического тока и к входу второго счетчика-делителя, выход которого соединен с первым входом девятого элемента И, второй вход которого подключен к прямому выходу первого триггера и к входу усилителя тока, выход которого подключен к выходу устройства, выход девятого элемента И соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с четвертым входом блока оперативного запоминающего устройства, третий вход которого подключен к выходу первого элемента ИЛИ и через одновибратор к управляющему входу аналогового коммутатора, вход которого соединен с выходом формирователя . переменного тока, а выход - с входом формирователя сигнала калибровки, выход четвертого элемента И подключен к тактовому входу формирователя переменного тока, выход второго элемента ИЛИ соединен с шестым входом блока оперативного запоминающего устройства, третий выход блока измерения критического тока соединен с

вторыми входами восьмого элемента И. четвертые выходы блока измерения критического тока подключены к управляющим входам мультиплексора, пятый выход блока 5 измерения критического тока соединен с тактовым входом формирователя постоянного тока, первый выход блока измерения критического тока и четвертый выход блока оперативного запоминающего устройства

10 подключены соответственно к входам режима работы формирователей постоянного и переменного токов,

2, Устройство по п. 1,отличающее- с я тем, что блок измерения критического

15 тока выполнен в виде двух компараторов, RS-триггеров, счетчика, формирователей, реверсивного счетчика, счетного триггера, одновибратора, элементов И, ИЛИ, причем первый установочный вход первого тригге0 ра соединен с первым входом блока, объединенные первые входы первого и второго компараторов соединены с вторым входом блока, объединенные вторые входы третьего седьмого элементов И соединены с треть5 им входом блока, объединенные второй вход первого элемента И и первый вход второго элемента И соединены с четвертым входом блока, вторые входы первого и второго компараторов соединены соответст0 венно с пятым и шестым входами блока, объединенные первый вход первого элемента ИЛИ, вторые сбросовые входы первого, второго и третьего триггеров соединены с седьмым входом блока, инверсный выход

5 третьего триггера, выход третьего элемента ИЛИ соединен с первым и третьим выходами блока, объединенные выход четвертого элемента И, установочный вход второго триггера и второй вход первого элемента

0 ИЛИ соединены с вторым выходом блока, прямой и инверсный выходы первого триггера соединены с четвертыми выходами блока, объединенные выход первого элемента И, тактовый вход счетного триггера и

5 первый вход пятого элемента И соединены с пятым выходом блока, объединенные выход третьего формирователя, вход одновибратора и первые сбросовые входы первого, второго и третьего триггеров соединены с

0 шестым выходом блока, прямой выход первого триггера соединен с первым входом первого элемента И, выходы первого и второго компараторов соединены с входами первого и второго формирователей, выход

5 первого формирователя соединен с первым входом третьего элемента ИЛ И и установочным входом шестого триггера, выход второго формирователя соединен с вторым входом третьего элемента ИЛИ и первым входом седьмого элемента И, выход которого соединен с вторым сбросовым входом шестого триггера, установочными входами третьего, пятого триггеров, сбросовым входом четвертого триггера, выход первого элемента ИЛИ соединен с первым сбросовым входом шестого триггера, сбросовым входом пятого триггера, установочным входом четвертого триггера, сбросовым входом счетного триггера, сбросовыми входами счетчика, реверсивного счетчика, выход счетного триггера соединен с вторым входом шестого элемента И, первый вход которого соединен с выходом пятого триггера, выход шестого триггера соединен с вторым входов пятого элемента И, выходы пятого и

шестого элементов И соединены соответственно с первым и вторым входами второго элемента ИЛИ, выход которого соединен с тактовым входом реверсивного счетчика,

вход режима работы которого соединен с прямым выходом четвертого триггера, выход переноса реверсивного счетчика через четвертый формирователь соединен с первым входом четвертого элемента И, второй

вход которого соединен с инверсным выходом четвертого триггера, выход второго триггера соединен с вторым входом второго элемента И, выход которого подключен к тактовому входу счетчика, выход которого

подключен к входу третьего формирователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ДЕКОДИРОВАНИЯ ЗАПРОСНЫХ СИГНАЛОВ | 2014 |

|

RU2550083C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ СОСТОЯНИЯ И УПРУГОДИССИПАТИВНЫХ СВОЙСТВ ПОВЕРХНОСТЕЙ ТРЕНИЯ | 1992 |

|

RU2036464C1 |

| Устройство для измерения давления | 1988 |

|

SU1569610A1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ ПОВЫШЕННОЙ ТОЧНОСТИ (ВАРИАНТЫ) | 2008 |

|

RU2376625C1 |

| Устройство для исследования магнитных свойств материалов | 1987 |

|

SU1518809A1 |

| Устройство для контроля пульса | 1989 |

|

SU1828741A1 |

| ЭЛЕКТРОННОЕ УСТРОЙСТВО КАТАПУЛЬТНОГО КРЕСЛА ДЛЯ САМОЛЕТА | 2017 |

|

RU2669720C1 |

| РЕГИСТРАТОР ПАРАМЕТРОВ АВАРИЙНЫХ СИТУАЦИЙ В ЭЛЕКТРИЧЕСКИХ СЕТЯХ | 2008 |

|

RU2381549C2 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

Изобретение относится к измерительной технике и может быть использовано для определения характеристик сверхпроводящих образцов. Целью изобретения является повышение точности и сокращение времени при измерении характеристик сверхпроводящих образцов. Устройство для измерения характеристик сверхпроводящих образцов

&«3

ФигЗ

Фиг 4

| Лобанов К.Б | |||

| Малоиндуктивный СКИ с двумя мостиковыми контактами | |||

| - ЖТФ, 1976 | |||

| Способ изготовления звездочек для французской бороны-катка | 1922 |

|

SU46A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Полый вставной колосник для подведения воздуха к топливу в русской печи | 1924 |

|

SU2443A1 |

Авторы

Даты

1991-09-07—Публикация

1989-05-10—Подача