Изобретение.относится к электросвязи и радиотехнике и может быть использовано для фазовой синхронизации в системах передачи дискретной информации, в системах навигации и точного времени. .

Цель изобретения - повьопение точности синхронизации.путем уменьшения влияния импульсной помехи.

.

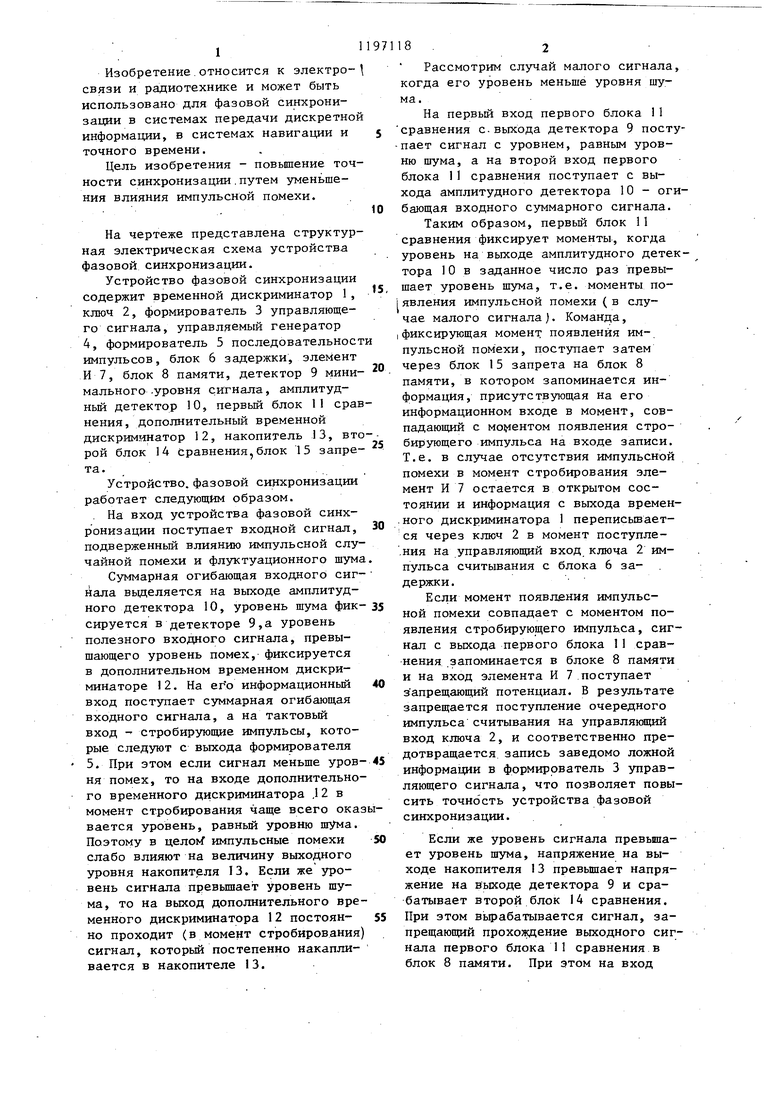

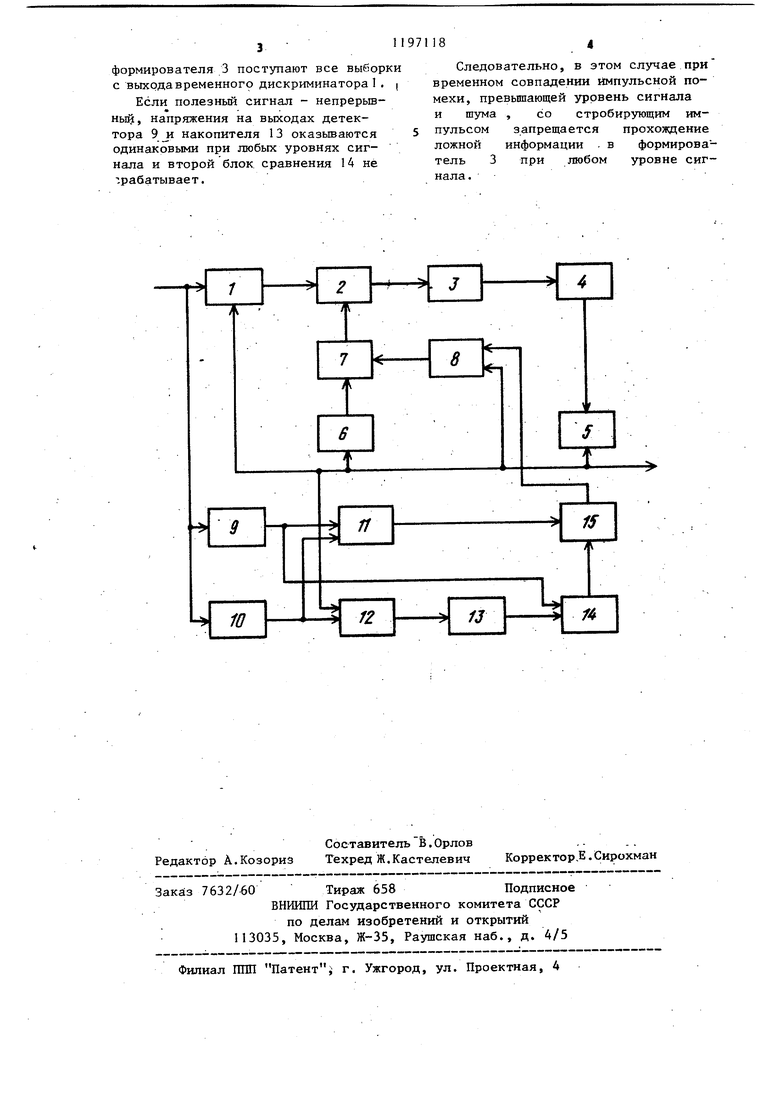

На чертеже представлена структурная электрическая схема устройства фазовой синхронизации.

Устройство фазовой синхронизации содержит временной дискриминатор 1, ключ 2, формирователь 3 управляющего сигнала, управляемый генератор

4,формирователь 5 последовательност импульсов, блок 6 задержки, элемент

И 7, блок 8 памяти, детектор 9 минимального .уровня сигнала, амплитудньй детектор 10, первый блок 1 сравнения, дополнительный временной дискриминатор 12, накопитель 13, второй блок 14 сравнения,блок 15 запрета.

Устройство, фазовой синхронизации работает следующим образом.

. На вход устройства фазовой синхронизации поступает входной сигнал, подверженный влиянию импульсной случайной помехи и флуктуационного шума

Суммарная огибающая входного сигйала выделяется на выходе амплитудного детектора 10, уровень шума фиксируется в детекторе 9,а уровень полезного входного сигнала, превышающего уровень помех, фиксируется в дополнительном временном дискриминаторе 12. На его информационньй вход поступает суммарная огибающая входного сигнала, а на тактовый вход стробирующие импульсы, которые следуют с выхода формирователя

5.При этом если сигнал меньше уровня помех, то на входе дополнительного временного дискриминатора ,12 в момент стробирования чаще всего оказвается уровень, равньй уровню шума. Поэтому в цело импульсные помехи слабо влияют на величину выходного уровня накопителя 13, Если же уровень сигнала превьш1ает уровень шума, то на выход дополнительного временного дискриминатора 12 постоянно проходит (в момент стробирования) сигнал, которьй постепенно накапливается в накопителе 13.

Рассмотрим случай малого сигнала когда его уровень меньше уровня шума.

На первьй вход первого блока 11 сравнения с-выхода детектора 9 пост-пает сигнал с уровнем, равным уровню шума, а на второй вход первого блока 1I сравнения поступает с выхода амплитудного детектора 10 - огбающая входного суммарного сигнала.

Таким образом, первьй блок 11 сравнения фиксирует моменты, когда уровень на выходе амплитудного дететора 10 в заданное число раз превышает уровень шума, т.е. моменты появления импульсной помехи (в случае малого сигнала). Команда, фиксирующая момент появления импульсной помехи, поступает затем через блок 15 запрета на блок 8 памяти, в котором запоминается информация, присутствующая на его информационном входе в момент, совпадающий с MoifieHTOM появления стробирующего импульса на входе записи. Т.е. в случае отсутствия импульсной помехи в момент стробирования элемент И 7 остается в открытом состоянии и информация с выхода времен.ного дискриминатора 1 переписьшается через ключ 2 в момент поступле,ния на управляющий вход ключа 2 импульса считывания с блока 6 задержки .

Если момент появления импульсной помехи совпадает с моментом появления стробирующего импульса, сигнал с выхода первого блока 11 сравнения запоминается в блоке 8 памяти и на вход элемента И 7 поступает запрещающий потенциал. В результате запрещается поступление очередного импульса считывания на управлякяций вход ключа 2, и соответственно предотвращается запись заведомо ложной информации в формирователь 3 управляющего сигнала, что позволяет повысить точность устройства фазовой синхронизации.

Если же уровень сигнала превышает уровень шума, напряжение на выходе накопителя 13 превьшает напряжение на выходе детектора 9 и срабатывает второй блок 14 сравнения. При этом вьфабатывается сигнал, запрещающий прохождение выходного сигнала первого блока 11 сравнения в блок 8 памяти. При этом на вход

формирователя 3 поступают все выборки с выхода временногр дискриминатора 1 . |

Если полезный сигнал - непрерьшный, напряжения на выходах детектора 9 JI накопителя 13 оказьгоаются одинаковыми при любых уровнях сигнала и второй блок сравнения 14 не .рабатывает.

Следовательно, в этом случае при временном совпадении импульсной помехи, превьшающей уровень сигнала и шума , со стробирующим импульсом запрещается прохождение ложной информации . в формирователь 3 при любом уровне сигнала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для подавления помех | 1983 |

|

SU1095419A1 |

| Фильтр помех с сосредоточенным спектром | 1980 |

|

SU894831A1 |

| Автоселектор периодической последовательности импульсов | 1982 |

|

SU1061278A2 |

| Стробоскопический преобразователь | 1990 |

|

SU1721522A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА СТАРТСТОПНЫХ СООБЩЕНИЙ | 2001 |

|

RU2214063C2 |

| УСТРОЙСТВО ДЛЯ ЗАЩИТЫ ОТ ИМПУЛЬСНЫХ ПОМЕХ | 1981 |

|

SU1840932A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ФОРМЫ СИГНАЛОВ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1997 |

|

RU2111504C1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ВРЕМЕННЫХ ИНТЕРВАЛОВ В УСЛОВИЯХ ПОМЕХ | 1991 |

|

RU2030757C1 |

| Устройство обнаружения цветоразностных сигналов | 1982 |

|

SU1085017A1 |

| Устройство для выделения импульсных сигналов на фоне шумов и импульсных помех | 1991 |

|

SU1786649A1 |

УСТРОЙСТВО ФАЗОВОЙ СИНХ- . РОНИЗАЦИИ, содержащее последовательно соединенные формирователь управляющего сигнала, управляемый ге.нератор, формирователь последовательности импульсов и временной дискриминатор, причем информационный вход временного дискриминатора и выход формирователя последовательности импульсов являются соответственно входом и выходом устройства, отличающееся тем, что, с целью повышения точности синхронизации путем уменьшения влияния импульсной помехи, введены последовательно соединенные детектор минимального уровня сигнала, первый блок сравнения, блок запрета и блок памяти, последовательно соединенные амплитудный детектор, дополнительный временной дискриминатор, накопитель и второй блок сравнения, последовательно соединенные блок задержки, элемент И и ключ, при этом входы амплитудного детектора и детектора минимального уровня сигнала объединены с входом временного дискриминатора, выходы амплитудного детектора и детектора минимального уровня сигнала подсоединены соответственно к втарым входам первого блока сравнения и второго блока сравнения, выход которого подсоединен к запрещающему входу блока запрета, (Л выход временного дискриминатора через ключ подсоединен к входу формирователя управл5 ющего сигнала, выход формирователя последовательности импульсов подсоединен к входу блока задержки, тактовому входу дополнительного временного дискрисо д минатора и входу записи блока памяти, выход которого подсоединен к второму входу элемента И.

| Фазокорректирующее устройство с подстройкой частоты | 1980 |

|

SU882010A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Лутченко А.Е | |||

| КоГерентньй прием | |||

| радионавйгационнь{х сигналов, М.: Советское радио, 1973, с | |||

| Питательный кран для вагонных резервуаров воздушных тормозов | 1921 |

|

SU189A1 |

Авторы

Даты

1985-12-07—Публикация

1984-07-18—Подача