1

Изобретение относится к электросвязи и Vioжет быть использовано в схемах фазирования по тактам в синхронных системах передачи данных.

Известно фазокорректирующее устройство, содержащее делитель частоты на I К-триггерах, два элемента И н формирователь импульсов, первый и второй входы которого соединены соответственно с тактовым и информационным входами устройства, первый выход формирователя импульсов подключен к первым входам первого I К-триггера делителя частоты и первого элемента И, к второму входу которого подключен выход первого I К-триггера делителя частоты, при этом выход перврго элемента И подключен к первому входу второго I К-триггера делителя частоты, ко второму и третьему входам которого подключен выход второго элемента И, к первому и второму входам которого подключены соответственно второй выход делителя частоты и второй выход формирователя импульсов, а третий вход второго элемента И объединен с третьим входом первого И {1.

Однако известное устройство обладает низкой . точностью коррекции и низким быстродействием, в нем отсутствует возможность подстройки частоты под частоту информационной последовательности.

Цель изобретения - повышение точности коррекции и быстродействия устройства.

Цель достигается тем, что в фазокорректирующее устройство с подстройкой частоты, содержащее делитель частоты на I К-триггерах, два

10 элемента И и основной формирователь импульсов, первый и второй входы которого соединены соответственно с тактовым и информационным входами устройства, первый выход основного формирователя импульсов подключен к

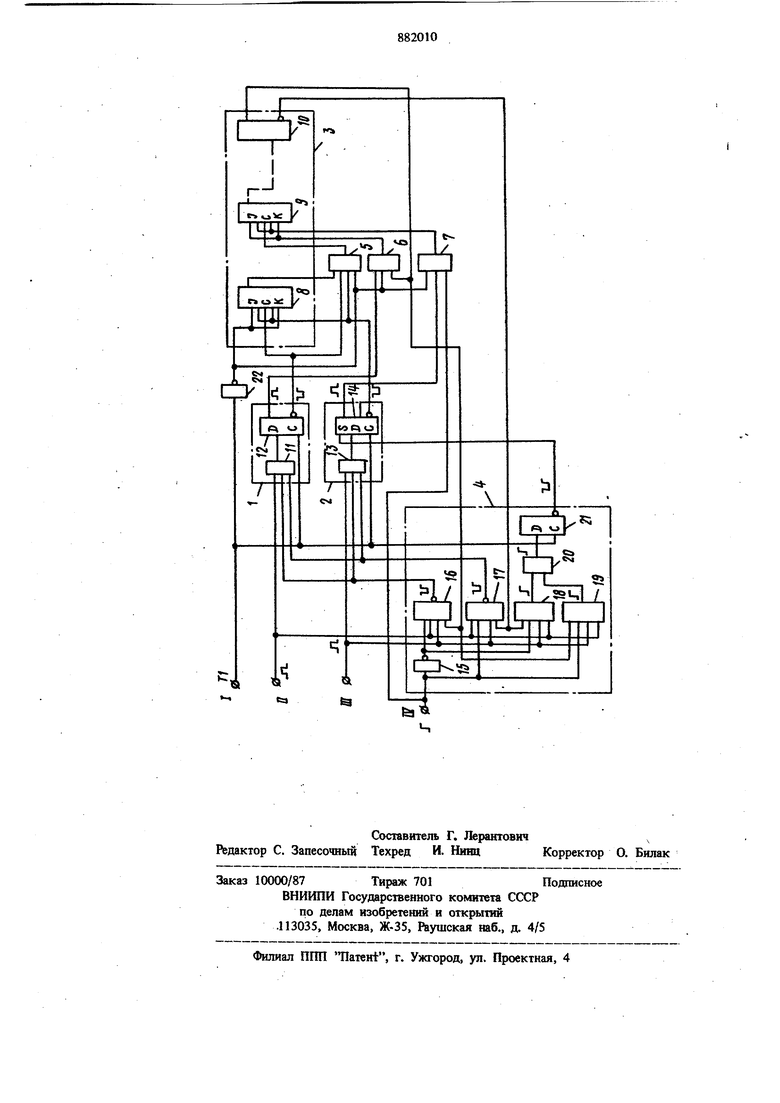

15 первым входам первого I К-триггера делителя частоты и первого элемента И, к второму входу которого подключен выход первого I К-триггера делителя частоты, прн этом вьпсод первого элемента И подключен к первому входу второгего 1К-триггера делителя частоты, к второму и третьему входам которого подключен выход второго элемента И, к первому и второму входам которого подключены соответственно второй выход делителя частоты и второй выход основного формирователя импульсов, а третий вход второго элемента И объединен с третьим входом первого элемента И, введены дополнительный формирователь импульсов, третий элемент И, инвертор и решающий блок, при этом тактовый вход устройства подключен к первым входам дополнительного формирователя импульсов и решающего блока непосредственно и через инвертор к второму и третьему входам пер вого I К-триггера делителя частоты, а также к первому входу третьего элемента И и третьему входу первого элемента И, к четвертому входу которого, объединенному с четвертым и пятым входами первого IК-триггера делителя частоты, подключен первый выход дополнительного формирователя импульсов, второй выход которого подключен к второму входу третьего элемента И, третий вход которого соединен со входом добавление устройства, а выход третьего элемента И подключен к четвертому и пятому входам второго I К-триггера делителя частоты, информационный вход, вход импульс коррекции и вход добавление устройства соединены соответственно со вторым, третьим и четвер тым входами решающего блока, к пятому и шестому входам которого подключены соответственно второй и третий выходы делителя частоты, причем второй вход дополнительного фор мирователя импульсов объединен со вторым вхо дом решающего блока, первый и второй выходы которого подключены соответственно к третьим и четвертым входам основного и дополнительно го формирователей импульсов, а третий выход решающего блока подключен к пятому входу дополнительного формирователя импульсов. Кроме того, решающий блок содержитинвертор, два элемента И-НЕ, два элемента И и последовательно соединенные элемент ИЛИ и триг гер, второй вход которого является первым входом решающего блока, при этом выход инвертора подключен к первым входам первых элементов И-НЕ, а вход инвертора объединен с первыми входами вторых элементов И-НЕ и И и является четвертым входом решающего бло ка, вторым и третьим входами которого являются соответственно вторые и третьи входы элементов И-НЕ и И, а выходы элементов И подключены ко входам элемента ИЛИ, причем четвертые входы первого элемента И-НЕ и второго элемента И, а также четвертые входы второго элемента И-НЕ и первого элемента И являются соответственно пятым и шестым входами решающего блока, первым, вторым и третьим выходами которого являются соответственно выходы первого и второго элементов И-НЕ и триггера. Формирователь импульсов содержит последовательно соединенные элементы И и триггер. ВЫХОДЫ которого являются первым и вторым выходами формирователя импульсов, первым и пятым входами которого являются входы триггера, а вторым, третьим и четвертым входами формирователя импульсов являются соответственно второй, третий и четвертый входы элемента И. На чертеже представлена структурная схема предложенного устройства. Устройство содержит основной формирователь 1 импульсов, дополнительный формирователь 2 импульсов, делитель 3 частоты, решающий блок 4, элементы И 5-7, I К-триггеры 8, 9, 10 элемент И 11, триггер 12, элемент И 13, триггер 14, инвертор 15, элементы И-НЕ 16, 17, элементы И 18, 19, элемент ИЛИ 20, триггер 21, инвертор 22. Устройство работает следующим образом. Импульсы Т1 с тактового входа поступают через инвертор 22 на счетный вход первого 1К-триггера 8, на выходе которого формируется деленная на два последовательность. Основной формирователь 1 импульсов формирует взаимно инвертированные импульсы положительной и отрицательной полярности при каждом поступлении фронта информащш на вход форм1фователя 1 импульсов. Импульс отрицательной полярности запрещает поступление на счетный вход первого I К-триггера 8 одного счетного импульса Свычитаю1е), осуществляемое каждым фронтом информационной последовательности. На элементе И 5 осуществляется формирование коротких импульсов, длительность которых соответствует длительности входных импульсов генератора импульсов, а фаза соответствует фазе сигналов на выходе первого I К-триггера 8, С этой целью на элементе И 5 осуществляется запрет отрицательными импульсами основного формирователя 1 импульсов, т.е. формируется последовательность импульсов, количество которых соответствует количеству перепадов, переносимых на второй IК-триггер 9. Элемент И 6 совмещает функции фазового дискриминатора (сравнение фазы входной информации с синхронным тактом на выходе делителя частоты) и формирователя коротких импульсов, длительность которых равна длительности входных импульсов генератора импульсов, при этом эти импульсы сдвинуты по фазе относительно импульсов переноса. Таким образом, на выходе злемента И 6 формируется короткий импульс в соответствующей фазе, если синхронный такт Т1-1 (выход делителя 3 частоты отстает по фазе от фронта входной информации). Импульсы на выходе элемента И 5 являются сигналами, переносимыми из первого во второй разряд делителя 3 частоты, а импульсы на выходе злемента И 6 являются сигналами добавления для смещения фазы синхронного такта (вы58ход делителя 3 частоты). При объединении сигналов с элементов И 5 и И 6 на входе I К-триггера 9 формируется результирующий суммарный сигнал. Управление фазокоррекгирующего устройства нМпульсами коррекции частоты осуществляется так же, как и от фронтов информации, только в этом случае работает дополнительный формирователь 2 импульсов, на вход которого поступают импульсы коррекции частоты, а на выходе формируются импульсы как отрицательной полярности, поступающие на третий вход первого I К-триггера 8 и элемента И 5, так и импульсы положительной полярности, поступающие на вход элемента И 7. С помощью этих импульсов осуществляется запрет одного импульса на входе I К-триггера 8 и добавление одного импульса (если поступает сигнал добавление на входе второго I К-триггера 9.). Если импульсы коррекции фаэы и частоты поступают в одном тактовом интервале, то возможно четыре варианта работы устройства, приведенные в таблицу .(+ - сигнал добавле-. - сигнал вычитание). В вариантах 1 и 2 импульсы коррекции фазы и частоты не должны осуществлять воздействие на фазокорректирующее устройство. В вариантах 3 и 4 должно осуществляться двойное воздействие. При работе устройства по информационному входу должно осуществляться Добавление, а по входу коррекции частоты вычитание (вариант 1). В этом случае на вход формирователей 1 и 2 импульсов поступают импульсы положительной полярности. На элемент И-НЕ 16 решающего устройства поступает положительный импульс фронта информации, импульс коррекции, шгнал добавление из делителя 3 частоты и положительный сигнал вычитание, сформированный поступающим через инвертор 15 низким уровнем на входе добавление. На выходе элемента И-НЕ 16 формируется отрицательный импульс, запирающий элементы И 11 (13) формирователей 1 (2) импульсов, на выходе которых не формируются импульсы подстройки. Аналогично работает устройство и в случае варианта. 2, т.е. когда по информационному входу должно осуществляться вычитание, а по входу коррек ции частоты добавление. Только в этом слу%е запрещающий сигнал формируется элементом И-НЕ 17. При работе устройства в случае вариаяга 3 должно осуществляться добавление как фронтом информации, так и импульсом коррекции частоты. В .этом случае в первом такте формирователи 1, 2 импульсов формируют сигналы положительной и отрицательной полярности, поступающие на элементы И 5-7. При этом осуществляется операция добавлеш е и соответствующий сдвиг фазы в делителе 3 частоты. Одновременно формируется импульс положительной полярности на выходе элемента И 19, который через элемент ИЛИ 20 поступает на вход триггера 21, на выходе которого формируется импульс отрицательной полярности, поступающий на S-вход D-триггера 14. В этом случае триггер 14 остается в состоянии 1 еще на один такт, пропуская через элемент И 7 два импульса тактовой частоты, а, следовательно, в фазокоррек тирующем устройстве осуществляется двойное управляющее воздействие. Аналогично работает устройство и по варианту 4, только в этом случае работает элемент И 18. Дополнительный формирователь 2 импульсов отрицательным импульсом двойной длительности вычитает на входе первого трипера 8 два импульса тактовой частоты; положительный импульс дополнительного формирователя 2 импульсов запрещается на входе элемента И 7 сигналом вычитание (отрицательным уровнем, поступающим по входу добавление). TexjHHKo-экономический эффект устройства состоит в повьпиении точности и быстродействия корректирования либо, при сохранении прежней точиости, позволяет понизить требования к стабильности и точности настройки задающих генераторов (например, к исключению термостатирования генераторов). Формула изобретения 1. Фазокорректирующее устройство с подстройкой частоты, содержащее делитель частоть на I К-триггерах, два элемента И и основной формирователь импульсов, первый и второй входы которого соеданены соответственно с тактовым и информационным входами устройства, первый выход основного формирователя импульсов подключен к первым входам первого 1К-триггера елителя частоты и первого элемента И, к второму входу которого подключен выход первого I К-триггера делителя частоты, при этом выход первого элемента И подключен к первому входу второго I К-триггера делителя частоты, к второму и третьему входам которого подключен выход второго элемента И, к первому и второму входам которого подключены соответственно второй выход делителя частоты и второй выход основного формирователя импульсов, а третий вход второго элемента И объединен с третьим входом первото элемента И, отличающееся тем, что, с целью повышения точности коррекции и быстродейств в устройство введены дополнительный формиро ватель импульсов, третий элемент И, инвертор и решающий блок, при этом тактовый вход устройства подключен к первым входам дополнительного формирователя импульсов и решающего блока непосредственно и через инвертор к второму и третьему входам первого 1К-триггера делителя частоты, а также к первому входу третьего элемента И и третьему входу первого элемента И, к четвертому входу которого, объединенному с четвертым и пятым входами 1К-триггера делителя частоты, подключен первый выход дополнительного формирователя импульсов, второй выход которого подключен к второму входу третьего элемеита И, третий вход которого соединен со входом добавление устройства, а выход третьего элемента И подключен к четвертому ипятому входам второго I К-триггера делителя частоты, а информацион ный вход, вход импульс коррекции и вход добавление устройства соединены соответственно со вторым, третьим и четвертым входами решающего блока, к пятому и шестому вхо дам которого подключены соответственно второй и третий выходы делителя частоты, причем второй вход дополнительного формирователя импульсов объединен со вторым входом решающего блока, первый и второй выходы которого подключены соответственно к третьим и четвертым входам основного и дополнительного формирователей импульсов, а третий выход решающего блока подключен к пятому входу дополнительного формирователя импульсов. 8 2. Устройство по п. 1, о т л и ч а ю щ ее с я тем, что решающий блок содержит инвертор, два элемента И-НЕ, два элемента И и последовательно соединенные элементы ИЛИ и тритгер, второй вход которого является первым входом решающего блока, при этом выход инвертора подключен к первым входам первых элементов И-НЕ и И, а вход инвертора объединен с первыми входами вторых элементов И-НЕ и И и является четвертым входом решающего блока, вторым и третьим входами которого являются соответственно вторые и третьи входы элементов И-НЕ и И, а выходы элементов И подключены ко входам элемента ИЛИ, причем четвертые входы первого элемента И-НЕ и второго элемента И, а также четвертые входы второго элемента И-НЕ и первого элемента И являются соответственно пятым и шестым входами решающего блокЭ) первым, вторым и третьим выходами которого являются соответственно выходы первого и второго элементов И-НЕ и триггера, 3. Устройство по п. 1, о т л и ч а ю щ ее с я тем, что формирователь импульсов содержит последовательно соединенные элемент И и триггер, выходы которого являются первым и вторым выходами формирователя импульсов, первым и пятым входами которого являются входы триггера, а вторым, третьим и четвертым входами форм1фователя импульсов являются соответственно второй, третий и четвертый входы элемента И. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР N 698146, л. Н 04 L 7/02, 1978 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для измерения исправляющейСпОСОбНОСТи пРиЕМНиКА дВОичНыХСигНАлОВ | 1979 |

|

SU815949A1 |

| Делитель частоты импульсов | 1980 |

|

SU869053A1 |

| Система передачи и приема цифровой информации | 1988 |

|

SU1559361A1 |

| Устройство фазирования псевдослучайных последовательностей | 1986 |

|

SU1381726A1 |

| Фазокорректирующее устройство | 1978 |

|

SU698146A1 |

| УСТРОЙСТВО ДЛЯ КОРРЕКЦИИ ШКАЛЫ ВРЕМЕНИ | 1995 |

|

RU2082216C1 |

| Имитатор ошибок в групповом тракте цифровых систем передачи | 1976 |

|

SU646459A1 |

| Делитель частоты следования импульсов с регулируемым коэффициентом деления | 1980 |

|

SU924865A1 |

| Устройство для передачи сигналов точного времени по линиям связи с переменным временем распространения | 1982 |

|

SU1095219A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

Авторы

Даты

1981-11-15—Публикация

1980-03-12—Подача