та задержки, первым входом элемента И-НЕ и входом синхронизации тригге ра, выход которого подключен к второму входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым . входом элемента И-НЕ, выход которого подключен к первому входу элемента запрета, второй вход которого через

второй элемент г адержки соединен с выходом формирователя импульсон, вход которого подключен к выходу счетчика, счетный вход которого соединен с выходом первого элемента задержки и подключен к второму выходу блока определения длины серий. I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения стационарности случайного процесса | 1984 |

|

SU1251120A1 |

| Способ регистрации сигнала резонансного взаимодействия вещества с электромагнитным излучением (ЭМИ) и устройство для его осуществления | 1987 |

|

SU1566275A1 |

| Устройство для статистической обработки результатов измерений по скользящей выборке | 1984 |

|

SU1223250A1 |

| Цифровой анализатор спектра | 1987 |

|

SU1413545A1 |

| Коррелятор | 1984 |

|

SU1173419A1 |

| Устройство для вычисления производной корреляционной функции | 1984 |

|

SU1257663A1 |

| Коррелятор | 1987 |

|

SU1444813A1 |

| Анализатор амплитудных распределений | 1982 |

|

SU1042041A1 |

| Устройство для определения скользящего среднего случайных сигналов | 1977 |

|

SU656075A1 |

| Коррелятор | 1989 |

|

SU1665386A1 |

. 1. УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ИНТЕРВАЛОВ СТАЦИОНАРНОСТИ ДИСКРЕТНОГО СЛУЧАЙНОГО ПРОЦЕССА, содержащее распределитель импульсов, сумматоры, блоки сравнения, счетчики,, блок памяти, блок постоянной памяти, выход блока памяти подключен к первбму входу первого блока сравнения, первый выход распределителя импульсов соединен с входом записи блока памяти, выход первого сумматора подключен к первому входу второго блока сравнения, выход которого является выходом стационарности устройства, отличающееся тем, НТО, с целью повьщ1ения точности, в него введены регистр, блок масштабирования , блок определения длины серий, информационный вход блока памяти объединен с первым входом второго сумматора и является информационным входом устройства, выход блока памяти соединен с вторым входом второго сумматора, вход сброса которого объединен с входом элемента задержки и подключен к первому выходу распределителя импульсов, выход второго сумматора соединен с информационным входом регистра, вход записи которого подключен к выходу элемента задержки, выход регистра соединен с входом блока масштабирования, выход которого подключен к второму входу первого блока сравнения и является выходом среднего значения устройства, выход первого блока сравнения соединен с первым входом блока определения длины серий, второй вход которого объединен с входом считывания блока памяти и входом синхронизации второго сумматора и подключен к второму выходу распределителя импульсов, счетный вход счетчика соединен с информационным выходом блока определения длины серий, второй выход которого подключен к входу сброса счетчика и входу сброса первого сумматора, (П информационный вход которого соединен с выходом блока постоянной памяти, вход которого подключен к выходу S счетчика, второй вход второго блока сравнения является входом установки уровня анализа устройства, вход распределителя импульсов является :о эо сд входом синхронизации устройства. 2. Устройство по п. 1, отличающееся тем, что блок: -U определения длины серии содержит триггеры, элемент ИСКЛЮЧАЩЕЕ ИЛИ, элемент И-НЕ, одновибратор, элемент задержки, счетчик, формирователь импульсов, элемент запрета, выход которого является информационным выходом блока определения длины серий, информационный вход триггера объединен с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и является первым входом блока определения длины серий, второй вход которого подключен к входу одновибратора, выход которого соединен с входом первого элемен

Изобретение относится к специализированным средствам вычислительной техники и может быть использовано ,для решения в реальном масштабе времени задач диагностического контроля и управления различными технологическими процессами.

Целью изобретения явлется повышение точности.

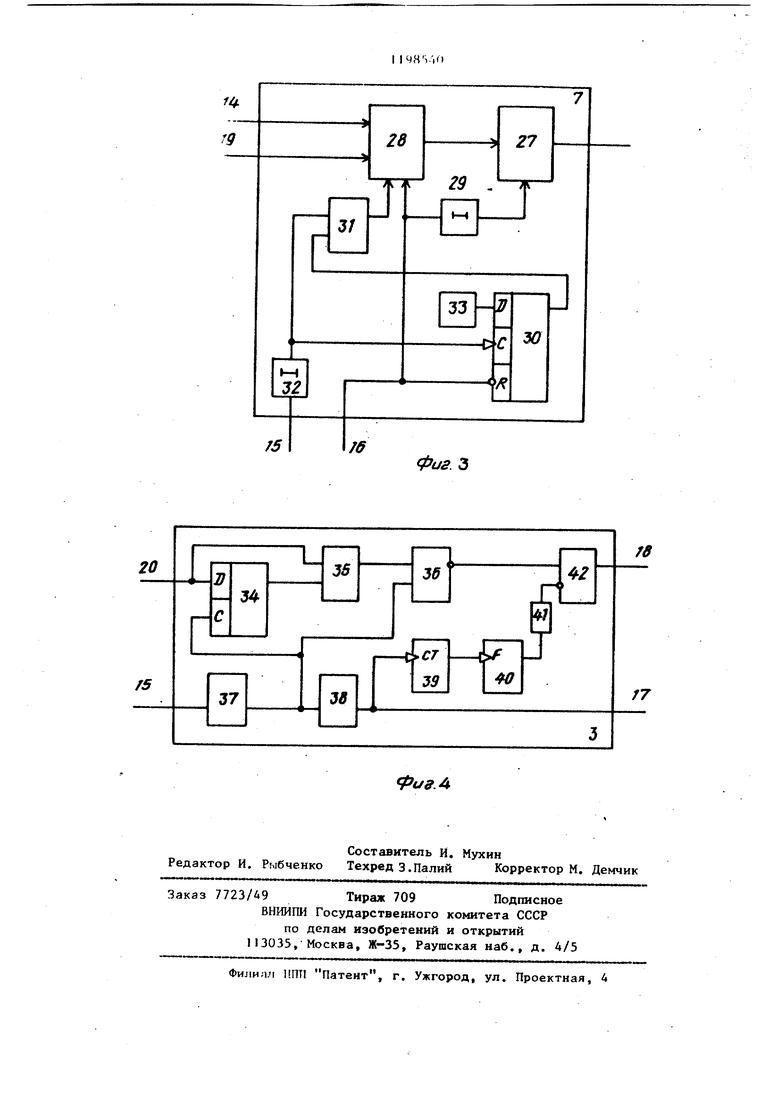

На фиг. 1 изображена блок-схема предлагаемого устройства; на фиг. 2, 3 и 4 - примеры выполнения блока памяти, второго блока суммирования и блока определения длины серий соответственно.

Устройство для определения интервалов стационарности дискретного случайного процесса содержит (фиг. О блЮк I памяти, блок 2 сравнеш1я, блок 3 определения длины серий, счетчик 4, блок 5 постоянной памяти, первый 6 и второй 7 сумматоры, блок 8 сравнения, регистр 9, блок 10 масштабирования, распределитель 11 импульсов, элемеит 12 задержки, вход 13 синхронизации устройства информационный вход 14 устройства, первый 15 и второй 16 выходы распределителя 1I импульсов, информационный 17 и гасящий 18 выходы блока 3 определения длины серий, информационный выход 19 блока 1 памяти, выход 20 блока 2 сравнения, первый 21 и второй 22 информационные выходы устройства.

Блок 1 памяти (фиг. 2) может быть выполнен, например, в виде элемента 23 памяти, счетчика 24 по модулю М, где М - объем скользящей выборки, элемента ИЛИ 25, элемента 26 задержки.

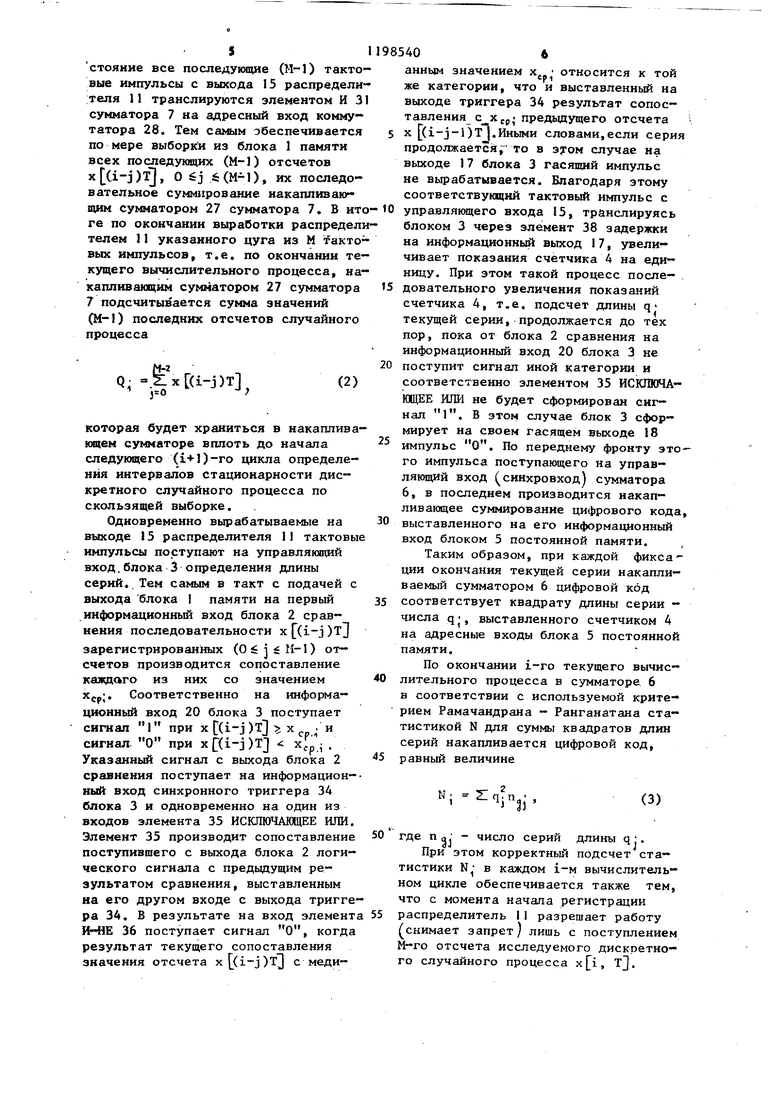

Сумматор (фиг. 3) может быть выполнен, например, в виде накапливающего сумматора 27, коммутатора 28, первого элемента 29 задержки, синхронного триггера 30, элемента И 31, второго элемента 32 задержки и источника 33 единичной логической кон станты.

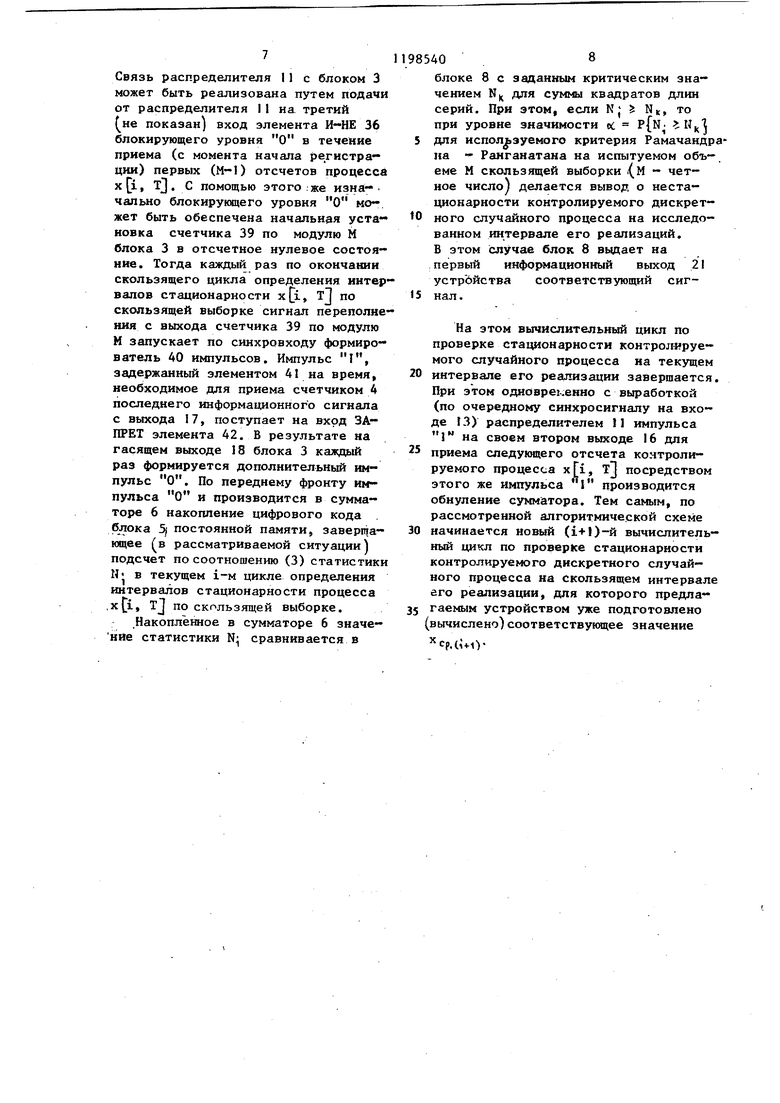

Блок определения длины серий (фиг. 4) может быть выполнен, например, в виде синхронного триггера 34, элемента 35 ИСКЛЮЧАЮЩЕЕ ИЛИ, элемента И-НЕ 36, одновибратора 37, элемента 38 задержки, счетчика 39 формирователя 40 импульсов, элемента 41 задержки и элемента 42 запрета.

Устройство для определения интервалов стационарности дискретного случайного процесса работает следуюшзнм образом.

Последовательность двоично-кодированных сигналов слов, характеризующих в соответствующие i-e моменты времени состояние дискретного случайного процесса х i, Т), где Т - шаг дискретизации, с информационного входа 14 устройства поступает на вход блока 1 памяти и одновременно, на первый информационный вход второго сумматора 7. По сигналу 1, вырабатываемому распределителем 11 на своем втором выходе 16 на каждый поступающий (на его управляющий вход 13) синхросигнал, производится запись соответствующего информационного двоично-кодированного слова , Т в блок 1 памяти (фиг. 2). Одновременно посредством этого же сигнала 1, выставляемого блоком 11 на второй управляющий вход 16 второго сумматора 7 (т.е. на первый адресный вход коммутатора 28), произ 3 водится суммирование поступившего двоично-кодированного числа х i T со значением второго слагаемого, хранимого в накапливающем сумматоре 27 (фиг. 3) и равного cytete X (i-j )ТЗ аредцдуцих М-1 наблюдений, где М - объем скользящей выборки. В результате на вьвсоде сумматора 7 выставляется значение скользящей сумм М последних Ha JjiKWeHHu случайного « м-« процесса Sj .Z. хГ(1-з)Т, которое 1 задержанным посредством элемента 12 сигндпом } с второго выхода 16 распределителя 1t записывается в регистр9. В этом случае блок 10 масштабирования, осуществляя норма .мм . лизацию числа S; .SI х ({i-j )Т, вы.ставляет на второй информационный выход 22 устройства и связанный с ним второй информационный вход блок 2 сравнения двоично-кодированное значение Хср , для последних М за-, регистрированных отсчетов исследуемого случайного процесса и/н|«С(И)т. в итоге в .ечение всей последующей фазы текущего вычислительного процесса на втором информационном входе блока 2 сравнения блоком 10 поддерживается двоично-кодированное значение х , между тем как накапли вакций сумматор 27 (фиг. 3) суммато ра 7 к началу этой фазывычислительного процесса обнулен с помощью задержанного посредством элемента 29 сигнала 1 с второго выхода 16 распределителя П. Кроме того, этот же сигиал с выхода 16 распределител 11 каждый раз обеспечивает установк триггера 30 сумматора 7 в нулевое состояние. В течение следующей завершающей фазы вычислительного процесса фазы подсчета суммы квадратов длин серий - распределитель 11 вырабатыв ет (генерирует) на первом своем выходе 15 цуг из М тактовых импульсов поступаю1ф1х на первый управляющий вход 15 блока 1 памяти и управляющи 404 вход блоки 3 определения длины серий. Под воздействием каждого из М тактовых импульсов счетчик 24 по модулю М блока 1 памяти (фиг. 2), последовательно |}зменяя свои показания, обеспечивает выборку из элемента 23 памяти последовательности М двоичнокодированных отсчетов x(i-j)Tj, 05j 6(М-1), исследуемого случайного процесса. При этом выборка двоичнокодированных слов производится в строго определенном порядке убывания у адреса этих слов значения номера j от (М-1) до 0. Такая строгая вре- -менная упорядоченность обеспечивается благодаря тому, что при поСтупЛении очередного двоично-кодированного сло ва xfi, Tj, j 0, оно под воздействием сигнала 1 с второго выхода 16 распределителя 11 записьгоается в ту ячейку элемента 23 памяти, в которой бьшо записано предшествующее на М шагов дискретизации пначенне х f(iM)Tj исследуемого сл5 чайного процес- са. Тогда под в.здействием первого из М тактовых импульсов, выработанных на первом выходе 15 распределителя 11, показания адресного счетчика увеличиваются на единицу и на выходе 19 элемента 23 памяти выставляется знач-ние отсчета х Г(1-11+1)Т7. Выставленное значение отсчета случайного процесса поступает на первый вход блока 2 сравнения, который осуществляет его сопоставление с постоянно присутствукнцим на втором входе блока 2 значением х, , определенным согласно соотношению (1). Одновременно значение х(1-11+1)т поступает на второй информационный вход второго сумматора. Однако данное значение не передается в накапливающий сумматор 27 сумматора 7, поскольку триггером 30, установленным в нулевое состояние, блокируется пропускание первого тактового импульса 1 с выхода 15 распределителя 11 на выход элемента ИЗ сумматора 7 (фиг. 3). При этом триггер 30 по заднему фронту первого тактового импульса 1 т.е. при переходе этого сигнала из состояния I в О устанавливается в состояние 1,в котором он находится вплоть до окончания текущего вычислительного процесса. Таким образом, в результате пере{спючения триггера 30 в единичное состояние все последукхцие (Н-1) такто вые импульсы с выхода 15 распредели ;теля 11 транслируются элементом И 3 сумматора 7 на адресный вход коммутатора 28. Тем самым обеспечивается по мере выборки из блока 1 памяти всех последуницих (М-1) отсчетов x(i-j)T, О j б(М-1), их последовательное суммирование накапливаю щим сумматором 27 сумматора 7. В ит ге по окончании выработки распредел телем 11 указанного цуга из М такто вых импульсов, т.е. по окончании те кущего вычислительного процесса, на капливающим сумматором 27 сумматора 7 подсчитывается сумма значений (М-1) последних отсчетов случайного процесса Q Ex()T (2) которая будет храниться в накапливающем сумматоре вплоть до начала следуняцего (i+l)-ro цикла определения интервалов стационарности дискретного случайного процесса по скользящей выборке. Одновременно вырабатываемые на выходе 15 распределителя II тактовы импульсы поступают на управляющий вход.блока 3 определения длины серий. Тем самым в такт с подачей с выхода блока памяти на первый информационный вход блока 2 сравнения последовательности X f(i-j )тЗ зарегистрирован1 1ых (0 jiM-l) отсчетов производится сопоставление калодаго из них со значением Соответственно на информационный вход 20 блока 3 поступает сигнал 1 при X (i-j )ТЗ :г: X р . и сигнал. О при xf(i-j)T х, . Указанный сигнал с выхода блока 2 сравнения поступает на информационный Вход синхроиного триггера 34 блока 3 и одновременно на один из входов элемента 35 ИСКЛЮЧАЮЩЕЕ ИЛИ. Элемент 35 производит сопоставление поступившего с выхода блока 2 логического сигнала с предыдущим результатом сравнения, выставленным на его другом входе с выхода триггера 34. В результате на вход элемент И-НЕ 36 поступает сигнал О, когда результат текущего сопоставления значения отсчета )Tj с медианным значением х.. относится к той же категории, что и выставленный на выходе триггера 34 результат сопоставления с Xcf предыдущего отсчета X (i-j-l)T |.йными словами,если серия продолжается то в этом случае на выходе 17 блока 3 гасящий импульс не вьфабатывается. Благодаря этому соответствующий тактовый импульс с управляющего входа 15, транслируясь блоком 3 через элемент 38 задержки на информационнь выход 17, увеличивает показания счетчика 4 на единицу. При этом такой процесс последовательного увеличения показаний счетчика 4, т.е. подсчет длины qтекущей серии, продолжается до тех пор, пока от блока 2 сравнения на информационный вход 20 блока 3 не поступит сигнал иной категории и соответственно элементом 35 ИСКШОЧАЮЩЕЕ ИЛИ не будет сформирован сигнал 1. В этом случае блок 3 сформирует на своем гасящем выходе 18 импульс О. По переднему фронту этого импульса поступающего на управляющий вход (синхровход) сумматора 6, в последнем производится накапливающее суммирование цифрового кода, выставленного на его информационный вход блоком 5 постоянной памяти. , Таким образом, при каждой фикса ции окончания текущей серии накапливаемый сумматором 6 цифровой код соответствует квадрату длины серии числа q -, выставленного счетчиком 4 на адресные входы блока 5 постоянной памяти. По окончании i-ro текущего вычислительного процесса в сумматоре. 6 в соответствии с используемой критерием Рамачандрана - Ранганатана статистикой N для суммы квадратов длин серий накапливается цифровой код, равный величине где Па - число серий длины q:. При этом корректный подсчет статистики в каждом i-M вычислительном цикле обеспечивается также тем, что с момента начала регистрации распределитель I1 разрешает работу снимает запрет/ лишь с поступлением М-го отсчета исследуемого дискретного случайного процесса , т.

7

Связь распределителя I1 с блоком 3 может быть реализована путем подачи от распределителя I1 на третий (не показан вход элемента И-НЕ 36 блокирующего уровня О в течение приема (с момента начала регистра- ции) первых (M-I) отсчетов процесса , Xj. С помощью этого же изна:- чапьно блокирукадего уровня О может быть обеспечена начальная уста новка счетчика 39 по модулю М блока 3 в отсчетное нулевое состояние. Тогда каждый раз по окончании скользящего цикла определения интервалов стационарности ., ij по скользящей выборке сигнал переполнения с выхода счетчика 39 по модулю М запускает по синхровходу формирователь АО импульсов. Импульс I, задержанный элементом 41 на время, необходимое для приема счетчиком 4 последнего информационного сигнала с выхода 17, поступает на вход ЗАПРЕТ элемента 42. В результате на гасящем выходе 18 блока 3 каждый раз формируется дополнительный tmпульс О. По переднему фронту импульса О и производится в сумматоре 6 накопление цифрового кода . блока 5j постоянной памяти, завершающее (в рассматриваемой ситуации) подсчет по соотношению (3) статистик N; в текущем i-м цикле определения интервалов стационарности процесса ,xfi, ij по скользящей выборке.

Накопленное в сумматоре 6 знача- ние статистики N сравнивается в

985408

блоке 8 с заданным критическим значением NH для суммы квадратов длин серий. При этом, если Kj NK, то при уровне значимости сс PlN к

5 для используемого критерия Рамачандрана - Ранганатана на испытуемом объ-. еме М скользящей выборки {м - четное число) делается вывод о нестациокарности контролируемого дискрет0 ного случайного процесса на исследованном интервале его реализаций. В этом случае блок 8 вьюает на первый информационный выход 21 устройства соответствующий сигнал.

На этом вычислительный цикл по проверке стационарности контролируемого случайного процесса на текущем интервале его реализации завершается. При этом одноврег-.енно с выработкой (по очередному синхросигналу на входе 13) распределителем II импульса 1 на своем втором выходе 16 для приема следующего отсчета контролируемого процесса , fj посредством этого же импульса I производится обнуление сумм атора. Тем самым, по рассмотренной алгоритмической схеме начинается новый (+1)-й вычислительный цикл по проверке стационарности контролируемого дискретного случайного процесса на Скользящем интервале его реализации, для которого предлагаемым устройством уже подготовлено (вычислено)соответствующее значение

..,).

fue. 2

rg

27

j;

W

/5

фиг. 3

| Устройство для определения стационарности случайного процесса | 1977 |

|

SU717781A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Широтно-импульсное множительное устройство | 1981 |

|

SU1015395A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1984-06-21—Подача