ны с отрицательным полюсом источника питания, коллекторы одноименных основных транзисторных ключей в группах, являющихся выходами блоков горизонтальных координатных ключей, через нагрузочные резисторы включены в цепи эмиттеров соответствующих вспомогательных вертикальных транзисторов, подключенных коллекторами к положительному полюсу источника питания, одноименные основные транзисторные ключи, эмиттеры которых являются выходами первого блока вер- тикальньпс координатных, ключей, подключены коллекторами в цепь эмиттеров соответствующих вспомогательных

98541

вертикальных транзисторов, соединенных коллекторами с; положительным полюсом источника испытательного тока, а одноименные основные транзисторные: ключи коллекторы которых являются выходами второго блока вертикальных координатных ключей, соединены эмиттерами с коллекторами соответствующих вспомогательных вертикальных транзисторов, подключенных эмиттерами к отрицательному полюсу источника испытательного тока, базы вспомога- тельных транзисторов блоков горизонтальных и вертикальных координатных ключей являются адресными входами коммутатора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Матричный регистратор | 1979 |

|

SU858004A1 |

| Матричный регистратор гальванических связей | 1975 |

|

SU607228A2 |

| МАТРИЧНЫЙ РЕГИСТРАТОР ГАЛЬВАНИЧЕСКИХ СВЯЗЕЙ | 1972 |

|

SU327482A1 |

| Постоянное запоминающее устройство | 1982 |

|

SU1112411A1 |

| ИЗМЕРИТЕЛЬНЫЙ КОММУТАТОР СЕТОЧНОЙ ЭЛЕКТРОМОДЕЛИ | 1967 |

|

SU222757A1 |

| Устройство для индикации | 1982 |

|

SU1072093A1 |

| Устройство для выборки информации из блоков памяти | 1976 |

|

SU641495A1 |

| Устройство для управления симистором | 1986 |

|

SU1403277A1 |

| Матричный коммутатор | 1974 |

|

SU530459A1 |

| Запоминающее устройство | 1976 |

|

SU690564A1 |

МАТРИЧНЫЙ КОММУТАТОР, содержащий два блока горизонтальных координатных ключей, два блока вертикальных координатных ключей, дополнительные -транзисторные ключи и две транзисторные матрицы, включающие несколько секций, число ,которых равно числу дополнительных транзисторных ключей, каждая секция двух транзисторных матриц состоит из транзисторов, объединенных в группы, число которых определяется числом выходов блоков горизонтальных координатных ключей, а число транзисторов в группе - числом выходов блоков вертикальных координатных ключей, в каждой группе базы транзисторов через ограничительные резисторы подключены к выходам эмиттерных повторителей каждой секции, нагрузочные резисторы которых соединены с отрицательныг- полюсом источника питания, а коллекторы включены в цепь эмиттера дополнит ельного транзисторного ключа соответствующей секции, базы дополнительных транзисторных ключей являются адресными входами выбора секции коммутатора, а коллекторы подключены к положительному полюсу источника питания , базы эмиттерных повторителей одноименных групп транзисторов всех секций через ограничительные резисторы соединены с выходами блоков горизонтальных координатных ключей, коллекторы одноименных транзисторов в группах всех секций первой транзисторной матрицы подключены к выходам первого блока вертикальных координатных ключей, эмиттеры транзисторов всех секций первой транзисторной матрицы и коллекторы транзисторов всех секций второй транзисторной матрицы являются выходами коммутатора, эмиттерь одноименных транзисторов в группах всех секций второй транзис« торной матрицы соединены с выходами (Л второго блока вертикальных координатных ключей, отличающийсятем, что, с целью сокращения аппаратурных затрат, в нем блоки горизонтальных и вертикальных координатных ключей состоят из основных транзисторных ключей и вспомогательньпх го:о эо ризонтальных и вертикальных транзисторов, основные транзисторные клюСП чи блоков горизонтальных и верти4 кальных координатных ключей объединены в группы, число которых определяется числом вспомогательных горизонтальных транзисторов, а число транзисторов в группах - числом вспомогательных вертикальных транзисторов, базы основных транзисторных ключей каждой группы через ограничительные резисторы подключены к положительному полюсу источника питания, эмиттеры основных транзисторных ключей блоков горизонтальных координатных ключей и вспомогательных горизонтальных транзисторов соедине

Изобретение относится к автоматике и может быть Использовано при автоматизированном контроле правильности электрического монтажа радиоэлектронного оборудования.

Целью изобретения является сокращение аппаратурных затрат.

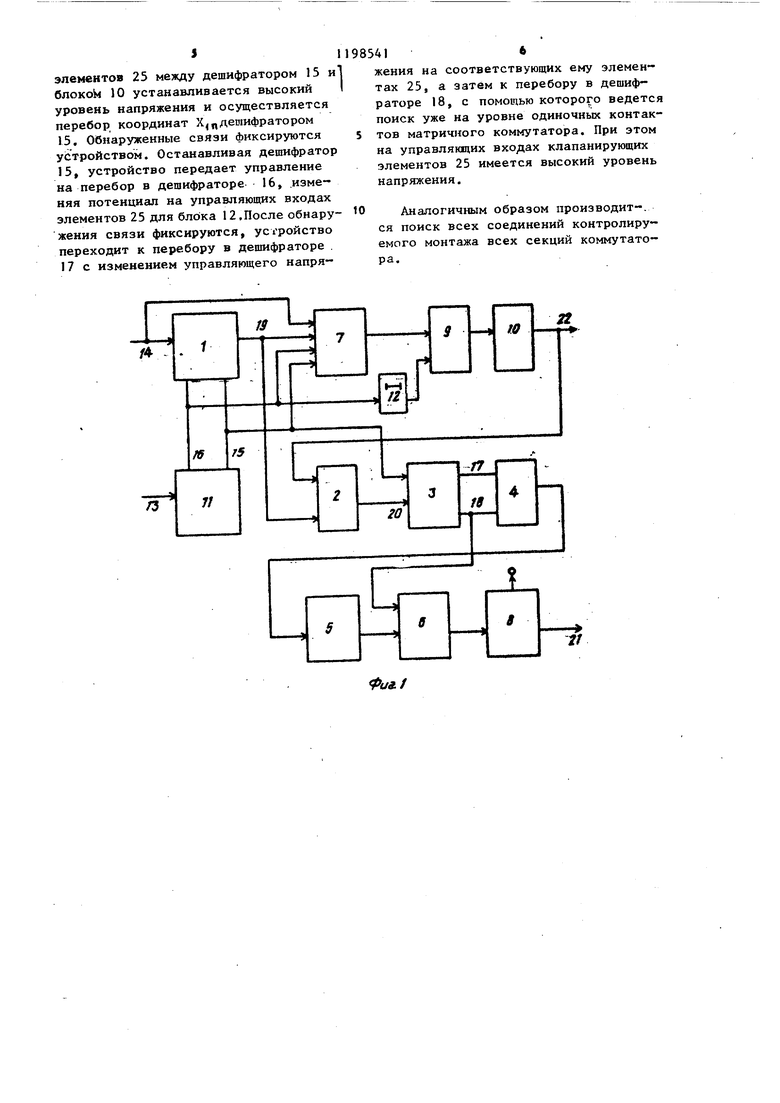

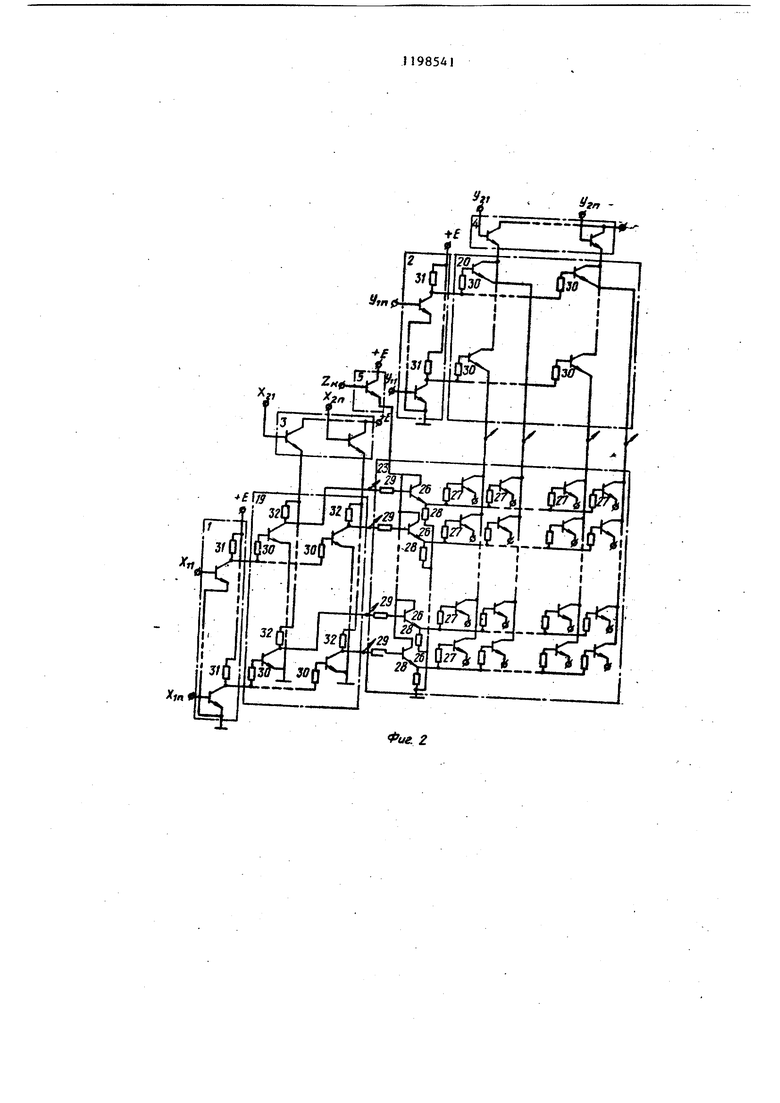

На фиг. 1 приведена структурная схемаматричного коммутатора; на фиг, 2функционапьная схема одной секции первой транзисторной матрицы; на фиг. 3 - функциональная схема одной секции второй транзисторной матрицы.

Коммутатор содержит (фиг. 1, 2, З) блоки 1 и 2 вспомогательных горизон- тальн 1х транзисторов, блоки 3 и 4 вспомогательных вертикальных транзисторов, дополнительные ключи 5, дешифраторы 6-9 первой транзисторной матрицы, блоки 10 и П вспомогательных горизонтальных транзисторов, блоки 12 и 13 вспомогательных вертикальных транзисторов, дополнительные ключи 14 второй транзисторной матрицы, дешифраторы 15-18 адресов, блоки 1922основных горизонтальных и вертикальных транзисторных ключей секции

23и 24 выходных транзисторов, клапанирующие элементы 25, эмиттерные повторители 26, резисторы 27-32.

Устройство работает следующим образом.

В исходном состоянии (фиг. 2 иЗ) на базах транзисторов в блоках 1,

3, 4, 5, 10, 12, 13 и 14 устанавливается низкий потенциал, а на базах транзисторов в блоках 2 и 11 - высокий потенциал. Все транзисторные

ключи во всех секциях первой и второй транзисторных матриц заперты. Во второй транзисторной матрице, кроме одиночных переключений выходных транзисторов секции 24, необходимо произвести групповые переключения для повышения быстродействия контроля. Это обеспечивается клапанирующими элементами 25, которые между блоками 15 и 10, 16 и 12, 18 и 13

функционально выполнены в виде элементов И-НЕ, а между блоками 17 и 11 - в виде элементов И, На выходах дешифраторов 15-18 в исходном положении имеется высокий потенциал,

В режиме одиночного контроля на разрешающие входы клапанирующих элементов 25 подан высокий потенциал. Подачей низкого потенциала на разрешающие входы клапанируннцих эле ментов 25 осуществляется переход к групповым режимам контроля.

Предположим, чтоВ режиме одиночной проверки заданы два кода контролируемых контактов, В этом случае

для первой матрицы выбраны, например вспомогательные координаты Х,, , и дополнительная шина Z а для второй матрицы Х-, j ) 2) и дополнительная шииа Z. При

31

этом положительный потенциал на базе i-ro вспомогательного транзистора блока 1 открьшает его, и напряжение низкого уровня с его коллекторного сопротивления 31 поступает на группу основных транзисторов блока 19 горизонтальных координатных ключей. Через ограничительные резисторы 30 потенциал низкого уровня, поданный на базы основных транзисторов этой группы, закрывает их. Потенциал на базе i-ro транзистора блока 3 открывает его,и напряжение источника питания +Е поступает на i-e транзисторы блока 19 горизонтальных координатных ключей. Выбранный таким образом транзистор имеет на своем коллекторном сопротивлении 32 высокий уровень напряжения, поступающий через ограничительные резисторы 29 на базе соответствующих эмиттерных повторителей 26 (фиг. 2). С дополнительного ключа 5 соответствующей секции, выбранной координатой Z.,, напряжение +Е подается на коллекторы эмиттерных повторителей 26, один из которых открывается, и высокий потенциал с его нагрузочного резистора 28 поступает на группу выходных транзисторных ключей секции

I

Выбор вертикальной шины производится следующим образом.

Потенциал низкого уровня подается на базу выбранного i-ro вспомогательного горизонтального транзистора блока 2, который запирается, и высокий уровень напряжения с его коллекторе через ограничительные резисторы 30 поступает на базы основных транзисторов соответствующей группы блока 20 вертикальных координатных ключей. Выбранная координата Y,, , поданная высоким уровнем напряжения на базу i-ro транзистора блока 4, открывает его, и положительный полюс источника испытательного тока подключается к соответствующим транзисторам блока 20 вертикальных координатных ключей. В вертикальном ряду тр;1нзисторов блока 20 вертикальных координатных ключей, на которые подано напряжение источника испытательного тока, лишь один транзистор принадлежит группе, на которую поступает высокий уровень напряжения из блока 2, и обеспечивает- передачу напряжения испытательного тока в вертикальный ряд выходных

41

транзисторов секции 23. Совпадение на базе одного из транзисторов секции 23 отпирающего напряжения с наличием напряжения источника испытательного тока на коллекторе обеспечивает появление на соответствующем выходе коммутатора напряжения испытательного тока.

Подключение выходного контакта

коммутатора к отрицательному полюсу источника исш11тательного тока, соответствующего заданным координатам

} .2J ) 2) m секции 24, производится аналогичным образом

При наличии электрической связи между выбранными контактами коммутатора, соответствующими заданным координатам, создается цепь для прохождения испытательного тока, по величине

которого можно судить о правильности монтажа объекта, подключенного к контактам матричного коммутатора.

Наличие клапанирующих элементов 25 матричного коммутатора в составе

устройства для контроля монтажа позволяет произвегти оперативный поиск контактов электрического монтажа, принадлежащих какой-либо цепи. В этом случае переходят к группонвлм

режимам контроля. Предположим, не обходимо найти электрические связи в монтаже контролируемого объекта с контактом, имеющим адрес, заданный координатами X,, , X.,, , Y, , Y , ,

В соответствии с заданным адресом формируются управляющие сигналы на блоки 1, 2, 3, 4и5, ав итоге положительное напряжение источника испытательного тока появляется на

эмиттере выходного транзистора секции 23 первой матрицы. Одновременно на все управляющие входы клапанирукгщих элементов 25 подается напряжение низкого уровня, что обеспечивает

подключение выходных транзисторов секции 24 второй матрицы к отрицательному полюсу источника испытатель кого тока. При наличии электрической связи контакта первой матрицы с кон тактами второй матрицы устройство переходит к поиску соединений, Дпя этого сначала осуществляется перебор секции 24 второй матрицы при помоп и

дополнительных шин Z блока 14, При обнаружении соединения в какой-либо из секций устройство переходит к поиску внутри этой секции, для чего на управляющих входах клапанирующих

1

элементов 25 между дешифратором 15 и1 блокоЪ4 10 устанавливается высокий I уровень напряжения и осуществляется перебор координат Х,„летифратором 15, Обнаруженные связи фиксируются устройством. Останавливая дешифратор 15, устройство передает управление на перебор в дешифраторе 16, изменяя потенциал на управляющих входах элементов 25 для блока 12,После обнаружения связи фиксируются, устройство переходит к перебору в дешифраторе 17 с изменением управляющего напря1985416

жения на соответствующих ему элементах 25, а затем к перебору в дешифраторе 18, с помощью KOTOpo io ведется поиск уже на уровне одиночных контактов матричного коммутатора. При этом на управлягадих входах клапанирующих элементов 25 имеется высокий уровень напряжения.

О Аналогичным образом производит-, ся поиск всех соединений контролируемого монтажа всех секций коммутатора.

Ха Хгп- Ж liilS . Jy

0t/e 3

| Матричный регистратор гальванических связей | 1975 |

|

SU607228A2 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Матричный регистратор | 1979 |

|

SU858004A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1985-12-15—Публикация

1984-02-10—Подача