Изобретение относится к вычисли тельной технике, а именно к устройствам для обработки информации специального назначения, и может быть использовано при построении спецнали зированных вычислительных устройств для моделирования сетевых задач, в частности задач ортаниза- ционного управления.

Цель изобретения сокращение уппаратурных затрат при моделирова НИИ сетевых задач.

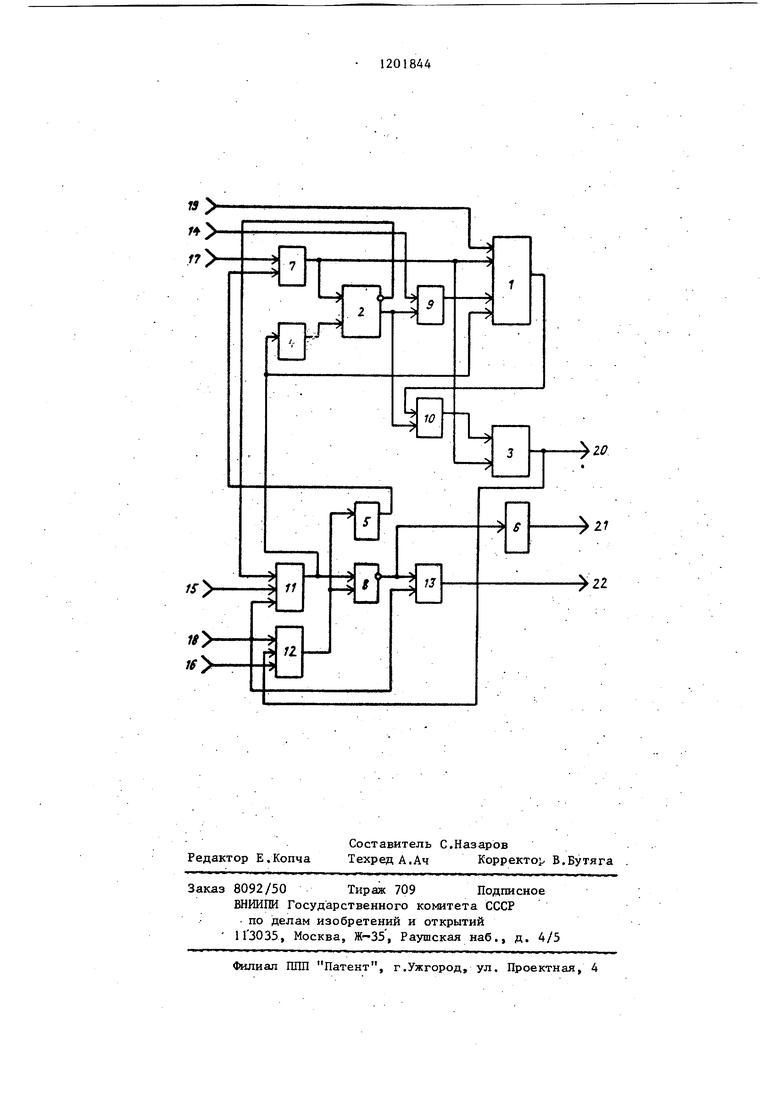

На чертеже изображена функциональная схема модели ветви сети.

Устройство содержит формирователь 1 временного интервала, трцг- гер 2 занятости, триггер 3 прерывания, элементы 4 и -5 задержки, шифратор 6 адреса, элемент ИЛИ 7, элемент ШШ-flE 8, элементы И 9-13.

Формирователь 1 временного интервала предназначен для формирования задержки сигнала, пропорциональной длительности моделируемой ветви сети. Он может быть выполнен на основе счетчико-регистро№1х структур. Триггер 2 занятости предназначен дл определения занятости данной модели Триггер 3 прерывания предназначен для фиксации момента окончания моделирования ветви сети. Элементы 4 и 5 з.адержки предназначены для формирования разрешающего сигнала, задержанного относительно сигнала на входных полюсах 15 и 16 на время большее времени действия, этого сиг.нала. ..

Шифратор 6 адреса предназначен для формирования кода, соответствующего номеру данной модели ветви.

Входами устройства являются полюса 14-19. Входной пдлюс 14 предназначен для подключения генератора импульсов. Входные полюса 15 и 16 служат для приема сигналов анализа состояния данной модели. Входной полюс 17 является полюсом общего сброса. Входной полюс 18 предназначен для приема сигнала запрета из предыдущей модели ветви. Входной полюс 1-9 служит для приема кода длительности ветви сети.

Входами устройства являются полю са 20-22. Полюс 20 служит для выдачи сигнала прерывания, который соответствует концу моделирования иременного интервала данной моделью Полюс 21 предназначен для выдачи

кода данной модели. Полюс 22 служит .для выдачи сигналуа запрета на все модели, следуницие за данной. Устройство работает следующим

образом.

Для решения сетевой задачи все модели соединяются между собой следующим образом. Входные полюса 14-17 и 19 всех моделей объединяются между собой. На входной полюс 18 первой модели постоянно подается разрешающий потенциал. Выходной полюс 22 первой модеди соединен с входным полюсом 18 второй модели,

5 выходной полюс 22 второй модели соединен с входным полюсом 18 третьей модели и т.д.

Процесс моделирования ветви графа происходит следующим образ.ом.

0 Ищется свободная модель. Для этого на входной полюс 15 полается сигнал, которьй поступает на вход элемента И 11 всех моделей. Анализ состояния модели начинается.с модели, стоящей

5 на первом месте. Если в первой модели триггер 2 занятости находится в состоянии О, то разрешающий потенциал с его нулевого выхода поступает на второй вход элемента И 11.

0 На третий вход этого элемента, постоянно подается разрешаниций потенциал с входного полюса.18, На выходе элемента И 11 появляется сигнал, который подается на вход элемента ИЛИ-НЕ 8, На вы:соде элемента ИЛИ--НЕ 8 появляется, сигнал, которьй поступает на вх9д шифр.атора 6 адреса, разрешая формирование кода, соответствующего номеру данной ветви. Этот код соответствует номеру свободной модели, и для этой модели назначается ветвь графа, которую необходимо моделировать. Таким образом, ставится в однозначное соответствие номер ветви графа и номер модели, в которую записывается длительность данной ветви. Кроме того,-сигнал с выхода элемента ИЛИ-НЕ 8 поступает на вход элемента И 13. На выходе элемента 13 появляется сигнал запрета. Этот сигнал поступает на выходной полюс 22, а с него - на входной полюс 18 второй модели. На второй модели сигнал запрета с входного полюса 18

5 поступает на вход элемента 11 и

запрещает прохождение сигнала анализа с входного полюса 15, Кроме этого, сигнал запрета на второй

модели с входного полюса 18 поступает на вход элемента И 13. На выходе элемента появляется сигнал запрета, который через выходной полюс 22 поступает на входной полюс 18 третьей модели и т.д. Таким образом сигнал запрета поступает на все модели, кроме первой.

Если пер-вая модель занята (триггер 2 в состоянии 1), потенциал запрета с нулевого выхода триггера 2 поступает на вход элемента И 11, запрещая прохождение сигнала с входного полюса 15. Запрет на вь1ходе элемента И 13 не формируется, и на выходном полюсе 22 присутствует потенциап разрешения. Этот потенциал подается на входной полюс 18 второй модели, разрешая анализ ее состояни Если триггер 2 в этой модели находится в состоянии 1, то и на этой модели сигнал запрета не формируетс и подается потенциал разрешения на входной полюс 18 третьей модели. Этот процесс происходит до тех пор, пока не обнаруживается модель, у которой триггер 2 в состоянии О (модель свободна). На этой модели .формируется сигнал запрета, который ; через вь)ходной. полюс 22 подается на входной полюс 18 следуннцей модел ;ветви и через элемент И 13 и выходной полюс 22 - на входной полюс 8 следующей модели и т.д. Таким образом, происходит распространение сигнала запрета на все модели за |перврй свободной.

; На первой свободной модели сигнала разрешения с выхода элемента ;И 11 подается на вход разрешения записи формирователя временного ин- тервапа 1. На информационные входы через входной полюс 19 поступает код, дополняющий код длительностиМО дел ируе мой ветви графа до полного объема счетчиков формирователя 1. Происходит запись этого кода в формирователь 1. Кроме того, сигнал с выхода элемента И 11 поступает на вход элемента задержки 4. По истечении времени, большего, чем время действия сигнала на входном полюсе 15, на выходе элемента 4 задержки появляется разрешающий сигнал, кото рый поступает на вход установки в 1 триггера 2. Триггер 2 устанав1ливается в 1, и йотенциап с его нулевого выхода запрещает прохождение сигнала с входного полюса 15

через элемент И 11. Почвление следую щего импульса на входном полюсе 15 не влияет на состояние схеьы данной модели.

Если в данный момент для моделирования назначены еще ветви графа, то на входной полюс 15 подается следукшщй импульс, и процесс поиска свободной модели и записи в нее длительности ветви графа повторяется. После записи длительности всех ветвей графа, -назначенных в данный момент времени для моделирования, на входной полюс 14 всех кюделей

начинают поступать импульсы генерато ра импульсов Входной полюс 14 соединен с входом элемента И 9. Если триггер 2 данной модели стоит

в 1 (модель занята), на второй

вход элемента И 9 подается разрешающий потенциал с выхода триггера 2. Поэтому импульсы генератора импульсов через элемент И 9 поступают на счетный вход формирователя вре5 менного интервала 1. После прихода количества импульсов, равного длительности ветви графа, записанной в данную модель, на выходе форми роват.еля 1 появляется сигнал переполнения . Этот сигнал поступает на вход элемента И 10, на другой вход которого подается разрешающий потенциал с выхода триггера 2. На выходе элемента И 10 появляется разрешающий сигнал, который поступает на вход установки в единичное состояние триггера 3. Триггер 3 устанавливается в 1, и потенциал прерывания с его единичного выхода поступает на выходной полюс 20, сигнализируя об окончании моделирования ветви графа, записанной в дан9ую модель.

Потенциал с выхоДного полюса 20 запрещает выработку импульсов генератора импульсов и разрешает выдачу сигнала на входной полюс 16 для анализа моделей ветви, выставивших прерывание .

Анализ начинается с модели, стоящей на первом месте. Если у этой модели триггер 3 прерывания стоит в О, то сигнал запрета с единичного выхода триггера 3 подается на вход элемента И 12,.запрещая про-

хождение сигнала с входного полюса 16. На выходе эелмента ИЛИ-НЕ не формируется сигнал разрешения фор.мирования кода модели, а на выходе элемента И 13 не формируется aanpei на анализ следунщих моделей. На выходном полюсе 22 присутствует потен циал разрешения, который подается на входной полюс 18 второй модели. Если у второй модели триггер 3 прерывания стоит в О, код этой модели не формируется, и потенциал разрешения через выходной полюс 22 подается на входной полюс 18 третьей модели и т.д. Этот процесс происхо дит до тех пор, пока не обнаружится модель, у которой триггер прерывания 3 установлен в 1. У этой модели на первый вход элемента И 12 подается потенциал разрешения с единичного выхода триггера 3, на второй вход поступает сигнал с входного полюса 16, на третий вход поступает потенциал разрешения с входного полюса 18. 11а выходе элемента И 12 появляется сигнал, который подается на вход элемента ИЛИ-НЕ 8. На выходе элемента HUmiE 8 появляется сигнал который поступает на шифратор 6 адреса, разрешаф формирование кода данной модели. С выхода шифратора 6КОД модели поступает на выходной полюс 21. По этому коду определяется номер ветви сети, моделирование которой окончено, и те ветви, которы необходимо подключить к моделированию на следующем этапе. Кроме того, сигнал с выхода элемента ИЛИ-НЕ 8 поступает на вход элемента И 13, С выхода элемента И 13 сигнал через выходной полюс 22 поступает на все модели, стоящие за данной моделью. Сигнал с выхода элемента И 12 поступает на вход элемента 5 задержки. По истечению времени задержки . на выходе элемента 5появляется сигнал, который подается на вход элемента ШШ 7. На выходе элемента 7 появляется сигнал разрешения. Этот сигнал подается на вход установки в нулевое состояние формирователя 1временного интервала, триггеров 2и 3. После этого схема приводится висходное состояниеи готовадля моделирования следующей ветви графа . .1 . . Использование новых элементов шифратора, первого элемента ИЛИ, второго элемента ИЛИ-НЕ, первой и второй линии задержки, соединенных соответствующими связями позволяет организовать параллельное моделирование сетей с числом моделей ветвей в устройстве меньшим, чем количество ветвей в исследуемом графе, которое достигается за счет многократного использованич одних и тех же моделей ветвей. В известных устройствах дпя моделирования той де задачи необходимо для каждой ветви иметь соответствующую модель ветви, которая в процессе решения используется только один раз. Предлагаемое устройство может -быть использовано как самостаятельный узел в специализированном вычислителе дпя моделирования длительности ветвей исследуемого графа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Модель ветви сети | 1988 |

|

SU1585802A2 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для решения сетевых задач | 1988 |

|

SU1564643A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для моделирования экстремальных путей на графе | 1980 |

|

SU926670A1 |

МОДЕЛЬ ВЕТВИ СЕТИ, содержащая формирователь временного интервала, выполненный в виде счетчика, триггер прерывания, триггер занятости, пять элементов И, причем первый вход первого элемента И является счетным входом модели ветви се- . ти, выход первого элемента И соединен со счетным входом формирователя вре- меиного интервала, информационный вход которого является входом кода длительности ветви сети, выход формирователя временного интервала соединен с первым входом второго элемента И, выход которого подключен к единичному входу триггера прерывания, единичный выход которого соединен с первым входом третьего элемента И, выход пятого элемента И является выходом сигнала запрета модели ветви сети, отличающая ся тем, что, с целью сокращения аппаратурных затрат, в нее введены элемент ИЛИ, элемент ШШ-41Е, первый и второй эле-. менты задержки и шифратор, причем первый вход первого элемента ИЛИ является входом сброса модели ветви сети, выход первого элемента ИЛИ подключен к нулевым входам, триггера занятости, триггера прерывания и входу установки в О формирователя временного интервала, нулевой выход триггера занятости соединен с первым входом четвертого элемента И, выход которого подключен к первому входу элемента ИЛИ-НЕ, входу разрешения установки кода формирователя временного интервала и через первьш элемент задержки - к единичному входу триггера занятости, второй вход элемента ШШ-ИЕ соединен с выходом тре- (О т.ьего элемента И и входом второго элемента задержки, выход которого подключен к второму входу элемента ИЛИ, выход элемента ИЖ-НЕ соединен с первым входом пятого элемента И и входом шифратора, выход которого является выходом кода модели ветви сети, вторые входы третьего, четвертого и пятого элементов И объеданены и являются входом сигнала запрета эо j 1 модели ветви сети, третий вход третьего элейент а И является входом прерьшания модели ветви сети, третий вход четвертого элемента И - входом определения занятости модели ветви сети, единичный выход триггера прерываний соединен с первым входом третьего элемента И и является выходом прерывания модели ветви сети, а единичный выход триггера занятости подключен к вторым входам первого и второго элементов И.

| 1972 |

|

SU422002A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Модель ветви графа | 1973 |

|

SU470811A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-30—Публикация

1983-10-10—Подача