Изобретение относится к вычислительной технике и может быть использовано для исследования путей в сети.

Цель изобретения - расширение функциональных возможностей устройства за счет решения задачи коммивояжера о

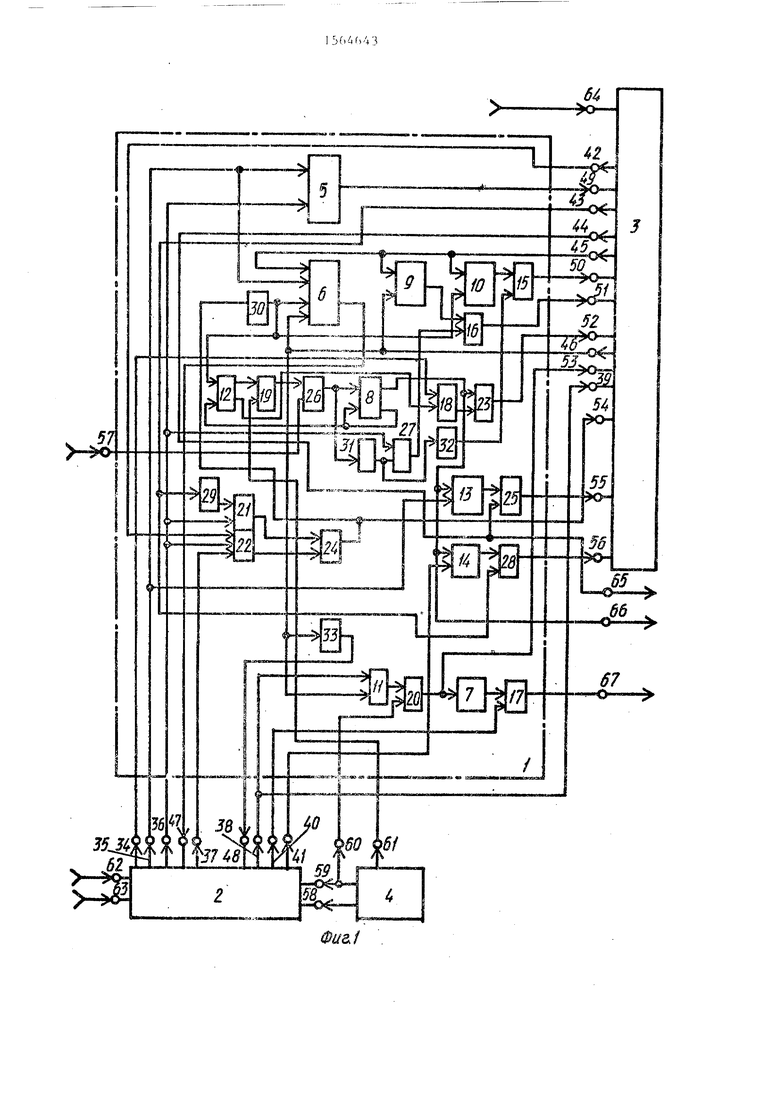

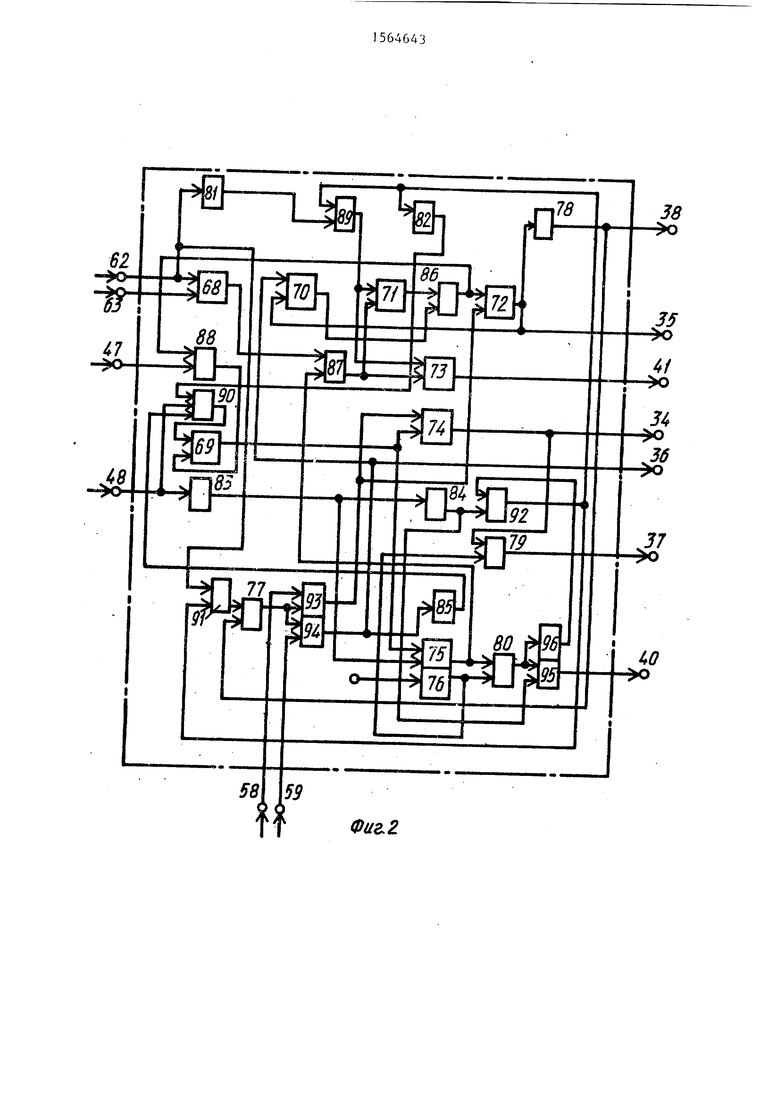

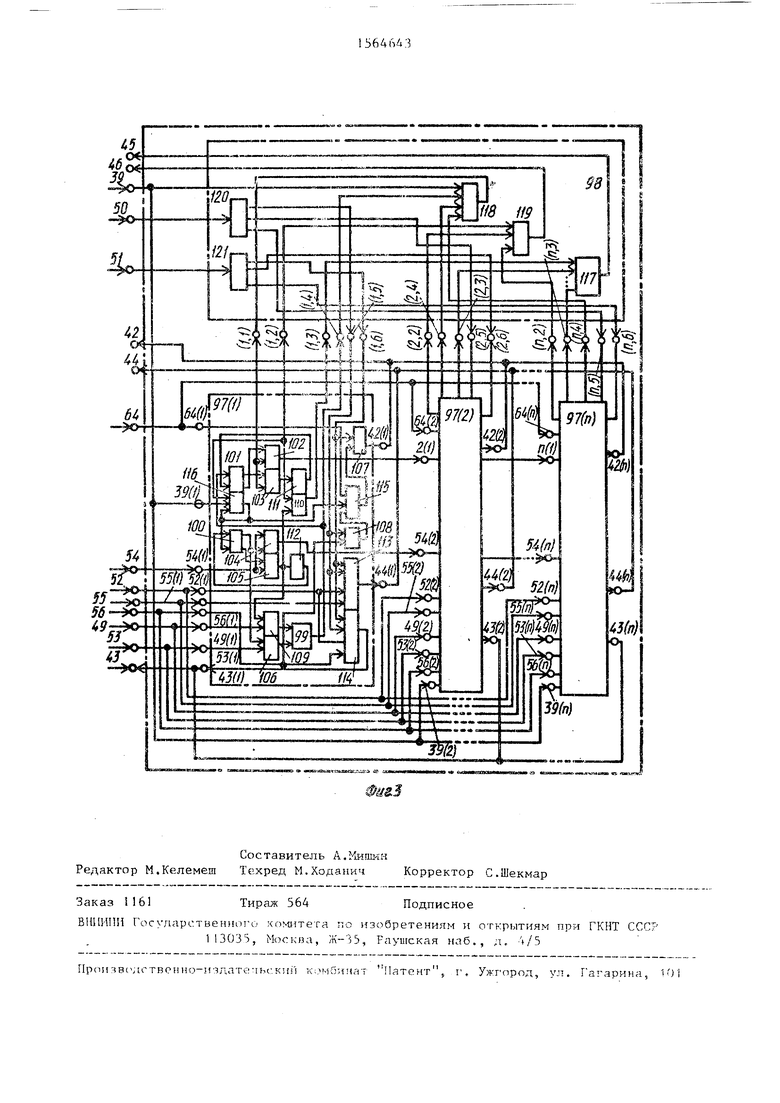

На фиг.1 представлена функциональная схема устройства; на фиг.2 - то же, блока формирования топологии; на фкг.З - то же, блока моделирования сети.

Устройство содержит блок 1 управления, блок 2 формир .вани/: топологии, блок 3 моделирования сети и блок 4 синхронизации.

Блок 1 управления содержит узел

5памяти длительности ветвей, узел

6памяти номеров моделируемых ветвей,. узел 7 измерения пути, узел 8 формирования адреса меток моделирования, регистр 9 номера отработавшей модели ветви, регистр 10 номера свободной модели ветви, триггер 11 прерывания, триггер 12 формирования меток моделирования, узел 13 сравнения номеров ветвей, 14 сравнения номеров узлов, узлы 15 - 18 элементов U, -элементы И 1 9 - 22,узел 23 элементен И И, элементы ИЛИ 24 - 28,элемент III 29, элементы задержки 30 - 33.

СЛ

О) Ј

О5 Јь СО

Выход номера конечного узла ветви блока 2 формирования топологии соединен через полюс 34 с входом узла 18 элементов И блока 1 управления. -Выход номера подготавливаемой к моделированию ветви блока 2 формирования топологии соединен через полюс 35 с адресным входом узла 5 памяти и с входом схемы 13 сравнения блока 1 управ- JQ пения. Выход поиска свободной модели ветви блока 2 формирования топологии соединен через полюс 36 с входом считывания узла 5 памяти, с входом эле- ентов И 21, 22 и через элемент ИЛИ 55 27 с входом узла 16 элементов И блока 1 управления. Выход признака конечной ветви сети блока 2 формирования топологии соединен через полюс 37 с входом элемента И 22 блока 1 управ- 20 пения. Выход поиска прерывания блока 2 формирования топологии соединен через полюс 38 с единичным входом триггера 11 прерывания блока 1 управления

чала анализа свершения ветви блока 2 подключен через полюс 48 к одноименному входу блока 1, выход кода длительности ветви блока 1 подключен через полюс 49 к одноименному входу блока 3, выход записи меток моделирования узла блока 1 подключен через полюс 50 к одноименному входу блока 3, выход считывания меток моделирования узла подключен через полюс 51 к одноименному входу блока 3, выход адреса меток моделирования узла подключен через полюс 52 к одноименному входу блока 3, тактовый выход блока 1 подключен через полюс 53 к одноименному входу блока 3, выход поиска свободной модели ветви блока 1 подключен через полюс 54 к одноименному входу блока 3, выход признака моделирования ветви блока 1 через полюс 55 подключен к одноименному входу блока 3, выход признака моделирова ния узла блока 1 подключен через пои с одноименным входом блока 3 моде- 25 5б к одноименному входу блока 3,

вход опроса устройства подключен через полюс 57 к одноименному входу блока 1, первый выход блока 4 (выДа- ет серию импульсов ГИ1) через полюс

лей ветвей через полюс 39.,Выход разрешения выдачи результата блока 2 формирования топологии соединен через полюс 40 с входом узла элементов блока 1 управления. Выход номера началь- JQ 58 подключен к первому тактовому вхо35

40

ного узла ветви блока 2 формирования топологии соединен через полюс 41 с входом схемы 14 сравнения блока 1 управления ,

Выход разрешения загрузки последней ветви сети блока 3 моделей ветвей соединен через полюс 42 с входом элемента И 22 блока 1 управления. Выход метки моделирования узла блока 3 моделей ветвей соединен через полюс 43 с входом элемента ИЛИ 28 и чарез элемент НЕ 29 с входом элемента И 21 блока 1 управления. Выход метки моделирования ветви соединен с входом элемента ИЛИ 25 через полюс 44. Выход номера модели ветви блока 3 моделей ветвей соединен через полюс 45 с адресным входом узла 6 памяти и с информационным входом регистров 9 и 10 блока 1 управления. Выход прерывания блока 3 моделей ветвей соединён через полюс 46 с входом считывания узла 6 памяти, с установочным входом регистра 9, с входом элемента 33 задержки и с нулевым входом триггера 11 блока 1 управлении.

Выход номера свершившейся ветви блока 2 подключен через полюс 47 к одноименному входу блока 1, выход на45

50

ду блока 2, второй выход блока 4 (выдает серию импульсов ГИ2) подключен через полюса 59 и 60 к второму такто- вому входу блока 2 и к первому тактовому входу блока 1, третий выход блока 4 (выдает серию импульсов ГИЗ) подключен через полюс 61 к второму тактовому входу блока 1, вход пуска устройства подключен через полюс 62 к одноименному входу блока 2, вход кода номера ветви, исходящей из начального узла сети устройства, подключен через полюс 63 к одноименному входу блока 2 вход задания количества узлов сети устройства подключен через полюс 64 к одноименному входу блока 3, выход признака принадлежности ветви кратчайшему пути коммивояжера блока 1 подключен через полюс 65 к одноименному выходу устройства, выход признака принадлежности ветви множеству путей коммивояжера блока 1 подключен через полюс 66 к одноименному выходу устройства, выход веса пути блока подключен через полюс 67 к одноименному выходу устройства.

Блок 2 формирования топологии содержит узел 68 памяти номеров начальных узлов ветвей сети, узел 69 памячала анализа свершения ветви блока 2 подключен через полюс 48 к одноименному входу блока 1, выход кода длительности ветви блока 1 подключен через полюс 49 к одноименному входу блока 3, выход записи меток моделирования узла блока 1 подключен через полюс 50 к одноименному входу блока 3, выход считывания меток моделирования узла подключен через полюс 51 к одноименному входу блока 3, выход адреса меток моделирования узла подключен через полюс 52 к одноименному входу блока 3, тактовый выход блока 1 подключен через полюс 53 к одноименному входу блока 3, выход поиска свободной модели ветви блока 1 подключен через полюс 54 к одноименному входу блока 3, выход признака моделирования ветви блока 1 через полюс 55 подключен к одноименному входу блока 3, выход признака моделирования узла блока 1 подключен через по58 подключен к первому тактовому вхо5

0

5

0

ду блока 2, второй выход блока 4 (выдает серию импульсов ГИ2) подключен через полюса 59 и 60 к второму такто- вому входу блока 2 и к первому тактовому входу блока 1, третий выход блока 4 (выдает серию импульсов ГИЗ) подключен через полюс 61 к второму тактовому входу блока 1, вход пуска устройства подключен через полюс 62 к одноименному входу блока 2, вход кода номера ветви, исходящей из начального узла сети устройства, подключен через полюс 63 к одноименному входу блока 2, вход задания количества узлов сети устройства подключен через полюс 64 к одноименному входу блока 3, выход признака принадлежности ветви кратчайшему пути коммивояжера блока 1 подключен через полюс 65 к одноименному выходу устройства, выход признака принадлежности ветви множеству путей коммивояжера блока 1 подключен через полюс 66 к одноименному выходу устройства, выход веса пути блока подключен через полюс 67 к одноименному выходу устройства.

Блок 2 формирования топологии содержит узел 68 памяти номеров начальных узлов ветвей сети, узел 69 памяти номеров конечных узпов ветвей СР- ти, узел 70 памяти номеров выходящих ветвей узлов сети,узел 71 памяти номеров первой выходящей ветви узлов сети, регистр 72 выходящей ветви,регистр 73 начального узла подготавливаемой ветви, регистр 74 конечного узла подготавливаемой ветви, регистр 75 конечного узла анализируемой ветви, регистр 76 узла сети, триггер 77, дешифратор 78, узлы 79 и 80 сравнения кодов, элементы задержки 81 - 85, узлы 86-88 элементов ИЛИ, элементы ИЛИ 89 - 91, элементы Pi 92 - 95, элемент НЕ 96.

Блок 3 моделей ветвей (фиг.З) содержит К моделей ветвей (где К - количество путей, проходящих через все узлы сети) 97 и узел 98 поиска моделей ветвей. Цифрами в скобках обозначены порядковые номера одинаковых по своему конструктивному исполнению и функциональному назначению блоков, узлов, элементов и полюсов. Каждая модель ветви 97 состоит из формирователя 99 временных интервалов, триггеров 100 и 101, 3j,«ментов И 102 - 108, узла 109 элементов И, элемента

0

5

5

114 (К), формирователи 94 (|), 99(2),

.... 99 (К) временных интервалов бпока 3 МОДОЛРЙ ветвей предварительно обнуляются. Триггеры 1 и 12 бпока

1 управления, триггер 7 блока 2 формирования топологии, триггеры 100(1),

100(2),...,100(К) и 101(1), 101(2),...

...,10(К) и формирователи 116(1),

116(2),.., 116(К) сброса модели ветви блока 3 моделей ветвей находятся первоначально в нулевом состоянии. В счетчике узлов 113(1), 115(2),..,

115(К) сети блока 3 моделей ветвей предварительно заносится код, на единицу меньший количества узлов сети.

После начального установа на полюс 63 блока 2 формирования топологии подается код номера ветви, выходящей ш узла, принятого при данном расчете за начальный узел сети, т.е. номер которого записан в регистр 76 узла сети. Таким образом, начальный узел моделирования сети определяется по адресу номера ветви в узле 68 памяти номеров начальных узлов блока 2 формирования топологии.

В некоторый момент времени сигнал Пуск, поступающий на полюс 62

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1242980A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

Изобретение относится к вычислительной технике и может быть использовано для исследования путей в сети. Целью изобретения является расширение функциональных возможностей устройства за счет решения задачи коммивояжера. Устройство содержит блок управления, блок формирования топологии, блок моделирования сети и блок синхронизации. Перед началом работы в блок формирования топологии заносят в виде списков номеров выходящих ветвей узлов сети, номеров заходящих ветвей узлов сети, номеров начальных узлов ветвей сети и номеров конечных узлов ветвей сети информацию о топологии графа. После запуска устройство реализует меточный алгоритм поиска пути коммивояжера, когда из начального угла по всем возможным направлениям выдают информационные сообщения, каждый разряд которых является меткой прохождения сообщения через соответствующий узел сети. 3 ил.

35

40

ИЛИ 110, элементов задержки 111 и 112,0 блока 2 формирования топологии, про- узла 113 памяти меток моделируемых ветвей, узла 114 памяти меток узлов, счетчика узлов 115 сети, формирователя 116 сброса модели ветви.

Узел 98 поиска моделей ветвей блока 3 моделей ветвей содержит шифра- - тор 117 адреса, элементы ИЛИ 118 и 119, дешифратор 120 записи меток, дешифратор 121 считывания меток.

Устройство работает следующим образом.

В узлы 68 - 71 памяти блока 2 формирования топологии в виде списков заносится информация о топологии моделируемой сети. Регистры 72 - 75 предварительно обнуляются, а в регистр 76 узла сети заносится код номера любого узла сети, принятого за начальный узел моделирования сети. В узел 5 памяти длительностей ветвей блока 3 управления предварительно заносится информация о длительности ветвей сети, т.е. по адресу номера каждой ветви сети записывается код ее длительности. Узел 6 памяти, узел 7 измерения пути, узел 8 формирования меток моделирования, регистры 9 и 10 блока I управления, узлы памяти ИЗ (О, ИЗ (2),. ...,113 (К) и 114 (1), 114 (2),...,

45

50

55

ходит через элемент ИЛИ 91 и устанавливает триггер 77 в единичное состояние. Единичное состояние триггера 77 разрешает прохождение серии импульсов ГИ (с первого.выхода блока 5) через полюс 58 и П-12 (с второго выхода блока 4 через полюс 59) через элементы И 93 и 94 соответственно. Кроме этого сигнал Пуск с входного полюса 62 поступает на вход элемента задержки 81 и на вход считывания узла 68 памяти начальных узлов. По этому сигналу в узле 68 памяти происходит считывание информации из ячейки памяти, ад рес которой определяется номером ветви, поступающим с полюса 63. Так как ветвь выбрана, как выходящая из начального узла моделирования сети, то на выходе узла 68 памяти формируется код этого узла, который через узел 87 элементов ИЛИ поступает на адресный вход узла 71 памяти первой выходящей ветви 7 и на информационный вход регистра начального узла 73 подготавливаемой ветви. Через время задержки, достаточное для считывания информации

из узла 68 памяти, сигнал Пуск появляется на выхо;;о элемента задержки и поступает чорез элешчп- ИЛИ 89

81

блока 2 формирования топологии, про-

ходит через элемент ИЛИ 91 и устанавливает триггер 77 в единичное состояние. Единичное состояние триггера 77 разрешает прохождение серии импульсов ГИ (с первого.выхода блока 5) через полюс 58 и П-12 (с второго выхода блока 4 через полюс 59) через элементы И 93 и 94 соответственно. Кроме этого, сигнал Пуск с входного полюса 62 поступает на вход элемента задержки 81 и на вход считывания узла 68 памяти начальных узлов. По этому сигналу в узле 68 памяти происходит считывание информации из ячейки памяти, адрес которой определяется номером ветви, поступающим с полюса 63. Так как ветвь выбрана, как выходящая из начального узла моделирования сети, то на выходе узла 68 памяти формируется код этого узла, который через узел 87 элементов ИЛИ поступает на адресный вход узла 71 памяти первой выходящей ветви 7 и на информационный вход регистра начального узла 73 подготавливаемой ветви. Через время задержки, достаточное для считывания информации

из узла 68 памяти, сигнал Пуск появляется на выхо;;о элемента задержки и поступает чорез элешчп- ИЛИ 89

81

на вход считывания узла 71 памяти и на управляющий вход регистра 73. По этому сигналу из узла 71 памяти осуществляется считывание кода номера ветви, являющейся первой в списке ветвей, выходящих из начального узла моделирования сети. Код номера этой ветви с выхода узла 71 памяти через узел 86 элементов ИЛИ поступает на информационный вход регистра 72 выходящей ветви и записывается в него по первому импульсу ГИ, поступающему на управляющий вход регистра 72 с выхода элемента И 93, Кроме этого, по заданному сигналу Пуск., который поступил на управляющий вход регистра 73, в него записывается код номера начального узла ветви. С выхода регистра 73 код номера начального узла ветви поступает на выходной полюс 41.

Записанный код первой выходящей ветви с выхода регистра 72 поступает на адресный вход узла 70 памяти, а также через полюс 35 на адресный вход узла 5 памяти длительности ветвей, на информационный вход узла 6 памяти номеров моделируемых ветвей и на вход схемы сравнения 13 блока 1 управления

Затем импульс ГИ2, сдвинутый относительно импульса ГИ1, с выхода элемента И 94 поступает на вход считывания узла 70 памяти, а по адресу первой выходящей ветви считывается номер второй ветви, выходящей из рассматриваемого узла. Кроме того,, импульс ГИ2 с выхода элемента И 94 поступает на полюс 36 и на вход элемента задержки 85..С выхода элемента задержки 85 сигнал, задержанный на время, достаточное для считывания информации из узла 70 памяти, через элемент ИЛИ 90 поступает на вход считывания узла 69 памяти номеров конечных узлов ветвей сети. На адресный вход узла 69 памяти, с выхода узла 88 элементов ИЛИ в это время поступает код номера ветви, счйтанньй с узла 70 памяти. Из узла 69 памяти осуществляется считывание кода номера кбнечного узла второй подготавливаемой ветви. Этот код с выхода узла 60 памяти поступает на информационный вход регистра 74 и записывается в него по приходу на управляющий вход следующего импульса ГИ1 с выхода элемента И 93.

В блоке 1 управления сигнал поиска свободной модели ветви с полюса 36

5

0

5

поступает на вход считывания узла 5 памяти длительности ветвей, на вход элементов И 21 и 22 и через элемент ИЛИ 27 на вход узла 16 элементов И. На другой вход этого узла поступает код с выхода регистра 9 номера отработавшей модели ветви. Так как в рассматриваемый момент регистр 9 обнулен, то на выходе узла 16 элементов И будет сформирован нулевой код, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. Так как на входе дешифратора 121 присутствует нулевой код, то ни на одном из выходов дешифратора сигнал считывания не сформируется и обращения к узлам 113(1), 113(2),...,ПЗ(К) памяти меток моделируемых ветвей и узлам 114(1), 114(2),,..,114(К) памяти меток узлов не будет. Поэтому на выходах узлов 114(1), 114(2),...,114(К) памяти бу- бет присутствовать нулевой потенциал, что даст потенциал низкого уровня на полюсе 43. Этот потенциал через элемент НЕ 29 поступает на вход элемента И 21, на другой вход которого поступает сигнал поиска свободной модели ветви с полюса 36. На выходе элемента И 21 сформируется сигнал высокого уровня, который через элемент ИЛИ 24 поступает на вход элемента задержки 30 и на полюс 54. Кроме того, по сигналу полюса 36, поступающему на вход считывания узла 5 памяти, осуществляется считывание длительности подготавливаемой ветви. Код длительности ветви с выхода узла 5 памяти через полюс 49 поступает в блок 3 моделей ветвей.

В блоке 3 моделей ветвей сигнал с полюса 54 поступает на входы элементов И 104(1) и 105(1) первой модели 5 ветви 97(1). Так как в рассматриваемый момент все модели свободные, то триггер 100(1) первой модели ветви 97(1) будет находиться в нулевом состоянии, и сигнал с выхода элемента И 105(1) через элемент задержки 112(1) поступит на единичный вход триггера 100(1), устанавливая его в единичное состояние. Это означает занятость процессом моделирования длительности загружаемой ветви первой моделью ветви. Одновременно сигнал с выхода элемента И 105 (1) поступает на вход узла 109(1) элементов И, на другой вход полюса 49 постзгпает код длительнос0

5

0

0

5

У1564643

ти подготавливаемой ветви. С выхода узла 109(1) элементов И код длительности ветви поступает на информационный вход формирователя 99 (1) вре5

10

менного интервала и заносится в него в качестве исходной информации. Кроме этого, сигнал с выхода элемента И 105(1) первой модели ветви через элемент ИЛИ 110(1) поступает на вход шифратора 1 1 7 адреса узла 98 поиска моделей ветвей. Шифратор 117 адреса сформирует код номера модели ветви (в данном случае первой), которая будет мо10

ления, на выходе элемента задержки 31 сформируется сигнал первого импульса серии ГИЗ, который через эле мент ИЛИ 27 поступает на вход узла lb элементов И, на другой вход кото рого поступает код с выхода регистр 97. Так как регистр 9 в настоящий момент находится в нулевом состояни то на выходе узла 16 элементов И сф мируется нулевой код, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 м делей ветвей. Так как на вход дешиф

делировать длительность первой выходя-, s ратора 121 поступил нулевой код, то

щей из узла ветви. С выхода дешифратора 117 код номера модели ветви через полюс 45 поступает в блок 1 управления.

В блоке 1 управления код номера модели ветви с полюса 45 поступает на информационный вход регистров 9 и 10 и на адресный вход узла памяти номеров моделируемых ветвей 6. На вход записи узла 6 памяти поступает сигнал с выхода элемент- ИЛИ 24, задержанный элементом 30 задержки на время поиска свободной модели ветви в блоке 3 моделей ветвей. По этому сигналу в узле 6 памяти производится запись кода номера ветви, поступающего на информационный вход с полюса 35, по адресу номера модели ветви, в формирователь временного интервала которой уже внесена длительность ветви. Кроме этого, сигнал с выхода элемента задержки 30 поступает на установочный вход регистра 10 и записывает в него код номера модели ветви, а также на единичный вход триггера 12, устанавливая его в единичное состояние. Единичное состояние триггера 12 разрешает прохождение импульсов серии ГИЗ (с третьего выхода блока 4 через полюса 61) через элемент И 19 и элемент ИЛИ 26 на счетный 8 формирования адреса меток моделируемых ветвей и на вход элемента задержки 31.

Первый импульс серии ГИЗ установит на выходе узла 8 код 1, который через узел элементов ИЛИ 23 и полюс 52 поступает на адресный вход узлов ПЗ(1),ПЗ(2),...,113(К) памяти меток моделируемых ветвей и узлов 114(1), 114(2),...,1I4(К) памяти меток узлов

20

25

30

35

40

45

50

всех моделей ветвей 97(1), 97(2),-...,

55

ни на одном из выходов дешифратора сигнал не сформируется. Выходы дешиф ратора 121 подключены i входам счит вания узлов 1 13(1), ,113(2),...,113( памяти меток моделируемых ветвей и узлов 1U(1), 1 14(2), . .., 1 14(К) памяти меток узлов моделей ветвей 97( 97(2),„..,97(К), поэтому ни на одном из выходов указанных узлов памяти сигнал не сформируется. Потенциал ни кого уровня метки моделирования узла с выходов узлов памяти 114(1), 114(2 . ,.,П4(К) через полюс 43 поступает на вход элемента ИЛИ 28 блока 1 управления .

По истечении времени, достаточного для организации описанных процессов в блоке 3 моделей ветвей, на выходе элемента задержки 32 блока 1 уп равления сформируется сигнал задержанного импульса серии ГИЗ, который поступает на вход узла 15 элементов P На другой вход этого узла поступает код с выхода регистра 10, где записа номер найденной свободной модели вет ви (в рассматриваемом случае первой) С выхода узла 15 элементов И код номера модели ветви через полюс 50 поступает на вход дешифратора 120 записи меток блока 3 моделей ветвей. На первом выхода дешифратора, который соответствует номеру модели ветви, сформируется сигнал высокого уровня, поступающий на вход записи узлов 113(1) памяти меток моделируемых ветвей и меток узлов 114(1), а также на вход элемента И 108(1) первой модели ветви 97(1), По этому сигналу в узел 13(1) памяти меток моделируемых ветвей записывается информация, поступающая с входного полюса 55, а в узел 114(1) памяти меток учпст - информация с полюса . Кач.(ыи ИМПУЛЬС, сфор мированный пл РЫЧОЧО 1леменгл II 108

97(К) блока 3 моделей ветвей. Через время, достаточное для формирования кода на выходе узла 8 блокг управ10

ления, на выходе элемента задержки 31 сформируется сигнал первого импульса серии ГИЗ, который через элемент ИЛИ 27 поступает на вход узла lb элементов И, на другой вход которого поступает код с выхода регистра 97. Так как регистр 9 в настоящий момент находится в нулевом состоянии, то на выходе узла 16 элементов И сформируется нулевой код, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. Так как на вход дешиф, s ратора 121 поступил нулевой код, то

20

25

30

5

0

5

0

5

ни на одном из выходов дешифратора сигнал не сформируется. Выходы дешифратора 121 подключены i входам считывания узлов 1 13(1), ,113(2),...,113(К) памяти меток моделируемых ветвей и узлов 1U(1), 1 14(2), . .., 1 14(К) памяти меток узлов моделей ветвей 97(1) 97(2),„..,97(К), поэтому ни на одном из выходов указанных узлов памяти сигнал не сформируется. Потенциал низкого уровня метки моделирования узла с выходов узлов памяти 114(1), 114(2) . ,.,П4(К) через полюс 43 поступает на вход элемента ИЛИ 28 блока 1 управления .

По истечении времени, достаточного для организации описанных процессов в блоке 3 моделей ветвей, на выходе элемента задержки 32 блока 1 управления сформируется сигнал задержанного импульса серии ГИЗ, который поступает на вход узла 15 элементов Pi. На другой вход этого узла поступает код с выхода регистра 10, где записан номер найденной свободной модели ветви (в рассматриваемом случае первой). С выхода узла 15 элементов И код номера модели ветви через полюс 50 поступает на вход дешифратора 120 записи меток блока 3 моделей ветвей. На первом выхода дешифратора, который соответствует номеру модели ветви, сформируется сигнал высокого уровня, поступающий на вход записи узлов 113(1) памяти меток моделируемых ветвей и меток узлов 114(1), а также на вход элемента И 108(1) первой модели ветви 97(1), По этому сигналу в узел 13(1) памяти меток моделируемых ветвей записывается информация, поступающая с входного полюса 55, а в узел 114(1) памяти меток учпст - информация с полюса . Кач.(ыи ИМПУЛЬС, сформированный пл РЫЧОЧО 1леменгл II 108

11156

по сигналу с полюса 56, уменьшает.на 1 код счетчика узлов 115(1).

В блоке 1 управления полюс 55 связан с выходом элемента ИЛИ 25. Первый вход элемента ИЛИ 25 связан с по- пюсом 44 выхода метки моделирования ветви, и в рассматриваемый момент на нем присутствует потенциал низкого уровня . (в регистре 9 записан нулевой код). На второй вход элемента ИЛИ 25 Поступает сигнал: с выхода узла 13 сравнения номеров ветвей. Входы узла 13 сравнения связаны соответственно с выходом узла 8 формирования адреса меток моделирования и с полюсом 35. Таким образом, на выходе узла 13 сравнения сформируется сигнал в том слу- чае, когда адрес записи меток моделирования будет соответствовать номеру Подготавливаемой ветви В рассматриваемом случае на выходе узла 13 сравнения будет сформирован сигнал в том Случае, если к моделированию подготавливается ветвь с номером 1. При этом будет произведена запись единичной .метки в узел 113(1) памяти первой модели ветви 97(1) блока 3 моделей ветвей по первому адресу.

Полюс 56 связан с выходом элемента ИЛИ 28 блока 1 управления„ Первый Вход элемента ИЛИ 28 связан с полюсом 43 выхода метки моделирования узла, где в рассматриваемый момент присутствует потенциал низкого уровня (в регистре 9 записан нулевой код, поэтому нет обращения ни к одной модели ветви). На второй вход элемента ИЛИ 28 поступает сигнал с выхода схемы 14 сравнения номеров узлов. Входы схемы 14 сравнения подключены соответственно к выходу узла 8 формирования адреса меток моделирования и к полюсу 41 номера начального узла подготавливаемой к моделированию ветви. Таким образом, на выходе узла 14 сравнения сформируется сигнал при условии, что адрес записи меток моделирования будет соответствовать номеру начального узла подготавливаемой к моделированию ветви В рассматривав-- мом моменте сигнал на выходе узла 15 сравнения будет сформирован в том случае, если к моделированию подготавливается ветвь, у которой номер начального узла равняется 1 При этом единичная метка будет записана в узел 114(1) памяти первой модели ветви 97(1) блока 3 моделей ветвей

0

5

0

5

643

30

35

40

45

50

55

12

по первому адресу, а код счетчика узлов сети 115(1) этой модели ветви уменьшится на ,

Следующий импульс серии ГИЗ, который поступит с полюса 61 через элемент И 19 на счетньй вход узла 8 формирования адреса меток моделируемых ветвей, установит на выходе узла код 2. Этот код через узел 23 элементов ИЛИ и полюс 52 поступает на адресный вход узлов 113(1), 113(2),...,113(К) памяти меток моделируемых ветвей и узлов 114(1), 1 14(2), .. ,, П4(К)памяти меток узлов блока 3 моделей ветвей. Через время, достаточное для формирования кода на выходе узла 8 блока i управления, на выходе элемента задержки 31 сформируется сигнал второго импульса серии ГИЗ, который через элемент ИЛИ 27 поступает на вход узла 16 элементов И, на другой вход которого поступает код с выхода регистра 97„ Так как регистр 9 в настоящий момент находится в нулевом состоянии, то на выходе узла 16 эле ментов И сформируется нулевой код, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. Так как на вход дешифратора 121 поступил нулевой код, то ни на одном из выходов дешифратора сигнал не сформируется. Выходы дешифратора 121 подключены к входам считывания узлов 113(1), 113(2) ,..,113(К) памяти меток моделируемых ветвей и узлов 114(lJ, 114(2),..,, 114(К) памяти меток узлов, поэтому потенциал низкого уровня метки моделирования узла с выхода узлов 114(1), 114(2),...,114(К) через полюс 43 поступает на вход элемента ИЛИ 28 блока 1 управления, а потенциал низкого уровня метки моделирования ветви с выхода узлов 113(1), 113(2), ..., ПЗ(К) памяти блока моделей ветвей через полюс 44 поступает на вход элемента ИЛИ 25.блока 1 управления.

По истечении времени, достаточного для организации описанных процессов в блоке 3 моделей ветвей, на выходе элемента задержки 32 блока 1 управления сформируется сигнал задержанного второго импульса серии ГИЗ, который поступает на зход узла 15 элементов И„ На другой вход этого узла поступает код с выхода регистра 10, где записан номер найденной свободной модели ветви. С выхода узла 15 элементов И код номера модели ветви через полюс 50 поступает на вход дешифратора 120 записи меток блока 3 моделей ветвей. Па первом его выходе, который соответствует номеру свободной модели ветви, сформируется сигнал, поступающий на вход записи узла 113(1) памяти меток моделируемых ветвей и меток узлов 114(1) первой модели ветви 97(1). По этому сигналу в узел 113(1) памяти меток моделируемых ветвей по второму адресу запишется единичная метка в случае, если к моделированию подготавливается ветвь с номером 2, а в узел 14(1) памяти меток узлов по второму адресу запишется единичная метка в случае, если к моделированию подготавливается ветвь, у которой номер начального узла 2.

Следующий импульс серии ГИЗ увеличит на 1 код узла 8 формирования адреса меток моделируемых ветвей блока 1 управления и процесс записи

10

15

20

дяцей из начального узла моделирования сети. Как отмечено, импульс серии Г112 .с выхода элемента И 94 блока 2 формирования топологии поступает на вход считывания узла 17 памяти номеров выходягих ветвей. На адресный вход узла /0 памяти в этот момент поступает код номера первой ветви, выходящей из того яе узла. Код номера этой ветви с выхода узла 70 памяти через узел 86 элементов ИЛИ поступает на информационный вход регистра 72 выходяшей ветви и- записывается в него по второму импульсу ГИ1, поступающему на управляющий вход регистра с выхода элемента И 93. С выхода регистра 72 код второй выходящей ветви через полюс 35 поступает в блок 1 управления.

Кроме этого, код второй ветви, выходящей из начального узла моделирования, считанный из узла 70 памяти блока 2 формирования топологии через

метки моделирования ветвей и метки уз-25Узлы 86 и 88 элементов ИЛИ поступает

лов повторяется для нового адреса.на адресньй вход узла 69 памяти номеТак осуществляется запись единичнойров конечных узлов ветвей сети. На

метки в узел 113(1) памяти меток мо-вход считьюания узла 69 памяти через

делируемых ветвеД первой модели ветви 97(1) по адресу номера приготавливав- мой к моделированию ветви и запись нулевой метки по всем остальным адресам, а также запись единичной метки в узел 114(1) памяти узлов первой модели ветви 97(1) по адресу номера начального узла подготавливаемой к мо- делированию- ветви, а запись нулевой метки - по всем остальным адресам.Описанный процесс поступления импуль

сов серии ГИЗ и запись меток моделирования ветвей и узлов будут продолжаться до тех пор, пока на выходе переполнения узла 8 формирования адресов моделированных ветвей блока 1 управления не сформируется сигнал высокого уровня, что соответствует .перебору всех возможных номеров ветвей и узлов сети. Сигнал с выхода переполнения узла 8 поступает на нулевой вход триггера 12 и устанавливает его в нулевое состояние. Нулевое состояние триггера 12 запрещает прохождение импульсов серии ГИЗ через элемент И 19. Кроме этого, сигнал переполнения с выхода узла 8 поступает на вход сброса этого узла, устанавливая его в нулевое состояние.

Рассмотрим процесс подготовки к моделированию следующей ветви иыхо-

0

5

0

дяцей из начального узла моделирования сети. Как отмечено, импульс серии Г112 .с выхода элемента И 94 блока 2 формирования топологии поступает на вход считывания узла 17 памяти номеров выходягих ветвей. На адресный вход узла /0 памяти в этот момент поступает код номера первой ветви, выходящей из того яе узла. Код номера этой ветви с выхода узла 70 памяти через узел 86 элементов ИЛИ поступает на информационный вход регистра 72 выходяшей ветви и- записывается в него по второму импульсу ГИ1, поступающему на управляющий вход регистра с выхода элемента И 93. С выхода регистра 72 код второй выходящей ветви через полюс 35 поступает в блок 1 управления.

Кроме этого, код второй ветви, выходящей из начального узла моделирования, считанный из узла 70 памяти блока 2 формирования топологии через

эп 35 „

0

5

0

5

элемент ИЛИ 90 поступает сигнал первого импульса серии ГИ2 с выхода элемента И 94, задержанный элементом задержки 85, Из узла 69 памяти считывается код номера конечного узла второй выходящей ветви. Этот код поступает на информационный вход регистра 74 и записывается в него по второму импульсу серии ГИ1, поступающему на установочный вход регистра с выхода элемента И 93. С выхода регистра 74 код номера конечного узла второй ветви, выходящей из начального узла моделирования, через полюс 34 поступает в блок 1 управления. Кроме этого, в блок 1 управления с выхода элемента И 94 через полюс 36 поступает второй импульс серии ГИ2.

В блоке 1 управления сигнал поиска свободной модели ветви с полюса 36 поступает на вход считывания узла 5 памяти длительности ветвей, на адресный вход которого с полиса 35 по- , ступает код номера втором выходящей ветви. Считанный код длительности этой ветви через полюс 49 поступает в блок 3 моделей ветвей. Кроме этого, сигнал поиска свободной .модели ветви с полюса 36 через элемент ИЛИ 27 поступает на вход узла 16 чломен- - тов И, на второй вход которо посту

10

пает код с выхода регистра У/. В рассматриваемый момент в регистре 9 хранится нулевой код, поэтому, как отмечалось, считывания информации из узлов памяти меток узла 114 блока моделей ветвей не производится, а на полюсе 43 присутствует нулевой потенциал. Этот потенциал через элемент НЕ 29 блока 1 управления поступает на вход элемента И 21, разрешая прохождение сигнала поиска свободной модели ветви с полюса 36 через элемент ИЛИ 24 на выходной полюс 54 и далее в блок 5 моделей ветвей. (5

В блоке 3 моделей ветвей сигнал поиска свободной модели ветви с полюса 54 поступает на входы элементов И 104(1) и 105(1) первой модели ветви 97(1). Так как триггер 100(1) пер- 20 вой модели ветви находится в единичном состоянии, означающем занятость первой модели ветви, то сигнал с выхода элемента 104(1) поступает на по156464J)6

этой модели ветви в регистре 10. Кроме этого, сигнал с выхода элемента задержки 30 блока 1 управления поступает на единичный вход триггера 12, устанавливая его в единичное состояние. Единичное состояние триггера 12 разрешает прохождение импульсов серии ГИЗ через элемент И 19 для формирования меток моделируемых ветвей и меток узлов. При этом каждый

импульс ГИЗ увеличивает на Г код узла 8 формирования адреса меток моделирования. Код с выхода узла 8 через узел элементов ИЛИ 22 и полюс 52 поступает на адресный вход узлов памяти 113(1), ПЗ(2),...,ПЗ(К) и 114(1), 1 14(2), ...,П4(К) все, моделей ветвей 97(1), 97(2),...,97(К) блока 3 моделей ветвей. Далее каждый импульс ГИЗ(задержанный элементом задержки 31 блока 1 управления,через элемент ИЛИ 27 поступает на вход узла 16 элементов И, формируя на вылюс 54(2) второй модели ветви 97(2). 25 ходе узла нулевой код, который через Триггер 100(2) этой модели ветви на- полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. Нулевой код определяет отсутствие сигнала считывания на 30 всех узлах 113(1), 113(2),...,113(К) памяти меток моделируемых ветвей и узлах 114(U, 114(2), ...,П4(К) памяти меток узлов. Отсутствие сигнала считывания определит нулевой потенциал на полюсах 43 и 44 блока 3 модехОдится в нулевом состоянии, поэтому на выходе элемента И 105(2) сформируется сигнал высокого уровня. Этот сигнал поступает на вход узла 109(2) элементов И, и в формирователь 99(2) временных интервалов записывается код длительности второй ветви, выходящей из начального узла моделирования„Кроме этого, сигнал с выхода элементов 105(1) через элемент задержки 112(2) поступает на единичньй вход триггера 100(2), устанавливая его в единичное состояние. По этому же сигналу шифратором 117 адреса узла 98 поиска моделей ветвей формируется код номера второй модели ветви, которьй с выхода шифратора через полюс 45 поступает в блок управления.

35

40

лей ветвей. Кроме этого, каждый импульс ГИЗ, задержанньй элементами задержки 31 и 32 блока 1 управления, / поступает на вход узла 15 элементов И, формируя на выходе узла код номера той модели ветви, куда была записана длительность подготавливаемой к моделированию ветви (в рассматриваемом случае код 2)„ Этот код через поВ блоке 1 управления код номера 45 пюс- 50 поступает на дешифратор 120 записи меток блока 3 моделей ветвей. Н втором выходе дешифратора 120, которьй соответствует номеру модели ветмодели ветви с полюса ч.) поступает на адресный вход узла 6 памяти номеров моделируемых ветвей, на информационные входы регистров 9 и 10 номеров отработавшей модели ветви и номера е;о свободной модели . На вход записи узла 6 памяти и установочный вход регистра 10 поступает задержанный сигнал поиска свободной модели ветви с выхода элемента задержки 30.Про- 55 вой или единично метки в узлы памк- изводится запись кода номера второй - ти 113(2) и 114(2) по адресу, кото- исходящей ветви в узел 6 памяти по t РЬ1Й определяется кодом узла 8 форми- адресу номера найденной свободной мо- рования меток моделирования блока 1 дели ветви и установка кода номера управления. Единичная метка моделиви, сформируется сигнал, поступающий на входы записи узла 113(2) памяти меток модулируемых ветвей и узла 14 (2) памяти меток узлов, а так же на вход элемента И 108 второй модели ветви. Происходит запись нулеимпульс ГИЗ увеличивает на Г код узла 8 формирования адреса меток моделирования. Код с выхода узла 8 через узел элементов ИЛИ 22 и полюс 52 поступает на адресный вход узлов памяти 113(1), ПЗ(2),...,ПЗ(К) и 114(1), 1 14(2), ...,П4(К) все, моделей ветвей 97(1), 97(2),...,97(К) блока 3 моделей ветвей. Далее каждый импульс ГИЗ(задержанный элементом задержки 31 блока 1 управления,через элемент ИЛИ 27 поступает на вход узла 16 элементов И, формируя на выходе узла нулевой код, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. Нулевой код определяет отсутствие сигнала считывания на 0 всех узлах 113(1), 113(2),...,113(К) памяти меток моделируемых ветвей и узлах 114(U, 114(2), ...,П4(К) памяти меток узлов. Отсутствие сигнала считывания определит нулевой потенциал на полюсах 43 и 44 блока 3 моде5

0

лей ветвей. Кроме этого, каждый импульс ГИЗ, задержанньй элементами задержки 31 и 32 блока 1 управления, / поступает на вход узла 15 элементов И, формируя на выходе узла код номера той модели ветви, куда была записана длительность подготавливаемой к моделированию ветви (в рассматриваемом случае код 2)„ Этот код через пописи меток блока 3 моделей ветвей. На втором выходе дешифратора 120, которьй соответствует номеру модели ветвой или единично метки в узлы памк- ти 113(2) и 114(2) по адресу, кото- РЬ1Й определяется кодом узла 8 форми- рования меток моделирования блока 1 управления. Единичная метка моделивой или единично метки в узлы памк- ти 113(2) и 114(2) по адресу, кото- РЬ1Й определяется кодом узла 8 форми- рования меток моделирования блока 1 управления. Единичная метка моделиви, сформируется сигнал, поступающий на входы записи узла 113(2) памяти меток модулируемых ветвей и узла 14 (2) памяти меток узлов, а также на вход элемента И 108 второй модели ветви. Происходит запись нуле

руемых ветвей в узел 113(2) памяти блока 3 моделей ветвей записывается в том случае, когда на выходе узла сравнения 3 блока 1 управления сформируется сигнал высокого уровня. Это произойдет в том случае, когда код узла 8 формирования адреса меток моделирования совпадает с кодом номера подготавливаемой ветви, т.е. в рассматриваемом случае единичная метка записывается в узел 113(2) памяти второй модели ветви 97(2) блока 3 моделей ветвей по адресу номера данной ветви о Единичная метка узлов в узел 114(2) памяти блока 3 моделей ветвей записывается в том случае, когда на выходе узла сравнения 14 блока 1 управления сформируется сигнал высокого уровня. А это произойдет в том случае, когда код узла 8 формирования адреса моделирования совпадет с кодом номера начального узла подготавливаемой ветви, т.е. в рассматриваемом случае единичная мет- ка записывается в узел памяти второй модели ветви 97 (2) блока 3 моделей ветвей по адресу номера начального узла второй ветви. Код счетчика узлов 115(2 сети второй модели ветви 97(2) уменьшается на 1.

Процесс формирования меток моделируемых ветвей и меток узлов продолжается до того момента, когда после поступления очередного импульса ГИЗ на выходе переполнения узла 8 блока 1 -управления не сформируется сигнал высокого уровня о Указанный сигнал поступает на нулевой вход триггера 12, устанавливая его в нулевое со- стояние. Этим запрещается прохождение импульсов ГИЗ через элемент И 19. Процесс подготовки к моделированию вто-

дов выработается сигнал конца списка выходящих из узла ветвей. Этот сигн«э с выхода дешифратора 78 поступает на нулевой вход триггера 7, устанавливая его в нулевое состояние. Нулевое состояние триггера запрещает прохождение импульсов ГИ1 и ГИ2 через соответственно элементы И 93 и 94. Кроме этого, сигнал с выхода дешифратора 78 поступает на полюс 38„ С полюса 38 сигнал поиска прерывания поступает на единичный вход триггера 11 блока 1 управления, устанавливая его в единичное состояние, а также через полюс 39 на вход элемента ИЛИ 118 узла 98 поиска моделей ветвей блока 3 моделей ветвей, а также на вход формирователей сброса 116(1), 1 1 6(2), ,..,116(К) всех моделей ветвей. С выхода элемента ИЛИ 118 сигнал поиска прерывания поступает на входы элементов И 102(1) и 103(1) первой модели ветви 97(1). Так как в рассматриваемый момент подготовлены к моделированию ветви, выходящие из начального узла моделирования сети, и моделей ветвей, закончивших процесс моделирования, нет, то триггер прерыва ния 101(1) первой модели ветви 97(1) будет находитьсяв нулевом состоянии Разрешающий потенциал с нулевого выхода триггера 101(1) поступает на вход элемента И 102(1), и на выходе элемента сформируется сигнал поиска прерывания, который через полюс (2,1} поступает на входы элементов И 102(2) и 103(2) второй модели ветви 97(2). Так как триггер прерывания 101(1) вто рой модели ветви 97(2) также находится в нулевом состоянии, то сигнал поиска прерывания, сформированный на выходе элемента 102(2), через полюс (3,1) поступит на входы элементов

рой ветви, выходящей из начального

узла моделирования сети, на этом окан- з И 102(3) и 103(3) третьей модели ветви 97(3) и т.д. до К. Так как в рассматриваемый момент нет триггеров прерывания 101(1), 101(2),...,101(К), находящихся в единичном состоянии, то на выходе ни одного из элементов 103(1), 103(2),103(К) сигнал прерывания не сформируется. Поэтому на выходе элемента ИЛИ 119 узла 98 поисчивается.

Так осуществляется подготовка ветвей, выходящих из начального узла моделирования сети, к процессу временного моделирования их длительности до тех пор,пока не будет подготовлена последняя ветвь из списка выходящих ветвей„ После этого по адресу ее номера в узле 70 памяти номеров выходящих ветвей блока 2 формирования топологии будет считан код X, который запишется в регистр 72. Выход регистра 72 подключен к дешифратору 78 состояния X, где путем сравнения ко50

55

ка моделей ветвей, входы которого соединены с выходами элементов И 103(1), 103(2),..., ЮЗ(К),будет присутствовать потенциал низкого уровня. Этот потенциал через попюс 4b поступает на нулевой вход Tpmicpi II бло5

0

5

0

5

о

0

5

дов выработается сигнал конца списка выходящих из узла ветвей. Этот сигн«эл с выхода дешифратора 78 поступает на нулевой вход триггера 7, устанавливая его в нулевое состояние. Нулевое состояние триггера запрещает прохождение импульсов ГИ1 и ГИ2 через соответственно элементы И 93 и 94. Кроме этого, сигнал с выхода дешифратора 78 поступает на полюс 38„ С полюса 38 сигнал поиска прерывания поступает на единичный вход триггера 11 блока 1 управления, устанавливая его в единичное состояние, а также через полюс 39 на вход элемента ИЛИ 118 узла 98 поиска моделей ветвей блока 3 моделей ветвей, а также на вход формирователей сброса 116(1), 1 1 6(2), ,..,116(К) всех моделей ветвей. С выхода элемента ИЛИ 118 сигнал поиска прерывания поступает на входы элементов И 102(1) и 103(1) первой модели ветви 97(1). Так как в рассматриваемый момент подготовлены к моделированию ветви, выходящие из начального узла моделирования сети, и моделей ветвей, закончивших процесс моделирования, нет, то триггер прерывания 101(1) первой модели ветви 97(1) будет находитьсяв нулевом состоянии Разрешающий потенциал с нулевого выхода триггера 101(1) поступает на вход элемента И 102(1), и на выходе элемента сформируется сигнал поиска прерывания, который через полюс (2,1} поступает на входы элементов И 102(2) и 103(2) второй модели ветви 97(2). Так как триггер прерывания 101(1) второй модели ветви 97(2) также находится в нулевом состоянии, то сигнал поиска прерывания, сформированный на выходе элемента 102(2), через полюс (3,1) поступит на входы элементов

з

50

ка моделей ветвей, входы которого соединены с выходами элементов И 103(1), 103(2),..., ЮЗ(К),будет присутствовать потенциал низкого уровня. Этот потенциал через попюс 4b поступает на нулевой вход Tpmicpi II блока 1 управления, подтверждая его единичное состояние. Единичное состояние триггера 11 разрешает прохождение импульсов серии ГИ1 через элемент И 20 на счетный вход узла 7 измерения пути и на полюс 53 С полюса 53 импульсы измерительной серии поступают на вход элементов И 106(1), 106(2),

. ,.,Ю6(К) всех моделей ветвей 97(1), 1Q равления„ Креме этого, сигнал пре97(2),...,97(К) блока 3 моделей ветвей и проходят на входы формирователей 99 временных интервалов тех моделей ветвей 97, у которых триггер 100 занятости находится в единичном состоянии,, С приходом каждого импульса измерительной серии код формирователей временных интервалов уменьшается на 1, а узел измерения пути суммирует временное моделирование. С приходом количества импульсов измерительной серии, равного минимальному коду, записанному в какой-либо формирователь, последний обнуляется и выдает сигнал об окончании процесса временного моделирования длительности ветви.

Сигналы с выходов формирователей временных интервалов 99(1), 99(2),.,., 99(К) поступают на единичные входы триггеров 101(1), 101(2),,..,101(К), устанавливая их в единичное состояние, а также на входы элемента ИЛИ 118 узла 98 поиска моделей ветвей.

15

20

рывания, сформированный на выходе элемента И 103 блока 3 моделей ветвей, через элемент ИЛИ 130 поступае на вход шифратора адреса 317 узла 9 поиска моделей ветвей„ С выхода шиф ратора 117 код номера модели ветви, выставившей прерывание, через полюс 45 поступает в блок 1 управления. К ме этого, сигнал, сформированный на выходе элемента И 103 блока 3 моделей ветвей, поступает на вход форми рователя 116 сброса модели ветви, у танавливая его триггер в единичное состояние, а также через элемент за 25 держки 1I1 поступает на нулевой вхо триггера прерывания 101, устанавливая его в нулевое состояние.

В блоке 1 управления сигнал прерывания с входного полюса 46 поступает на вход считывания узла 6 памя ти номеров моделируемых ветвей и на установочный вход регистра 9 номера отработавшей модели ветви. На адрес ный вход узла 6 памяти и на информа

30

С выхода элемента ИЛИ 118 сигнал поис-35 ционный вход реги-стра 9 с полюса 45

ка прерывания через полюс (1,1) поступает на входы элементов И 102(1) и 103(1) первой модели ветви 97 (1). Если триггер прерывания 101(1) первой модели ветви 97(1) установлен в единичное состояние, на выходе элемента 103(1) сформируется сигнал прерыванияs который через полюс (1,2) поступает на вход элемента ИЛИ 119 узла 98 поиска моделей ветвей. В противном случае сигнал поиска прерывания сформируется на выходе элемента И 102(1) первой модели ветви 97(1). Этот сигнал через полюс (2,1),поступает на входы элементов И 102(2) и 103(2) второй модели ветви 97(2). Если триггер 101(2) второй модели ветви 97(2) также находится в нулевом состоянии, сигнал поиска прерывания, сформированный на выходе элемента 102(2), через полюс (3,1) поступает на входы элементов И 102(3) и 103(3) третьей мо- , дели ветви 97(3) и т.д., пока не обнаружится модель ветви, в которой

40

45

50

55

поступает код номера модели ветви, выставившей прерывание. Осуществляе ся запись кода номера отработавшей модели ветви в регистр 9 и считывание информации из ячейки памяти узла 6 памяти по адресу номера модели ветви, т.е. считывание кода номера ветви, моделирование длительности которой закончено. Код.номера ветви с выхода узла 6 памяти поступает на полюс 47. Кроме этого, сигнал прерывания с полюса 46 поступает на нулевой вход триггера 11, устанавливая его в нулевое состояние, а та же на вход элемента задержки 33. Че рез время, достаточное для считывания кода номера ветви из узла 6 памяти, на выходе элемента задержки 3 сформируется сигнал начала анализа свершения ветви, который через полюс 48 поступает в блок 2 формирования топологии.

В блоке 2 формирования топологии сигнал начала анализа свершения вет

триггер прерывания 101 установлен в единичное состояние. Сигнал прерывания, сформированный на выходе элемента И 103 этой модели ветви, поступает на вход элемента ИЛИ 119 узла 98 поиска моделей ветвей. С выхода элемента ИЛИ 119 сигнал прерывания через полюс 46 поступает в блок 1 управления„ Креме этого, сигнал пре5

0

рывания, сформированный на выходе элемента И 103 блока 3 моделей ветвей, через элемент ИЛИ 130 поступает на вход шифратора адреса 317 узла 98 поиска моделей ветвей„ С выхода шифратора 117 код номера модели ветви, выставившей прерывание, через полюс 45 поступает в блок 1 управления. Кроме этого, сигнал, сформированный на выходе элемента И 103 блока 3 моделей ветвей, поступает на вход формирователя 116 сброса модели ветви, устанавливая его триггер в единичное состояние, а также через элемент за- 5 держки 1I1 поступает на нулевой вход триггера прерывания 101, устанавливая его в нулевое состояние.

В блоке 1 управления сигнал прерывания с входного полюса 46 поступает на вход считывания узла 6 памяти номеров моделируемых ветвей и на установочный вход регистра 9 номера отработавшей модели ветви. На адресный вход узла 6 памяти и на информа0

ционный вход реги-стра 9 с полюса 45

поступает код номера модели ветви, выставившей прерывание. Осуществляется запись кода номера отработавшей модели ветви в регистр 9 и считывание информации из ячейки памяти узла 6 памяти по адресу номера модели ветви, т.е. считывание кода номера ветви, моделирование длительности которой закончено. Код.номера ветви с выхода узла 6 памяти поступает на полюс 47. Кроме этого, сигнал прерывания с полюса 46 поступает на нулевой вход триггера 11, устанавливая его в нулевое состояние, а также на вход элемента задержки 33. Через время, достаточное для считывания кода номера ветви из узла 6 памяти, на выходе элемента задержки 33 сформируется сигнал начала анализа свершения ветви, который через полюс 48 поступает в блок 2 формирования топологии.

В блоке 2 формирования топологии сигнал начала анализа свершения ветви

с полюса 48 поступает на вход элемента задержки 83 и через элемент ИЛИ 90 на вход считывания узла 69 памяти номеров конечных узлов ветвей сети, на адресный вход которого с полюса 47 через элемент ИЛИ 88 поступает код номера ветви, моделирование длительности которой окончено. Происходит считывание информации из ячейки узла 69 памяти, где записан номер конечного узла рассматриваемой ветви. С выхода узла 69 памяти код номера конечного узла ветви поступает на информационные входы регистра 74 конечного узла подготавливаемой ветви и регистра 75 анализируемой ветви. Через время, достаточное для считывания информации из узла 69 памяти, на выходе элемента задержки 83 сформируется сигнал высокого уровня, который поступает на вход элемента задержки 84 и на установочный вход регистра 75, Происходит запись кода номера конечного узла обрабатываемой ветви в регистр 75. С выхода регистра 75 код номера конечного узла ветви через узел 87 элементов. ИЛИ поступает на адресный вход узла 7J памяти номеров первой выходящей ветви, Через вре мя, достаточное для записи номера конечного узла ветви в регистр 75, на выходе элемента задержки 84 сформируется сигнал высокого уровня, который поступает на вход элемента И 92, На другой вход этого элемента в случае, если-код конечного узла обрабатываемой ветви не равняется коду номера уз ла сети, принятого за начальный узел

моделирования сети (процесс моделкро

вания находится не в конечной точке и на выходе узла 80 сравнения кодов присутствует нулевой потенциал), поступает разрешающий потенциал с выхода элемента НЕ 96.

На выходе элемента И 92 сформируется сигнал, который через элемент ИЛИ 89 поступает на вход считывания узла 71 памяти и установочный вход регистра 73, а через элемент ИЛИ 91 - на единичный вход триггера 77. Триггер 77 устанавливается в единичное состояние, разрешая, прохождение импульсов ГИ1 и ГИ2 соответственно через элементы И 93 и 94. На этом закан чивается этап обработки прерывания от модели ветви, которая закончила процесс моделирования длительности ветви, и начинается этап подготовки к мо

10

46

5 25 ,„

20

35

0

с

0

делированию ветвей, выходящих и: конечного узла обрабатываемой летни,

Сигнал, который поступает на вход считывания узла 71 памяти, осуществляет считывание ячейки памяти по адресу, который поступает на адресный вход с выхода регистра 75 конечного узла анализируемой ветви через элемент ИЛИ 87, т.е. считывается первая в списке ветвь, выходящая из конечного узла ветви, моделирование длительности которой окончено. Код номера считанной ветв-и с выхода узла 71 памяти через узел 86 элементов ИЛИ поступает на информационный вход регистра 72 выходящей ветви и записывается в него по первому импульсу ГИ, поступающему на управляющий вход регистра с выхода элемента И 93. Кроме этого,код номера первой выходящей ветви с выхода узла 71 памяти блока 2 формирования топологии через узлы 86 и 88 элементов ИЛИ поступает на адресный вход узла 69 памяти номеров конечных узлов ветвей сети. На вход считывания указанного узла через элемент ИЛИ 90 поступает сигнал с элемента задержки 82, задержанный на время, достаточное для считывания информации из узла 71 памяти. По этому сигналу из узла 69 памяти осуществляется считывание кода номера конечного узла первой выходящей ветви. Этот код с выхода узла 71 памяти поступает на информационный вход регистра 74 и записывается в него по первому импульсу ГИ, поступающему на установочный вход регистра с выхода элемента И 93. С выхода регистра 74 код номера конечного узла первой выходящей ветви через полюс 34 поступает в блок 1 управления. Кроме этого, по сигналу, который поступил на установочный вход регистра 73, в него записывается код начального узла первой выходящей ветви из регистра 75. С выхода регистра 73 код номера начального узла ветви поступает на выходной полюс 41.

Записанный код первой выходящей ветви с выхода регистра 72 поступает на адресный вход узла 70 памяти, а также через выходной полюс 35 блока формирования топологии 2 - на адресный вход иузла 5 памяти длительности ветвей, па информационный нход учла 6 памяти номеров моделируемых сет- вей и на РХОД узла сравнения I t блока 1 управления.

Затем импульс ГИ2, сдвинутый относительно импульса ГИ1, с выхода элемента И 94 блока 2 формирования топологии поступает на вход считывания узла 70 памяти, и по адресу первой выходящей ветви осуществляется считывание номера второй ветви, выходящей из рассматриваемого узла.Кроме этого, сигнал ГИ2 с выхода элемента И 94 через полюс 36 поступает в блок 1 управления. В блоке 1 управления сигнал поиска свободной модели ветви с полюса 36 поступает на вход считывания узла 5 памяти длительности ветвей, на вход элементов И 21 и 22 и через элемент ИЛИ 27 на вход узла 16 элементов И. На другой вход указанного узла элементов И с регистра 9 поступает код номера модели ветви, прерывание от которой обрабатывалось последним. На выходе узла I6 элементов И сформируется код указанной модели ветви, который через полюс 51 поступает на вход дешифратора 121 считывания меток блока 3 моделей ветвей. На том выходе дешифратора, который соответствует номеру модели ветви, сформируется сигнал, Поступающий на вход считывания узлов 113 и 114 памяти указанной модели веви, а также на вход элемента И 107 На адресный вход узлов 113 и 114 через полюс 52 с узла 23 элементов ИЛИ блока I управления поступает код, сформированный на выходе,узла 18 элементов И. Первый вход узла 18 элементов И подключен к полюсу 34 и на него из блока 2 формирования топологии поступает.код конечного узла подготавливаемой к моделированию ветви, на другой вход узла 18 элементов И поступает разрешающий потенциал с нулевого выхода триггера 12. Таким образом, на выходе узла 18 элементов И а значит, и на адресном входе узлов памяти 113 и 114 блока 3 моделей ветвей будет сформирован код конечного узла подготавливаемой к моделированию ветви. Осуществляется считывание информации из узла 114 памяти меток узлов той модели ветви, которая окончила моделирование длительности ветви по адресу номера конечного узла подготавливаемой к моделированию ветви. И если считана единичная метк которая означает, что данная ветвь входит в уже пройденный узел сети, сигнал высокого уровня с выхода узла

0

5

0

5

45

30

35

40

50

55

памяти 114 через полюс 43 и элемент НЕ 29 блока 1 управления поступает на вход элемента И 21, запрещая прохождение сигнала поиска свободной модели ветви с полюса 36 через этот элемент.

В рассматриваемом случае (при единичной метке узла) сигнал поиска свободной моделей ветви может быть сформирован на выходе элемента И 22. Это произойдет при наличии разрешающих сигналов на входах элемента И 22, связанных с полюсом 37 и с полюсом 42. Разрешающий сигнал с полюса 37, который связан с выходом узла 79 сравнения кодов блока 2 формирования топологии, сформируется при совпадении кодов, записанных в регистрах 74 и 76, т.е. когда конечный узел подготавливаемой ветви равняется начальному узлу моделирования сети (путь замыкается в исходной точке). Разрешающий сигнал на полюсе 42,который связан с объединенным выходом элементов И 107 (1), 107(2),...,107(К) блока 3 моделей ветвей, будет сформирован в том случае, если счетчик 115 узлов сети модели ветви, откуда считывается метка узлов, будет обнулен, и на его выходе переполнения,, связанном с входом элемента М Q/S будь-- сформирован сигнал высокого уровня (моделируемый путь прошел через все узлы и подготавливаемая ветвь замыкает его в начальном узле моделирования сети)о

В рассмотренном примере сигнал поиска свободной модели ветви с выхода элемента И 22, а при считывании нулевой метки узла с выхода элемента И 21 через элемент ИЛИ 24 поступает на вход элемента задержки 30, а также на выходной полюс 54.

Если хотя бы на одном из полюсов 37 или 42 отсутствует разрешающий сигнал, а из узла 114 памяти меток узлов блока 3 моделей ветвей считана единичная метка, сигнал поиска свободной модели ветви не вырабатывается, длительность ветви в формирователь временного интервала модели ветви не заносится и подготовка ветви к моделированию на этом заканчивается.

Если же сигнал поиска свободной модели ветви выработался с полюса 54, он поступает на вход элементов И 104(1) и 105 (1) первой модели вет5

251564643

ви 97(1) блока 3 моделей ветвей. Если триггер 100(1) первой модели ветви 97(1) находится в единичном состоянии (модель занята), сигнал с выхода элемента И 104(1) через полюс 54(2) поступает на вход элементов И 104(2) и 105(2) второй модели ветви 97(2). Если триггер 100(2) второй модели ветви 97(2) также находится в еди- JQ ничном состоянии, сигнал с выхода элемента И 104(2) через полюс 54(3) поступает на вход элементов И 104(3) и 105(3) третьей модели ветви 97(3) и т.д. до первой свободной модели вет-

20

30

35

ви, у которой триггер 100 находится в нулевом состоянии. У этой модели ветви сигнал высокого уровня с выхода элемента И 105 поступает на вход элемента И 109 и в формирователь 99 временных интервалов данной модели ветви заносится код длительности подготавливаемой ветви, который поступает на другой вход элемента И 109 с полюса 49. Кроме этого, сигнал с выхо- 25 да элемента И 105 через элемент задержки 112 поступает ча вход ™риг- гера 100, устанавливая его в единичное состояние. Далее сигнал с выхода элемента И 105 через элемент ИЛИ 110 поступает на вход шифратора 117 адреса узла 98 поиска моделей ветвей. На выходе шифратора адреса сформируется код номера данной свободной модели ветви, который через полюс 45 поступает в блок 1 управления.

В-блоке 1 управления код номера модели ветви с полюса 45 поступает на адресный вход узла 6 памяти номеров моделируемых ветвей, на информационный вход регистров 10 и 9 номера свободной модели ветви и регистра номера отработавшей модели ветви. На информационный вход узла 6 памяти в рассматриваемый момент поступает код 45 номера подготавливаемой ветви с ползо- са 35, а на вход записи - задержанный сигнал поиска свободной модели ветви с выхода элемента задержки 30.

роисходит запись номера подготавли- j-n

сэи

аемои ветви в узле о памяти по адреу номера модели ветви, которая будет оделировать ее длительность. Кроме того,, задержанный сигнал поиска своодной модели ветви с выхода элемента г г адержки 30 поступает на установочый вход регистра 10, куда записыается номер модели ветви. Кроме этоо, задержанный сигнал поиска свобод40

1 о в 1 в л р

мо че ме ли вы си ре ци мо ве вы уп

26

5

JQ

0

0

5

5

5

n

и

г

0

ной модели ветви с выхода элемента задержки 30 поступает на вход триггера 12 формирования меток моделирования. Начинается процесс записи меток моделируемых ветвей в у:;ел 1 1 3 памяти и меток узлов в узел 114 памяти блока 3 моделей ветвей.

Потенциал высокого уровня с единичного выхода триггера 12 блока 1 управления поступает на вход элемента И 19 и разрешает прохождение импульсов ускоренной серии ГИЗ с полюса 61 через элемент И 19 и элемент ИЛИ 26 на счетный вход узла 8 формирования меток моделирования. Первый импульс серии ГИЗ установит на выходе узла 8 код 1, который поступает на вход схем 13 сравнения номеров ветвей и номеров узлов 14, а также через узел 23 элементов ИЛИ и полюс 52 на адресные входы узлов памяти 113 и 114 всех моделей ветвей 97 блока 3 моделей ветвей. Кроме этого, сигнал серии ГИЗ, задержанный элементом задержки 31 на время, достаточное для срабатывания узла 8, проходит через элемент ИЛИ 27 и поступает на вход узла 16 элементов И. На другой вход указанного узла с выхода регистра 9 поступает код модели ветви, которая окончила моделирование длительности ветви. Указанный код с выхода узла 16 элементов И через полюс 51 поступает на дешифратор 121 считывания меток узла 98 поиска моделей ветвей блока 3 моделей ветвей. На выходе дешифратора 121, который соответствует номеру отработавшей модели ветви, сформируется сигнал, который поступает на вход считывания узлов памяти ИЗ и 114 указанной модели ветви 97. Происходит считывание метки моделируемой ветви из узла памяти 113 и метки узла из узла памяти 114 по первому адресу о

Сигнал считанной метки моделируемой ветви с выхода узла памяти 113 через полюс 44 поступает на вход элемента ИЛИ 25 блока 1 управления. Если была считана единичная метка, на выходе элемента ИЛИ 25 сформируется сигнал высокого уровня, который через полюс 55 поступает на информационный вход узлов памяти 113 всех моделей ветвей 97 блока 3 моделей ветвей. В рассматриваемый момент на выходе элемента задержки 32 блока 1 управления сформируется сигнал высо

кого уровня первого импульса ускоренной серии ГИЗ, который поступил на вход элемента задержки 32 с выхода элемента задержки 31. Задержанный сигнал поступает на вход узла 15 элементов И, на другой вход которого поступает код найденной свободной модели ветви с выхода регистра 10. Сформированный на выходе узла 15 элементов И код свободной модели ветви через полюс 50 поступает на вход дешифратора 120 записи узла 98 поиска моделей ветвей блока 3 моделей ветвей. На выходе дешифратора, который соответствует номеру свободной модели ветви, сформируется сигнал высокого уровня, поступающий на вход записи узлов памяти 113 и 114 указанной модели ветви. Происходит запись единичной метки в узел ИЗ памяти меток моделируемых ветвей„ Если же из узла 113 памяти отработавшей модели ветви будет считана нулевая метка, на первом входе элемента ИЛИ 26 блока 1 управления будет присутствовать потенциал низкого уровня, а сигнал на выходе элемента будет определяться наличием сигнала на втором входе, который связан с выходом узла сравнения 13. Сигнал высокого уровня на выходе схемы сравнения 13 сформируется в том случае, когда код узла 9 формирования адреса меток моделирования будет равен коду номера подготавливаемой к моделированию ветви, поступающему с полюса 35, т.е.-когда к моделированию подготавливается ветвь с номером 1. В этом случае сигнал высокого уровня с выхода элемента ИЛИ 25 через полюс 55 поступает на информационный вход узлов памяти 113 всех моделей ветвей 97 блока 3 моделей ветвей, а в узел памяти 113 найденной свободной модели ветви записывается единичная метка. Б противном случае в узел памяти 113 найденной свободной модели ветви записывается нулевая метка. Так осуществляется формирование и запись в узел памяти 113 свободной модели ветви метки моделируемых ветвей по первому адресу.

Рассмотрим, как происходит формирование и запись метки узла в узел памяти 114 найденной свободной модели ветви по первому адресу. Сигнал считанной метки узла с выхода узла памяти 114 отработавшей модели ветви блока 3 моделей ветвей через полюс 43

5

0

поступает на вход элемента ИЛИ 28 блока 1 управления. Если была считана единичная метка, на выходе элемента ИЛИ 28 сформируется сигнал высокого уровня. В противном случае сигнал на выходе элемента ИЛИ 28 будет определяться вторым входом элемента, связанным с выходом схемы сравнения 14. Сигнал высокого уровня на выходе схема сравнения сформируется в том случае, когда код узла 8 формирования адреса меток моделирования будет равен коду номера начального узла подготавливаемой ветви, поступающему с полюса 41, т.е. если к моделированию подготавливается ветвь с номером начального узла, равным 1. Таким образом, сигнал единичной метки узла на выходе элемента ИЛИ 28 сформируется в том случае, если из узла 114 памяти меток узлов отработавшей модели ветви блока 3 моделей ветвей будет считана единичная метка или если к 5 моделированию подготавливается ветвь, у которой начальный узел равняется 1. С выхода элемента ИЛИ 28 сигнал единичной или нулевой метки через полюс 56 поступает на информационный вход узлов памяти 114 всех моделей ветвей 97 блока моделей ветвей. Как отмечалось, в рассматриваемый момент на вход записи узла памяти 114 свободной модели ветви поступает сигнал с соответствующего выхода дешифратора записи 120 узла 98 поиска моделей ветвей. Происходит запись метки в узел памяти 114 свободной модели ветви по первому адресу.

Следующий сигнал серии ГИЗ, поступающий на счетный вход -узла 8 формирования адреса меток моделирования блока 1 управления с выхода элемента ИЛИ 26, установит на выходе узла код 2. Этот код через элемент ИЛИ 23 и полюс 52 поступает на адресный вход узла 113 памяти меток моделируемых ветвей и узла 114 памяти меток узлов всех моделей ветвей 97 блока 3 моделей ветвей. Кроме этого, сигнал серии ГИЗ с выхода элемента ИЛИ 26 блока 1 управления через элемент задержки 31 и элемент ИЛИ 27 поступает на вход узла 16 элементов И, на другой вход которого поступает код отработавшей модели ветви с выхода регистра 9. С выхода узла. 16 элементов И код отработавшей модели ветви через полюс 5 поступает на

0

5

0

5

0

5

291

вход дешифратора 121 считывания меток узла 98 поиска моделей ветвей блока 3 моделей ветвей. На яыходе дешифратора, который соответствует номеру отработавшей модели ветви, сформируется сигнал, который поступает на вход считывания узла 113 памяти меток моделируемых ветвей и узла 114 памяти меток узлов указанной модели ветви 97. Считанная метка моделируемой ветви с выхода узла памяти 113 через полюс 44 поступает на вход элемента ИЛИ 25 блока 1 управления, а метка узла с выхода узла памяти 114 блока 3 моделей ветвей чере полюс 43 поступает на вход элемента ИЛИ 28 блока I управления. Если из узла памяти 113 отработавшей модели ветви блока 3 моделей ветвей считана единичная метка или подготавливается к моделированию ветвь с номером 2, на выходе элемента ИЛИ 25 блока 1 управления сформируется сигнал высокого уровня, который через полюс 55 поступает на информационный вход узлов памяти ИЗ всех моделей ветвей 97 блока 3 моделей ветвей. Если из узла памяти 114 отработавшей мо

дели ветви блока ч моделей ветвей СЧИ-JQ элемент И 19 на счетный вход узла 8.

тана единичная метка, или к моделированию подготавливается ветвь, у которой начальный узел равняется 2, на выходе элемента ИЛИ 28 блока 1 управления сформируется сигнал высокого уровня, который через полюс 56 поступает -на информационный вход узлов памяти 114 всех моделей ветвей 97 блока 3 моделей ветвей.

В рассматриваемый момент в блоке 1 управления сформируется задержанный элементами задержки 31 и 32 сигнал второго импульса серии ГИЗ. Этот сигнал поступает на вход узла 15 элементов И, на другой вход которого с Выхода регистра 10 поступает код свободной модели ветви. С выхода узла 15 элементов И код свободной модели ветви через полюс 50 поступает на вход дешифратора 120 записи меток узла 98 поиска моделей ветвей блока 3 моделей ветвей. На выходе дешифратора, который соответствует номеру свободной модели ветви, сформируется сигнал, который поступает на вход записи узлов памяти 113 и 114 указанной модели ветви. Происходит запись метки моделируемых ветвей с полюса 55 в узел памяти 1)3 и метки узлов в

0

643

5

0

5

30

узел памяти 114 с полюса 56 по второму адресу.

Следующий импульс серии ГИЗ, поступивший на счетный вход узла 8 формирования адреса меток моделирования блока 1 управления, установит на выходе узла код 3. Повторяется описанный процесс формирования метки моделируемых ветвей и запись ее в узел памяти 113 свободной модели ветви 97 блока 3 моделей ветвей , формирование метки узлов и запись ее в узел памяти 114 свободной модели ветви по третьему адресу и т.д.

Описанный процесс формирования меток моделируемых ветвей и меток узлов будет продолжаться до тех пор, пока на выходе переполнения узла 8 формирование адреса меток моделирования блока 1 управления не сформируется сигнал высокого уровня, что соответствует перебору всего множества возможных номеров ветвей и узлов сети. Сигнал переполнения поступает на нулевой вход триггера 12, устанавливая его в нулевое состояние. Нулевое состояние триггера 12 запрещает прохождение сигналов серии ГИЗ через

5

0

5

0

5

Кроме этого, сигнал переполнения с выхода узла 8 поступает на его нулевой вход, сбрасывая узел 8 в нулевое состояние. На этом заканчивается подготовка к моделированию первой ветви, выходящей из свершившегося узла.

Начинается процесс подготовки к моделированию второй по списку ветви, выходящей из свершившегося узла. Как отмечалось выше, код номера первой выходящей ветви с выхода регистра 72 блока 2 формирования топологии поступает на адресный вход узла 70 памяти номеров выходящих ветвей. На вход считывания указанного узла поступает сигнал ГИ2 с выхода элемента И 94. Происходит считывание из узла 70 памяти ячейки памяти по адресу номера первой выходящей ветви, т.е, считывается номер второй ветви, выходящей из свершившегося узла,. Код номера считанной ветви с выхода узла 70 памяти через узел 86 элементов ИЛИ поступает на информационный вход регистра 72 и записывается в него по импульсу серии ГИ1, поступающему на установочный вход регистра с выхода элемента К 93. С выхода регистра 72 код номера второй выходящей ветви

вновь поступает на адресный вход узла 70 памяти, а также через выходной полюс 35 в блок 1 управления

Кроме этого, в блоке 2 формирования топологии код номера второй вы ходящей ветви с выхода узла 70 памяти через узлы 86 и 88 элементов ИЛИ поступает на адресный вход узла 69 памяти номеров конечных узлов ветвей сети о На вход считывания указанного узла через элемент ИЛИ 90 поступает задержанный сигнал импульса ГИ2 с выхода элемента задержки 85. По этому сигналу из узла 69 памяти производится считывание кода номера конечного узла второй выходящей ветви. Считанный код с выхода узла 69 памяти поступает на информационный вход регистра 74 и записывается в него по второму импульсу ГИ1у поступающему на установочный вход регистра с выхода элемента И 93. С выхода регистра 74 код номера конечного узла второй выходящей ветви через полаос 34 поступает в блок 1 управления.

Таким образом, при подготовке к моделированию второй выходящей ветви в блок 1 управления с блока 2 формирования топологии через полюс 35 по ступает код номера подготавливаемой ветви, через полюс 34 - код номера конечного узла подготавливаемой ветви и через полюс 41 - код номера начального узла подготавливаемой ветви. Кроме этого,в блок 1 управления через полюс 36 с блока формирования топологии поступает сигнал второго импульса ГИ2 поиска свободной модели ветви. В блоке 1 управления сигнал поиска свободной модели ветви с полюса 36 через элемент ИЛИ 27 поступает на вход узла 16 элементов И, на другой вход которого поступает код отработавшей модели ветви с выхода регистра 9. Сформировавшийся на выходе узла 16 элементов И код отработавшей модели ветви через полюс 51 поступает на вход дешифратора 121 считывания меток узла 98 поиска моделей ветвей блока 3 моделей ветвей. На выходе дешифратора, который соответствует номеру отработавшей модели ветви, сформируется сигнал, поступающий на вход считывания узлов памяти 113 и 114 указанной модели ветви. Происходит считывание метки узлов из узла памяти 114 по адресу номера конечного узла подготавливаемой к моделирова

5

0

5

0

5

0

5

0

5

нию ветви, поступающего с полюса блока 1 управления через элементы И 18 и ИЛИ 23 и полюс 52 на адресный вход узлов памяти 113 и 114 всех моделей ветвей 97 блока 3 моделей ветвей. Если из узла памяти 114 считана единичная метка, обозначающая, что данная ветвь образует частный контур сети, сигнал единичной метки с выхода узла памяти 114 через полюс 43 и элемент НЕ 29 блока управления поступает на вход элемента И 21, запрещая прохождение сигнала поиска свободной модели ветви через этот элемент. В этом случае, если на входных полюсах 37 и 42 (как рассматривалось выше) присутствуют разрешающие сигналы, сигнал поиска свободной модели ветви сформируется на выходе элемента И 22. С выхода элемента И 22, а в случае считывания нулевой метки узла - с выхода элемента И 21, сигнал поиска свободной модели через элемент ИЛИ 24 и полюс 54 поступает в блок 3 моделей ветвей. В последнем по этому сигналу ищется свободная модель ветви, в формирователь-99 временных интервалов которой заносится код длительности подготавливаемой к моделированию ветви. Далее производится формирование меток моделируемых ветвей и запись их в узел памяти 113 свободной модели ветви, а также формирование меток узлов и запись их в узел памяти 114 указанной модели ветви. В результате в узле памяти 113 сформируются единичные метки по тем адресам, по которым были считаны единичные метки с узла памяти 113 отработавшей- модели ветви, а также по адресу номера подготавливаемой к моделированию ветви. В узле памяти 114 свободной модели ветви считаны единичные метки с узла памяти 114 отработавшей модели ветви, а также по адресу номера начального узла подготавливаемой к моделированию ветви. Так осуществляется подготовка к моделированию второй ветви, выходящей из свершившегося узла.

Описанный процесс подготовки к моделированию ветвей, выходящих из свершившегося узла, будет продолжаться до тех пор, пока не будет подготовлена последняя ветвь из списка выходящих ветвей. После этого по адресу ее номера в узле 70 памяти номеров выходящих ветвей блока 2 формирования топологии будет считан код X, означающий конец списка выходящих ветвей. Этот код записывается в регистр 72, выход которого подключен к дешифратору 78 состояния X. В дешифраторе путем сравнения кодов вырабатывается сигнал конца списка выходящих из узла ветвей. Этот сигнал с выхода дешифратора 78 поступает на нулевой вход триггера 77, устанавливая его в нулевое состояние. Нулевое состояние триггера запрещает прохождение импульсов ГИ1 и ГИ2 через зле- |менты И 93 и 94 соответственно. Кроме этого, сигнал поиска прерывания с выхода дешифратора 78 через полюс 38 поступает в блок 1 управления„

В блоке 1 управления сигнал поиска прерывания с полюса 38 поступает на единичный вход триггера 11, устанавливая его в единичное состояние, а также через полюс-39 - в блок 3 моделей ветвей. С полюса 39 сигнал поиска прерывания поступает на вход стробирования формирователей U6 сброса всех моделей ветвей 97, а также на вход элемента ИЛИ 118 узла 98 поиска моделей ветвей. На выходе формирователя 116 сброса той модели ветви, на установочный вход формирователя сброса которой поступил сигнал с выхода элемента И 103, т.е. отработавшей модели ветви, прерывание от которой обрабатывалось последним, сформируется сигнал, поступающий на нулевой вход этого же формирователя, на нулевой вход триггера 100 занятости и на установочный вход счетчика 115 узлов. Триггер 100 занятости устанавливается в нулевое состояние, что означает освобождение данной модели для дальнейших вычислений, а в счетчик 115

узлов записывается код, постоянно за- дз второй вход элемента И 106 поступает

данный на полюса 64 и который на еди- .ницу меньший количества узлов сети. Сигнал поиска прерьюания, который поступил на вход элемента ИЛИ 118 узла 98 поиска моделей ветвей, сформирует на выходе сигнал высокого уровня. Этот сигнал через полюс (1,1).поступает на входы элементов И 102 (1) и 103 (О первой модели ветви 97. Так как триггер 101 прерывания первой модели ветви находится в нулевом состоя- нии (если даже модель ветви и отработала временной интервал, то прерывание от нее уже отработано), на вы50

55