Изобретение относится к радиотехнике, в частности к контролю импульс ных сигналов, и может быть использо- .вано для проверки функционирования и нахождения неисправностей устройств, построенных на логических микросхемах.

Цель изобретения - расширение функциональных возможностей логического пробника путем определения коэффициента деления и количества импульсов в пачке.

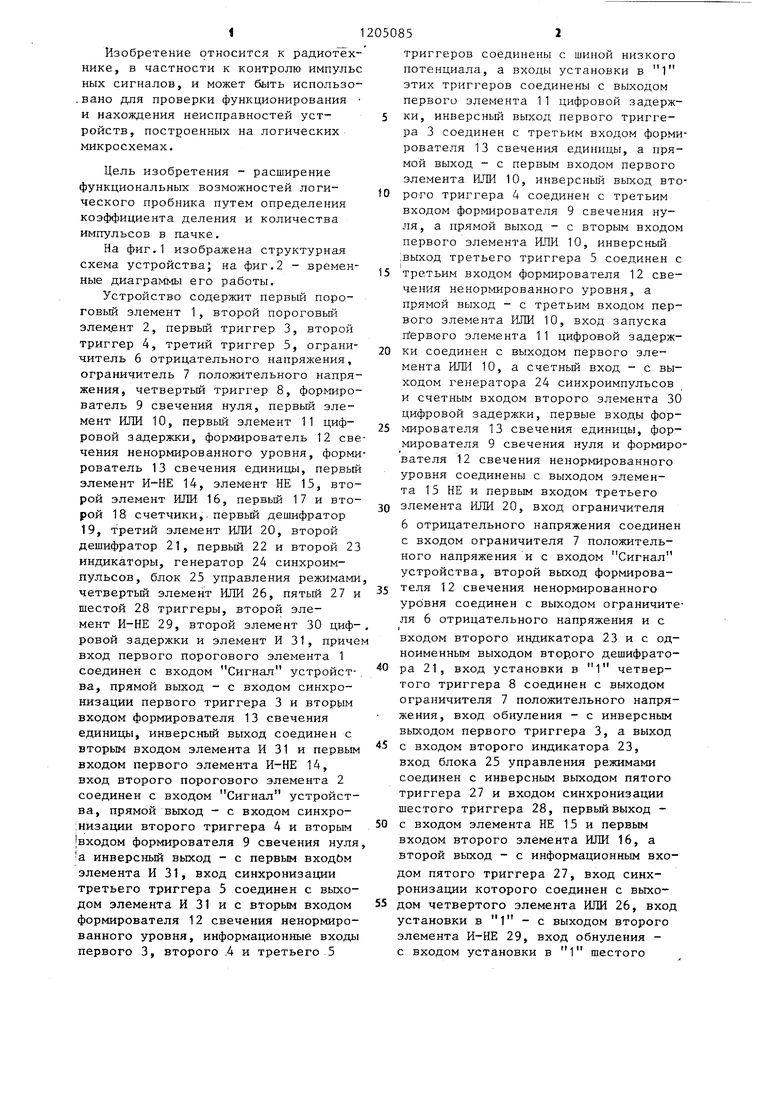

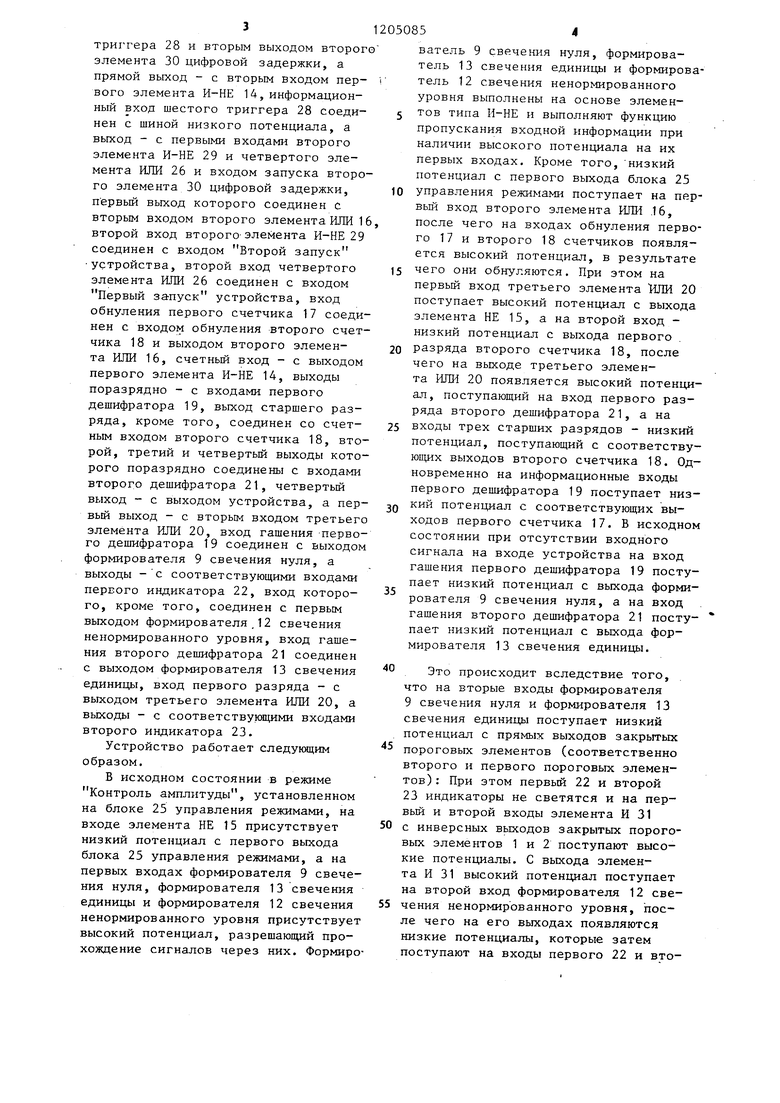

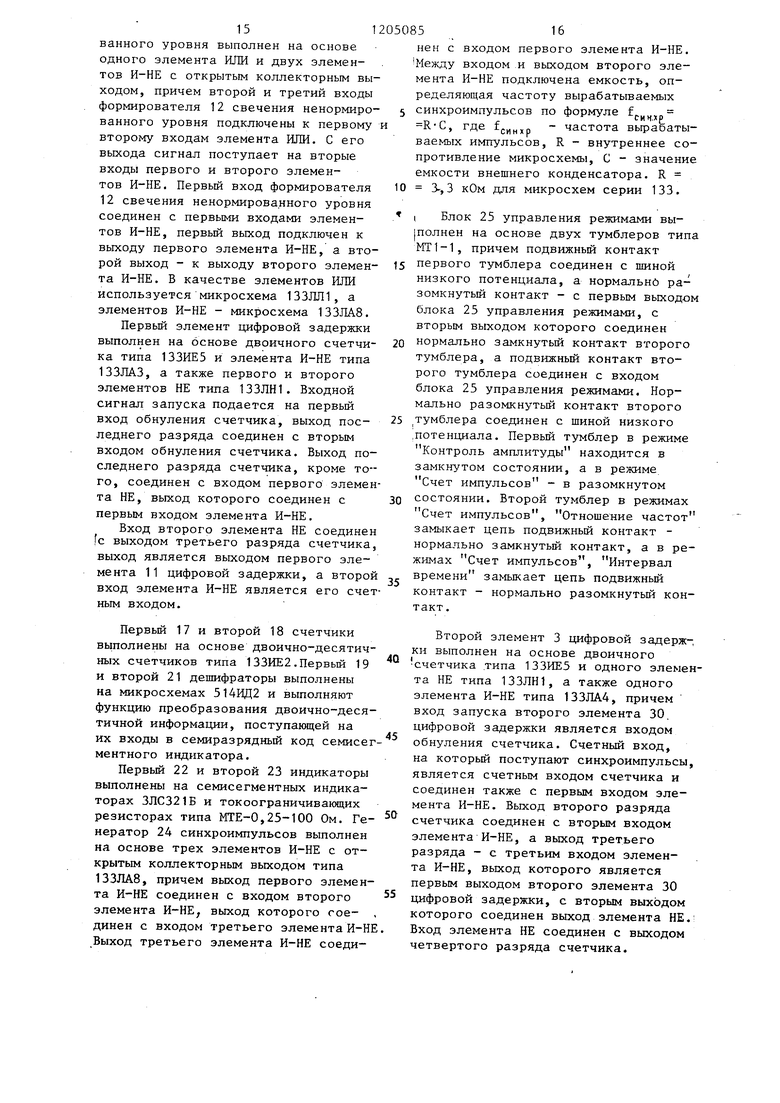

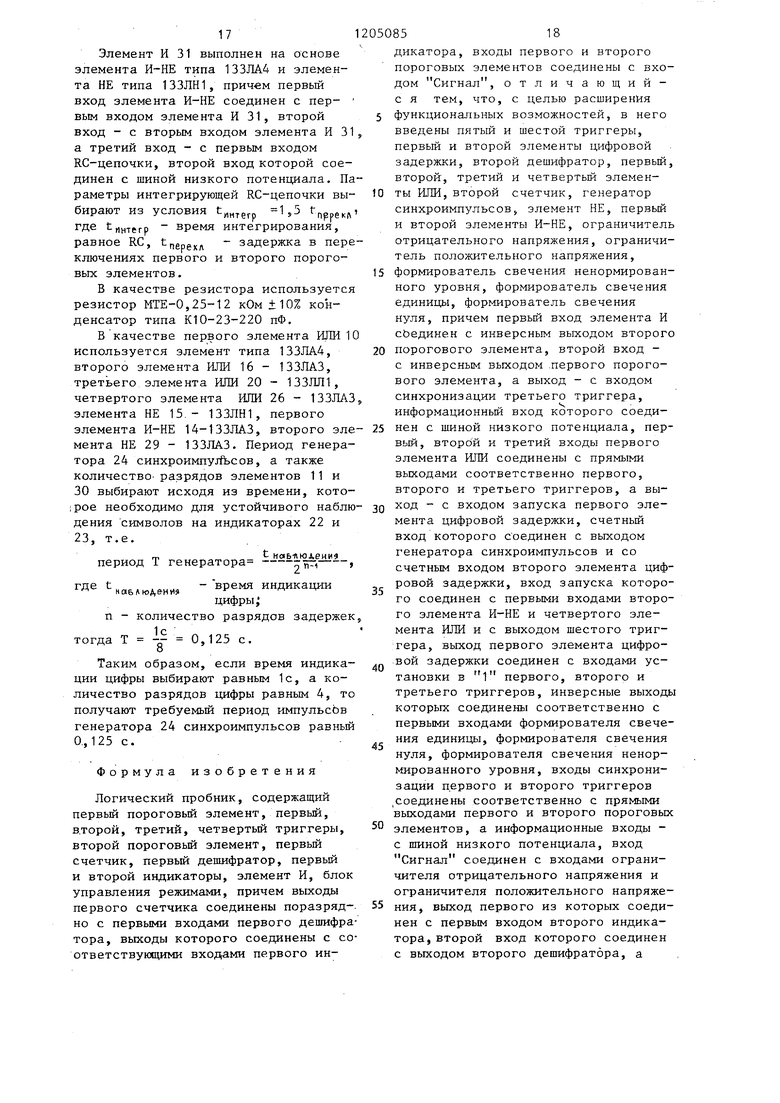

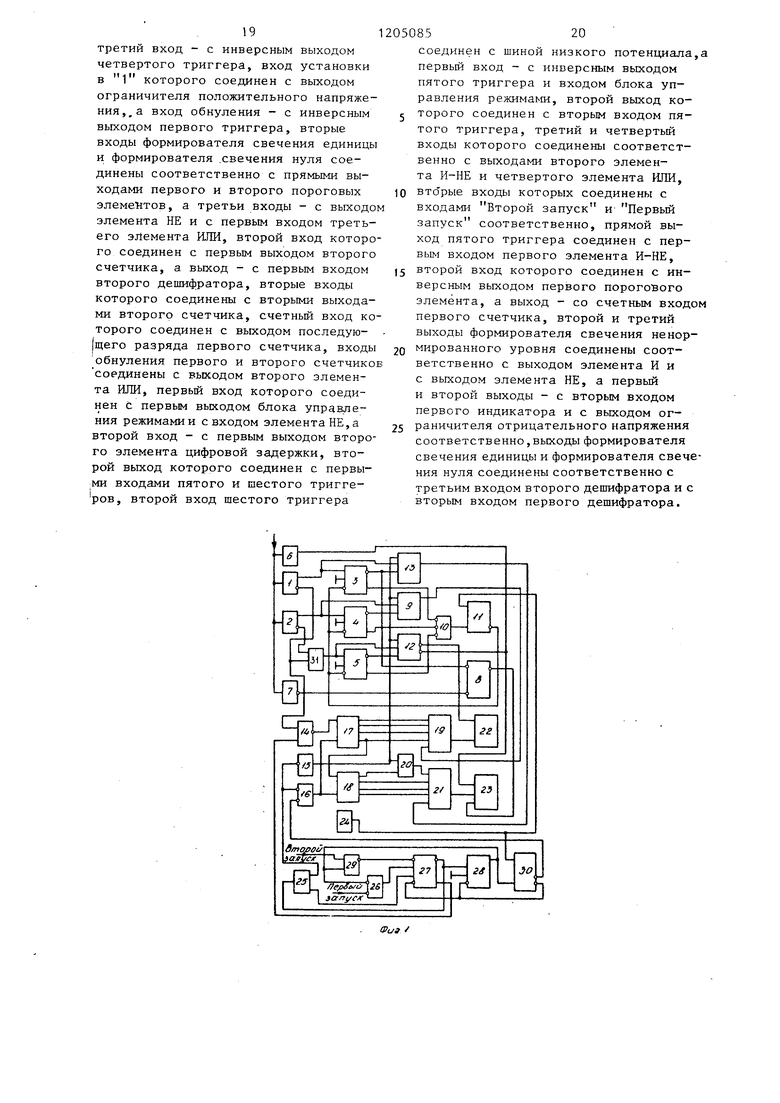

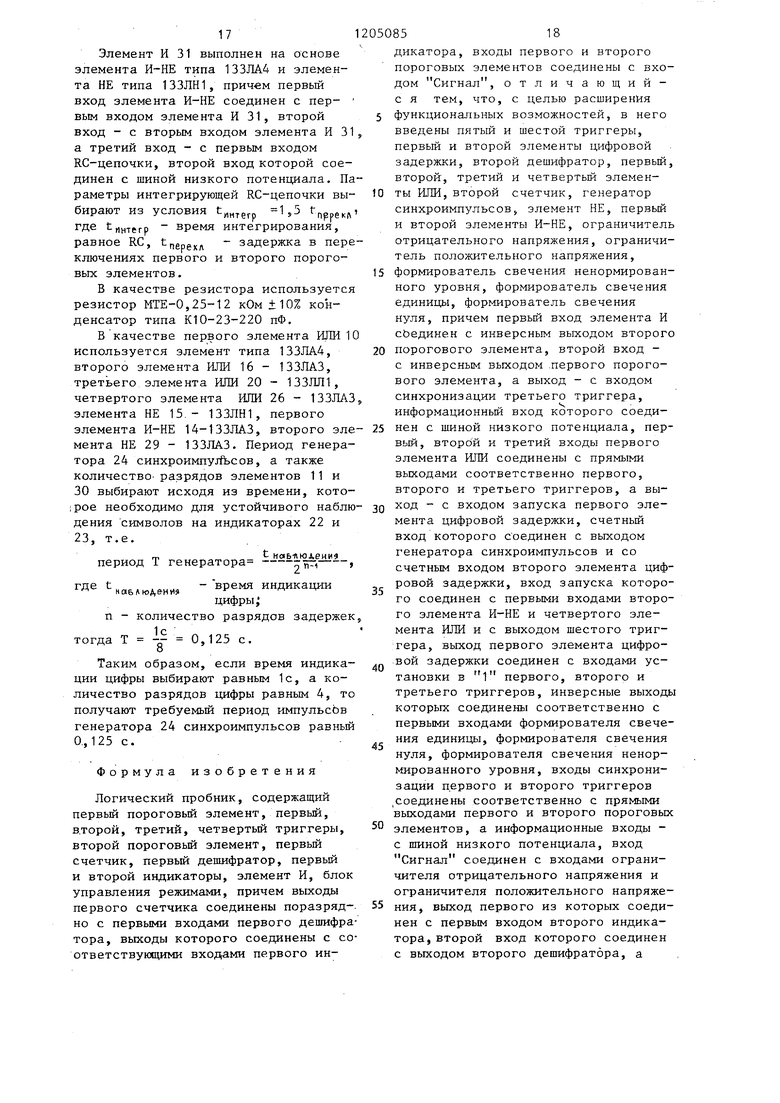

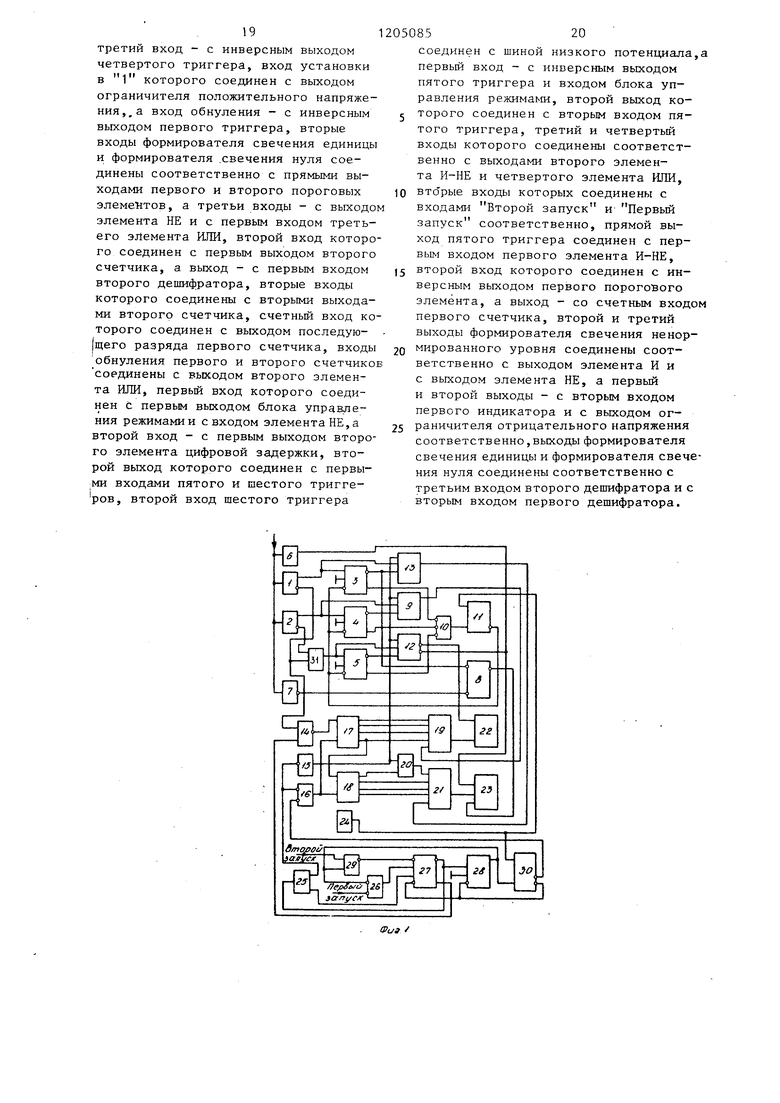

На фиг.1 изображена структурная схема устройства; на фиг.2 - временные диаграммы его работы.

Устройство содержит первый пороговый элемент 1, второй пороговый элемент 2, первый триггер 3, второй триггер 4, третий триггер 5, ограничитель 6 отрицательного напряжения, ограничитель 7 положительного напряжения, четвертый триггер 8, формирователь 9 свечения нуля, первый элемент ИЛИ 10, первый элемент 11 цифровой задержки, формирователь 12 свечения ненормированного уровня, формирователь 13 свечения единицы, первый элемент И-НЕ 14, элемент НЕ 15, второй элемент ИЛИ 16, первый 17 и второй 18 счетчики,. первый дешифратор 19, третий элемент ИЛИ 20, второй дешифратор 21, первый 22 и второй 23 индикаторы, генератор 24 синхроимпульсов, блок 25 управления режимами четвертый элемент ИЛИ 26, пятый 27 и шестой 28 триггеры, второй элемент И-НЕ 29, второй элемент 30 цифровой задержки и элемент И 31, приче вход первого порогового элемента 1 соединен с входом Сигнал устройст- ва, прямой выход - с входом синхронизации первого триггера 3 и вторым входом формирователя 13 свечения единиць, инверсный выход соединен с вторым входом элемента И 31 и первым входом первого элемента И-НЕ 14, вход второго порогового элемента 2 соединен с входом Сигнал устройства, прямой выход - с входом синхро- :низации второго триггера 4 и вторым |входом формирователя 9 свечения нуля а инверсный выход - с первым входЬм элемента И 31, вход синхронизации третьего триггера 5 соединен с выходом элемента И 31 и с вторым входом формирователя 12 свечения ненормированного уровня, информационные входы первого 3, второго ,4 и третьего 5

триггеров соединены с шиной низкого потенциала, а входы установки в 1 этих триггеров соединены с выходом первого элемента 11 цифровой задержки, инверсный выход первого триггера 3 соединен с третьим входом формирователя 13 све-чения единицы, а прямой выход - с первым входом первого элемента ИЛИ 10, инверсньй выход второго триггера 4 соединен с третьим входом формирователя 9 свечения нуля, а прямой выход - с вторым входом первого элемента ИЛИ 10, инверсный ;вьгход третьего триггера 5 соединен с

третьим входом формирователя 12 свечения ненормированного уровня, а прямой выход - с третьим входом первого элемента ИЛИ 10, вход запуска первого элемента 11 цифровой задержки соединен с выходом первого элемента ИЛИ 10, а счетный вход - с выходом генератора 24 синхроимпульсов и счетным входом второго элемента 30 цифровой задержки, первые входы формирователя 13 свечения единицы, формирователя 9 свечения нуля и формирователя 12 свечения ненормированного уровня соединены с выходом элемента 1 5 НЕ и первым входом третьего

элемента ИЛИ 20, вход ограничителя 6 отрицательного напряжения соединен с входом ограничителя 7 положительного напряжения и с входом Сигнал устройства, второй выход формирователя 12 свечения ненормированного

урбвня соединен с выходом ограничителя 6 отрицательного напряжения и с входом второго индикатора 23 и с одноименным выходом второго дешифратора 21, вход установки в 1 четвертого триггера 8 соединен с выходом ограничителя 7 положительного напряжения, вход обнуления - с инверсным выходом первого триггера 3, а выход

с входом второго индикатора 23, вход блока 25 управления режимами соединен с инверсным выходом пятого триггера 27 и входом синхронизации шестого триггера 28, первый выход с входом элемента НЕ 15 и первым входом второго элемента ИЛИ 16, а второй выход - с информационным входом пятого триггера 27, вход синхронизации которого соединен с выходом четвертого элемента ИЛИ 26, вход установки в 1 - с выходом второго элемента И-НЕ 29, вход обнуления - с входом установки в 1 шестого

триггера 28 и вторым выходом второго элемента 30 цифровой задержки, а прямой выход - с вторым входом пер- вого элемента И-НЕ 14, информационный вход шестого триггера 28 соеди-

нен с шиной низкого потенциала, а выход - с первыми входами второго элемента И-НЕ 29 и четвертого элемента РШИ 26 и входом запуска второго элемента 30 цифровой задержки, первый вькод которого соединен с вторым входом второго элемента ИЛИ 16 второй вход ВТОРОГО элемента И-НЕ 29 соединен с входом Второй запуск устройства, второй вход четвертого элемента ИЛИ 26 соединен с входом Первый запуск устройства, вход обнуления первого счетчика 17 соединен с входом обнуления второго счетчика 18 и выходом второго элемен- та ИЛИ 16, счетный вход - с выходом первого элемента И-НЕ 14, выходы поразрядно - с входами первого дешифратора 19, выход старшего разряда, кроме того, соединен со счет- ным входом второго счетчика 18, второй, третий и четвертый выходы которого поразрядно соединены с входами второго дешифратора 21, четвертый выход - с выходом устройства, а пер- выход - с вторым входом третьего элемента ИЛИ 20, вход гашения первого дешифратора 19 соединен с выходом формирователя 9 свечения нуля, а выходы - с соответствующими входами первого индикатора 22, вход которого, кроме того, соединен с первым выходом формирователя.12 свечения ненормированного уровня, вход гашения второго дешифратора 21 соединен с выходом формирователя 13 свечения единицы, вход первого разряда - с выходом третьего элемента ИЛИ 20, а выходы - с соответствующими входами второго индикатора 23.

Устройство работает следующим образом.

В исходном состоянии в режиме Контроль амплитуды, установленном на блоке 25 управления режимами, на входе элемента НЕ 15 присутствует низкий потенциал с первого выхода блока 25 управления режимами, а на первых входах формирователя 9 свечения нуля, формирователя 13 свечения единицы и формирователя 12 свечения ненормированного уровня присутствует высокий потенциал, разрешающий прохождение сигналов через них. Формиро

5 0 5 Q

5

5

0

5

ватель 9 свечения нуля, формирователь 13 свечения единицы и формирователь 12 свечения ненормированного уровня выполнены на основе элементов типа И-НЕ и выполняют функцию пропускания входной информации при наличии высокого потенциала на их первых входах. Кроме того, низкий потенциал с первого выхода блока 25 управления режимами поступает на первый вход второго элемента ИЛИ ,16, после чего на входах обнуления первого 17 и второго 18 счетчиков появляется высокий потенциал, в результате чего они обнуляются. При этом на первый вход третьего элемента ИЛИ 20 поступает высокий потенциал с выхода элемента НЕ 15, а на второй вход - низкий потенциал с выхода первого разряда второго счетчика 18, после чего на выходе третьего элемента ИЛИ 20 появляется высокий потенциал, поступающий на вход первого разряда второго дешифратора 21, а на входы трех старших разрядов - низкий потенциал, поступающий с соответствующих выходов второго счетчика 18. Одновременно на информационные входы первого дешифратора 19 поступает низкий потенциал с соответствующих выходов первого счетчика 17. В исходном состоянии при отсутствии входного сигнала на входе устройства на вход гашения первого дешифратора 19 поступает низкий потенциал с выхода формирователя 9 свечения нуля, а на вход гашения второго дешифратора 21 поступает низкий потенциал с выхода формирователя 13 свечения единицы.

Это происходит вследствие того, что на вторые входы формирователя 9 свечения нуля и формирователя 13 свечения единицы поступает низкий потенциал с прямых выходов закрытых пороговых элементов (соответственно второго и первого пороговых элементов) : При этом первый 22 и второй 23 индикаторы не светятся и на первый и второй входы элемента И 31 с инверсных выходов закрытых пороговых элементов 1 и 2 поступают высокие потенциалы. С выхода элемента И 31 высокий потенциал поступает на второй вход формирователя 12 свечения ненормированного уровня, после чего на его выходах появляются низкие потенциалы, которые затем поступают на входы первого 22 и второго 23 индикаторов. На информационном табло состоящем из первого и второго индикаторов,, высвечивается символ ненормированного уровня входного сигнала в виде двух поперечных полос. Пятый триггер 27 обнуляется, а шестой триггер 28 устанавливается в 1 низким потенциалом, приходящим с второго выхода второго элемента 30 цифровой задержки и вырабатываемым им при включении питания,

Пороговые элементы 1 и 2 настроены соответственно на напряжения срабатывания 2,4 В и 0,4 Б, причем при поступлении на вход устройства сигнала с уровнем менее 0,4 В открыт пороговый элемент 2 и на его прямом выходе высокий потенциал, а на инверсном низкий. При поступлении сигнала с уровнем более 2,4 В открыт пороговый элемент 1 и на его прямом выходе высокий потенциал, а на инверсном низкий.

Таким образом, при поступлении на вход устройства уровня напряжения в интервале 0-0,4 В открыт второй пороговый элемент 2, на второй вход формирователя 9 свечения нуля поступает высокий потенциал и на ег выходе появляется высокий потенциал При этом на вход гашения второго дешифратора 19 поступает высокий потенциал и на первом индикаторе 22 высвечивается цифра 0. Она светится до тех пор, пока на входе устройства присутствует уровень напряжения 0-0,4 В.

При поступлении на вход устройства уровня напряжения отрицательной полярности срабатывает ограничитель 6 отрицательного напряжения и ограничивает его. на уровне - 0,7 В. При этом открьшается второй пороговый элемент 2 и сигнал с его выхода проходит так же, как при поступлении на вход устройства уровня напряжения логического нуля (напряжения 0-0,4 В). Одновременно с выхода ограничителя 6 отрицательного напряжения на вход второго индикатора 23 поступает низкий потенциал, что вы- зьтает свечение соответствующего, сегмента. При этом на информационном табло индицируется символ О, что сигнализирует о наличии отрицательного напряжения на входе устройства

При поступлении на вход устройства напряжения более 2,4 В открывается первый пороговый элемент 1, с прямого выхода которого высокий потенциал поступает на второй вход формирователя 13 свечения единицы. С выхода 5 формирователя 13 свечения единицы на вход гашения второго дешифратора 21 поступает высокий потенциал, при этом на втором индикаторе 23 начинает светиться цифра 1. Она светится

0 до тех пор, пока на входе устройства присутствует уровень напряжения более 2,4 В.

Если входное напряжение устройства превьш1ает уровень 4,5 В, то сра5 батывает ограничитель 7 положительного напряжения и ограничивает входное напряжение,.на входе пороговых элементов 1 и 2 на уровне 5 В. При этом на выходе ограничителя 7

0 положительного напряжения появляется низкий потенциал, котбрый поступает на вход установки в 1 четвертого триггера 8, после чего с выхода последнего на вход свечения

5 децимальной точки второго индикатора 23 поступает низкий потенциал. На .втором индикаторе 23 при этом светится цифра 1 и децимальная точка, сигнализируя о поступлении на вход уст0 ройства сигнала, превьш1ающего по уровню логическую единицу.

Если уровень напряжения, поступа- гаций на вход устройства, находится . в пределах 0,4-2,4 В, то оба пороговых элемента 1 и 2. закрыты, что аналогично отсутствию напряжения на входе устройства. При этом на индикаторах 22 и 23 индицируется символ -, что сигнализирует о поступлении на вход устройства сигнала, уровень которого не соответствует нормам на логический нуль и логическую единицу.

Если на вход устройства подаются импульсные сигналы положительной полярности (фиг.2а), причем длительность значительно меньше паузы между импульсами, то на прямом выходе пер-г

вого порогового элемента 1 (фиг.2б) появляются импульсы положительной

полярности, которые поступают на вход синхронизахщи первого триггера 3 и второй вход формирователя 13 свечения единицы. При этом по переднему фронту первого импульса срабатывает 5 триггер 3 и на его инверсном выходе (фиг.2в) появляется высокий потенциал, который поступает на третий вход формирователя 13 свечения единицы.

5

0

5

0

7

Одновременно с прямого выхода первого триггера 3 низкий потенциал постпает на первый вход первого элемента ИЛИ 10, после чего с выхода этого элемента сигнал высокого потенци ала поступает на вход запуска первого элемента 11 цифровой задержки. Элемент задержки выполнен на основе двоичного счетчика, и входной сигна поступает на его первый вход обнуле ния, второй вход обнуления соединен с выходом последнего разряда этого счетчика. Таким образом, как только входной сигнал обнуляет счетчик вследствие действия обратной связи, его дальнейшее наличие на входе запуска необязательно. Первый элемент 11 цифровой задержки начинает отсчитывать синхр оимпульсы генератора 24 синхроимпульсов. После поступления определенного количества импульсов на счетный вход первого элемента 11 цифровой задержки на его выходе появляется низкий потенциал, который поступает на входы установки в 1 первого 3, второго 4 и третьего 5 триггеров. После этого первый триггер 3 сбрасывается в исходное сос- :Тояние. Однако первый элемент 11 цировой задержки не возвращается в исходное состояние, а продолжает отсчитьшать счетные импульсы до тех пор, пока на выходе старшего разряда счетчика не появится высокий потенциал, разрешающий повторный запуск первого элемента 11 цифровой задержки. Далее описанньш процесс повторяется.

Таким образом, первьй триггер 3 периодически запускается импульсами с выхода первого порогового элемен- )та 1, а сбрасывается выходным импульсом первого элемента 11 цифрово задержки. При этом на выходе формирователя 13 свечения единицы |(фиг.2г) появляются импульсы положительной полярности, которые получаюся из наложения входной импульсной последовательности (фиг.2а) и импульсов на выходе первого триггера 3 (фиг.2в). Далее импульсы с выхода формирователя 13 свечения единицы поступают на вход гашения второго дешифратора 21, что вызьшает свечение цифры 1 на втором индикаторе 23 Свечение определяется длительностью импульса на выходе первого триггера 3. Это связано с тем, что длитель

5 5 0 5 о

5

5

0

5

0

8

ность импульсов на входе устройства значительно меньше паузы и, следовательно, средняя энергия свечения первого индикатора 22, которая определяется их соотношением, очень мала.

Второй пороговый элемент 2 открыт при отсутствии импульса на входе устройства и закрывается при его поступлении. Таким образом, на его прямом вькоде (фиг.2д) появляются инвертированные входные импульсы, которые поступают на второй вход формирователя 9 свечения нуля. По заднему фронту этих импульсов обнуляется второй триггер 4, при этом на его инверсном выходе формируется импульс положительной полярности, который поступает на третий вход формирователя 9 свечения нуля, где они суммируются с импульсами, поступающими по второму входу. После этого сигнал с выхода фop шpoвaтeля 9 свечения нуля (фиг.2е) поступает на вход гашения первого дешифратора 19. В связи с тем, что на этом входе в паузе между импульсами присутствует высокий потенциал, а длительность импульсов мала по отношению к паузе между ними, на первом индикаторе 22 постоянно светится цифра 0. Таким образом, на информационном табло, состоящем из первого и второго индикаторов, постоянно индицируется цифра О и периодически светится цифра 1 . Это сигнализирует о подаче импульсов положительной полярности на вход устройства.

При подаче на вход устройства импульсов отрицательной полярности работа устройства аналогична описанному, однако вследствие того, что на устройство при отсутствии импульсов подается высокий потенциал, на входе гашения второго дешифратора 21 высокий потенциал при отсутствии импульсы и низкий при наличии импульса. В связи с тем, что отношение длительности импульсов к паузе между ними мало, то на втором индикаторе 23 постоянно светится цифра 1.

При этом на входе гашения первого дешифратора 19 присутствуют импульсы второго триггера 4 и импульсы входной последовательности устройства. В связи с тем, что в паузе между входными импульсами на вход гашения первого дешифратора 19 подается низкий потенциал, то свечение первого дешифратора

определяется импульсами второго триггера 4, который периодически об- нуляется импульсами входной последовательности, а устанавливается в 1. первым элементом 11 цифровой задержк Таким образом, на первом индикаторе 22 синхронно с импульсом второго триггера 4 периодически светится цифра О.При этом на информационном табло постоянно индицируется цифра 1 и периодически светится цифра 0.

При подаче на вход устройства импульсов, амплитуда которых не достигает заданных уровней (фиг.2и), в паузе между импульсами открыт второй пороговьм элемент 2, а во время импульса он закрьшается и на второй вход элемента И 31 подается высокий потенциал. На первый вход этого элемента с инверсного выхода первого порогового элемента 1 постоянно поступает высокий потенциал (первый по роговый элемент 1 закрыт вследствие того, что амплитуда импульсов меньше порога срабатывания этого элемента). На выходе элемента И 31 при этом появляется высокий потенциал, который поступает на вход синхронизации третьего триггера 5. Третий триггер 5 устанавливается в О, при этом запускается первый элемент 11 цифровой задержки, а с инверсного выхода третьего триггера 5 на второй вход формирователя 12 свечения ненормированного уровня поступает высокий потенциал, после чего низкий потенциал с первого и второго выходов формирователя 12 свечения ненормированного уровня поступает на входы первого 22 и второго 23 индикаторов. Свечение сегментов продолхсается до тех пор, пока третий триггер 5 сигналом с первого элемента 11 цифровой задержки не установится в 1. Таким образом, постоянно светится цифра О на первом индикаторе 22 и периодически символ - на первом 22 и втором 23 индикаторах, сигнализируя о недопустимо малой амплитуде входных импульсов. Если на вход устройства поступает сигнал, изображенный на фиг.2к, то постоянно индицируется символ - на первом 22 и втором 23 индикаторах и периодически загорается цифра О на первом индикаторе 22. Если на вход устройства поступает сигнал, изображенный на (фиг.2л), то постоянно индицируется цифра 1 на втором индикаторе 2,3 и периодически

0

5

0

5

0

0

0

светится символ - на первом 22 и втором 23 индикаторах.

В исходном состоянии в режимах Счет импульсов, Интервал времени, установленных на блоке 25 управления режимами, на входе элемента НЕ 15 и первом входе второго элемента ИЛИ 16 присутствует высокий потенциал с первого выхода блока 25 управления режимами. Одновременно с выхода элемента НЕ 15 на первьш вход третьего элемента ИЛИ 20 и на первые входы формирователя 9 свечения нуля, формирователя 13 свечения единицы и форJ мирователя 12 свечения ненормированного уровня поступает низкий потенциал, после чего формирователи не про- пускают импульсы. На выходах формирователя 9 свечения нуля и формирователя 13 свечения единицы при этом устанавливается высокий потенциал, который поступает на вход гашения дешифраторов 19 и 21 и постоянно дает разрешение на свечение индикаторов 22 и 23. На выходе третьего элемента ИЛИ 20 появляется низкий потенциал (на второй вход элемента ИЛИ 20 с выхода первого разряда второго счетчика поступает низкий потенциал). На второй вход второго элемента ИЛИ 16 с первого выхода второго элемента 30 цифровой задержки поступает высокий потенциал, поэтому на его выходе присутствует низкий потенциал, который поступает на входы обнуления первого. 17.и второго 18 счетчиков. На второй вход элемента И-НЕ 14 с прямого выхода пятого триггера 27 поступает низкий потенциал, что запрещает прохождение импульсов, поступающих на первый вход этого элемента с инверсного выхода первого порогового элемента 1. На втором выходе блока 25 управления режимами присутствует низкий потенциал, который поступает

на информационньш вход пятого триггера 27. При поступлении на вход Второй запуск устройства импульсов положительной полярности (фиг,2м) они проходят на вход установки в 1 пятого триггера 27 с выхода второго элемента И-НЕ 29. После этого по переднему фронту самого первого импульса триггер устанавливается в 1, при этом с его прямого выхода высокий потенциал поступает на второй вход элемента И-НЕ 14 и импульсы, поступающие на вход Сигнал устройства начинает поступать на счетный вход

первого счетчика 17 с инверсного выхода первого порогового элемента 1 через первый элемент И-НЕ 1А. С выхода старшего разряда этого счетчика сигнал поступает на счетный вход вто- рого счетчика 18. Этим обеспечивается счет единиц импульсов на первом счетчике 17 и десятков импульсов на втором счетчике 18. При этом на первом индикаторе 22 индицируется коли- чество единиц, а на втором индикаторе 23 - десятков импульсов, поступивших на вход Сигнал устройства. Счет импульсов ведется до поступления импульса на вход Первьш запуск устройства. После поступления импульса на вход Первый запуск устройства (фиг.2н) обнуляется пятый триггер 27, при этом с его прямого выхода

низкий потенциал поступает на второй

вход первого элемента И-НЕ 14 и импульсы на счетный вход первого счетчика 17 перестают поступать. Одновременно с инверсного выхода пятого триггера 27 высокий потенциал посту- пает на вход синхронизации шестого триггера 28 и триггер обнуляется, после чего низкий потенциал с информационного входа шестого триггера 28 поступает на его выход. Этот потенциал поступает на вход запуска второго элемента 30 цифровой задержки, разрешая счет импульсов, и на первый вход второго элемента 29 И-НЕ запрещая поступление импульсов с входа Второй запуск устройства на вход установки в 1 пятого триггера 27. На счетчиках 17 и 18 запоминается код, соответствующий количеству импульсов, поступивших на вход Сигнал устройства между поступлением импульсов по входам Второй запуск и Первый запуск. Этот код поступает на дешифраторы 19 и 21 и индицируется в виде цифр индикаторами 22 и 23. После поступления определенного количества синхроимпульсов на счет- ньй вход второго элемента 30 цифровой задержки на его первом выходе появляется низкий потенциал, который поступает на второй вход второ- го элемента ИЛИ 16, после чего на входах обнуления счетчиков 17 и 18 получается высокий потенциал и они обнуляются. С приходом следующего

синхроимпульса на втором выходе второго элемента 30 цифровой зрдерж- ки появляется низкий потенциал, пос- |ле чего устанавливается в 1 шес10 jj

20

0

5

5

той триггер 28, при этом на его выходе появляется высоки потенциал, разрешающий прохождение импульсов Первь й запуск и Второй запуск. Процесс повторяется циклически. Таким образом, устройство ведет подсчет импульсов, поступающих по входу Сигнал, в интервале от поступления импульса на вход Второй за- пус-к до поступления импульса по входу Первьй запуск.

1

При работе устройства в режимах

Счет импульсов, Отношение частот импульсы с инверсного выхода пятого триггера 27 поступают на вход блока 25 управления режимами, а затем с его второго выхода на информационный вход пятого триггера 27. При этом обеспечивается работа этого триггера в счетном режиме от импульсов, поступающих по входу Первый запуск устройства (фиг.2н), и на его прямом выходе (фиг.2п) появляется положительный импульс, который поступает на второй вход элемента И-НЕ 14. На вход первого счетчика 17 поступают импульсы, которые успевают пройти через элемент И-НЕ 14 за время импульса пятого триггера 27. По окончании этого импульса на инверсном выходе пятого триггера 27 появляется высокий уровень, который устанавливает в О шестой триггер 28. При этом на его прямом выходе появляется низкий потенциал, который запускает второй элемент 30 цифровой задержки и блокирует дальнейшее прохождение импульсов первого запуска через четвертый элемент ИЛИ 26.На счетный вход второго элемента 30 задержки приходят синхроимпульсы с генератора 24. После поступления определенного количества синхроимпульсов второй элемент 30 цифровой задержки срабатывает, после чего с его первого выхода на второй вход второго элемента ИЛИ 16 поступает низкий потенциал, которьй обнуляет счетчики 17 и 18. При поступлении еще одного синхроимпульса на втором выходе второго элемента 30 цифровой задержки появляется низкий потенциал, устанавли- вагаций в исходное состояние пятый

27и шестой 28 триггеры, при этом на прямом выходе пятого триггера 27 устанавливается низкий потенциал,

а на прямом выходе шестого триггера

28- высокий потенциал, который разрешает прохождение импульсов на вхо пятого триггера 27 и одновременно обнуляет второй элемент 30 цифровой задержки.

Таким образом, после прохождения второго импульса Первый запуск первый 17 и второй 18 счетчики прекращают счет импульсов, поступающих на вход Сигнал устройства, а на разрядах счетчиков устанавливается код, соответствующий количеству поступивших импульсов на вход Сигнал устройства. Этот код поступает на дешифраторы 19 и 21 и через них на индикаторы 22 и 23. На первом индикаторе высвечивается количество единиц импульсов, а на втором индикаторе 23 - количество десятков импульсов. Через некоторое время, определяемое вторым элементом 30 цифровой задержки.эти цифры сбрасываются и н ачинается новый цикл счет Процесс повторяется циклически.

Первый 3, второй 4, третий 5, пятый 27 и шестой 28 триггеры выполнены по схеме D-тр ггера, четвертый триггер 9 - по схеме RS-триггера. В качестве триггеров использованы D-триггеры типа 133ТМ2. Б четвертом триггере 8 вход синхронизации соединён с шиной низкого потенциала. Первый 1 и второй 2 пороговые эле- .менты выполнены на основе компарато ра напряжения и инвертора, причем в первом пороговом элементе опорное напряжение 2,4 В подается на неинветирующий вход, а входной сигнал - на инвертирующий вход компаратора, с его выхода берется инверсное значение выходного сигнала порогового элемента 1, которое затем поступает на вход инвертора. После инвертора сигнал поступает на прямой выход первого порогового элемента 1. Во втором пороговом элементе 2 опорное напряжение 0,4 В подается на инвертирующий вход компаратора, а входной сигнал -. на неинвертирующий вхо Инверсное значение выходного сигнала второго порогового элемента 2 берется с выхода компаратора, а прямое значение - с выхода инверто- .ра подключенного к выходу компаратора. В качестве компаратора используется микросхема 521 САЗ (возможно применение и другой, обладающей достаточным быстродействием), в качестве инвертора - микросхема

0

133ЛН1. Первый 17 и второй 18 счетчики выполнены по схеме двоично-десятичного счетчика на микросхеме 133ИЕ2. Ограничитель 6 отрицательного напряжения выполнен на основе транзистора п-р-п-типа и двух инверторов НЕ, соединенных последовательно, причем транзистор включен по схеме с общей базой. База транзистора подключена к шине низкого потенциала, сигнал ограничителя 6 отрицательного напряжения подается на эмиттер транзистора, а коллектор транзистора подключен к входу

5 первого инвертора. Выход второго элемента НЕ соединен с выходом огра- ничителя 6 отрицательного напряжения. В качестве транзистора используется один транзистор из транзис0 торной матрицы 1НТ251, а в качестве инвертора - микросхема 133ЛН1. Ограничитель 7 положительного напряжения выполнен на основе транзистора р-п-р-типа, включенного по схеме с

5 общей базой, причем база подключена к шине высокого потенциала. Входной сигнал поступает на эмиттер этого транзистора, с коллектора снимается выходной сигнал, который через резистор поступает на базу транзистора п-р-п-типа, включенного по схеме с общим эмиттером. Коллектор транзистора п-р-п-типа является выходом ограничителя 7 положительного напряжения. В качестве транзистора р-п-р-типа используется транзистор 21203А, а в качестве транзистора п-р-п-типа - один транзистор из транзисторной матрицы 1НТ251.

0

Формирователь 9 свечения нуля и формирователь 13 свечения единицы выполнены на основе одного элемента ИЛИ, двух элементов И-НЕ, причем второй и третий входы формирователя 9 свечения нуля подключены к первому и второму входам элемента ИЛИ, а выход элемента ИЛИ - к второму входу первого элемента И-НЕ. Выход первого элемента И-НЕ подключен к второму входу второго элемента И-НЕ, а первый вход формирователя 9 свечения нуля - к первым входам первого и второго элементов И-НЕ. Формирователь 13 свечения единицы имеет аналогичное соединение элементов, элемент ИЛИ и два элемента И-НЕ выполнены на микросхемах 133 серии 133ЛЛ1 и 133ЛЛЗ. Формирователь 12 свечения ненормированного уровня выполнен на основе одного элемента ИЛИ и двух элементов И-НЕ с открытым коллекторным выходом, причем второй и третий входы формирователя 12 свечения ненормированного уровня подключены к первому второму входам элемента ИЛИ. С его выхода сигнал поступает на вторые входы первого и второго элементов И-НЕ. Первый вход формирователя 12 свечения ненормированного уровня соединен с первыми входами элементов И-НЕ, первый выход подключен к выходу первого элемента И-НЕ, а второй выход - к выходу второго элемента И-НЕ. В качестве элементов ИЛИ используется микросхема 133ЛЛ1, а элементов И-НЕ - микросхема 133ЛА8.

Первый элемент цифровой задержки выполнен на основе двоичного счетчика типа 133ИЕ5 и элемента И-НЕ типа 133ЛАЗ, а также первого и второго элементов НЕ типа 133ЛН1, Входной сигнал запуска подается на первый вход обнуления счетчика, выход последнего разряда соединен с вторым входом обнуления счетчика. Выход последнего разряда счетчика, кроме того, соединен с входом первого элемента НЕ, выход которого соединен с первым входом элемента И-НЕ.

Вход второго элемента НЕ соединен fc выходом третьего разряда счетчика выход является выходом первого элемента 11 цифровой задержки, а второ вход элемента И-НЕ является его сченым входом.

Первьш 17 и второй 18 счетчики выполнены на основе двоично-десятичных счетчиков типа 1ЗЗИЕ2.Первьш 19 и второй 21 дешифраторы выполнены на микросхемах 514ИД2 и выполняют функцию преобразования двоично-десятичной информации, поступающей на их входы в семиразрядный код семисег ментного индикатора.

Первый 22 и второй 23 индикаторы выполнены на семисегментных индикаторах ЗЛС321Б и токоограничивающих резисторах типа МТЕ-0,25-100 Ом. Ге- нератор 24 синхроимпульсов выполнен на основе трех элементов И-НЕ с открытым коллекторным выходом типа 133ЛА8, причем выход первого элемента И-НЕ соединен с входом второго элемента И-НЕ выход которого сое- динен с входом третьего элемента И-Н Выход третьего элемента И-НЕ соединен с входом первого элемента И-НЕ. Между входом ,и выходом второго элемента И-НЕ подключена емкость, определяющая частоту вырабатываемых синхроимпульсов по формуле fcj,,,p- R-C, где fcMHxp - частота вырабатываемых импульсов, R - внутреннее сопротивление микросхемы, С - значение емкости внешнего конденсатора. R 3-, 3 кОм для микросхем серии 133.

I Блок 25 управления режимами вы- 1полнен на основе двух тумблеров типа МТ1-1, причем подвижный контакт

первого тумблера соединен с шиной низкого потенциала, а нормально разомкнутый контакт - с первым выходом блока 25 управления режимами, с вторым выходом которого соединен

нормально замкнутый контакт второго тумблера, а подвижньш контакт второго тумблера соединен с входом блока 25 управления режимами. Нормально разомкнутый контакт второго

,тумблера соединен с шиной низкого .потенциала. Первьш тумблер в режиме Контроль амплитуды находится в замкнутом состоянии, а в режиме Счет импульсов - в разомкнутом

состоянии. Второй тумблер в режимах Счет импульсов, Отношение частот замыкает цепь подвижный контакт - нормально замкнутый контакт, а в режимах Счет импульсов, Интервал

времени замыкает цепь подвижный контакт - нормально разомкнутьш контакт.

Второй элемент 3 цифровой задерж-, ки выполнен на основе двоичного счетчика типа 133ИЕ5 и одного элемента НЕ типа 133ЛН1, а также одного элемента И-НЕ типа 133ЛА4, причем вход запуска второго элемента 30. цифровой задержки является входом обнуления счетчика. Счетный вход, на который поступают синхроимпульсы, является счетным входом счетчика и соединен также с первым входом элемента И-НЕ. Выход второго разряда счетчика соединен с вторым входом элемента И-НЕ, а выход третьего разряда - с третьим входом элемента И-НЕ, выход которого является первым выходом второго элемента 30 цифровой задержки, с вторым выходом которого соединен выход элемента НЕ. Вход элемента НЕ соединен с выходом четвертого разряда счетчика.

17

Элемент И 31 выполнен на основе элемента И-НЕ типа 133ЛА4 и элемента НЕ типа 133ЛН1, причем первый вход элемента И-НЕ соединен с пер- вым входом элемента И 31, второй вход - с вторым входом элемента И 31 а третий вход - с первым входом RC-цепочки, второй вход которой соединен с шиной низкого потенциала. Параметры интегрирующей RC-цепочки выбирают из условия t. 1,5 t.ppeKft где - время интегрирования, равное RC, ( задержка в переключениях первого и второго пороговых элементов.

В качестве резистора используется резистор МТЕ-0,25-12 кОм+10% конденсатор типа К10-23-220 пФ.

В качестве первого элемента РЩИЮ используется элемент типа 133ЛА4, второго элемента ИЛИ 16 - 133ЛАЗ, третьего элемента ИЛИ 20 - 133ЛЛ1, четвертого элемента ИЛИ 26 - ПЗЛАЗ элемента НЕ 15.- 133ЛН1, первого элемента И-НЕ 14-133ЛАЗ, второго эле мента НЕ 29 - 133ЛАЗ. Период генератора 24 синхроимпу1Й сов, а также количество- разрядов элементов 11 и 30 выбирают исходя из времени, кото- 1 рое необходимо для устойчивого наблю дения символов на индикаторах 22 и 23, т.е.

период Т генератора ,

Д Чс-Блюлени. --время индикации

цифры i п - количество разрядов задержек

тогда Т - 0,125

8

с.

Таким образом, если время индикации цифры выбирают равным 1с, а количество разрядов цифры равным 4, то получают требуемый период импульсов генератора 24 синхроимпульсов равный 0., 125 с.

Формула изобретения

Логический пробник, содержащий первый пороговый элемент, первьш, в.торой, третий, четвертый триггеры, второй пороговьм элемент, первьм счетчик, первый дешифратор, первый и второй индикаторы, элемент И, блок управления режимами, причем выходы первого счетчика соединены поразрядно с первыми входами первого дешифратора, выходы которого соединены с соответствующими входами первого ин25 зо

0508518

дикатора, входы первого и второго пороговых элементов соединены с входом Сигнал, отличающий- с я тем, что, с целью расширения

5 функциональных возможностей, в него введены пятый и шестой триггеры, первый и второй элементы цифровой задержки, второй дешифратор, первый, второй, третий, и четвертый элемен10 ты ИЛИ, второй счетчик, генератор синхроимпульсов, элемент НЕ, первьш и второй элементы И-НЕ, ограничитель отрицательного напряжения, ограничитель положительного напряжения,

15 формирователь свечения ненормированного уровня, формирователь свечения единицы, формирователь свечения нуля, причем первый вход элемента И сЬединен с инверсным выходом второго порогового элемента, второй вход - с инверсным выходом .первого порого20

вого элемента, а выход

с входом

синхронизации третьего триггера, информационный вход которого соединен с шиной низкого потенциала, пер

элемента ШШ соединены с прямыми выходами соответственно первого, второго и третьего триггеров, а выход - с входом запуска первого элемента цифровой задержки, счетный вход которого с оединен с выходом генератора синхроимпульсов и со счетным входом второго элемента цифровой задержки, вход запуска которого соединен с первыми входами второго элемента И-НЕ и четвертого элемента ШШ и с выходом шестого триггера, выход первого элемента цифровой задержки соединен с входами установки в 1 первого, второго и третьего триггеров, инверсные выходы которых соединены соответственно с первыми входами формирователя свечения единицы, формирователя свечения нуля, формирователя свечения ненормированного уровня, входы синхронизации первого и второго триггеров .соединены соответственно с прямыми выходами первого и второго пороговых элементов, а информационные входы - с шиной низкого потенциала, вход Сигнал соединен с входами ограничителя отрицательного напряжения и ограничителя положительного напряжения, выход первого из которых соединен с первым входом второго индикатора, второй вход которого соединен с выходом второго дешифратора, а

19

третий вход - с инверсным выходом четвертого триггера, вход установки в 1 которого соединен с выходом ограничителя положительного напряжения,.а вход обнуления - с инверсным выходом первого триггера, вторые входы формирователя свечения единицы и: формирователя .свечения нуля соединены соответственно с прямыми выходами первого и второго пороговых элементов, а третьи входы - с выходо элемента НЕ и с первым входом третьего элемента ИЛИ, второй вход которого соединен с первым выходом второго счетчика, а выход - с первым входом второго дешифратора, вторые входы которого соединены с вторыми выходами второго счетчика, счетньй вход которого соединен с выходом последую- |щего разряда первого счетчика, входы обнуления первого и второго счетчико соединены с выходом второго элемента ИЛИ, первый вход которого соединен с первым выходом блока управления режимами и с входом элемента НЕ, а второй вход - с первым выходом второго элемента цифровой задержки, второй выход которого соединен с первыми входами пятого и шестого тригге- ров, второй вход шестого триггера

0508520

соединен с шиной низкого потенциала,а первый вход - с инверсным выходом пятого триггера и входом блока управления релшмами, второй выход ко- 5 торого соединен с вторым входом пятого триггера, третий и четвертый входы которого соединены соответственно с выходами второго элемента И-НЕ и четвертого элемента ИЛИ, )0 вто рые входы которых соединены с входами Второй запуск и Первый

запуск соответственно, прямой выход пятого триггера соединен с пер- BbLM входом первого элемента И-НЕ,

второй вход которого соединен с инверсным выходом первого порогового элемента, а выход - со счетным входом первого счетчика, второй и третий выходы формирователя свечения ненормированного уровня соединены соответственно с выходом элемента И и с выходом элемента НЕ, а первый и второй выходы - с вторым входом первого индикатора и с выходом ограничителя отрицательного напряжения соответственно,вьсходы формирователя свечения единицы и формирователя свечения нуля соединены соответственно с третьим входом второго дешифратора и с вторым входом первого дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический пробник | 1986 |

|

SU1386946A1 |

| Логический зонд | 1978 |

|

SU951201A1 |

| МНОГОУРОВНЕВЫЙ СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ДЛИТЕЛЬНОСТИ ВЫБРОСОВ И ПРОВАЛОВ НАПРЯЖЕНИЯ | 1991 |

|

RU2054195C1 |

| Устройство для контроля логических узлов | 1980 |

|

SU868764A1 |

| Устройство записи и воспроизведения двоичной информации на магнитной ленте | 1983 |

|

SU1117689A2 |

| Шкальный индикатор | 1984 |

|

SU1276999A1 |

| Устройство для психофизиологических исследований | 1990 |

|

SU1780717A1 |

| Устройство для моделирования каналов передачи дискретной информации | 1982 |

|

SU1049915A1 |

| Устройство для перезапуска и контроля электропитания микроЭВМ | 1989 |

|

SU1797122A1 |

| Голографическое постоянное запоминающее устройство | 1990 |

|

SU1725258A1 |

Изобретение относится к радиотехнике, в частности к устройствам для контроля импульсных сигналов. Изобретение может быть использовано для нахождения неисправностей и проверки функционирования электронных устройств, выполненных на логических микросхемах. Цель изобретения - расширение функциональных возможностей логического пробника путем определения коэффициента деления и количества импульсов в пачке. Это достигается тем, что в известный логический пробник, вьшолненный на логических элементах и четырех триггерах, содержащий индикаторы,дешифратор и счетчик, дополнительно введены два триггера, два элемента цифровой задержки, второй дешифратор, второй счетчик, логические элементы ИЛИ, НЕ, И-НЕ, ограничители положительного и отрицательного напряжений и формирователи свечения единицы, нуля, ненормированного уровня. При этом соответственно изменены и дополнены функциональные связи устройства. Работа устройства приводится в описании изобретения и поясняется временными диаграммами и структурной схемой. 2 ил. (Л §

nn.

L

ri

fLJl

пг 1гтги

.к/е/«гс га е емеле

J7ffSi/ eC 2ff

-i eaff/ if S7

{//уг А ozf/yffc/r

го

TJ S SQasc pssst. ,,„

4

f/yjfff

jf

п

fLJl

А J7ffSi/

{//уг А ozf/yffc/rff го

ssst. ,,„

asc pssst.

п

4

f/yjfff

н

17

LJ

J

Фс/г.2

Составитель Н.Помякшева Редактор А.Огар Техред А.АчКорректор Л.Патай

Заказ 8524/48 Тираж 747Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Филиал ПГШ Патент, г,Ужгород, ул.Проектная, 4

и

| Логический зонд | 1976 |

|

SU612412A1 |

| Н ,03 К 19/00, 1978 | |||

| Йнформационньш листок / ВИМИ, № 79-1883, сер | |||

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-01-15—Публикация

1984-08-30—Подача