1138

Изобретение относится к контрольно-измерительной технике и может быть использовано при контроле импульсных сигналов.

Цель изобретения - расширение функциональных возможностей путем контроля информации в последовательном и параллельном коде, поступающей на соответствующие входы устройства.

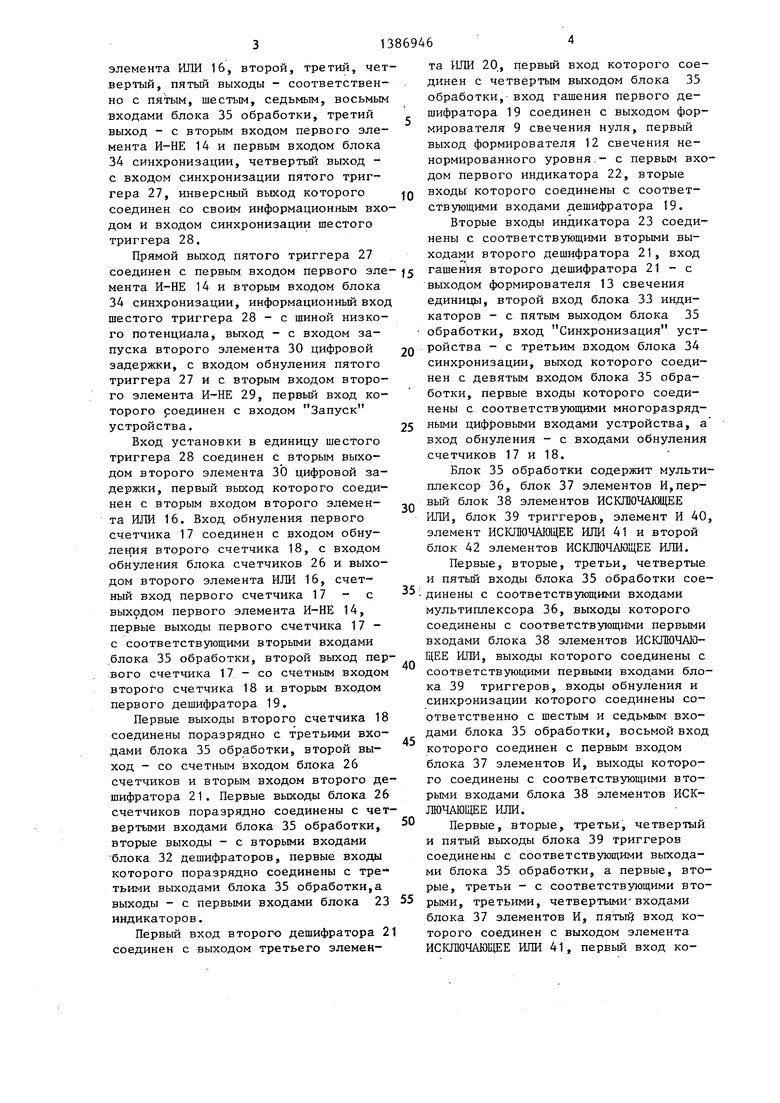

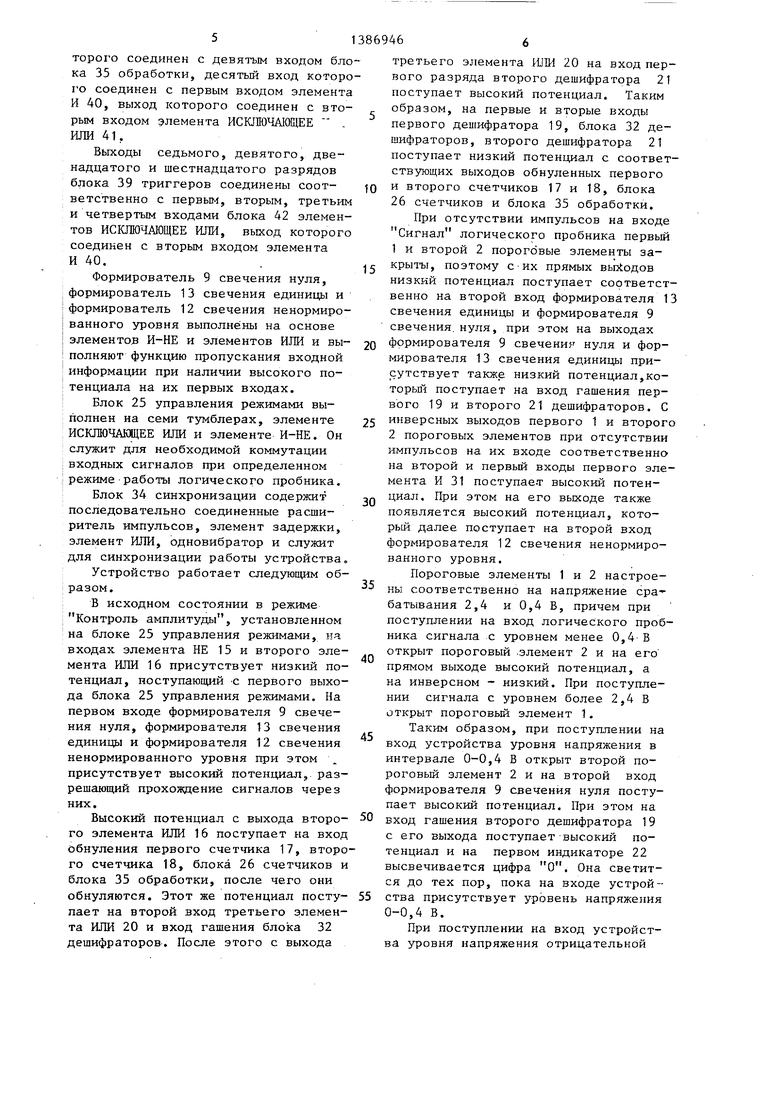

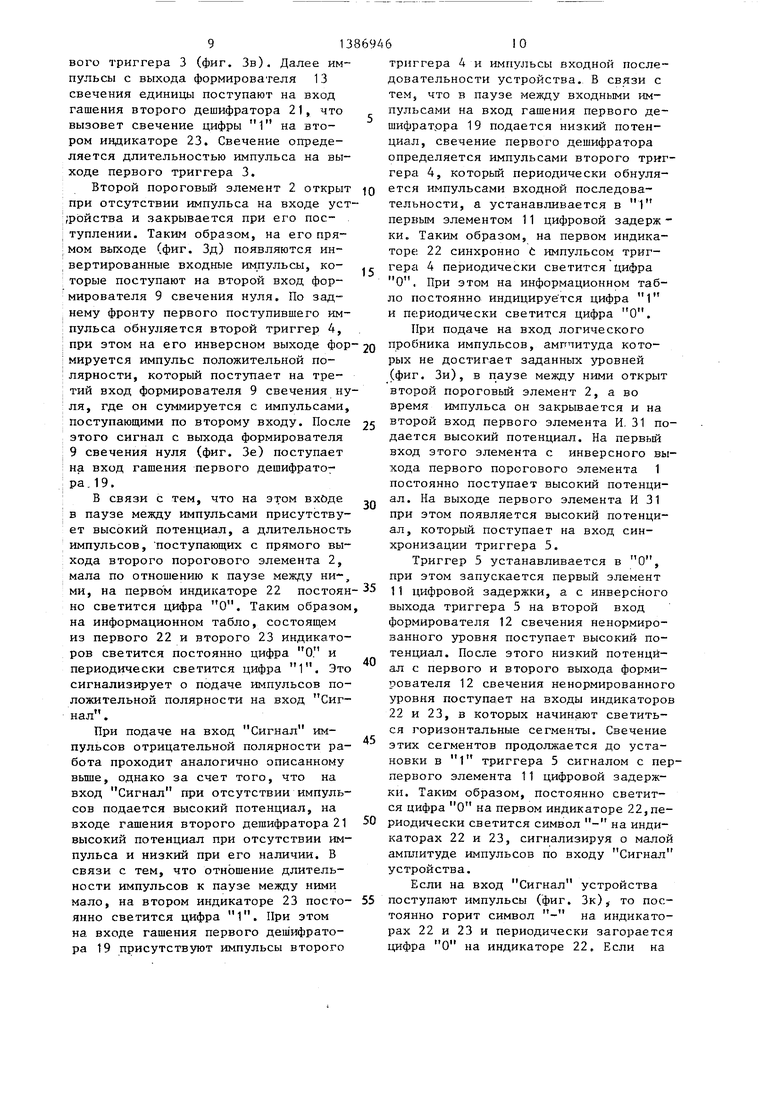

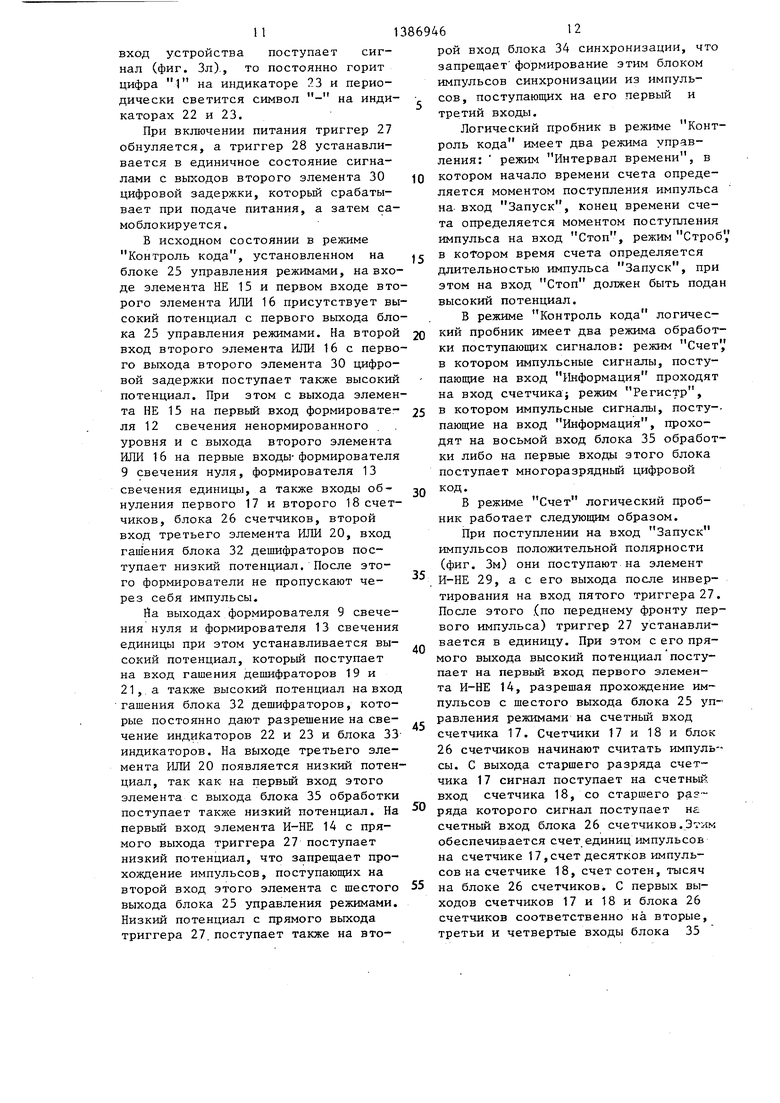

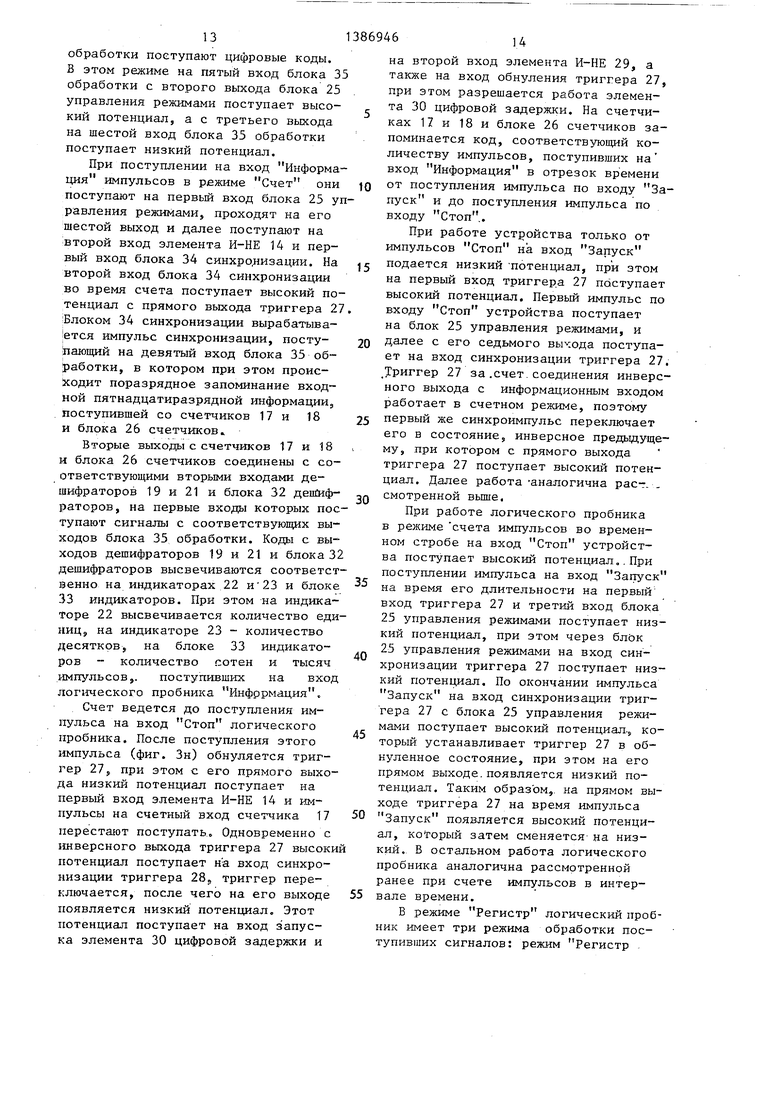

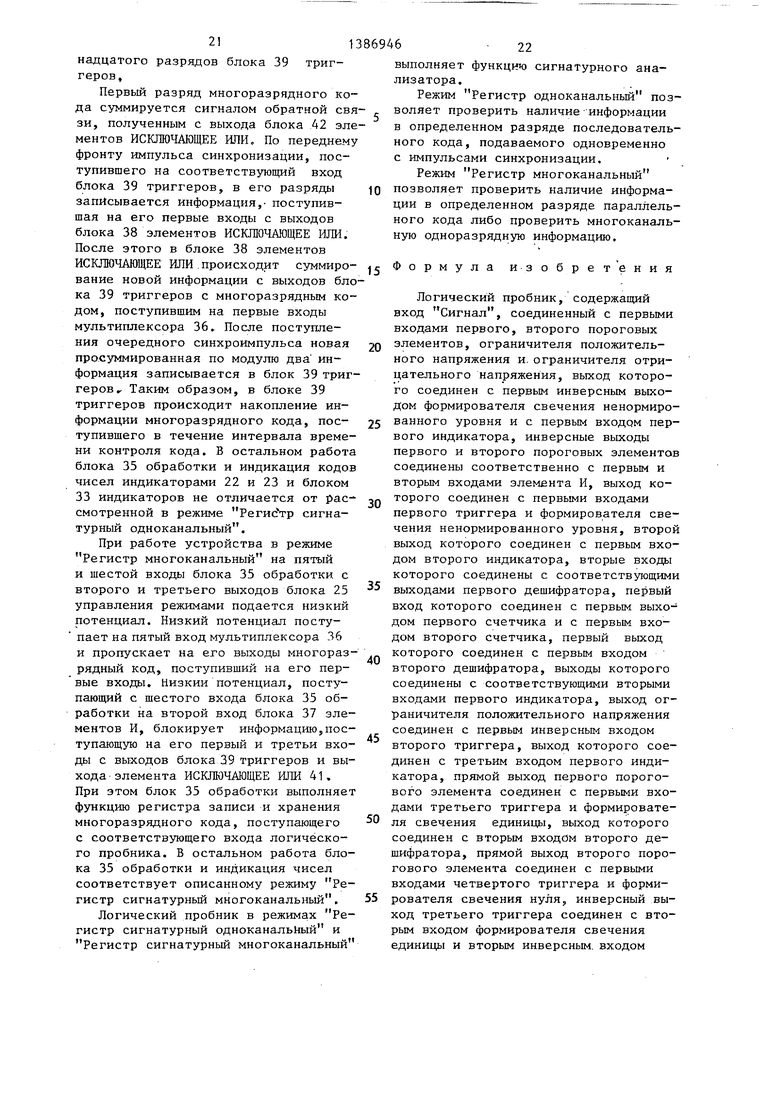

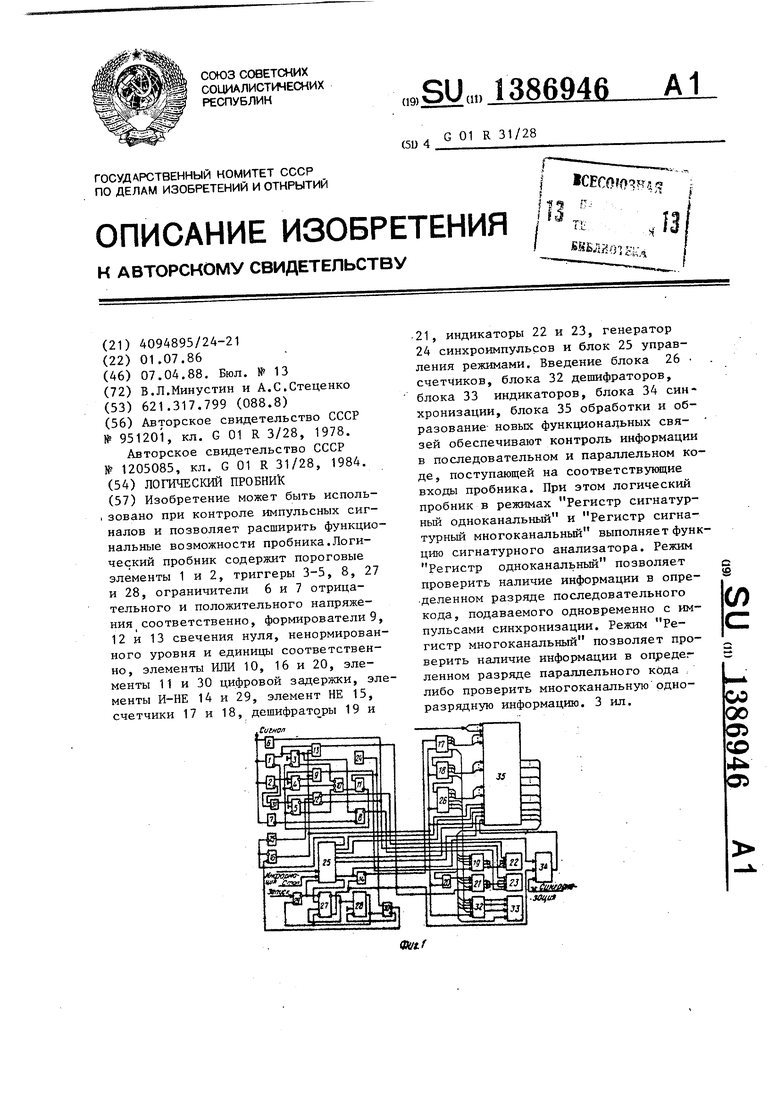

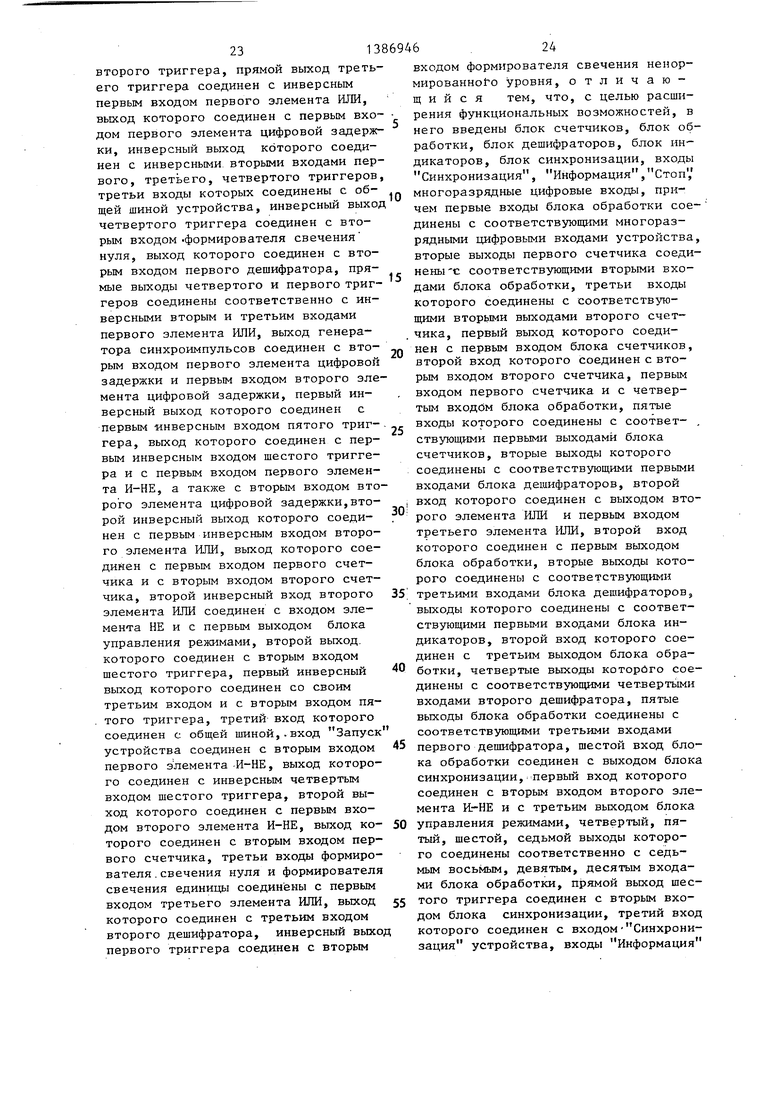

На фиг. 1 представлена функцио- :нальная схема устройства; на фиг.2 - Iфункциональная схема блока обработки на фиг. 3 временные диаграммы.

Устройство содержит пороговые эле- :менты 1 и 2, первый 3, второй 4 и I третий 5 триггеры, ограничители отрицательного 6 и положительного 7 напряжения, четвертый триггер 8, фор

|мирователь 9 свечения нуля, первый 1элемент ИЛИ 10, первьй элемент 11 1цифровой задержки, формирователь 12 Свечения ненормированного уровня, |формирователь 13 свечения единицы, ервый элемен - И-НЕ 14, элемент НЕ 115, второй элемент ШШ 16, первый рчетчик 17, второй счетчик 18,первый Дешифратор 19, третий элемент ИЛИ 20 бторой дешифратор 21, первый 22 и второй 23 индикаторы, генератор - 24 Синхроимпульсов, блок 25 управления 1)ежимами, блок 26 счетчиков, пятый 27 и шестой 28 триггеры, второй эле- И-НЕ 29, второй элемент 30 цифровой задержки, первый элемент И 31, блок 32 дешифраторов, блок 33 инди- KJaторов, блок 34 синхронизации, блок 3|5 обработки, а также входы Сигнал {информация, Стоп, Синхронизация многоразрядный цифровой вход.

Вход первого порогового элемента 1 соединен с входом Сигнал устройства, прямой выход первого порогового элемента 1 - с входом синхронизации первого триггера 3 и вторым входом формирователя 13 свечения единицы, инверсный выход первого порогового элемента 1 - с вторым входом эле- М€шта И 31, вход второго порогового элемента 2-е входом Сигнал устройства, прямой выход - с входом син хронизации второго триггера 4 и вто- рьлм входом формирователя 9 свечения нуля, инверсный выход - с первым входом элемента И 31, вход синхронизации третьего триггера 5 - с выходом элемента И 31 и с вторым входом формирователя 12 свечения ненормированного уровня.

Информационн1 е входы первого 3, второго 4 и третьего 5 триггеров соединены с шиной низкого потенциала, входы установки в единицу этих

триггеров соединены с выходом первого элемента 11 цифровой задержки,инверсный выход первого триггера 3 со е- динен с третьим входом формирователя 13 свечения единицы, а прямой выход- с первым входом первого элемента ИЛИ 10, инверсный выход второго триггера

4соединен с трет,ьим входом формирователя 9 свечения нуля, а прямой выход - с вторым- входом первого элемента ИЛИ 10.

Инверсный выход третьего триггера

5соединен с третьим входом формирователя 12 свечения ненормированного

5

0

5

0

0

5

5

0 уровня, а прямой выход - с третьим входом первого элемента ШШ 10,вход .запуска первог.о элемента 11 цифровой задержки соединен с выходом первого элемента ИЛИ 10, а счетный вход - с выходом генератора 24 синхроимпульсов и счетным входом второго элемента 30 цифровой задержки, первые входы . формирователя 13 свечения единицы, формирователя 9 свачения нуля соединены., с выходом второго элемента ИЛИ 16, вторым входом третьего элемента ИЛИ 20 и третьим входом блока 32 дешифраторов.

Первьй вход формирователя 12 свечения ненормированного уровня соединен с выходом элемента НЕ 15, входьь ограничителя 6 отрицательного напря- жения и ограничителя 7 положительного напряжения - с входом Сигнал устройства, второй выход формирователя 12 свечения ненормированного уровня- с выходом ограничителя 6 отрицательного напряжения и с первым входом второго индикатора 23, вход установки в единицу четвертого триггера 8 - с инверсным выходом ограничителя 7 положительного напряжения, вход обнуления - с инверсным выходом первого триггера 3, а выход - с третьим входом второго индикатора 23.

Первый вход блока 25 управления режимами соединен с входом Информация устройства, второй вход - с входом Стоп устройства, третий вход - с выходом второго элемента И-НЕ 29 и входом установки в единицу пятого триггера 27, первый выход блока 25 управления режимами - с входом элемента НЕ 15 и первым входом второго

элемента ИЛИ 16, второй, третий, четвертый, пятый выходы - соответственно с пятым, шестым, седьмым, восьмым входами блока 35 обработки, третий выход - с вторым входом первого элемента И-НЕ 14 и первым входом блока 34 синхронизации, четвертьй выход - с входом синхронизации пятого триггера 27, инверсный выход которого соединен со своим информационным входом и входом синхронизации шестого триггера 28,

Прямой выход пятого триггера 27 соединен с первым входом первого эле мента И-НЕ 14 и вторым входом блока 34 синхронизации, информационный вход шестого триггера 28 - с шиной низкого потенциала, выход - с входом запуска второго элемента 30 цифровой задержки, с входом обнуления пятого триггера 27 и с вторым входом второго элемента И-НЕ 29, первый вход которого соединен с входом Запуск устройства.

Вход установки в единицу шестого триггера 28 соединен с вторым выходом второго элемента 30 цифровой задержки, первый выход которого соединен с вторым входом второго элемен- та ИЛИ 16. Вход обнуления первого счетчика 17 соединен с входом обнуления второго счетчика 18, с входом обнуления блока счетчиков 26 и выходом второго элемента ИЛИ 16, счетный вход первого счетчика 17 - с выходом первого элемента И-НЕ 14, первые выходы первого счетчика 17 - с соответствуюш;ими вторыми входами блока 35 обработки, второй выход первого счетчика 17 - со счетным входом второго счетчика 18 и вторым входом первого дешифратора 19.

Первые выходы второго счетчика 18 соединены поразрядно с третьими входами блока 35 обработки, второй выход - со счетным входом блока 26 счетчиков и вторым входом второго дешифратора 21. Первые выходы блока 26 счетчиков поразрядно соединены с четвертыми входами блока 35 обработки, вторые выходы - с вторыми входами блока 32 дешифраторов, первые входы которого поразрядно соединены с третьими выходами блока 35 обработки,а выходы - с первыми входами блока 23 индикаторов.

Первый вход второго дешифратора 2 соединен с выходом третьего элемен

Q

5 0 5

Q

5

5

0

5

та ИЛИ 20, цервый вход которого соединен с четвертым выходом блока 35 обработки,-вход гашения первого дешифратора 19 соединен с выходом формирователя 9 свечения нуля, первый выход формирователя 12 свечения ненормированного уровня.- с первым входом первого индикатора 22, вторые входы которого соединены с соответствующими входами дешифратора 19.

Вторые входы индикатора 23 соединены с соответствующими вторыми выходами второго дешифратора 21, вход гашения второго дешифратора 21 - с выходом формирователя 13 свечения единицы, второй вход блока 33 индикаторов - с пятым выходом блока 35 обработки, вход Синхронизация устройства - с третьим входом блока 34 синхронизации, выход которого соединен с девятым входом блока 35 обработки, первые входы которого соединены с соответствующими многоразрядными цифровыми входами устройства, а вход обнуления - с входами обнуления счетчиков 17 и 18.

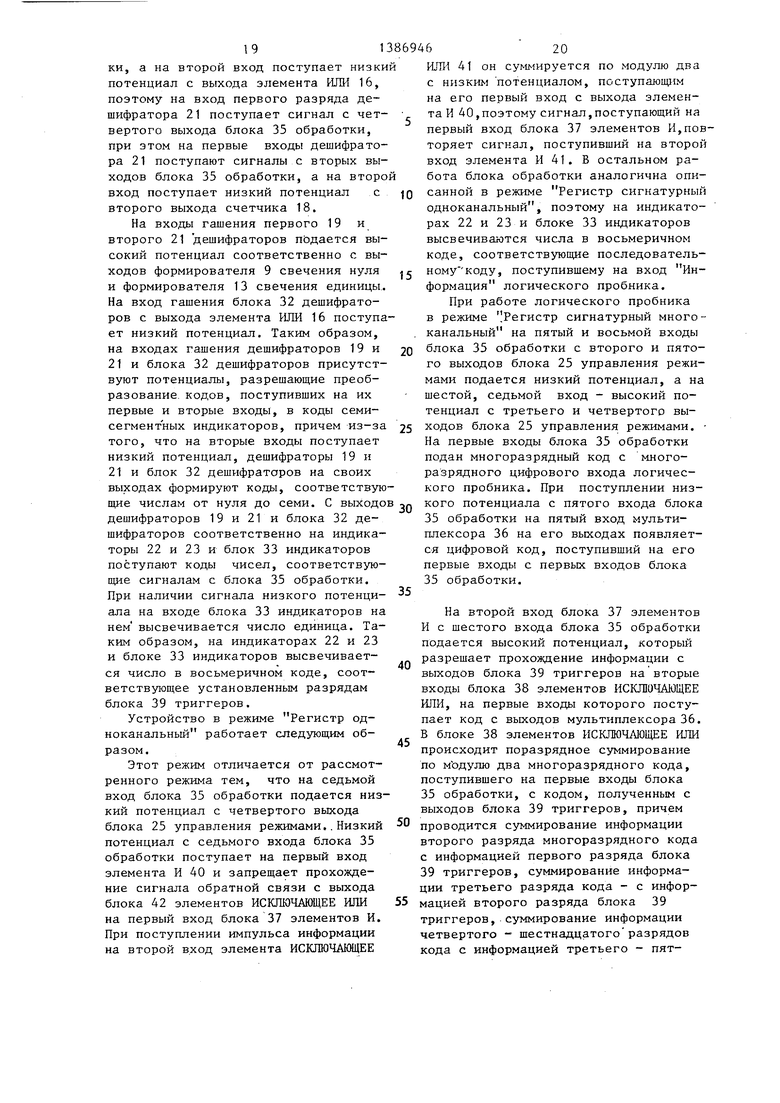

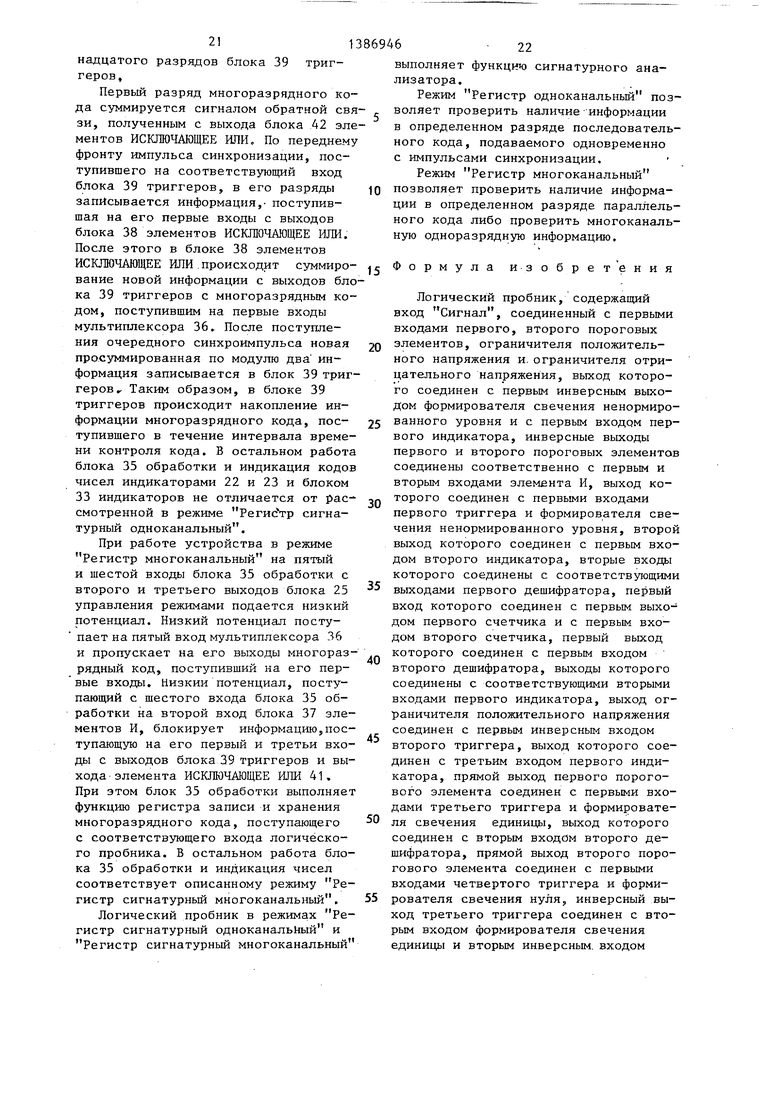

Блок 35 обработки содержит мультиплексор 36, блок 37 элементов И,первый блок 38 элементов ИСКЛЮЧАЩЕЕ ИЛИ, блок 39 триггеров, элемент И 40, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41 и второй блок 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Первые, вторые, третьи, четвертые и пятый входы блока 35 обработки сое- динены с соответствующими входами мультиплексора 36, выходы которого соединены с соответствующими первыми входами блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выходы которого соединены с соответствующими первыми входами блока 39 триггеров, входы обнуления и синхронизации которого соединены соответственно с шестым и седьмым входами блока 35 обработки, восьмой вход которого соединен с первьм входом блока 37 элементов И, выходы которого соединены с соответствующими вторыми входами блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Первые, вторые, третьи, четвертый и пятый выходы блока 39 триггеров соединены с соответствующими выходами блока 35 обработки, а первые, вторые, третьи - с соответствующими вторыми, третьими, четвертыми входами блока 37 элементов И, пятый вход которого соединен с выходом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, первый вход ко5

Toporo соединен с девятым входом блока 35 обработки, десятый вход которо I O соединен с первым входом элемента И 40, выход которого соединен с вторым входом элемента ИСКЛЮЧАЮЩЕЕ . ИЛИ 41.

Выходы седьмого, девятого, двенадцатого и шестнадцатого разрядов блока 39 триггеров соединены соответственно с первым, вторым, третьим и четвертым входами блока 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, выход которого соединен с вторым входом элемента И 40.

Формирователь 9 свечения нуля, формирователь 13 свечения единицы и формирователь 12 свечения ненормированного уровня выполнены на основе элементов И-НЕ и элементов ИЛИ и выполняют функцию пропускания входной информации при наличии высокого потенциала на их первых входах.

Блок 25 управления режимами выполнен на семи тумблерах, элементе ИСКЛЮЧАЩЕЕ ИЛИ и элементе И-НЕ. Он служит для необходимой коммутации входных сигналов при определенном ;режиме работы логического пробника.

Блок 34 синхронизации содержит последовательно соединенные расширитель импульсов, элемент задержки, элемент ИЛИ, одновибратор и служит для синхронизации работы устройства.

Устройство работает следуюпщм образом.

В исходном состоянии в режиме Контроль амплитуды, установленном на блоке 25 управления режимами, ня входах элемента НЕ 15 и второго элемента ИЛИ 16 присутствует низкий потенциал, поступающий -с первого выхода блока 25 управления режимами. На первом входе формирователя 9 свечения нуля, формирователя 13 свечения единицы и формирователя 12 свечения ненормированного уровня при этом . присутствует высокий потенциал, разрешающий прохождение сигналов через них.

Высокий потенциал с выхода второго элемента ИЛИ 16 поступает на вход обнуления первого счетчика 17, второ го счетчика 18, блока 26 счетчиков и блока 35 обработки, после чего они обнуляются. Этот же потенциал поступает на второй вход третьего элемента ИЛИ 20 и вход гашения блока 32 дешифраторов. После этого с выхода

869466

третьего элемента ШШ 20 на вход первого разряда второго дешифратора 21 поступает высокий потенциал. Таким образом, на первые и вторые входы первого дешифратора 19, блока 32 дешифраторов, второго дешифратора 21 поступает низкий потенциал с соответствующих выходов обнуленных первого 10 и второго счетчиков 17 и 18, блока 26 счетчиков и блока 35 обработки.

При отсутствии импульсов на входе Сигнал логического пробника первьм

1и второй 2 пороговые элементы за- 2 кры1Ъ1, поэтому с их прямых выводов

низкий потенциал поступает соответственно на второй вход формирователя 13 свечения единицы и формирователя 9 свечения, нуля, при этом на выходах

20 формирователя 9 свечения нуля и формирователя 13 свечения единицы присутствует также низкий потенциал,ко- торьп поступает на вход гашения первого 19 и второго 21 дешифраторов. С

25 инверсных выходов первого 1 и второго

2пороговых элементов при отсутствии импульсов на их входе соответственно на второй и первый входы первого элемента И 31 поступае-т высокий потен

циал. При этом на его выходе также появляется высокий потенциал, который далее поступает на второй вход формирователя 12 свечения ненормированного уровня.

Пороговые элементы 1 и 2 настроены соответственно на напряжение срабатывания 2,4 и 0,4 В, причем при поступлении на вход логического пробника сигнала с уровнем менее 0,4-В открыт пороговый .элемент 2 и на его

прямом выходе высокий потенциал, а на инверсном - низкий. При поступлении сигнала с уровнем более 2,4 В открыт пороговьй элемент 1.

Таким образом, при поступлении на вход устройства уровня напряжения в интервале 0-0,4 В открыт второй пороговый элемент 2 и на второй вход формирователя 9 свечения нуля поступает высокий потенциал. При этом на

вход гашения второго дешифратора 19 с его выхода поступает-высокий потенциал и на первом индикаторе 22 высвечивается цифра О. Она светится до тех пор, пока на входе устройства присутствует уровень напряжения 0-0,4 В.

При поступлении на вход устройства уровня напряжения отрицательной

полярности срабатывает ограничитель 6 отрицательного напряжения и ограничивает его на уровне - 0,7 В, а на его выходе появляется низкий потен- циал. Кроме того, открывается второй пороговый элемент 2. Одновременно с выхода ограничителя 6 отрицательного напряжения на вход второго индикатор 23 поступает низкий потенциал, что вызьшает свечение символа О.

При поступлении на вход устройства напряжения более 2,4 В открьшает- ся первьй пороговьм элемент 1, с прямого выхода которого высокий по- тенциал поступает на второй вход формирователя 13 свечения единицы, а с выхода формирователя 13 свечения единицы на вход гашения второго дешифратора 21 поступает высокий потен- циал, который разрешает прохождение кода единицы с его выхода на второй индикатор 23, при этом на втором индикаторе 23 начинает светиться цифра 1. Она светится до тех пор, пока на входе Сигнал присутствует уровень напряжения более 2,4 В.

Если входное напряжение устройства, превьппает уровень 4,5 В, срабатывает ограничитель 7 положительного напряжения и ограничивает входное напряжение на входе пороговых элементов 1 и 2 на уровне 5 В. При этом на выходе ограничителя 7 положительного напряжения появляется низкий потенциал, который поступает на вход ус- тановки в единицу четвертого триггера 8, после срабатывания которого с его выхода на третий вход второго . индикатора 23 поступает низкий потенциал. На втором индикаторе 23- при этом светятся цифра 1 и децимальная точка, сигнализируя, что на вход Сигнал поступает сигнал, превышающий по уровню логическую единицу.

Если уровень напряжения, поступающий на вход Сигнал, лежит в пределах 0,4-2,4 В, то оба пороговых элемента 1 и 2 закрыты, что анало- гично отсутствию напряжения на входе логического пробника. При этом на первом 22 и втором 23 индикаторах индицируется символ -.

Если на вход Сигнал подаются импульсные сигналы положительной полярности (фиг. За), причем длитель- ность импульсов значительно меньше паузы между импульсами, то на прямом выходе первого порогового элемен

5 0 5

Q

0

5

та 1 (фиг. Зб) появляются импульсы положительной полярности, которые поступают на вход синхронизации первого триггера 3 и второй вход формирователя 13 свечения единицы. При этом по переднему фронту первого импульса срабатывает триггер 3 и на его инверсном выходе (фиг. Зв) появляется высокий потенциал, которьш поступает на третий вход формирователя 13 свечения единицы.

Одновременно с прямого выхода первого триггера 3 низкий потенциал поступает на первый вход первого элемента ИЛИ 10, после чего с выхода этого элемента сигнал высокого потенциала поступает на вход запуска первого элемента 11 цифровой задержки, который выполнен на двоичном счетчике, а входной сигнал поступает на первый вход его обнуления, второй вход обнуления соединен с выходом последнего разряда этого счетчика. Таким . образом,- как только входной сигнал обнуляет счетчик за счет действия обратной связи, его дальнейшее наличие на входе запуска не обязательно.

Первый элемент 11 цифровой задержки начинает отсчитьшать синхроимпульсы генератора 24 синхроимпульсов.После поступления определенного количества импульсов на счетньш вход первого элемента 11 цифровой задержки на его выходе появляется низкий потенциал, который поступает на входы установки в единицу триггеров 3-5.После этого триггер 3 сбрасывается в исходное состояние, однако первый элемент 11 цифровой задержки не устанавливается в исходное состояние, а продолжает отсчитывать счетные импульсы до появления на выходе старшего разряда счетчика высокого потенциала, разрешающего повторный запуск первого элемента 11 цифровой задержки.Далее описанньй вьш1е процесс повторяется вновь.

Таким образом, триггер 3 периодически запускается импульсами с выхода первого порогового элемента 1, а сбрасывается выходным импульсом пер-- вого элемента 11 цифровой задержки. При этом на выходе формирователя 13 свечения единицы (фиг. Зг) появляются импульсы положительной полярности, которые получаются из наложения входной импульсной последовательности (фиг. За) и импульсов на выходе первого триггера 3 (фиг. Зв). Далее импульсы с выхода формирователя 13 свечения единицы поступают на вход гашения второго дешифратора 21, что вызовет свечение цифры 1 на втором индикаторе 23. Свечение опредеяется длительностью импульса на выоде первого триггера 3.

Второй пороговый элемент 2 открыт Q при отсутствии импульса на входе уст- рЬйства и закрывается при его пос- туплении. Таким образом, на его пря- ом выходе (фиг. Зд) появляются ин- вертированные входные импульсы, ко- ,,. торые поступают на второй вход форирователя 9 свечения нуля. По заднему фронту первого поступившего импульса обнуляется второй триггер А, при этом на его инверсном выходе фор- 20 мируется импульс положительной полярности, который поступает на третий вход формирователя 9 свечения нуля, где он суммируется с импульсами, поступающими по второму входу. После 25 этого сигнал с выхода формирователя 9 свечения нуля (фиг. Зе) поступает на вход гашения первого дешифратора . 1 9 .

В связи с тем, что на этом вхОде « в паузе между импульсами присутствует высокий потенциал, а длительность импульсов, поступающих с прямого выхода второго порогового элемента 2, мала по отношению к паузе между ни-, ми, на первом индикаторе 22 постоян- 35 но светится цифра О. Таким образом, на информационном табло, состоящем из первого 22 и второго 23 индикаторов светится постоянно цифра 0 и периодически светится цифра 1. Это сигнализирует о подаче импульсов положительной полярности на вход Сиг40

нал,

При подаче на вход Сигнал им

пульсов отрицательной полярности работа проходит аналогично описанному вьше, однако за счет того, что на вход Сигнал при отсутствии импульсов подается высокий потенциал, на входе гашения второго дешифратора 21 высокий потенциал при отсутствии импульса и низкий при его наличии. В связи с тем, что отношение длительности импульсов к паузе между ними мало, на втором индикаторе 23 посто- янно светится цифра 1. При этом на входе гашения первого дешифратора 19 присутствуют импульсы второго

. 0 5

« 5

0

5

0 5

триггера 4 и импульсы входной последовательности устройства. В связи с тем5 что в паузе между входными импульсами на вход гашения первого де- шифратрра 19 подается низкий потенциал, свечение первого дешифратора определяется импульсами второго триггера 4, который периодически обнуляется импульсами входной последовательности, а устанавливается в 1 первым элементом 11 цифровой задерж - ки. Таким образом, на первом индикаторе 22 синхронно t импульсом триггера 4 периодически светится цифра О, При этом на информационном табло постоянно индицируе тся цифра 1 и периодически светится цифра О.

При подаче на вход логического пробника импульсов, амтитуда которых не достигает заданных уровней (фиг. Зи), в паузе между ними открыт второй пороговый элемент 2, а во бремя импульса он закрывается и на второй вход первого элемента И. 31 подается высокий потенциал. На первый вход этого элемента с инверсного выхода первого порогового элемента 1 постоянно поступает высокий потенциал. На выходе первого элемента И 31 при этом появляется высокий потенциал, который поступает на вход синхронизации триггера 5.

Триггер 5 устанавливается в О, при этом запускается первый элемент 11 цифровой задержки, а с инверсного выхода триггера 5 на второй вход формирователя 12 свечения ненормированного уровня поступает высокий потенциал. После этого низкий потенциал с первого и второго выхода формирователя 12 свечения ненормированного уровня поступает на входы индикаторов 22 и 22, в которых начинают светиться горизонтальные сегменты. Свечение этих сегментов продолжается до установки в 1 триггера 5 сигналом с пер- первого элемента 11 цифровой задержки. Таким образом, постоянно светится цифра О на первом индикаторе 22,периодически светится символ - на индикаторах 22 и 23, сигнализируя о малой амплитуде импульсов по входу Сигнал устройства.

Если на вход Сигнал устройства поступают импульсы (фиг. Зк), то постоянно горит символ - на индикаторах 22 и 23 и периодически загорается хщфра О на индикаторе 22. Если на

и1386946

вход устройства поступает сигнал (фиг. 3л)., то постоянно горит цифра 1 на индикаторе 23 и периодически светится символ - на индикаторах 22 и 23.

При включении питания триггер 27 обнуляется, а триггер 28 устанавливается в единичное состояние сигналами с выходов второго элемента 30 цифровой задержки, который срабатывает при подаче питания, а затем самоблокируется,

В исходном состоянии в режиме Контроль кода, установленном на блоке 25 управления режимами, на входе элемента НЕ 15 и первом входе второго элемента ИЛИ 16 присутствует высокий потенциал с первого выхода блока 25 управления режимами. На второй вход второго элемента ИЛИ 16 с первого выхода второго элемента 30 цифровой задержки поступает также высокий потенциал. При этом с выхода элемента НЕ 15 на первый вход формирователя 12 свечения ненормированного уровня и с выхода второго элемента ИЛИ 16 на первые входы- формирователя 9 свечения нуля, формирователя 13 свечения единицы, а также входы обнуления первого 17 и второго 18 счетчиков, блока 26 счетчиков, второй ход третьего элемента ИЛИ 20, вход гашения блока 32 дешифраторов поступает низкий потенциал. После этого формирователи не пропускают через себя импульсы.

Йа выходах формирователя 9 свечения нуля и формирователя 13 свечения единицы при этом устанавливается высокий потенциал, который поступает а вход гашения дешифраторов 19 и 1, а также высокий потенциал на вход гашения блока 32 дешифраторов, котоые постоянно дают разрешение на свеение индикаторов 22 к 23 к блока 33 ндикаторов. На выходе третьего элеента ИЛИ 20 появляется низкий потениал, так как на первьй вход этого лемента с выхода блока 35 обработки оступает также низкий потенциал. На ервый вход элемента И-НЕ 14 с пряого выхода триггера 27 поступает изкий потенциал, что запрещает проождение импульсов, поступающих на торой вход этого элемента с шестого ыхода блока 25 управления режимами. изкий потенциал с прямого выхода риггера 27. поступает также на второза им со тр

ро ле 10 ко ля на та им J5 в дл эт вы

20 ки ки в па на 25 в па дя ки по код

ни

им (фи ИтирПо во вае мог пае та пул рав сче 26 сы. чик вхо ряд сче обе на сов 55 на ход сче тре

30

35

40

45

50

12

рой вход блока 34 синхронизации, что запрещает формирование этим блоком импульсов синхронизации из импульсов, поступающих на его первый и третий входы.

Логический пробник в режиме Контроль кода имеет два режима управления: режим Интервал времени, в 10 котором начало времени счета определяется моментом поступления импульса на вход Запуск, конец времени счета определяется моментом поступления импульса на вход Стоп, режим Строб , 5 в котором время счета определяется длительностью импульса Запуск, при этом на вход Стоп должен быть подан высокий потенциал.

В режиме Контроль кода логичес- 0 кий пробник имеет два режима обработки поступающих сигналов: режим Счет , в котором импульсные сигналы, поступающие на вход Информация проходят на вход счетчика} режим Регистр, 5 в котором импульсные сигналы, посту-- пающие на вход Информация, проходят на восьмой вход блока 35 обработки либо на первые входы этого блока поступает многоразрядный цифровой код.

в режиме Счет логический пробник работает следующим образом.

При поступлении на вход Запуск импульсов положительной полярности (фиг. 3м) они поступают на элемент ИНЕ 29, а с его выхода после инвертирования на вход пятого триггера 27. После этого (по переднему фронту первого импульса) триггер 27 устанавливается в единицу. При этом с его прямого выхода высокий потенциал поступает на первый вход первого элемента И-НЕ 14, разрешая прохождение импульсов с шестого выхода блока 25 управления режимами на счетньш вход счетчика 17. Счетчики 17 и 18 и блок 26 счетчиков начинают считать импульсы. С выхода старшего разряда счетчика 17 сигнал поступает на счетньк вход счетчика 18, со старшего разряда которого сигнал поступает на счетный вход блока 26 счетчиков.Этим обеспечивается счет единиц импульсов на счетчике 17,счет десятков импульсов на счетчике 18, счет сотен, тысяч 5 на блоке 26 счетчиков. С первых выходов счетчиков 17 и 18 и блока 26 счетчиков соответственно на вторые, третьи и четвертые входы блока 35

0

5

0

5

0

13

обработки поступают цифровые коды. В этом режиме на пятый вход блока 3 обработки с второго выхода блока 25 управления режимами поступает высокий потенциал, а с третьего выхода на шестой вход блока 35 обработки поступает низкий потенциал.

При поступлении на вход Информация импульсов в режиме Счет они поступают на первый вход блока 25 уравления режимами, проходят на его шестой выход и далее поступают на Второй вход элемента И-НЕ 14 и первый вход блока 34 cинxpo изaции. На второй вход блока 34 синхронизации во время счета поступает высокий потенциал с прямого выхода триггера 2 Блоком 34 синхронизации вырабатыва- ется импульс синхронизации, посту- Дающий на девятый вход блока 35 обработки, в котором при этом происходит поразрядное запоминание входной пятнадцатиразрядной информации, поступившей со счетчиков 17 и 18 и блока 26 счетчиков

Вторые выходы с счетчиков 17 и 18 и блока 26 счетчиков соединены с соответствующими вторыми входами дешифраторов 19 и 21 и блока 32 дешифраторов, на первые входы которых потупают сигналы с соответствующих выходов блока 35 обработки. Коды с выходов дешифраторов 19 и 21 и блока 3 дешифраторов высвечиваются соответсвенно на индикаторах 22 и 23 и блок 33 индикаторов. При этом на индикаторе 22 высвечивается количество едниц, на индикаторе 23 - количество десятков, на блоке 33 индикаторов - количество сотен и тысяч гмпульсов,. поступивших на вхо лог1иеского пробника Инфррмация.

Счет ведется до поступления импульса на вход Стоп логического пробника. После поступления этого импульса (фиг. Зн) обнуляется триггер 27, при этом с его прямого выхода низкий потенциал поступает на первый вход элемента И-НЕ 14 и импульсы на счетный вход счетчика 17 перестшот поступать.. Одновременно с инверсного выхода триггера 27 высок потенциал поступает на вход синхронизации триггера 28,, триггер переключается, после чего на его выходе появляется низкий потенциал. Этот потенциал поступает на вход запуска элемента 30 цифровой задержки и

5

6946

о 0 5

0 5

0

5

0

5

1,4

на второй вход элемента И-НЕ 29, а также на вход обнуления триггера 27, при этом разрешается работа элемента 30 цифровой задержки. На счетчиках 17 и 18 и блоке 26 счетчиков запоминается код, соответствующий количеству импульсов, поступивших на вход Информация в отрезок времени от поступления импульса по входу Запуск и до поступления импульса по входу Стоп..

При работе устройства только от импульсов Стоп на вход Запуск подается низкий потенциал, при этом на первый вход триггера 27 поступает высокий потенциал. Первый импульс по входу Стоп устройства поступает на блок 25 управления режимами, и далее с его седьмого выхода поступает на вход синхронизации триггера 27. Дриггер 27 за .счет.соединения инверсного выхода с информационным входом работает в счетном режиме, поэтому первый же синхроимпульс переключает его в состояние, инверсное предьщуще- му, .при котором с прямого выхода триггера 27 поступает высокий потенциал. Далее работа-аналогична рас-. , смотренной Bbmie.

При работе логического пробника в режиме счета импульсов во временном стробе на вход Стоп устройства поступает высокий потенциал.,При поступлении импульса на вход Запуск на время его длительности на первый вход триггера 27 и третий вход блока 25 управления режимами поступает низкий потенциал, при этом через блок 25 управления режимами на вход синхронизации триггера 27 поступает низкий потенциал. По окончании импульса Запуск на вход синхронизации триггера 27 с блока 25 управления режимами поступает высокий потенциал.;, который устанавливает триггер 27 в обнуленное состояние, при этом на его прямом выходе.появляется низкий потенциал. Таким образом,, на прямом выходе триггера 27 на время импульса Запуск появляется высокий потенциал, который затем сменяется на низкий. В остальном работа логического пробника аналогична рассмотренной ранее при счете импульсов в интервале времени.

В режиме Регистр логический пробник имеет три режима обработки поступивших сигналов: режим Регистр ,

сигнатурный одноканальный , в котором одноканальная информация в последовательном коде поступает на вход Информация логического пробника одновременно с импульсами по входу Синхронизация, обработка ведется в сдвиговом регистре с обратными связями (сигнатурном анализаторе); режим Регистр одноканальный, в котором обработка входной однока- нальной информации ведется в сдвиговом регистр е без обратной -связи; режим Регистр сигнатурный многоканальный, в котором многоканальная инфор мация в виде многоразрядного параллельного кода поступает на многоразрядные цифровые входы устройства одновременно с импульсами по входу Синхронизация, обработка ведется в многоразрядном сигнатурном анализаторе.

В режиме Регистр многоканальный многоканальная информация, поступающая одновременно с импульсами по вхо ду Синхронизация, записывается без преобразований в блок 39 триггеров блока 35 обработки.

В режиме Регистр сигнатурный одноканальный с второго, третьего и четвертого выходов блока 25 управления режимами соответственно на пятый шестой и седьмой входы блока 3 обработки поступает высокий потенциал, а с пятого выхода на восьмой вход блока 35 обработки поступают импульсы, пришедшие на первый вход блока 25 управления режимами с входа Информация логического пробника. В этом режиме с шестого выхода блока 25 управления режимами на второй вход элемента И-НЕ 14 импульсы не поступают, поэтому на его втором входе присутствует постоянно низкий потенциал, а на счетном входе счетчика 17- высокий потенциал с выхода элемента И-НЕ 14.

Высокий потенциал с пятого, шестого и седьмого входов блока 35 обработки подается соответственно на пятый вход мультиплексора 36, второй вход блока 37 элементов И и первый вход элемента И 40. При этом на выходах мультиплексора 36 появляется низкий потенциал, поступающий на вторые третьи и четвертые входы блока 35 обработки. Высокий потенциал, поступающий с седьмого входа блока 35 обработки на первый вход элемента И 40,

0

Q

5

0 5

0

5

0

5

разрешает прохождение через него сигналов обратной связи, поступающих на его второй вход с выхода блока 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ.

Сигнал обратной связи вырабатывается блоком 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, первый, второй, третий и четвертый входы которого соединены с выходами седьмого, девятого, двенадцатого и шестнадцатого разрядов блока 39 триггеров. При поступлении на восьмой вход блока 35 обработки первого импульса информации он подается на второй вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, в котором происходит суммирование по модулю два импульса информации с сигналом обратной связи. До поступления первого импульса информации в блок 35 обработки на всех выходах блока 39 триггеров находятся низкие потенциалы, поэтому сигнал обратной связи низкого потенциала суммируется с высоким потенциалом импульса и на выходе элемента ИСЮПЮЧАЮЩЕ Е ШШ . 41 появляется высокий потенциал, поступающий далее на первый вход блока 37 элементов И.

С выхода первого разряда блока 37 элементов И высокий потенциал проходит на соответствующий второй вход блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, на первые входы которого поступает низкий потенциал с соответствующих выходов мультиплексора 36. Блок 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ во всех своих разрядах повторяет информацию, поступившую на его вторые входы, при поступлении на его первые входы низкого потенциала, поэтому при поступлении высокого потенциала на второй вход первого разряда блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ высокий потенциал появляется на его выходе и соответствующем первом входе блока 39 триггеров.

При поступлении импульса синхронизации с девятого входа блока 35 обработки на вход синхронизации блока 39 триггеров в его первый разряд записывается высокий потенциал, а в остальные - низкий потенциал. Потенциалы с выходов блока 39 триггеров поступают на третьи входы блока 37 элементов И, причем выход первого разряда блока 39 триггеров соединен с входом второго разряда блока 37 элементов И, выход второго разряда - с входом третьего разряда блока

171

37 элементов И, аналогично выходы третьего - пятнадцатого разрядов блока 39 триггеров соединены с входами второго - шестнадцатого разрядов блока 37 элементов И, поэтому высокий потенциал с выхода первого разряда блока 39 триггеров поступает на вход второго разряда блока 37 элементов И и проходит на его выход из-за присутствия высокого потенциала на втором входе блока 37 элементов И.

Высокий потенциал с выхода второго разряда блока 37 элементов И поступает на вход второго разряда блока 38 элементов ИСКЛЮЧАЮЩЕЕ ШШ и проходит на его выход без изменений При поступлении следующего импульса синхронизации на вход, синхронизации блока 39 триггеров и наличии импульса информации на втором входе элемента ИСКЛЮЧ/УОЩЕЕ ИЛИ 41 в первый и второй разряды блока 39 триггеров записывается высокий потенциал, а при отсутствии импульса информации на втором входе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 высокий потенциал записывается только во второй разряд блока 39 триггеров. Таким образом в блоке 39 триггеров накапливается информация о импульсной последовательности поступающей на восьмой вход блока 35 обработки.

При наличии высоких потенциалов на седьмом, девятом, двенадцатом и шестнадцатом разрядах блока 39 триггеров в блоке 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ происходит их суммирование п модулю два и результат суммирования поступает на второй вход элемента И 40, на первый вход которого поступает потенциал с седьмого входа блока 35 обработки, поэтому сигнал, поступающий на второй вход элемента И 40, лроходит на его выход Если на первый, второй, третий, четвертый входы блока 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ поступает четное количество высоких потенциалов, то на его выходе появляется низкий потен

циал, а при нечетном количестве высоких потенциалов появляется высокий потенциал.

Сигнал обратной связи суммируется по модулю два с импульсом информации в элементе ИСКЛЮЧАЮЩЕЕ ИЛИ 41: при наличии импульса информации на его втором входе присутствует высокий потенциал, а при наличии сигнала обрат0

5

0

6946

5

0

5

0

5

18

ной связи на его первом входе присутствует высокий потенциал,, тогда на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 вырабатывается низкий потенциал,- при неравенстве потенциалов на его входах вырабатывается высокий потенциал.

Так как запись информации в разряды блока 39 триггеров происходит по переднему фронту импульса синхронизации, поступающего на его соответствующий вход, то с приходом импульса синхронизации просуммированный по модулю два сигнал информации с сигналом обратной связи, прошедший блок 37 элементов И и блок 38 элементов ИС.КЛЮЧАЮЩЕЕ ИЛИ, записывается в первый разряд блока 39 триггеров. Таким образом, в рассматриваемом режиме блок 35 обработки ведет обработку поступающей на его восьмой вход последовательной информации, синхронизируемой синхроимпульсами, поступающими на его девятый вход. Выходная шестнадцатиразрядная информация подается на первые выходы блока 35 обрат ботки с первых трех разрядов блока 39 триггеров, на вторые выходы - с пятого и шестого разрядов блока 39 триггеров, на третьи выходы - с седьмого по пятнадцатый разрядов блока 39 триггеров, на четвертый выход - с четвертого разряда блока триггеров , на пятый выход - с шестнадцатого разряда.

Импульс синхронизации вырабатыва-- ется блоком 34 синхронизации при поступлении на его третий вход импульсов с входа Синхронизация логического пробника и наличии высокого потенциала на его втором входе, поступающего с прямого выхода триггера 27, При этом в блоке 34 синхронизации работает одновибратор, с выхода которого импульсы подаются на выход блока 34 синхронизации.

Выходные сигналы с разрядов блока 39 триггеров поступают объединенные в группы по три на первые входы де0 шифратора 19 и блока 32 дешифраторов, причем на их вторые входы поступают низкие потенциалы с вторых выходов счетчика 17 и блока 26 счетчиков. Вход первого разряда второго дешиф5 ратора 21 соединен с выходом третьего элемента ИЛИ 20, на первый вход элемента ИЛИ 20 подается информация с четвертого выхода блока 35 обработ19

ки, а на второй вход поступает низки потенциал с выхода элемента ИЛИ 16, поэтому на вход первого разряда дешифратора 21 поступает сигнал с четвертого выхода блока 35 обработки, при этом на первые входы дешифратора 21 поступают сигналы с вторых выходов блока 35 обработки, а на второ вход поступает низкий потенциал с второго выхода счетчика 18.

На входы гашения первого 19 и второго 21 дешифраторов пЬдается высокий потенциал соответственно с выходов формирователя 9 свечения нуля и формирователя 13 свечения единицы. На вход гашения блока 32 дешифраторов с выхода элемента ИЛИ 16 поступает низкий потенциал. Таким образом, на входах гашения дешифраторов 19 и 21 и блока 32 дешифраторов присутствуют потенциалы, разрешающие преобразование, кодов, поступивших на их первые и вторые входы, в коды семи- сегментных индикаторов, причем из-за того, что на вторые входы поступает низкий потенциал, дешифраторы 19 и 21 и блок 32 дешифраторов на своих выходах формируют коды, соответствующие числам от нуля до семи. С выходо дешифраторов 19 и 21 и блока 32 дешифраторов соответственно на индикаторы 22 и 23 и блок 33 индикаторов поступают коды чисел, соответствующие сигналам с блока 35 обработки. При наличии сигнала низкого потенциала на входе блока 33 индикаторов на нем высвечивается число единица. Таким образом, на индикаторах 22 и 23 и блоке 33 индикаторов высвечивается число в восьмеричном коде, соответствующее установленньм разрядам блока 39 триггеров.

Устройство в режиме Регистр од- ноканальный работает следующим образом.

Этот режим отличается от рассмотренного режима тем, что на седьмой вход блока 35 обработки подается низкий потенциал с четвертого выхода блока 25 управления режимами,.Низкий потенциал с седьмого входа блока 35 обработки поступает на первый вход элемента И 40 и запрещает прохождение сигнала обратной связи с выхода блока 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ на первый вход блока 37 элементов И. При поступлении импульса информации на второй вход элемента ИСКЛЮЧАЮЩЕЕ

й й

10

15

8694620

ИЛИ 41 он суммируется по модулю два с низким потенциалом, поступающим на его первый вход с выхода элемента И 40,поэтому сигнал,поступающий на первый вход блока 37 элементов И,повторяет сигнал, поступивший на второй вход элемента И 41. В остальном работа блока обработки аналогична описанной в режиме Регистр сигнатурный одноканальный, поэтому на индикаторах 22 и 23 и блоке 33 индикаторов высвечиваются числа в восьмеричном коде, соответствующие последовательному коду, поступившему на вход Информация логического пробника.

При работе логического пробника в режиме Регистр сигнатурный многоканальный на пятый и восьмой входы блока 35 обработки с второго и пятого выходов блока 25 управления режимами подается низкий потенциал, а на шестой, седьмой вход - высокий потенциал с третьего и четвертого выходов блока 25 управления режимами. - На первые входы блока 35 обработки подан многоразрядный код с многоразрядного цифрового входа логического пробника. При поступлении низкого потенциала с пятого входа блока 35 обработки на пятый вход мультиплексора 36 на его выходах появляется цифровой код, поступивший на его первые входы с первых входов блока 35 обработки.

20

25

30

35

0

5

На второй вход блока 37 элементов И с шестого входа блока 35 обработки подается высокий потенциал, который разрешает прохождение информации с выходов блока 39 триггеров на вторые входы блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, на первые входы которого поступает код с выходов мультиплексора 36. В блоке 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ происходит поразрядное суммирование по мЪдулю два многоразрядного кода, поступившего на первые входы блока 35 обработки, с кодом, полученным с выходов блока 39 триггеров, причем проводится суммирование информации второго разряда многоразрядного кода с информацией первого разряда блока 39 триггеров, суммирование информации третьего разряда кода - с информацией второго разряда блока 39 триггеров, суммирование информации четвертого - шестнадцатого разрядов кода с информацией третьего - пят5

надцатого разрядов блока 39 триггеров.

Первый разряд многоразрядного кода суммируется сигналом обратной связи, полученным с выхода блока 42 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ. По переднему фронту импульса синхронизации, поступившего на соответствующий вход блока 39 триггеров, в его разряды записывается информация,- поступившая на его первые входы с выходов блока 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, После этого в блоке 38 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ происходит суммирование новой информации с выходов блока 39 триггеров с многоразрядным кодом, поступившим на первые входы мультиплексора 36. После поступления очередного синхроимпульса новая просуммированная по модулю два информация записывается в блок 39 триггеров Таким образом, в блоке 39 триггеров происходит накопление информации многоразрядного кода, поступившего в течение интервала времени контроля кода. В остальном работа блока 35 обработки и индикация кодов чисел индикаторами 22 и 23 и блоком 33 индикаторов не отличается от рассмотренной в режиме Регис тр сигнатурный одноканальный.

При работе устройства в режиме Регистр многоканальный на пятый и шестой входы блока 35 обработки, с второго и третьего выходов блока 25 управления режимами подается низкий потенциал. Низкий потенциал поступает на пятый вход мультиплексора 36 и пропускает на его выходы многоразрядный код, поступивший на его пер- вые входы. Низкий потенциал, поступающий с шестого входа блока 35 обработки на второй вход блока 37 элементов И, блокирует информацию,поступающую на его первый и третьи входы с выходов блока 39 триггеров и выхода элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41. При этом блок 35 обработки выполняет функцию регистра записи и хранения многоразрядного кода, поступающего с соответствующего входа логического пробника. В остальном работа блока 35 обработки и индикация чисел соответствует описанному режиму Регистр сигнатурный многоканальный. Логический пробник в режимах Ре„ч

гистр сигнатурный одноканальНый и Регистр сигнатурный многоканальный

выполняет функцию сигнатурного анализатора.

Режим Регистр одноканальньш позволяет проверить наличие информации в определенном разряде последовательного кода, подаваемого одновременно с импульсами синхронизации.

Режим Регистр многоканальный позволяет проверить наличие информации в определенном разряде параллельного кода либо проверить многоканальную одноразрядную информацию.

Формула изобрет ения

Логический пробник, содержащий вход Сигнал, соединенный с первыми входами первого, второго пороговых

5

0

ного напряжения и. ограничителя отрицательного напряжения, выход которого соединен с первым инверсным выходом формирователя свечения ненормированного уровня и с первым входом первого индикатора, инверсные вькоды первого и второго пороговых элементов соединены соответственно с первым и вторым входами элемента И, выход которого соединен с первыми входами первого триггера и формирователя свечения ненормированного уровня, второй выход которого соединен с первым входом второго индикатора, вторые входы которого соединены с соответствующими выходами первого дешифратора, первый вход которого соединен с первым выходом первого счетчика и с первым входом BTopdro счетчика, первый выход которого соединен с первым входом второго дешифратора, выходы которого соединены с соответствующими вторыми входами первого индикатора, выход ограничителя положительного напряжения соединен с первым инверсным входом второго триггера, выход которого соединен с третьим входом первого индикатора, прямой выход первого порогового элемента соединен с первыми входами третьего триггера и формирователя свечения единицы, выход которого соединен с вторым входом второго дешифратора, прямой выход второго порогового элемента соединен с первыми входами четвертого триггера и форми- 5 рователя свечения нуля, инверсный выход третьего триггера соединен с вторым входом формирователя свечения единицы и вторым инверсным, входом

5

0

5

0

второго триггера, прямой выход третьего триггера соединен с инверсньм первым входом первого элемента ИЛИ, выход которого соединен с первым вхо дом первого элемента цифровой задержки, инверсный выход которого соединен с инверснь ми вторыми входами первого, третьего, четвертого триггеров третьи входы которых соединены с об- щей шиной устройства, инверсный выхо четвертого триггера соединен с вторым входом .формирователя свечения нуля, выход которого соединен с вторым входом первого дешифратора, прямые выходы четвертого и первого триггеров соединены соответственно с инверсными вторым и третьим входами первого элемента ИЛИ, выход генератора синхроимпульсов соединен с вторым входом первого элемента цифрово задержки и первым входом второго элемента цифровой задержки, первый инверсный выход которого соединен с первым инверсным входом пятого триггера, выход которого соединен с пер- вь№1 инверсным входом шестого триггера и с первым входом первого элемента И-НЕ, а также с вторым входом второго элемента цифровой задержки,второй инверсный выход которого соединен с первым инверсным входом второго элемента ИЛИ, выход которого соединен с первым входом первого счетчика и с вторым входом второго счетчика, второй инверсный вход второго элемента ИЛИ соединен с входом элемента НЕ и с первым выходом блока управления режимами, второй выход, которого соединен с вторым входом шестого триггера, первый инверсный выход которого соединен со своим третьим входом и с вторым входом пятого триггера, третий вход которого соединен с общей шиной,.вход Запуск устройства соединен с вторым входом первого элемента -И-НЕ, выход которого соединен с инверсным четвертьм входом шестого триггера, второй выход которого соединен с первым входом второго элемента И-НЕ, выход которого соединен с вторым входом первого счетчика, третьи входы формирователя . свечения нуля и формирователя свечения единицы соединены с первым входом третьего элемента ИЛИ, выход которого соединен с третьим входом второго дешифратора, инверсный выхо первого триггера соединен с вторым

15

20

25

45

ЗО

35

40

0

5

входом формирователя свечения ненор- мированно1 о уровня, отличающийся тем, что, с целью расширения функциональных возможностей, в него введены блок счетчиков, блок обработки, блок дешифраторов, блок индикаторов, блок синхронизации, входы Синхронизация, Информация,Стоп , многоразрядные цифровые входы, причем первые входы блока обработки сое- динены с соответствующими многоразрядными цифровыми входами устройства, вторые выходы первого счетчика соединены с соответствующими вторыми входами блока обработки, третьи входы которого соединены с соответствующими вторьши выходами второго счетчика, первый выход которого соединен с первым входом блока счетчиков, второй вход которого соединен с вторым входом второго счетчика, первым входом первого счетчика и с четвертым входом блока обработки, пятые входы которого соединены с соответствующими первыми выходами блока счетчиков, вторые выходы которого соединены с соответствующими первыми входами блока дешифраторов, второй вход которого соединен с выходом второго элемента ИЛИ и первьм входом третьего элемента ИЛИ, второй вход которого соединен с первым выходом блока обработки, вторые выходы которого соединены с соответствующими третьими входами блока деашфраторов, выходы которого соединены с соответствующими первыми входами блока индикаторов, второй вход которого соединен с третьим выходом блока обработки, четвертые выходы которйго соединены с соответствующими четвертыми входами второго дешифратора, пятые выходы блока обработки соединены с соответствующими третьими входами первого дешифратора, шестой вход блока обработки соединен с выходом блока синхронизации, первый вход которого соединен с вторым входом второго элемента R-HE и с третьим выходом блока управления режимами, четвертый, пятый, шестой, седьмой выходы которого соединены соответственно с седьмым восьмым, девятьм, десятым входами блока обработки, прямой выход шестого триггера соединен с вторым входом блока синхронизации, третий вход которого соединен с входом- Синхронизация устройства, входы Информация

25138694626

и Стоп которого соединены соответ- элемента И-НЕ, а выход элемента НЕ ственно с первым и вторым входами бло- соединен с третьим входом-формирована управления режимами, третий вход теля свечения ненормированного урон- которого соединен с выходом первого ня.

| название | год | авторы | номер документа |

|---|---|---|---|

| Логический пробник | 1984 |

|

SU1205085A1 |

| Логический пробник | 1987 |

|

SU1525636A1 |

| Логический пробник | 1986 |

|

SU1352421A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Логический пробник | 1984 |

|

SU1242863A1 |

| Устройство для ввода информации | 1986 |

|

SU1319015A1 |

| Устройство для поиска неисправностей в логических узлах | 1981 |

|

SU970283A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| Логический пробник | 1986 |

|

SU1352420A1 |

| Вторичные часы | 1986 |

|

SU1525671A1 |

Изобретение может быть исполь- 1 зовано при контроле импульсных сигналов и позволяет расширить функциональные возможности пробника.Логический пробник содержит пороговые элементы 1 и 2, триггеры 3-5, 8, 27 и 28, ограничители 6 и 7 отрицательного и положительного напряжения соответственно, формирователи 9, 12 и 13 свечения нуля, ненормированного уровня и единицы соответственно, элементы ИЛИ 10, 16 и 20, элементы 11 и 30 цифровой задержки, элементы И-НЕ 14 и 29, элемент НЕ 15, счетчики 17 и 18, дешифраторы 19 и Счснал 21, индикаторы 22 и 23, генератор 24 синхроимпульсов и блок 25 управления режимами. Бведение блока 26 счетчиков, блока 32 дешифраторов, блока 33 индикаторов, блока 34 синхронизации, блока 35 обработки и образование новых функциональных свя- зей обеспечивают контроль информации в последовательном и параллельном коде, поступающей на соответствующие входы пробника. При этом логический пробник в режимах Регистр сигнатурный одноканальный и Регистр сигнатурный многоканальный выполняет функцию сигнатурного анализатора. Режим Регистр одноканальный позволяет проверить наличие информации в опре- .деленном разряде последовательного кода, подаваемого одновременно с импульсами синхронизации. Режим Регистр многоканальный позволяет проверить наличие информации в опредег ленном разр5ще параллельного кода , либо проверить многоканальную одноразрядную информацию. 3 ил. i (Л С со 00 ОС 4 05

-Л

JLJT

Урова минее- jl Ц г - -

-Л

л

1

гг

JJLJT

гг

| Логический зонд | 1978 |

|

SU951201A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Логический пробник | 1984 |

|

SU1205085A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1988-04-07—Публикация

1986-07-01—Подача