(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ЛОГИЧЕСКИХ УЗЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля логических узлов | 1982 |

|

SU1020829A1 |

| Устройство для контроля логических блоков | 1984 |

|

SU1180901A1 |

| Устройство для контроля логических блоков цвм | 1976 |

|

SU633019A1 |

| Формирователь тестов | 1985 |

|

SU1259271A1 |

| УСТРОЙСТВО ДЛЯ ИМИТАЦИИ ОТКАЗОВ И ВНУТРИСХЕМНОГО ТЕСТИРОВАНИЯ ЭЛЕМЕНТОВ ДИСКРЕТНОЙ АППАРАТУРЫ | 1995 |

|

RU2093885C1 |

| Устройство для контроля субблока логического блока | 1986 |

|

SU1327111A1 |

| Устройство для контроля электрического монтажа | 1981 |

|

SU993275A1 |

| СПОСОБ КОНТРОЛЯ КОНТАКТИРОВАНИЯ КМОП-БИС И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1991 |

|

RU2009518C1 |

| ПОЖАРНЫЙ ИЗВЕЩАТЕЛЬ | 1992 |

|

RU2032225C1 |

| СИСТЕМА АВТОМАТИЗИРОВАННОГО КОНТРОЛЯ | 1991 |

|

RU2006896C1 |

1

Изобретение относится к автоматике и. вычислительной технике и может быть использовано для контроля исправности логических блоков и цифровых интегральных схем.

Известны устройства для контроля логических блоков ЦВМ, принцип действия которых основан на сравнении сигналов проверяемого и эталонного блоков tl3 и 23 .

Недостатком этих устройств является то, что для каждого типа блоков необходимо иметь карты включения коммутационных шнуров, в соответствии с которыми необходимо осуществлять соединения проверяемого и эталонного блоков.

Наиболее близким к предлагаемому является устройство, в котором для перехода на контроль другого типа логических блоков достаточно лишь заменить эталонный блок и нет необходимости производить какие-либо дополнительные коммутации.

Это устройство содержит генератор импульсЮв, счетчик эталонный блок схем сравнения, элементы памяти, индикаторы, блок обнаружения входов и блок управления. Выход генератора импульсов соединен.со входом счетчика, первые входы блоков обнаружения входов соединены с первым выходом блока управления, первые и вторые выходы блоков обнаружения входов - со входами и выходами контролируемого и эталонного блоков, а также с соответствующими входами схем сравнения, выходы которых соединены соответственно с первыми входа10ми элементов памяти, вторые входы которых соединены с первым выходом блока управления, а выходы - с индикаторами .

Известное устройство работает по принципу сравнения выходных и входных сигналов двух блоков - контролируемого и эталонного. На входы обоих блоков подаются всевозможные двоичные комбинации и производится сравнение состояний на всех выводах обоих блоков. При обнаружении дефекта в контролируемом блоке загорается один или несколько индикаторов. Блок обнаружения входов позволяет различать вход блока от выхода Г31 ,

Недостаток известного устройства - при проверке блоков с открытым коллекторным выходом при закрытом выходом транзисторе блок обнаружения входов будет ошибочно классифиЦировать выход блока как его вход. Это происходит вследствие того, что на выходе блока обнаружения входов (выход с элемента 13 И-НЕ) всегда присутствует потенциал, прцсущий входу ТТЛ-логики, поступающий с первого входа элемента 14 И-НЕ блока обнаружения входов (3, фиг.2), а .так как закрытый транзистор открытого коллекторного выхода эталонного блока не вносит изменения уровня на выходе блока обнаружения входов, то происходит ошибка в распознавании входов. Таким образом, известное устройство не обеспечивает достоверного результата при распознавании входов и выходов.

Кроме того, известное устройство не позволяет осуществлять локализацию неисправности в блоках (т.е. не проверяет интегральные микросхемы, установленные на печатных плата На входах интегральной схемы, установленной на печатной плате, присутствуют логические уровни, поступающие с выходов других микросхем, поэтому при использовании известного устройства на входах проверяемой микросхемы будет наблюдаться наложение сигналов (искусственное ИЛИ) ранее присутствующих и поступающих от счетчика 2 известного устройства Поэтому сигналы на входах контролируемой микросхемы будут отличаться от сигналов на входах эталонной микросхемы, что приведет к ошибочной браковке исправной интегральной схемы.

Цель изобретения - расширение области применения.

Поставленная цель достигается тем, что в устройство для контроля логических узлов, содержащее генератор импульсов, счетчик, блок хранения эталонов, элементы сравнения, блоки памяти, индикаторы, блоки фиксации входов и блок управления, причем выход генератора импульсов соединен со входом счетчика, первые входы блоков фиксации входов соединены с первым выходом блока управления, первые и вторые выходы блоков фиксации входов соединены соответственно с выводами контролируемого узла и блока хранения эталонов, а также с соответствующими входами элементов сравнения, выходы которых соединены соответственно с первыми входами блоков памяти, вторые входы KOliopbix соединены с первым выходом блока управления, а выходы - с индикаторами, введены элементы И и ключ при этом первые входы элементов И соединенысоответственно с группой выходов счетчика, вторые входы элементов И соединены соответственно с вторым выходом блока управления, с первыми входами ключей, а выходы элментов И соединены со вторыми входами блоков фиксации входов, третьи входы которых соединены с третьим выходом блока управления, вторые -вхды ключей соединены с первыми выходми блоков фиксации входов, третьи входы ключей соединены с третьими выходами блоков фиксации входов, а выходы - со вторыми входами элементов сравнения.

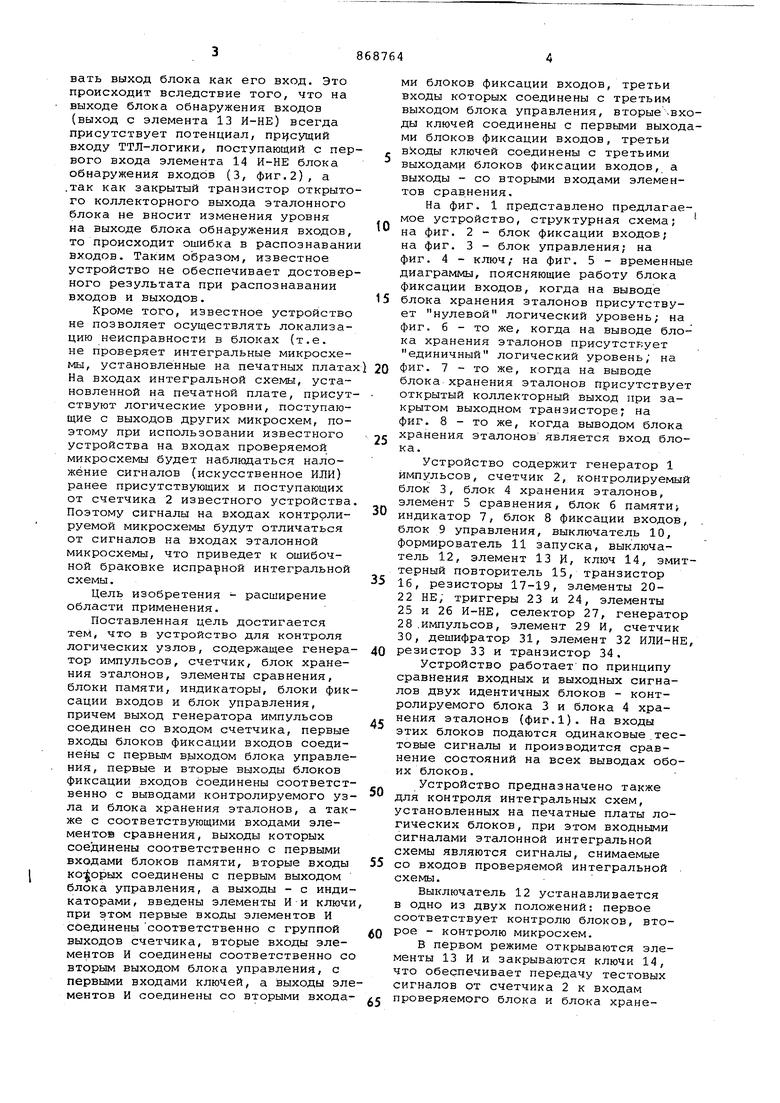

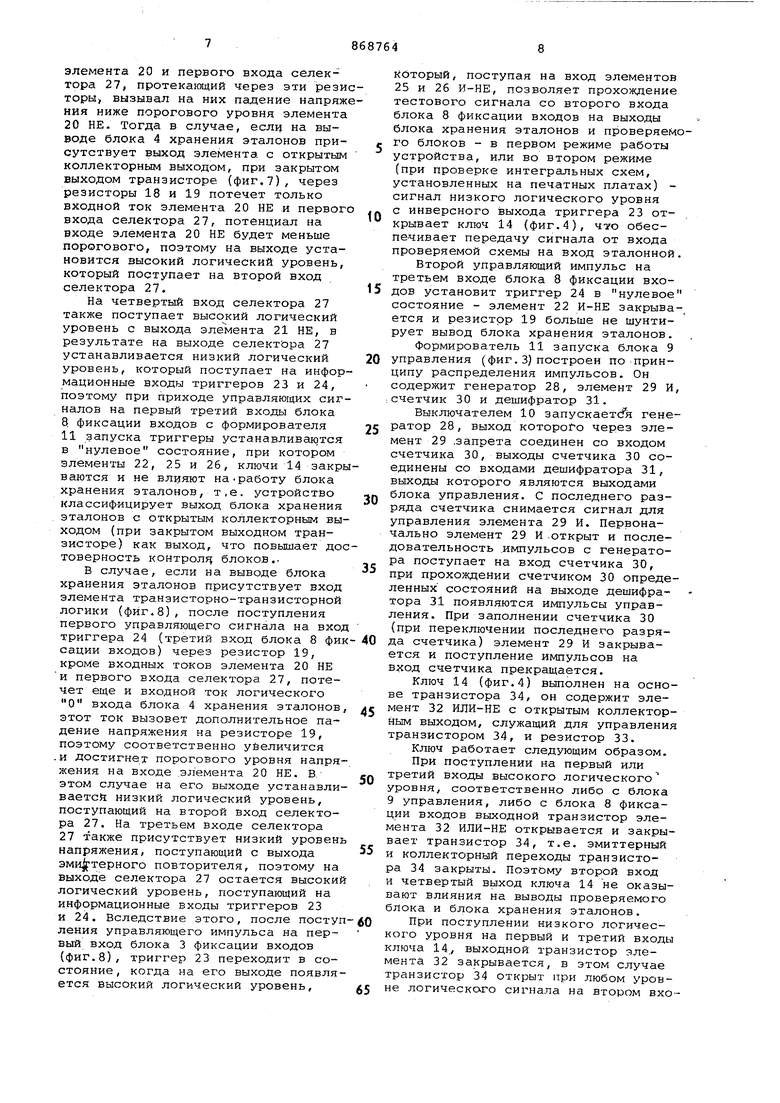

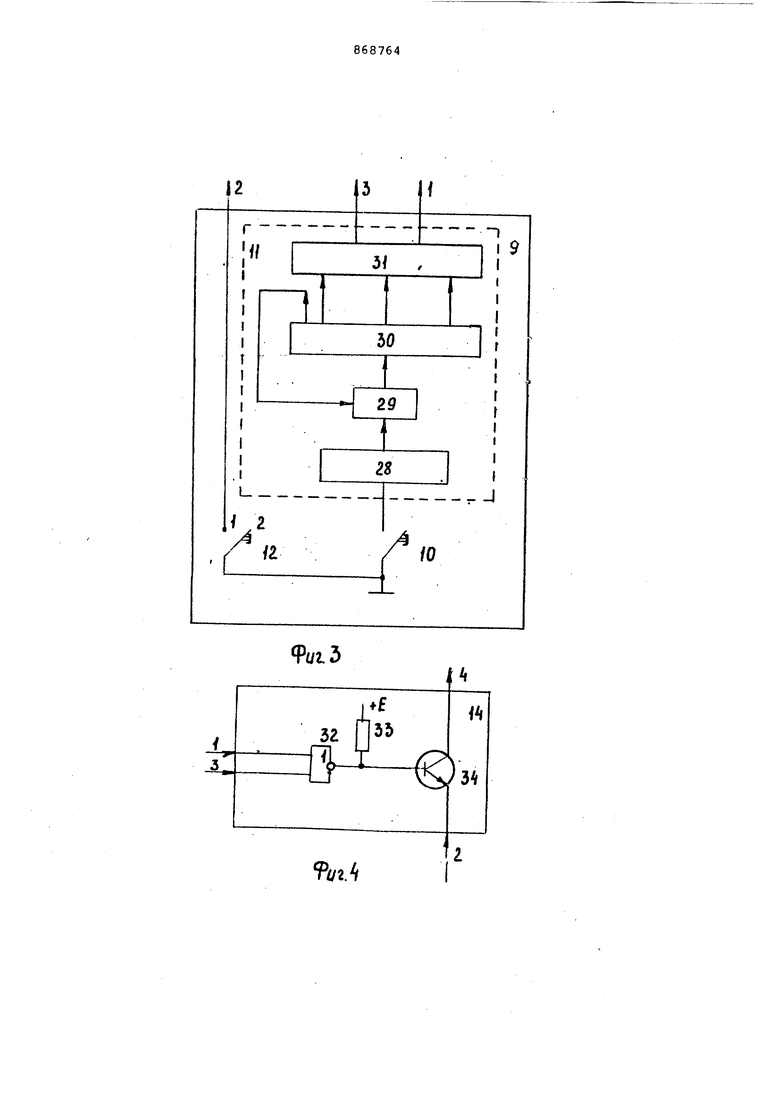

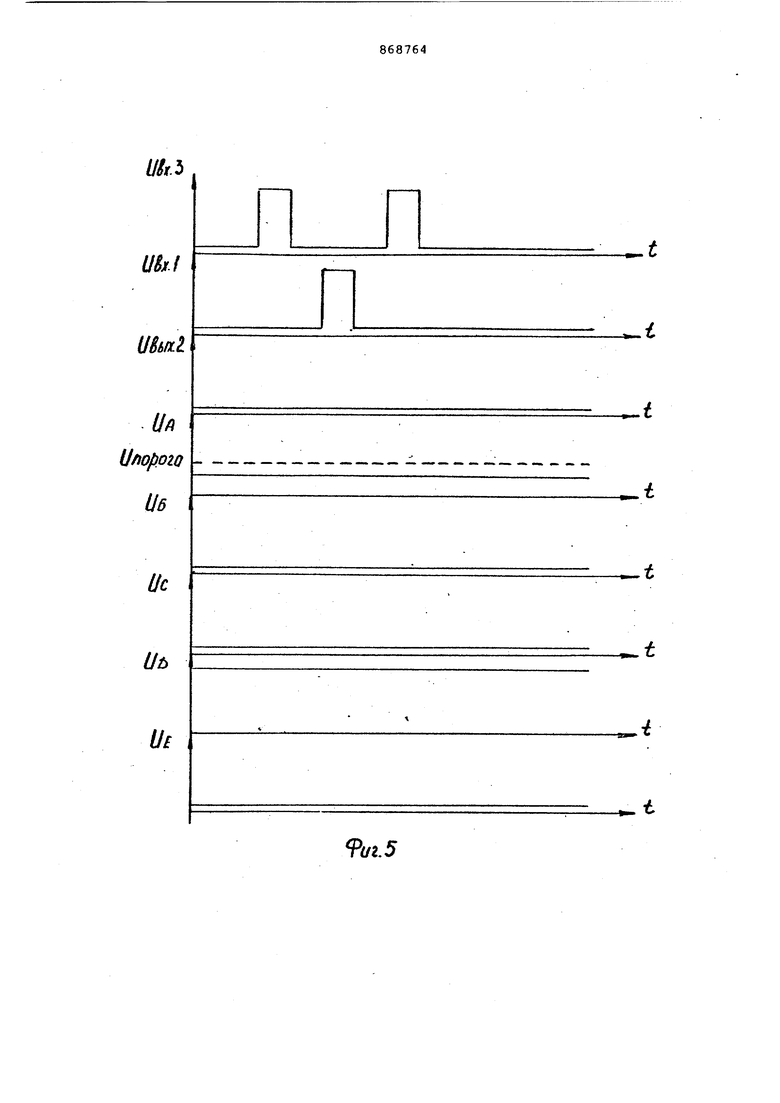

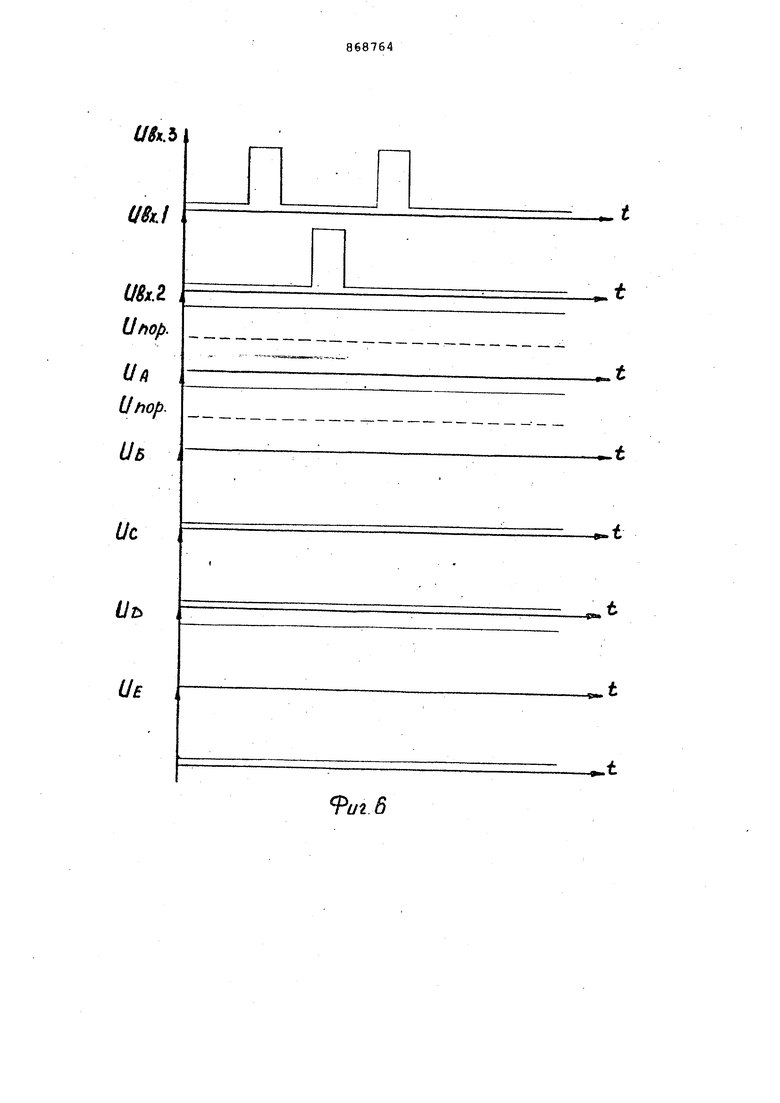

На фиг. 1 представлено предлагаемое устройство, структурная схема; на фиг. 2 - блок фиксации входов; на фиг. 3 - блок управления; на фиг. 4 - ключ; на фиг. 5 - временны диаграммы, поясняющие работу блока фиксации входов, когда на выводе блока хранения эталонов присутствует нулевой логический уровень; на фиг. 6 - то же, когда на выводе блока хранения эталонов присутстг;ует единичный логический уровень; на фиг. 7 - то же, когда на выводе блока хранения эталонов присутствуе открытый коллекторный выход при закрытом выходном транзисторе; на фиг. 8 - то же, когда выводом блока хранения эталонов является вход блока.

Устройство содержит генератор 1 импульсов, счетчик 2, контролируемы блок 3, блок 4 хранения эталонов, элемент 5 сравнения, блок 6 памяти; индикатор 7, блок 8 фиксации входов блок 9 управления, выключатель 10, формирователь 11 запуска, выключатель 12, элемент 13 И, ключ 14, эмитерный повторитель 15, транзистор 16, резисторы 17-19, элементы 2022 НЕ, триггеры 23 и 24, элементы 25 и 26 И-НЕ, селектор 27, генерато 28 .импульсов, элемент 29 И, счетчик 30, дешифратор 31, элемент 32 ИЛИ-Н резистор 33 и транзистор 34.

Устройство работает по принципу сравнения входных и выходных сигналов двух идентичных блоков - контролируемого блока 3 и блока 4 хранения эталонов (фиг.1). На входы этих блоков подаются одинаковые.тестовые сигналы и производится сравнение состояний на всех выводах обоих блоков.

Устройство предназначено также для контроля интегральных схем, установленных на печатные платы логических блоков, при этом входными сигналами эталонной интегральной схемы являются сигналы, снимаемые со входов проверяемой интегральной схемы.

Выключатель 12 устанавливается в одно из двух положений: первое соответствует контролю блоков, второе - контролю микросхем.

В первом режиме открываются элементы 13 И и закрываются ключи 14, что обеспечивает передачу тестовых сигналов от счетчика 2 к входам проверяемого блока и блока хранения эталонов. Во втором режиме элементы 13 И закрываются, но открываются ключи 14, что обеспечивает передачу сигналов со входом контролируемого блока 3 на входы блока 4 хранения эталонов.

Первоначально все элементы памяти блоков 6 и 8 устанавливаются в нулевое состояние, соответствующее отсутствию свечения в индикаторах 7, закрытию ключей 14 и запрещению прохождения тестовых сигналов от счетчика 2 через элементы 13 И и блоки 8 фиксации входов на выводы контролируемого и эталонного блоков.

Устройство работает следующим образом.

Выключателем 10 запускается формирователь 11 управляквдих импульсов, открывающий блоки 8 фиксации входов, которые в первом режиме начинают передавать тестовые сигналы от счетчика 2 через элементы 13 И на входы контролируемого блока, а во втором режиме открываются ключи 14, соответствующие входам блока 4 хранения эталонов,, что обеспечивает передачу сигналов со входом контролируемого блока 3 на входы блока 4 хранения эталонов.

Элементы 5 сравнения в обоих режимах сравнивают сигналы на выходах блоков 3 и 4 и в случае несовпадения выдают сигналы на соответствующий блок 6 памяти, который в этом случае устанавливается в состояние, соответствующее свечению индикатора 7. В случае, если контролируемый блок 3 исправен, то в конце проверки, длительность которой задается формирователем 11 запуска, ни один из индикаторов 7 не светится, если-контролируемый блок 3 является неисправным, то в конце проверки, в зависимости от характера неисправности, высвечивается определенная комбинация индикаторов 7. Блоки 8 фиксации входов построены таким образом, что каждый из них открывается только в том случае, если на .выходе блока 4 хранения эталонов был зарегистриро.ван потенциал, характерный для входа блока (для транзисторно-транзисторной логики, порядка 1,3 В), а после щунтирования этого вывода через резистор на землю через этот резистор протекает входной ток логического нуля.

Отличие входа от выхода производится следующим образом. Если на втором выходе блока 8 фиксации входов (фиг.2), присоединенного к блоку хранения эталонов 4, присутствует нулевой (.$.0,4 в) потенциал (фиг.5 то последний, поступая через резистор 18 на вход элемента 20 НЕ, устанавливает его в состояние, когда на его выходе появляется высокий уровень напряжения, который подается на второй вход селектора 27, на четвертый вход селектора 27 также поступает высокий уровень напряжения с выхода элемента 21 НЕ, в результате на выходе селектора 27 устнавливается низкий логический уровень, который поступает на информационные вхрды триггеров 23 и 24, в результате чего в момент поступлени управляющих сигналов с формировател 11 запуска на первый и третий входы блока 8 фиксации входов, триггеры устанавливаются в нулевое состояние и элементы 22, 25 и 26 И-НЕ с открытым коллекторным выходом остаются закрытыми, также остается закртым ключ 14, на третий вход которог с инверсного выхода триггера 23 подается высокий логический уровень (фиг.4).

То же самое происходит и в случае когда на выводе блока 4 хранения эталонов присутствует высокий ( 2,4 в) потенциал (фиг.6), только в этом случае высокие логические уровни поступают на первый и третий входы селектора 27.

Если на выводе блока 4 фиксации эталонов присутствует неопределенный уровень (1,3 в), что возможно в двух случаях: первый - вывод блока хранения эталонов является входом, второй - вывод блока хранения эталонов является выходом с открытым коллекторным выходом при закрытом выходном транзисторе, тогда уровень на выходе эмиттерного повторителя 15, собранного на транзисторе 16 и ре-. зифторе 17, станет равным порядка 0,4 В, так как на эмиттерном переходе транзистора падает от 0,7 до 1,0 В, т.е. низкий.логический уровень поступает на третий вход селектора 27,

На вход элемента 20 НЕ ток, при неопределенном уровне, практически отсутствует, поэтому на его выходе устанавливается низкий уровень, который поступает на второй вход селектора 27.

При поступлении на второй и третий входы селектора 27 низкого уровня на его выходе появляется высокий логический уровень.

В результате, после поступления первого управляющего импульса (фиг.7 и 8) на третий вход блока 8 фиксации входов, триггер 24 устанавливается в единичное состояние, т.е. с выхода триггера 24 на вход элемента 22 НЕ с открытым коллекторным выходом поступает высокий логический уровень, в результате чего выходной транзистор элемента 22 открывается и через резистор 19 шунтирует вывод эталонного блока на землю .

Номиналы резисторов 18 и 19 выбраны так, чтобы суммарный входной ток элемента 20 и первого входа селектора 27, протекающий через эти рези торы, вызывал на них падение напряж ния ниже порогового уровня элемента 20 НЕ. Тогда в случае, если на выводе блока 4 хранения эталонов присутствует выход элемента с открытым коллекторным выходом, при закрытом выходом транзисторе (фиг.7), через резисторы 18 и 19 потечет только входной ток элемента 20 НЕ и первог входа селектора 27, потенциал на входе элемента 20 НЕ будет меньше порогового, поэтому на выходе установится высокий логический уровень, который поступает на второй вход селектора 27. На четвертый вход селектора 27 также поступает высокий логический уровень с выхода 21 НЕ, в результате на выходе селектЬра 27 устанавливается низкий логический уровень, который поступает на инфор мационные входы триггеров 23 и 24, поэтому при приходе управляющих сиг налов на первый третий входы блока 8 фиксации входов с формирователя 11 запуска триггеры устанавливаются в нулевое состояние, при котором элементы 22, 25 и 26, ключи 14 закры ваются и не влияют на-работу блока хранения эталонов, т,е. устройство классифицирует выход блока хранения эталонов с открытым коллекторным вы ходом (при закрытом выходном транзисторе) как выход, что повышает до товерность контроля блоков.. В случае, если на выводе блока хранения эталонов присутствует вход элемента транзисторно-транзисторной логики (фиг.8), после поступления первого управляющего сигнала на вхо триггера 24 (третий вход блока 8 фи сации входов) через резистор 19, кроме входных токов элемента 20 НЕ и первого входа селектора 27, потечет еще и входной ток логического О входа блока 4 хранения эталонов этот ток вызовет дополнительное падение напряжения на резисторе 19, поэтому соответственно уйеличится .и достигнет порогового уровня напря жения на входе .элемента 20 НЕ. В. этом случае на его выходе устанавли ваетсй низкий логический уровень, поступающий на второй вход селектора 27. На третьем входе селектора 27 также присутствует низкий уровен напряжения, поступающий с выхода эми терного повторителя, поэтому на выходе селектора 27 остается высоки логический уровень, поступающий на информационные входы триггеров 23 и 24. Вследствие этого, после посту ления управляющего импульса на первый вход блока 3 фиксации входов (фиг.8), триггер 23 переходит в состояние, когда на его выходе появля ется высокий логический уровень, Кйторый, поступая на вход элементов 25 и 26 И-НЕ, позволяет прохождение тестового сигнала со второго входа блока 8 фиксации входов на выходы блока хранения эталонов и проверяемого блоков - в первом режиме работы устройства, или во втором режиме (при проверке интегральных схем, установленных на печатных платах) сигнал низкого логического уровня с инверсного выхода триггера 23 открывает ключ 14 (фиг.4), чтсо обеспечивает передачу сигнала от входа проверяемой схемы на вход эталонной. Второй управляющий импульс на третьем входе блока 8 фиксации входов установит триггер 24 в нулевое состояние - элемент 22 И-НЕ закрывается и резистор 19 больше не шунтирует вывод блока хранения эталонов. Формирователь 11 запуска блока 9 управления (фиг.3}построен по принципу распределения импульсов. Он содержит генератор 28, элемент 29 И, счетчик 30 и дешифратор 31. Выключателем 10 запускаетс я генератор 28, выход которого через элемент 29 .запрета соединен со входом счетчика 30, выходы счетчика 30 соединены со входами дешифратора 31, выходы которого являются выходами блока управления. С последнего разряда счетчика снимается сигнал для управления элемента 29 И. Первоначально элемент 29 И -открыт и последовательность .импульсов с генератора поступает на вход счетчика 30, при прохождении счетчиком 30 определенных состояний на выходе дешифратора 31 появляются импульсы управления. При заполнении счетчика 30 (при переключении последнего разряда счетчика) элемент 29 И закрывается и поступление импульсов на вход счетчика прекращается. Ключ 14 (фиг.4) выполнен на основе транзистора 34/ он содержит элемент 32 ИЛИ-НЕ с открытым коллекторным выходом, служащий для управления транзистором 34, и резистор 33. Ключ работает следующим образом. При поступлении на первый или третий входы высокого логического уровня, соответственно либо с блока 9 управления, либо с блока 8 фиксации входов выходной транзистор элемента 32 ИЛИ-НЕ открывается и закрывает транзистор 34, т.е. эмиттерный и коллекторный переходы транзистора 34 закрыты. Поэтому второй вход и четвертый выход ключа 14 не оказывают влияния на выводы проверяемого блока и блока хранения эталонов. При поступлении низкого логического уровня на первый и третий входы ключа 14., выходной транзистор элемента 32 закрывается, в этом случае транзистор 34 открыт при любом уровне логического сигнала на втором входе ключа (на эмиттере транзистора 3 поэтому на четвертом выходе ключа 14 (коллектор транзистора 34) будет повторяться логический уровень второго входа , таким образом осуществл ется передача сигнала со входа проверяемого блока 3 на вход эталонног блока 4, Предлагаемое устройство значител но облегчает процесс локализации неисправностей, так как позволяет проверять интегральные схемы, установленные на печатных платах. Глуби на поиска дефектов при использовани устройства достигает корпуса интегральной схемы. Кроме того, устройст во позволяет Проверять более достоверно широкую номенклатуру блоков, включая блоки с-открытым коллекторным выходом. Формула изобретения 1. Устройство для контроля логических узлов, содержащее генератор импульсов, счетчик, блок хранения эталонЪв, элементы сравнения, блоки памяти, индикаторы, блоки фиксации входов и блок управления, причем выход генератора импульсов соединен со входом счетчика, первые входы блоков фиксации входов соединены с первым выходом блрка управления, первые и вторые выходы блоков фикса ции входов соединены соответственно с выводами контролируемого узла и блока хранения эталонов, а также с соответствующими входами элементов сравнения, выходы которых соединены соответственно с первыми входами блоков памяти, вторые входы которых соединены с первым выходом блока управления, а выходы - с индикаторами, отличающее ся тем, что, с целью расширения области применения, в устройство введены элементы И и ключи, при этом первые входы элементов И соединены соответственно с группой выходов счетчика, вторые входы элементов И соединены со вторым выходом блока управления, с первыми входами ключей, а выходы элементов И соединены со вторыми входами блоков фиксации входов, третьи входы которых соединены с третьими выходами блока управления, вторые входы ключей соединены с первыми выходами блоков фиксации входов, третьи входы ключей соединены с третьими выходами блоков фиксации входов, а выходы - со вторыми входами элементов сравнения. 2.Устройство ПОП.1, отличающееся тем, что блок фиксации входов содержит первый и второй триггеры, первый, второй и третий элементы НЕ, первый и второй элементы И-НЕ, селектор,делитель на резисторах, эмиттерный повторитель, причем второй вход блока соединен с первыми входами первого и второго элементов И-НЕ, вторые входы которых соединены с первым выходом первого триггера, счетный вход которого соединен с первым входом блока, третий вход блока соединен со счетным входом второго триггера, выход которого соединен со входом первого элемента НЕ, выход которого через первый резистор делителя соединен с выходом элемента И-НЕ,. со вторым выходом блока, -со входом эмиттерного повторителя и через второй резистор делителя со входом второго элемента НЕ, вход которого соединен с первым входом селектора, выход второго элемента И-НЕ соединен с первым выходом блока, третий выход которого соединен со вторым выходом первого триггера, информационный вход которого соединен с информационным входом второго триггера и с инверсным выходом селектора, второй вход которого соединен с выходом второго элемента НЕ, третий вход селектора соединен с выходом эмиттерного повторителя и входом третьего элемента НЕ, выход которого соединен с четвертым входом селектора. . 3.Устройство поп.1,отличающеес я тем, что блок управления содержит выключатель, выход которого является вторым выходом блока управления, а шина, нулевого потенциала соединена через второй выключатель со входом формирователя запуска, выходы которого являются первыми и третьими выходами блока управления. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР №441532, кл. G 01 R 31/28, 1971. 2.Авторское свидетельство СССР №553618, кл. G 06 F 11/00, 1975. 3.Авторское свидетельство СССР №633019, кл. G 06 F 11/04, 1976.

9иг. I

9аг.г.

Ф(/г.З

иы тьт1

Ufi

ило/)ого U6

Uc Ut

и I

t

i

i

i

9(/г.5

Шк.Ь I

USti ,

ибк2

Ufjoj).

UA

Uhop.

UB и С Ub UE

t

9иг6

9иг7

L r

Авторы

Даты

1981-09-30—Публикация

1980-01-21—Подача