выход которого соединен с входом второго триггера, первьй выход регистра памяти соединен с первым входом первого элемента И и входом элемента НЕ, выход которого соединен с первым входом пятого элемента И, второй вход которого, объединенный с вторым входом первого элемента И, соединен с выходом третьего элемента И, первый вход которого, объединенньгй с входами первого и второго счетчиков, первого триггера и первым входом второго элемента И, соединен с выходом генератора тактовых импульсов, выход первого счетчика соединен с вторым входом второго элемента И, выход которого соединен с входом регистра памяти и вторыми входами элементов И группы, выход второго элемента ИЛИ соединен с первым входом четвертого элемента И, второй вход которого соединен с выходом первого триггера выход второго счетчика соединен с вторым входом третьего элемента И, выход первого элемента И соединен с входом первого регистра начального состояния группы, выход пятого элемента И соединен со входом второго регистра начального состояния группы.

i

Изобретение относится к импульсной технике.

Целью изобретения является расширение функциональных возможностей за счет осуществления возможности формирования больших ансамблей последовательностей.

На фиг. 1 представлена функциональная схема устройства для форми рования псевдослучайных сигналов, на фиг. 2 - функциональная схема блока управления; на фиг. 3 - функ- циональная схема коммутирующего блока.

Устройство содержит (фиг. 1) пер вый счетчик 1, второй счетчик 2, первый 3, второй 4, третий 5 блоки коммутации, формирователи 6 остатко блок 7 умножения, блок 8 кодообра- зования, блок 9 элементов И, дели-

205262

3. Устройство по п. 1, отличающееся тем, что коммутирующий блок содержит регистр, счетчик, первую группу элементов И, первый элемент ИЛИ, вторую группу элементов И, группу элементов НЕ, регистр длительности, второй элемент ИЛИ, триггер, первый вход которого соединен с выходом второго элемента ИЛИ, входы которого соединены с выходами элементов И второй группы, первые входы элементов И которой соединены с выходами первой группы выходов регистра, вторая группа выходов которого соединена с соответствующими первыми входами элементов И первой группы, вторые входы элементов И которой соединены с соответствующими выходами регист- , ра длительности и входами элементов НЕ группы, выходы элементов НЕ которой соединены с вторыми входами

элементов И второй группы, третьи входы элементов И первой группы соединены с выходами соответствую-i щих разрядов счетчика, выходы элементов И первой группы-соединены с входами первого элемента ИЛИ, выход которого соединен с первым входом регистра, второй вход которого соединен с вторым выходом триггера.

0

тель 10 частоты, блок 11 памяти, блок 12 хранения, программный блок 13, первый регистр 14 сдвига, генератор 15 управляемых импульсов, блок 16 управления, второй регистр 17 сдвига, группу 18 элементов И, элемент ИЛИ 19, коммутирующий блок 20, регистр 21 управления, первый сумматор 22 по модулю два, элемент И 23 и второй сумматор 24 по модулю два. Выходы первого счетчика 1 соединены с входами первого блока 3 коммутации, вьтходы которого соединены с входами формирователей 6 остатков, выходы которого соединены с входами второго блока 4 коммутации, выходы которого соединены с входами регистра 14 сдвига, выходы которого соединены с входами третьего блока 5 коммутации, выходы которого

мое для представления максимального остатка по максимальному модулю Plhian .При этом каждому триггеру регистра 14 должно соответствовать два элемента ИЛИ любого формирователя 6 остатков (для установки в О и в 1), а каждому элементу ИЛИ последнего должно соответствовать такое число элементов И, сколько возможных ситуаций приводит к переводу одного триггера регистра. 14 в соответствующее состояние, А так как у каждого формирователя 6 остатков имеется свое определенное число элементов ИЛИ, которые соответствуют определенному числу триггеров регистра 14, то блок 4 коммутации, подобно блоку 3 коммутации, и осуществляет под воздействием определенной, соответствующей модулю Р| , серии входных коммутирующих импульсов коммутацию определенных выходов формирователей 6 с определенными входами регистра.

Так как для формирования остатко от числа по определенному модулю Р( задействуется определенное число триггеров регистра 14 и определен- ный формирователь 6 остатков, то при этом должно быть обеспечено соединение других входов определенного /формирователя 6 остатков с выходами определенного числа триггеров регистра 14. Эту функцию выполняет блок 5 коммутации под воздействием определенной, соответствующей модулю Pi , серии управляющих импульсо

Блок 7 предназначен для умножения двух чисел для формирования мультипликативной группы поля GF(Pi). Для этого перед началом работы из блока 12 в блок 7 поступает код модуля наименьшего первообразного элемента поля GF(Pc)j из блока 13 в блок 7 поступают тактовые импульсы Начало счета. Для получения каждого последующего числа - элемента мультипликативной группы, блок 7 обеспечивает умножение предыдущего числа элемента а, код которого поступает на его пер- вые входы с выходов блока 5 коммутации, на первообразный элемент Qi поля и по своему первому выходу выдает в двоичном последовательном коде число, которое поступает пос- едовательно в формирователи 6. Перед моментом выдачи очередного (числа в формирователи 6 по третьим

2052628

выходам блок 7 выдает в блок 8 ко- дообразования код числа - элемента а;, , а по пятому выходу в блок 8 и блок 11 сигнал Такт считьшания с числа - элемента, а с второго выхо- -да блока 7 на первые входы счетчика 1 и регистра 14 поступает сигнал Конец умножения, приводящий в исходное нулевое состояние счетчик

)Q 1 и регистр 14, подготавливая их для работы по отысканию очередного остатка at А;, (модуль Pj,) . В следующий момент с первого выхода блока 7 в формирователи 6 считы 5 Бается код числа A.I, Счетчик 2 с каждым сигналом Такт считывания числа - элемента, поступающим на его первый вход с выхода блока 7, вьщает по своим выходам в делитель

2Q 10 код числа данных тактов, поступающих к данному моменту. Делитель 10 осуществляет деление числа N Pi. - 1 (Р было записано ранее в делитель 10 из блока 12) на код

25 числа тактов, и если результат деления является дробным числом, то делитель 10 вьщает на второй вход блока 9 элементов И сигнал, открывающий его и разрешающий тем самым запись кода числа - элемента а с выходов блока 5 в блок 11 памяти. Записьшаемые таким образом в блок коды определенных элементов представляют собой другие первообразные элементы поля GF(PL), т.е. следуя

теории-чисел, любое б к li

(модуль PL), где К, Р, - 1 1, „т.е. взаимно простые К и Р; - 1 ЯЕ ляются первообразным элементом поля GF(Pi.).

Таким образом, делитель 10 осуществляет определение момента поступления очередного К, взаимно простого с PL - 1 числа Тактов считыва

ния числа - элемента . При этом а, 0. (модуль PL), где 0,очередной первообразный элемент поля, и тем самым записывается в блок 11.

По окончании формирования всех

элементов мультипликативной группы поля GF(P( ) из блока 7 по четвертому выходу в блок 8 поступает сигнал Конец формирования группы, на основании которого блок 8 начинает

считывать код псевдослучайной последовательности, сформированной к данному моменту на основании кодов чисел - элементов поля GF(PL), поступающих на его входы, и управляющих сигналов, поступающих на его третий вход из блока 7 и шину управляющих входов из блока 13.

Одновременно сигнал, соответствующий определенному модулю Р, поступает в блок 16 управления. В блоке 16 управления осуществляется выбор начального состояния и управляющих импульсов для формирования задающего ортогонального сигнала. Через первый выход блока 16 управления во второй регистр 17 сдвига записывается начальное состояние для формирования задающего ортогонального сигнала, а через четвертый выход в регистр 21 управления записываются управляющие импульсы. Через второй выход блока 16 управления устанавливает коммутирующий бло 20 в начальное состояние, при котором на первом выходе действует единичное значение, а на других и втором выходах - нулевое значение сигнала.

На второй вход коммутирующего блока 20 поступает код, соответствующий длительности формируемого сигнала.

Второй регистр 17 сдвига содержи тац 2 ячеек памяти (триггеров), где К - показатель степени, соответствующий максимально возможной формируемой длительности сигнала. Элементы И группы 18 соединены только с выходами тех ячеек памяти второго регистра 17 сдвига, номера которых кратны 2 , где V 1,К .

В регистр 21 управления с четвертого выхода блока 16 управления за.писывается управляющая последовательность.

Управляющая последовательность и выбор начального состояния второго регистра 17 сдвига в блоке 16 управления осуществляется в результате анализа двоичного кода формируемого задающего ортогонального сигнала из матрицы Адамара порядка L 2 . Если номер строки (столбца) в двоичном коде заканчивается нулем, то во второй регистр 17 сдвига необходимо записьшать начальное состояние 11, иначе 10. Чтобы получить управляющую последовательность, необходимо записать номер строки в двоичной форме и сосчитать в регистр управ20526210

ления лишь J - 1 первых разрядов этого номера.

Например, L 2 16, возьмем шестую строку. В двоичной форме но5 мер строки есть 0110. Тогда начальное состояние для второго регистра сдвига 17 выберем 11, а последовательность имеет вид 011. В процессе функционирования устfO ройства тактовые импульсы с шестого выхода блока 16 управления поступают на вход второго регистра 17 сдвига и коммутирующего блока 20. Первоначально последовательность,

55 записанная во второй регистр 17 сдвига, через первый элемент И группы 18, элемент. ИЛИ 19 суммируется по модулю два с первым элементом управляющей последовательности,

20 записанной в регистр 21 управления, в сумматоре 22 по модулю два.

Полученные элементы сигнала записывают снова во второй регистр 17 сдвига. Таким образом, сформиро25 ваны четыре элемента сигнала. Коммутирующий блок 20 подсчитьшает число тактовых импульсов и через

3€

35

2 тактов, где , , открьшает и переносит единичное значение на вход f-ro элемента И группы 18 (на элементах Ис1по(-1).и с (f + 1) по группы 18 действует нулевое значение) и сдвигает на один такт управляющую последовательность, записанную в регистре 21

40

45

управления, Таким образом, через L - 1 такт сформируется одна из строк матрицы Адамара размерностью L, которая запишется в L ячейках памяти второго регистра 17 сдвига.

Через L - 1 такт коммутирующий блок 20 формирует- на своем выходе единичное значение, которое действует на третьем входе элемента И 23.

При поступлении из блока 7 по четвертому выходу в блок 8 и блок 16 управления сигнала Конец формирования группы блок 8 кодообразо- вания начинает считывание во второй сумматор 24 по модулю два кода псевдослучайной последовательности, а блок 16 управления формирует единичное значение на своем пятом выходе, тем самым разрешая прохождение на 55 второй сумматор 24 по модулю два через элемент И 23 задакицего ортогонального сигнала. Таким образом на выходе второго сумматора 24 по мо50

3

соединены с входами блока 7 умножения и входами блока 9 элементов выходы которого соединены с входам блока 11 памяти, первьш вход которого соединен с четвертым выходом программного блока 13, пятьй выход которого соединен с вторым входом блока 11 памяти, первым входом делителя Ю частоты и первым входом второго счетчика 2, выходы которого соединены с группой входов де-. лителя 10 частоты, выход которого соединен с входом блока 9 элементов И. Первый выход блока 7 умножения соединен с входом формирователя 6 остатков, группа входов которого соединена с выходами третьего блока 5 коммутации. Второй выход блока 7 умножения соединен с первым входом регистра 14 сдвига и с первым входом счетчика 1, второй вход которого соединен с вторым входом ре- |гистра 14 сдвига, первым входом блока 7 умножения и вторым выходом программного блока 13, первый выход которого соединен с вторым входом блока 7 умножения, группа выходов которого соединена с группой входов блока 8 кодообразова 1ия, первый вход которого соединен с вторым входом блока 16 управления и четвертым выходом блока 7 умножения пятый выход которого соединен с вторым входом счетчика 2 и вторым входом блока 8 кодообразования, третий вход которого соединен с третьим входом блока 7 умножения и выходом блока 12 хранения, входы которого соединены с входами блока 16 управления, выходами программно- го блока 13 и входами генератора j15, первый вьпсод которого соединен с входом блока 3 коммутации. Второй выход генератора 15 соединен с входом блока 4 коммутации, третий выход генератора 15 соединен с входом блока 5 коммутации. Выход блока 11 памяти соединен с четвертым входом блока 7 умножения. Шестой выход программного блока соединен с четвертым входом блока 8 кодообразования, первый выход которого соединен с входом программного блока 13. Второй выход блока 8 кодообразования соединен с входом сумматора 24 по модулю два. Первый выход блока 16 управления соединен с входом регистра 17 сдвига, выходы которого через элементы И группы 18

05262

соединены с входами элемента ИЛ выход которого соединен с первым входом сумматора 22 по модулю два, второй вход которого соединен с 5 выходом регистра 21 управления. Группа выходов коммутирующего блока

20соединена с входами элементов И группы 18. Первый вход регистра

21управления соединен с четвертым Q ВЫХОДОМ блока 16 управления, второй выход которого соединен с первым входом коммутирующего блока 20, второй вход которого соединен с трет ьим выходом блока 16 управления,

5 шестой выход которого соединен с третьим входом коммутирующего блока 20 и соответствующим входом регистра 17 сдвига, вход которого соединен с выходом сумматора 22

0 по модулю два и первым входом элемента И 23, второй вход которого соединен с пятым выходом блока 16 управления. Первый выход коммутирующего блока 20 соединен с вторым

5 входом регистра 21 управления. Второй выход коммутирующего блока 20 соединен с третьим входом элемента И 23, выход которого соединен с входом сумматора 24 по модулю два.

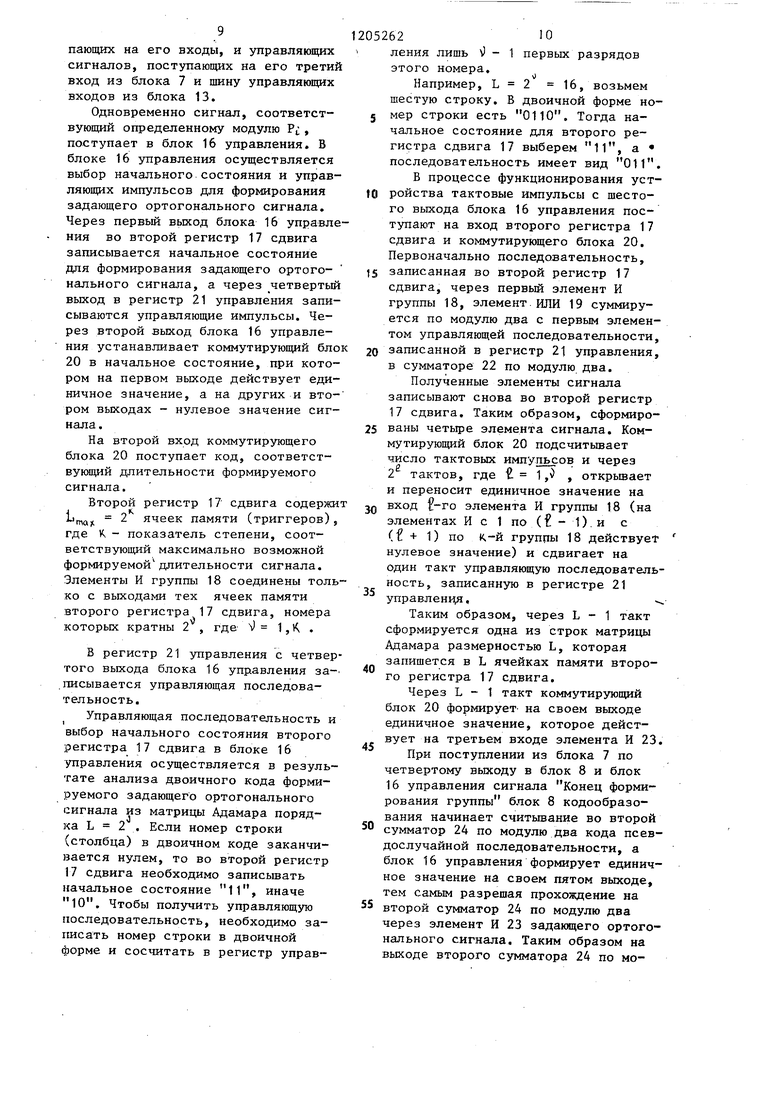

Q Блок 16 управления (фиг. 2)

содержит последовательно соединенные регистр 25 памяти и дешифратор 26, первый элемент И 27, элемент НЕ 28, второй элемент И 29, первый счетчик 30, третий элемент И 31, группу 32

элементов И, группу регистров 33 начального состояния, второй счетчик 34, первый триггер 35, генератор 36 тактовых импульсов, группу регистров 37 управления длительностью сигнала, втчэрой элемент ИЛИ 38, четвертый элемент И 39, первый элемент ИЛИ 40, последовательно соединенные дискретный согласованный фильтр 41 и второй триггер 42, а также элемент И 43. Выходы дешифратора 26 соединены с первыми входами элементов И группы 32,вторые входы которых соединены с входом регистра 25 памяти и выходом элемента И 29, вход которого соединен с выходом счетчика 30, вход которого соединен с выходом генератора 36, вторым входом элемента И 29, входом элемента И 31, входом триггера 35 и входом

5 счетчика 34, выход которого через элемент И 31 соединен с входом элемента И 43 и входом элемента И 27, выход которого соединен с входом

0

5

0

первого регистра 33 начального состяния группы, выход которого через элемент ИЛИ 38 соединен с входом элемента И 39, второй вход которого соединен с выходом триггера 35. Выход элемента И 43 соединен с входом второго регистра 33 начального состояния группы, выход которого соединен с входом элемента ИЛИ 38. Первый выход регистра 25 памяти соединен с входом элемента И 27 непосредственно, а с входом элемента И 43 - через элемент НЕ 28, Выходы элементов И 32 группы соединены соответствующими регистрами 37 управления длительностью сигнала, выходы которых соединены с входами элемента ИЛИ 40.

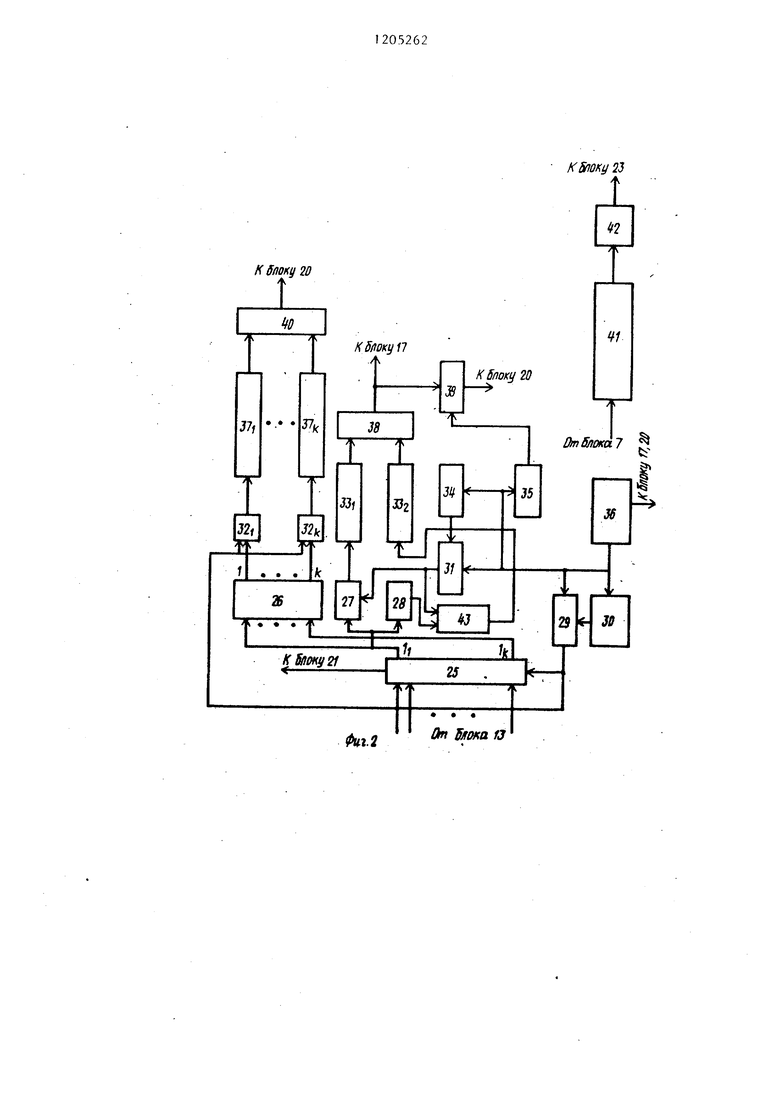

Коммутирующий блок 20 (фиг. 3) содержит регистр 44, счетчик 45, певую группу элементов И 46, первый элемент ИЛИ 47, вторую группу элементов И 48, группу элементов НЕ 49 регистр 50 длительности, последовательно соединенные второй элемент ИЛИ 51 и триггер 52. Входы второго элемента ИЛИ 51 соединены с выходами элементов И 48, первые входы которых соединены с выходами первой группы выходов регистра 44, вторая группа выходов которого соединена с первыми входами элементов И 46, вторые входы которых соединены с выходами регистра 50 длительности и входами элементов НЕ 49, выходы которых соединены с вторыми входами элементов И 48, третьи входы элементов И 46 соединены с выходами счетчика 45. Выходы элементов И 46 соединены с входами элемента ИЛИ 47, выход которого соединен с первым входом регистра 44, второй вход которого соединен с вторым входом триггера 52.

Устройство для формирования псевдослучайных сигналов (фиг. 1) работает следующим образом.

В соответствии с заданной программой блок 13 выдает сигнал по одному из своих третьих выходов, каждый из которых соответствует определенному модулю Р, и наименьшему первообразному эле менту 0 поля GF(P). По одному из этих сигналов на одном из своих входов блок 12 выдает в блок 8 и делитель 10 код модуля Р , а в блок 7 - код модуля

Р, и код первообразного элемента 0;. По поступлении сигнала на один из своих входов генератор 15 форми- рует на каждом из своих выходов серии управляющих импульсов, которые соответствуют длине N Р,; - 1 . Эти серии импульсов поступают на управляющие входы блоков 3-5 коммутации, которые под их воздействием осуществляют коммутацию определенного числа, соответствующего длине серии N, своих входов и выходов. Кроме того, блок 13 в тот же момент

сигналом по одному из выходов приводит в исходное нулевое состояние делитель 10, блок 11 и счетчик 2. Формирователи 6 остатков предназначены для формирования остатка по

определенному модулю Р{ от поступающего на него кода числа с выхода блока 7. В процессе функционирования устройства в целом тактовые импульсы поступающие с второго выхода блока

13 на входы счетчика 1 и регистра 14, сопровождают импульсы кода сравниваемого по модулю PL числа, поступающего с выхода блока 7 на входы формирователей 6. Количество состояний счетчика 1 определяется из рассмотрения остатка от деления веса каждого разряда сравниваемого числа на выбранный модуль Pi . Если получаемая последовательность цифр

имеет период повторения, то количество состояний счетчика 1 равно количеству цифр в периоде.

Если результат от деления представляет некоторую последовательность цифр без периода, то количество состояний счетчика 1 равно количеству разрядов в передаваемом числе, т.е. определенное число выходов (разрядов) счетчика 1 соответствует определенному модулю Р и, следовательно, определенному формирователю 6 остатков. Блок 3 коммутации осуществляет под воздействием определенной, соответствующий модулю PI , серии входных управляющих импульсов коммутацию определенных выходов счетчика 1 с определенными входами формировад елей 6. Выходные сигнЕшы с формирователей 6, при наличии тактовых импульсов на другом входе регистра 14, должны запоминаться в последнем, который имеет количество разрядов, необходи11

дулю два формируется производный сигнал.

Блок 16 управления (фиг. 2) работает следующим образом.

Код длительности формируемого сигнала поступает на регистр 25 памяти в параллельном коде и записывается в него. Дешифратор 26 анализирует поступивший код и выдает на одном из своих выходов единичное значение, соответствующее показателю степени формируемого сигнала. Одновременно с первого выхода регистра 25 памяти на вход элемента И 27 и элемента НЕ 28 действует нулевое или единичное значение сигнала. Если в первой ячейке памяти регистра 25 записана единица, то через элемент И. 27 проходит два тактовых импульса, которые считают начальное состояние 11 с регистра 33 начального состояния и элемент ИЛИ 38 во второй регистр 17 сдвига. Если в первой ячейке памяти регистра 25 памяти записан ноль, то на выходе элемента НЕ 28 будет едини- . ца, а на выходе элемента И 27 - ноль и тактовые импульсы пройдут через элемент И 43 на регистр 33 начального с остояния, где хранится начальное состояние 10. Число тактовых импульсов, которое необходимо пропустить через элемент И 31, подсчитывает счетчик 34 импульсов, Счетчик 30 считает мо модулю К + 1 и разрешает прохождение через элеме И 29 К - 1 тактовых импульсов от генератора 36 тактовых импульсов. Тем самым в коммутирующий блок 20 записьшается (через блоки 32, 37 и 40) управляющая последовательност длительности сигнала, а в регистр 21 управления управляющая последовательность. Триггер 35 первоначально находится -в единичном состоянии и разрешает прохождение одной единицы с элемента ИЛИ 38 в коммутирующий блок 20.

При поступлении первого тактовог импульса на вход триггера 35 он переходит в нулевое состояние и зак рьшает элемент И 39.

При приеме кода сигнала Конец формирования группы на выходе дискретного согласованного фильтра 41 -появляется импульс, который перевод триггер 42 в единичное состояние из нулевого. Необходимо отметить, что формирование ортогонального

0526212

задающего сигнала должно закончить- ся раньше или одновременно с формированием псевдослучайной последовательности.

5 Коммутирующий блок 20 (фиг. 3) работает следующим образом.

Из блока 16 управления в первоначальный момент времени в регистр 44 записывается в К-и элемент па10 мяти единица, в остальные ячейки памяти записаны нули.

В регистр 50 длительности записывается управляющая последовательность, содержащая к - v первых ну15 лей и i последующих единиц. Триггер 52 устанавливается в нулевое состояние. При поступлении на вход коммутирующего блока 20 тактовых импульсов счетчик 45 начинает под20 считьшать их. Так как на входе

элемента И 46 действует единичное значение, то через два тактовых импульса на выходе К-той ячейки . памяти счетчика 45 импульсов появ25 ляется единичный импульс, который через К-и элемент И 46, элемент ИЛИ 47, переписьшает единицу в регистре 44 в К- 1 элемент памяти и поступает на вход регистра 21

3Q управления, производя сдвиг на один элемент управляющей последовательности. Импульс перезаписи единицы

р в регистре 44 врзникает каждые 2

тактов, f 1, О . Одновременно содержимое ячеек памяти регистра 44 сравнивается с содержимым ячеек памяти регистра 50 длительности, причем К- ячейка регистра 44 сравнивается с К,- f. - 1 ячейкой регистра 50 длительности.

5

0

После того, как счётчик 45 под- считвает L - 2 2 - испульсов (тактов) в регистре 44, единица находится в К- ) + 1 ячейках памяти, а сравнение производится с . К, - ячейкой памяти регистра 50 длительности, в которую записан ноль. Тем самым через ( К- )-й элемент НЕ группы 49 на вход ( К, vj + 1)-го элемента И группы 48

действует единичное значение, которое через элемент ИЛИ 51 переводит триггер 52 в единичное состояние и разрешает прохождение сформированного ортогонального сигнала на второй сумматор 24 по модулю два через элемент И 23 с второго регистра 17 сдвига.

г.З

l frj§maw К8ту23

/(Smy2l

От SMKU 1S

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования псевдослучайных сигналов | 1979 |

|

SU995292A1 |

| Устройство для формирования имитостойких последовательностей сигналов сложной формы | 1984 |

|

SU1203533A1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| Устройство для формирования последовательности дискретно-частотных сигналов | 1991 |

|

SU1820393A1 |

| Устройство для формирования последовательностей дискретно-частотных сигналов | 1988 |

|

SU1541627A1 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| Устройство для формирования элементов расширенных полей Галуа GF ( @ ) и кодовых последовательностей на их основе | 1987 |

|

SU1441413A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПЕРВООБРАЗНЫХ ЭЛЕМЕНТОВ КОНЕЧНЫХ ПОЛЕЙ | 1991 |

|

RU2020755C1 |

| СПОСОБ ТРАНСЛЯЦИОННОГО УСЛОЖНЕНИЯ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ В ВИДЕ КОДОВ КВАДРАТИЧНЫХ ВЫЧЕТОВ, СУЩЕСТВУЮЩИХ В ПРОСТЫХ ПОЛЯХ ГАЛУА GF(p), И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2669506C1 |

| Устройство для контроля программных автоматов | 1988 |

|

SU1571552A1 |

| Устройство для формирования псевдослучайных сигналов | 1979 |

|

SU995292A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-01-15—Публикация

1984-06-19—Подача