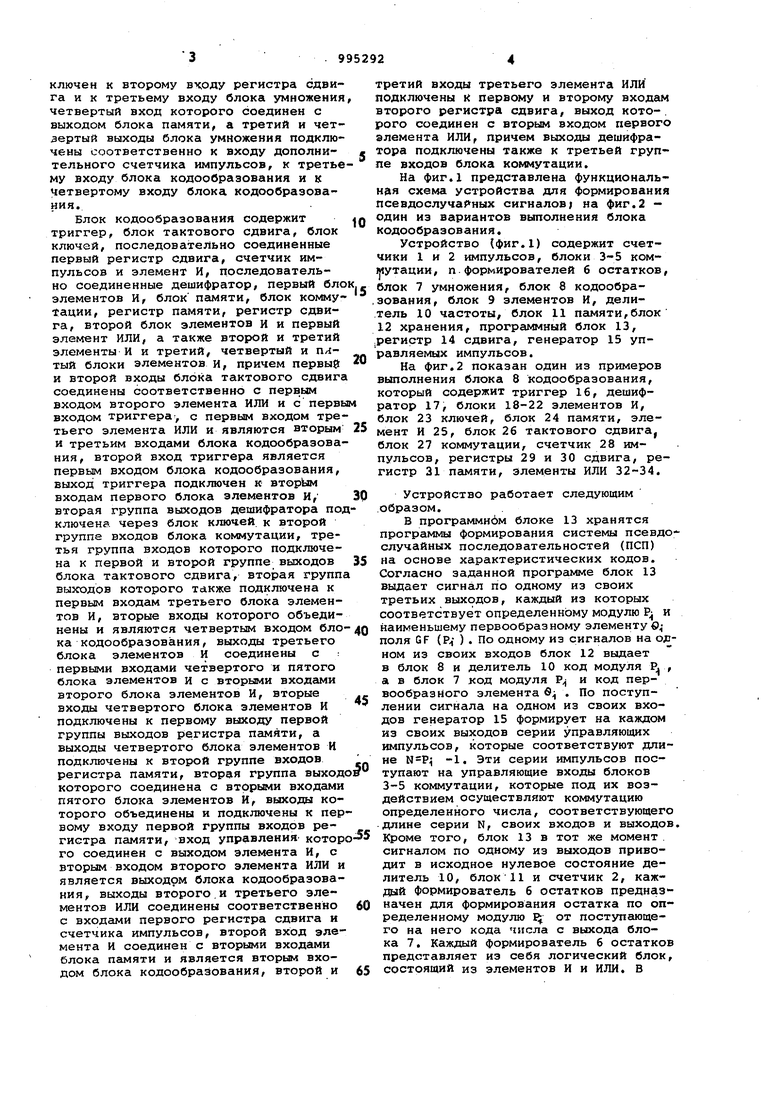

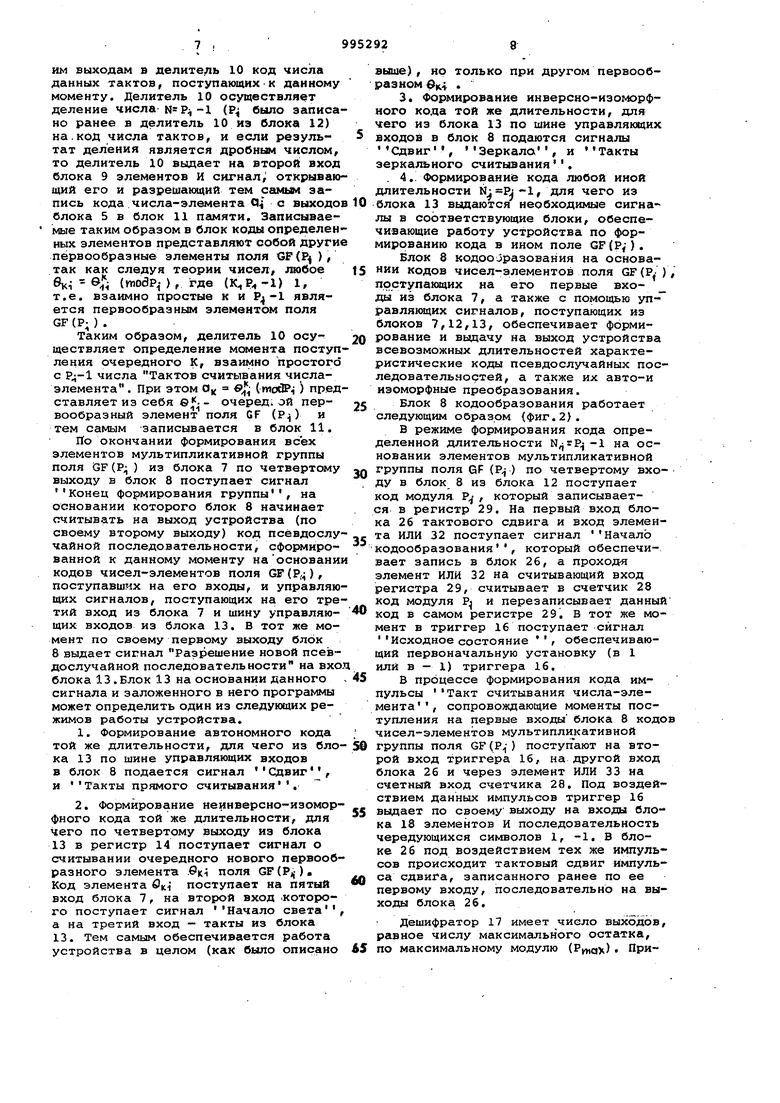

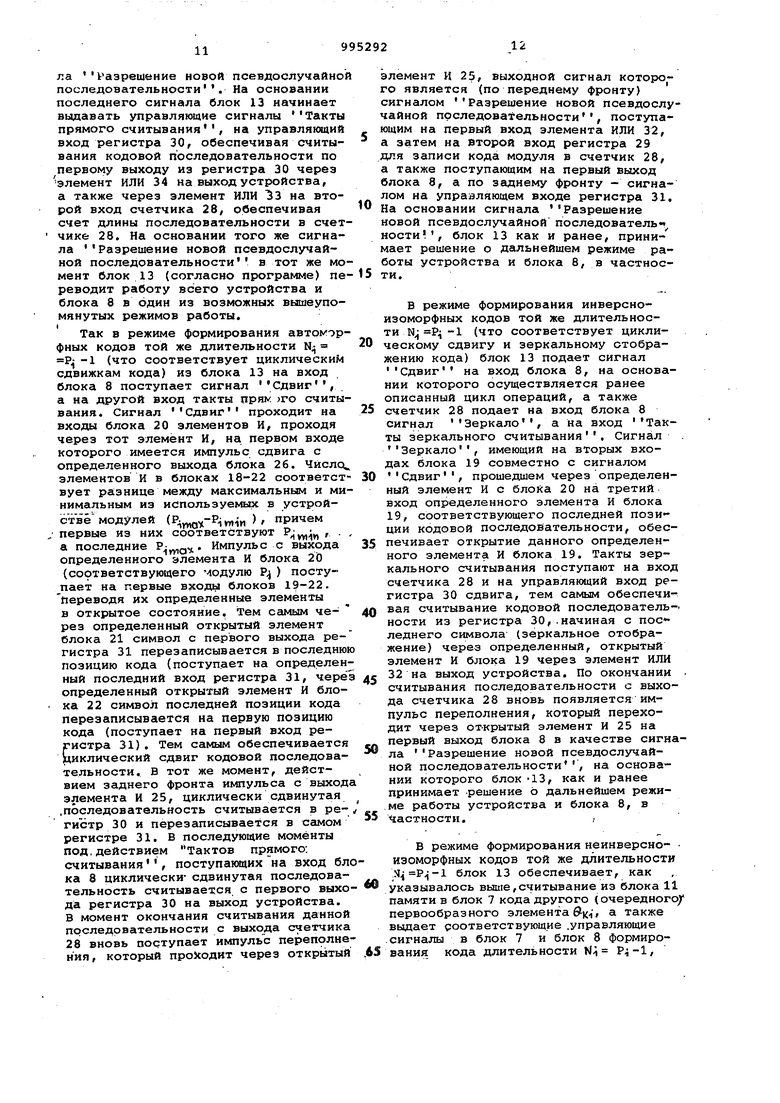

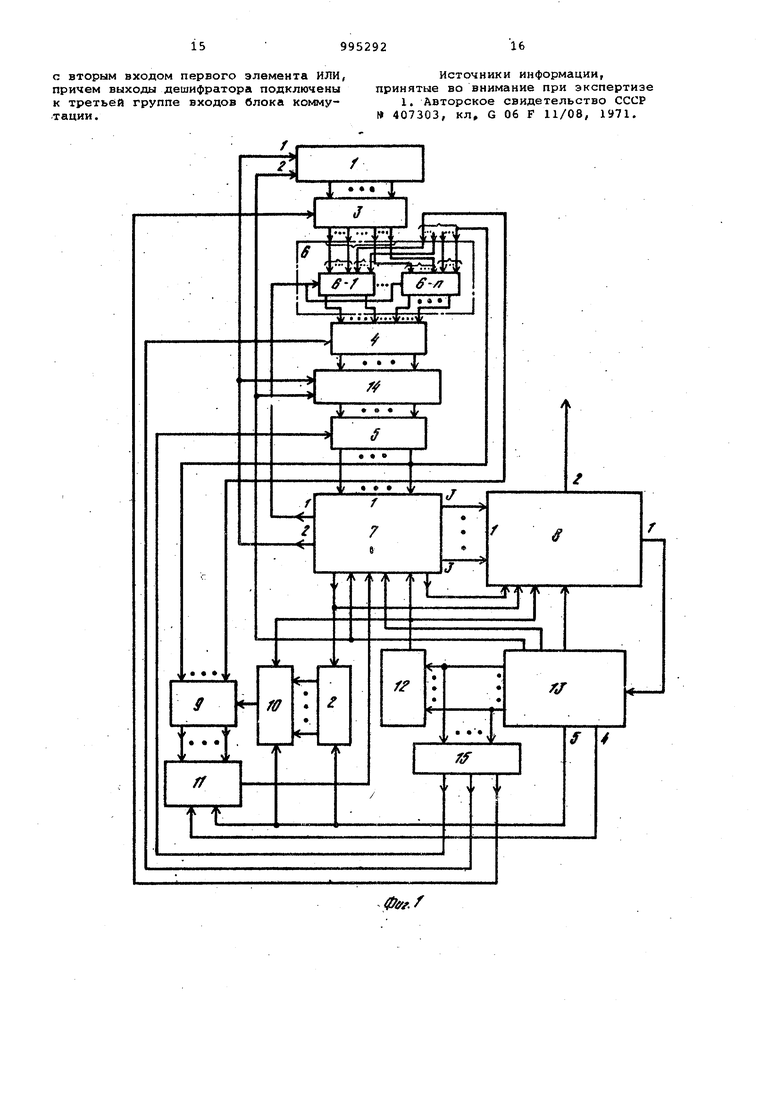

ключей к второму входу регистра сдвига и к третьему входу блока умножения четвертый вход которого соединен с выходом блока памяти, а третий и четаертый выходы блока умножения подключены соответственно к входу дополни тельного счетчика импульсов, к третье му входу блока кодообразования и к четвертому входу блока кодообразования. Блок кодообразования содержит триггер, блок тактового сдвига, блок ключей, последовательно соединенные первый регистр сдвига, счетчик импульсов и элемент И, последовательно соединенные дешифратор, первый бло элементов И, блок памяти, блок коммуtauHH, регистр памяти, регистр сдвига, второй блок элементов и и первый элемент ИЛИ, а также второй и третий элементы И и третий, четвертый и пятый блоки элементов и, причем первый и второй входы блока тактового сдвига соединены соответственно с первым входом второго элемента ИЛИ и с первы входом триггера, с первым входом тре тьего элемента ИЛИ и являются вторым и третьим входами блока кодообраэова ния, второй вход триггера является первьм входом блока кодообразования, выход триггера подключен к втор1ым входам первого блока элементов И, вторая группа выходов дешифратора по ключена через блок ключей к второй группе входов блока коммутации, третья группа входов которого подключена к первой и второй группе выходов блока тактового сдвига, вторая групп выходов которого также подключена к первым входам третьего блока элементов И, вторые входы которого объединены и являются четвертым входом бло ка кодообраэования, выходы третьего блока элементов И соединены с : первыми входами четвертого и пятого блока элементов и с вторыми входами второго блока элементов И, вторые входы четвертого блока элементов И подключены к первому вьлходу первой группы выходов регистра памяти, а выходы четвертого блока элементов И подключены к второй группе входов регистра памяти, вторая группа выход которого соединена с вторыми входами пятого блока элементов И, выходы которого объединены и подключены к пер вому входу первой группы входов регистра памяти, вход управления котор го соединен с выходом элемента И, с вторым входом второго элемента ИЛИ и является ВЫХОД9М блока кодообразования, выходы второго.и третьего элементов ИЛИ соединены соответственно с входами первого регистра сдвига и счетчика импульсов, второй вход элемента И соединен с вторыми входами блока памяти и является вторым входом блока кодообразования, второй и третий входы третьего элемента ИЛИ подключены к первому и второму входам второго регистра сдвига, выход кото-, рого соединен с вторым входом первого элемента ИЛИ, причем выходы дешифратора подключены также к третьей группе входов блока коммутации. На фиг.1 представлена функциональная схема устройства для формирования псевдослучайных сигналов; на фиг.2 один из вариантов выполнения блока кодообразования. Устройство (фиг.1) содержит счетчики 1 и 2 импульсов, блоки 3-5 ком1}1утации, п. формирователей 6 остатков, блок 7 умножения, блок 8 кодообразования, блок 9 элементов И, делитель 10 частоты, блок 11 памяти,блок 12 хранения, программный блок 13, регистр 14 сдвига, генератор 15 управляемых импульсов. На фиг.2 показан один из примеров выполнения блока 8 кодообразования, который содержит триггер 16, дешифратор 17, блоки 18-22 элементов И, блок 23 ключей, блок 24 памяти, элемент И 25, блок 26 тактового сдвига, блок 27 коммутации, счетчик 28 импульсов, регистры 29 и 30 сдвига, регистр 31 памяти, элементы ИЛИ 32-34. Устройство работает следующим образом. В программном блоке 13 хранятся программы формирования системы псевдослучайных последовательностей (ПСП) на основе характеристических кодов. Согласно заданной программе блок 13 выдает сигна.л по одному из своих третьих выходов, каждый из которых соответствует определенному модулю PJ и наименьшему первообразному элементу в.,поля GF (Р.,- ) . По одному из сигналов на одном из своих входов блок 12 выдает в блок 8 и делитель 10 код модуля Р. , а в блок 7 код модуля Р и код первообразного элемента в . По поступлении сигнала на одном из своих входов генератор 15 формирует на каждом из своих выходов серии управляющих импульсов, которые соответствуют длине -1. Эти серии импульсов поступают на управляющие входы блоков 3-5 коммутации, которые под их воздействием осуществляют коммутацию определенного числа, соответствующего длине серии N, своих входов и выходов. Кроме того, блок 13 в тот же момент . сигналом по одному из выходов приводит в исходное нулевое состояние делитель 10, блок 11 и счетчик 2, каждый формирователь 6 остатков предназначен для формирования остатка по определенному модулю от поступающего на него кода числа с выхода блока 7. Каждый формирователь б остатков представляет из себя логический блок, состоящий из элементов И и ИЛИ. В процессе функционирования устройства в целом тактовые импульсы, поступаюи с второго выхода блока 13 на входа счетчика 1 и регистра 14 сопровождают импульсы кода, сравниваемого по мо дулю В числа, поступающего с выхода блока 7 на вход формирователя 6. Количество состояний счётчика 1 определяется из рассмотрения остатка от деления веса каждого разряда срав ниваемрго числа на выбранный модуль Р;. Если получаемая прследовательность цифр имеет период повторения, то количество состояний счетчика 1 равно количеству цифр в периоде. Если результат от деления представля feT некоторую последовательность цифр без периода, то количество состояний счетчика 1 равно количеству разрядов в передаваемом числе, . определен ное. число выходов (разрядов) счетчика 1 Соответствует опред1еленному 14одулю Р. и, следовательно определенному формирователю 6 остатков. Влок 3 коммутации осуществляет под воздействие определенной, соответствующий модулю Р серии входных управляющих импульсов, коммутацию oir ределынных выходов счетчика 1с определенными входами формирователей 6. Выходные сигналы с фоцяушрователей 6 при наличии тактовых имЛульсов на другом входе регистра 14 должны запоминаться в последнем, который т«еет количество разрядов, необходимое , для представления максимального остатка по максимальному модулю Р, . При этом каждому триггеру регистра 14 должно, соответствовать два элемента ИЛИ любого формирователя б остатков (для установки в О и в ) причем каждому элементу ИЛИ последнего должносоответствовать такое число элементов и, сколько воз можных ситуаций приводит к переводу одного триггера регистра 14 в соРтветствующее состОяние. А так как у каждого формирователя б остатков име ется свое определенное число элёментов ИЛИ, которые соответствуют onредёлеиному числу триггеров регистра 14, то блок 4 коммутаций, подобно блоку 3 коммутации, и осуществляет под воздействием определенной, соответдтвующей модулю Р серии входных коммутирующих импульсов, коммутацию определенных выходов формирова те ёй б с определенными входгми регистра. Так как для формирования остатков от числа по определенному.МОДУЛ Р| эадействуется определепное число триггеров регистра 14 и определенный формирователь 6 остатков, то при этом должно быть обеспечено соединение других входов определенного формирователя 6 остат ков с выходами определенного числа триггеров регистра 14. Эту функцию выполняет блок 5 коммутации под воздейс вием определенной, соответствующей модулю , серии управляющих импульсов. Таким образом, с поМощью генератора 15, счетчика 1, формирователей б, регистра 14, блоков 3-5, реализуется функция нахождения остатков от двоичных чисел, поступающего с первого выхода блока 7 на третий вход формирователя 6, по любомуиз п Модулей Р , на которые рассчитано уст- ройство. Блок 7 предназначен для умножения двух чисел для формирования . мультипликативной группы полявР(Р ), имеющий вид последовательности чисел (wioapj); ai50 Cwiodp X a- e C odRi),..., , где - первообразный элемент поля dF(P ) . Для чего перед началом работы из блока 12 в блок 7 пос-г тупают на четвертый вход код модуля Р код наименьшего первообразного элемента е,,.; поляСР(Р4), из блока 13 в блок 7 поступают тактовые импульсы Начало счета. Для получения каждого последующего числа-элемента. мультипликативной группы блок 7 обеспечивает умножение предшрущего числа элемента а , код которого поступает на его первые входы с выходов блока 5 коммутации на первообразный элемент в поля и по своему первому-выходу выдает в двоичном последовательном коде число AiCl.J..,e,sa(WoaPi), где , .( AvQa&i a,,ftriodPi)...,- ар.-ав5« Р1-/ «оарД которые поступают последовательно в формирователи б. Перед моментом : выдачи очередного числа А в формирователи б, по третьим выходам блок 7 выдает в блок 8 кодообразования код числа-элемента , а по пятому выходу в блок 8 и блок 11 сигнал Такт считывания числа элемента, а с второго выхода блока 7 на первые входы счетчика 1 и регистра 14 поступает сигнал Конец умножения, приводящий в исходное нулевое состояние счетчик 1 и регистр 14, подготавливая их .для работы по отысканию очередного оотаткаа.; « А.; (гхзЙР,-) . В следующий момент с первого йыхода блока 7 в формирователи 6 считывает- ся код числа А . Счетчик 2 с каждым сигналом Такт считывания числа-элемента, поступающим на его первый вход с выхода блока 7, выдает по своим выходам в делитель 10 код числа данных тактов, поступающих к данному моменту. Делитель 10 осуществляет деление числа ,-1 (Р было записа но ранее в делитель 10 из блока 12) на.код числа тактов, и если результат деления является дробным числом, то делитель 10 выдает на второй вход блока 9 элементов И сигнал открываю щий его и разрешакхций тем самым запись кода числа-элемента 0 с выходо блока 5 в блок 11 памяти. Записываемые таким образом в блок коды определен ных элементов представляют собой други первообразные элементы поля GF(Р| }, так как следуя теории чисел, любое - ®4 (гооар -)ггде (,-1) 1, т.е. взаимно простые к и является первообразным элементом поля GF (Р;) . Таким образом, делитель 10 осуществляет определение мсилента поступ ления очередного К, взаимно простого с числа Тактов считывания числаэлемента . При этом а, & (гиойР, ) пред ставляет из себя очередной первообразный элемент поля GF (Р) и тем самым записывается в блок 11. rto окончании формирования всех элементов мультипликативной группы поля GF(Р ) из блока 7 по четвертому выходу в блок 8 поступает сигнал Конец формирования группы, на основании которого блок 8 начинает считывать на выход устройства (по своему второму выходу) код псёвдослу чайной последовательности, сфоютированной к данному моменту наосновани кодов чисел-элементов поля GF(P(4), поступавших на его входы, и управляю щих сигналов, поступающих на его тре тий вход из блока 7 и шину управляющих входов из блока 13. В тот же момент по своему первому выходу блок 8 выдает сигнал Разрешение новой псевдослучайной последовательности на вхо блока 13.Блок 13 на основании данного сигнала и заложенного в него программы может определить один из следующих режимов работы устройства. 1. Формирование автономного кода той же длительности, для чего из бло ка 13 по шине управляющих входов в блок 8 подается сигнал Сдвиг, Такты прямого считывания. 2. Формирование неинверсно-изоморфного кода той же длительности, для чего по четвертому выходу из блока 13 в регистр 14 поступает сигнал о считывании очередного нового первообразного элемента. & поля GF(Pj) Код элемента поступает на пятый вход блока 7, на второй вход .которого поступает сигнал Начало света а на третий вход - такты из блока 13. Тем самым обеспечивается работа устройства в целом (как было описано выще), но только при другом первообраз ном вк-v 3. Формирование инверсно-изоморфного кода ТОЙ же длительности, для чего из блока 13 по шине управляющих входоа в блок 8 подаются сигналы Сдвиг, Зеркало, и Такты зеркального считывания. . 4. Формирование кода любой иной длительности , для чего из блока 13 выдаются необходимые сигна лы в соответствующие блоки, обеспечивающие работу устройства по формированию кода в ином поле GF(P). Блок 8 кодооОразования на основании кодов чисел-элементов поля GF(P.-), прступакндих на его первые вхо- ,цы из блока 7, а также с помощью управляющих сигналов, поступающих из блоков 7,12,13, обеспечивает формирование и вьщачу на выход устройства всевозможных длительностей характеристические коды псевдослучайных последовательностей, а также их авто-и изоморфные преобразования. Блок 8 кодообразования работает следующим Образом (фиг.2). В режиме формирования кода определенной длительности N P -1 на основании элементов мультипликативной группы поля GF (Р) по четвертому входу в блок 8 из блока 12 поступает код модуля. Р , который записывается в регистр 29. На первый вход блока 26 тактового сдвига и вход элемента ИЛИ 32 поступает сигнал Начало кодообразования, который обеспечивает запись в бЛок 26, а проходя элемент ИЛИ 32 на считывающий вход регистра 29, считывает в счетчик 28 код модуля Р и перезаписывает данный код в самом регистре 29. В тот же момент в триггер 16 поступает сигнал Исходное состояние , обеспечивающий первоначальную установку (в 1 или в - 1) триггера 16. В процессе формирования кода импульсы Такт считывания числа-элемента , сопровождающие моменты поступления на первые входы блока 8 кодов чисел-элементов мультипли кативной группы поля GP ( ) поступают на второй вход триггера 16, на другой вход блока 26 и через элемент ИЛИ 33 на счетный вход счетчика 28. Под воздействием данных импульсов триггер 16 выдает по своему выходу на входы блока 18 элементов И последовательность чередующихся символов 1, -1. В блоке 26 под воздействием тех же импульсов происходит тактовый сдвиг импульса сдвига, записанного ранее по ее первому входу, последовательно на выходы блока 26. Дешифратор 17 имеет число выходов, равное числу максимального остатка, по максимальному модулю (Ркиа) Причём каждый из последних выходов дешифратора 17, соединенных с входами блока 23 ключей, соответствует определенному числу PJ -I.

Перед началом работы блока 8 из блока 7 на первые входы блока 8 в дешифратор 17. поступает код числа Рд-1. Сигнал на соответствующем из последних его выходах записывается в блок 8 по соответствующему входу. . .

Дешифратор 17 дешифрирует очередной Ю код числа элемента а, поступающего на его входы таким образом что определенному числу соответствует импульс на определенном его выходе (аналогичном месту нахождения данного tS числа в натуральном ряде чисел).

Таким образом, в каждый .Такт считывания числа-элемента, с определенного выхода дешифратора 17 появляе ся импульс, поступающий на второй вход определенного элемента И блока 18 и открывает его. Символ 1 или -1 с выхода триггера 16 проходит через определенный элемент И блока 18 и записывается в определенную ячейку 25 памяти блока 24. Кроме того, импульс с определенного выхода дешифратора 17 поступает на вторые входы блока 27, причем номер элемента блока 27 на единицу превышает номер дешифратора 30 17. В тот же момент с определенного выхода блока 26, соответствующего Такту считывания числа-элемента , поступает импульс сдвига на соответствующий определенный вход всех эле- 35 ментов блока 27. Тем самым при суще.ствовании сигналов одновременно на двух входах определенных элементов блока 27 определенный 12-(К+1) элемент коммутации коммутирует свой 40 первый вход, соединенный с выходом (9-К)-й ячейки памяти блока 24, с своим выходом, соединенным с i-м выходом блока 27. Причем, при поступлении на входы дешифратора 17 кода 45 числа-элемента а -1 на соответствующем его выходе, соединенном с соответствующим входом с блока 8, по которому ранее был уже записан импульс, появляется импульс, который JQ открывает соответствующий ключ блока 8, (т.е. по приходе только двух импульсов на соответствующем входе блока 8 открывается соответствующий ключ) И с выхода блока 8 на третьи входы .. блока 27 поступает импульс, который совместно с импульсом с выхода блока 26, обеспечивает коммутацию первого входа определенного элемента коммутации с определенным выходом блока 27 ... Необходимость введения с блоки 8, связанного определенным образом с последними выходами дешифратора 17 и третьими входами с блока 27, вызвано тем, что для обеспечения выполнения выше описанного правила кодирования,

вторые .входа первых элементов блока 27 должны быть соединены с одним иэ последних выходов дешифратора 17, соответствующими числу , тем самым будет обеспечено взаимно-однозначное соответствие (по набору чисел натурального ряда) между числами

;с|:,2вЧпюа Pi), Oj вV1{,юdPj) и их индексами. Действительно, если « Р4 -1; тоQX Pf -1+1 Р г в (Vnod3 i ). Индекса от О не существует и выхода дешифратора 17, соответствующего О, нет, поэтому для обеспечения соответ ствия между индексгши чисел q и q ai набор которых должен быть идентичен и введен блок 8.

Таким образом, в момент Такта считывания числа-элемеита, соответствуквдего последнему элементу мультипликативной группы поля GF( ) блоком 27 обеспечивается определенная коюлутация его первых входо и выходов, соответствующая правилу кодирования характеристических кодов и в момент поступления иэ элемента ИЛИ 32 на второй вход блока 18 сигнала Конец формирования , который проходит на вторые входы блока 24 и элемента И 25, из блока 8 списываются записанные значения символом (1, -1) через блок 27 Определенным образом, соответствукицим правилу кодирования на входы регистра 31 памяти, а сам блок 24 обнуляется и нулевым сигналом на своих выходах приводит в исходное состояние (срывает коммутацию) блок 27. При этом последний вход регистра 31, на котором существует информационный символ (1 или -1) соответствует определенному одному из последних выходов блока 26,на котором появился импульс сдвига при последнем Такте считывания чис|ла-элемента, и одному из последних

выходов дешифратора.17, соответствующего числу .

1 . Таким образом, в регистр 31 записывается кодовая последовательность длиной N . К этому моменту счетчик 28 под действием счетных импульсов Такт считывания числа-элемента, поступающих на его второй вход через з;лемент ИЛИ 33, с третьего входа блрка переполняется и выдает на вход элемента И 25 импульс переполнения. Два сигнала на обоих входах элемента И 25 открывают его и сигнал с его выхода поступает: на управлякидий вход регистра 31, обеспечивая считывание кода в регистр 30 сдвига и перезапись кода в самом регистре 31 через элемент ИЛИ 32 на вход регистра 29, обеспечивая запись кода модуля P,j в счетчик 28 и перезапись кода модуля в самом регистре 29, а также поступает на вход блока Б в качестве сигнапа Разрешение новой псевдослучайно последовательности. На основании последнего сигнала блок 13 начинает выдавать управляющие сигналы Такты прямого считывания , на управлякнций вход регистра 30, обеспечивая считывания кодовой последовательности по первому выходу из регистра 30 через элемент ИЛИ 34 на выход устройства, а также через элемент ИЛИ 3 на второй вход счетчика 28, обеспечивая счет длины последовательности в счет чике 28. На основании того же сигнала Разрешение новой псевдослучайной последовательности в тот же мо мент блок 13 (согласно программе) пе реводит работу всего устройства и блока 8 в один из возможных вышеупомянутых режимов работы. Так в режиме формирования автоморфных кодов той же длительности Ы (что соответствует циклическим сдвижкам кода) из блока 13 на вход блока 8 поступает сигнал Сдвиг, а на другой вход такты пряк. го считывания. Сигнал Сдвиг проходит на входы блока 20 элементов И, проходя через тот элемент И, на первом входе которого имеется импульс сдвига с определенного выхода блока 26. Чйсло элементов И в блоках 18-22 соответст вует разнице между максимальным и ми нимальным из используемых в устройстве модулей (P y y-Piwin ) f причем первые из них соответствуют , , а последние . Импульс с выхода определенного элемента И блока 20 (соответствующего модулю Р) поступает на первые входы блоков 19-22. переводя их определенные элементы в открытое состояние. Тем самым через определенный открытый элемент блока 21 символ с первого выхода регистра 31 перезаписывается в последню позицию кода (поступает на определен ный последний вход регистра 31, чере определенный открытый элемент И блока 22 символ последней позиции кода перезаписывается на первую позицию кода (поступает на первый вход регистра 31). Тем самым обеспечивается циклический сдвиг кодовой последовательности. В тот же момент, действием заднего фронта импульса с выход элемента И 25, циклически сдвинутая .последовательность считывается в регистр 30 и перезаписывается в самом регистре 31. В последующие моменты под,действием Тактов прямого; считывания, поступаквдих на вход бл ка 8 циклически- сдвинутая последовательность считывается с первого выхо да регистра 30 на выход устройства. В момент окончания считывания данной последовательности с выхрда счетчика 28 вновь поступает импульс переполне ния, который проходит через открытый элемент И 25, выходной сигнал котороо является (по переднему фронту) сигналом Разрешение новой псевдослуайной последовательности, поступащим на первый вход элемента ИЛИ 32, а затем на второй вход регистра 29 ля записи кода модуля в счетчик 28, а также поступающим на первый выход блока 8, а по заднему фронту - сигнаом на управляющем входе регистра 31. На основании сигнала Разрешение новой псевдослучайной последователь- ости, блок 13 как и ранее, приниает решение о дальнейшем режиме работы устройства и блока 8, в частноси. В режиме формирования инверсноизоморфных кодов той же длительности (что соответствует циклическому сдвигу и зеркальному отображению кода) блок 13 подает сигнал Сдвиг на вход блока 8, на основании которого осуществляется ранее описанный цикл операций, а также счетчик 28 подает на вход блока 8 сигнал Зеркало, а на вход Такты зеркального считывания Сигнал Зеркало, имеющий на вторых входах блока 19 совместно с сигналом Сдвиг, прошедшем через определенный элемент И с блока 20 на третий вход определенного элемента И блока 19, соответствующего последней позиции кодовой последовательности, обеспечивает открытие данного определенного элемента И блока 19. Такты зеркального считывания поступают на вход счетчика 28 и на управляющий вход регистра 30 сдвига, тем самым обеспечивая считывание кодовой последовательности из регистра 30,.начиная с пос леднего символа (зеркальное отображение) через определенный, открытый элемент И блока 19 через элемент ИЛИ 32 на выход устройства. По окончании считывания последовательности с выхода счетчика 28 вновь появляется импульс переполнения, который переходит через открытый элемент И 25 на первый выход блока 8 в качестве сигнала Разрешение новой псевдослучайной последовательности , на основании которого блок -13, как и ранее принимает решение 6 дальнейшем режиме работы устройства и блока 8, в Частности., В режиме формирования неинверсно- изоморфных кодов той же длительности , блок 13 обеспечивает, как указывалось выше,считывание из блока 11 памяти в блок 7 кода другого (очередного/ первообразного элемента ° также выдает соответствующие .управляющие .сигналы в блок 7 и блок 8 формирования кода длительности Mi Pi-1/

НО при другом первообразном. Алгоритм работы блока 8 в этом случае аналогичен алгоритму работы при наименьшем первообразном , который был описан ранее.

Таким образом, предлагаемое устройство, по сравнению с известным, позволяет расширить функциональные возможности.

Формула изобретения

1. Устройство для формирования псевдослучайных сигналов, содержгицее счетчик импульсов, регистр сдвига и формирователь остатков, отличающееся тем, что, с целью расширения функциональных возможностей, в него введены три блока коммутации, блок умножения, блок кодообразования программный блок, блок хранения программы, генератор управляемых импульсов, И-1 формирователей остатков и последовательно соединенные счетчик импульсов, делитель частоты, блок элементов И и блок памяти, второй и третий входы которого подключены соответственно к первым входгш делителя частоты и счетчика импульсов и к первому и второму выходам прогргилмного блока, третьи выходы которого через блок хранения програквлы подключен к второму входу делителя частоты к первому входу блока умножения и к первому входу блока кодообразования, а через генератор управляемых импульсов - к управляющим входам первого, второго и третьего блоков коммутации соответственно, выходы первого из которых соединены через последовательно подключенные vi формирователей остатков, второй блок коммутации, регистр сдвига и третий блок коммутации с разрядными входами блока умножения, с группой входов блока элементов И и с второй группой входов «формирователей остатков, причем входы первого блока коммутации соединены через основной счетчик импульсов с первым и вторым входами регистра сдвига и с первым и вторым выходами блока умножения, разрядные выходы которого подключены к разрядным входам блока кодообразования, выход которого соединен с входом программного блока, четвертый и пятый выходы которого соединены с вторым входом блока кодообразования и с вторым входом блока умножения, а шестой выход программного блока подключен к второму входу регистра сдвига и к третьему входу блока умножения, четвертый вход которого соединен с выходом блока памяти, а третий и четвертый выходы блока умножения подключены соответственно к входу дополнительного

рчётчика импульсов, к третьему входу блока кодообразования и к- четвертому входу блока кодообразования

2. Устройство по п.1, отличающее с я тем, что блок кодообразования содержит триггер, блок тактового сдвига, блок ключей, последовательно соединенные первый регистр,

0 сдвига, счетчик импульсов и элемент И, последовательно соединенные дешифратор, первый блок элементов И, блок памяти, блок коммутации, регистр памяти, регистр сдвига, второй блок элементов И и первый элемент ИЛИ, а также второй и третий элементы И и третий, четвертый и пятый блоки элементов И, причем первый и второй входы блока тактового сдвига соединены соответственно с первым входом второго элемента ИЛИ и с первым входом триггера, с первым входом третьего .элемента ИЛИ и являются вторым и третьим входами блока кодообразования, второй вход триггера является

5 первым входом блока кодообразования, выход триггера подключен к вторым входги 4 первого блока элементов И, вторая группа выходов дешифратора подключена через блок ключей к второй

0 группе входов блока коммутации, третья группа входов которого подключена к первой и второй группе выходов блока тактового сдвига, вторая группа выходов которого также подключена к первым входам третьего блока элементов И, вторые входы которого объединены и являются четвертым входом блока кодообразования, выходы третьего блока элементов И соединены с первыми входами четвертого и пятого блоков элементов И с вторыми входами второго блока элементов И, вторые входы четвертого блока элементов И подключены к первому выходу первойгруппы выходов регистра памяти, а выходы четвертого блока элементов И подключены к второй Группе входов регистра памяти, вторая группа выходов которого соединена с вторыми входс1ми пятого блока элементов и, выходы которого

0 объединены и подключены к первому входу первой группы входов регистра памяти, вход управления которого соединен с выходом элемента И, вторым , входом второго элемента ИЛИ и являет-: ся выходом блока кодообразования, выходы второго и третьего элементов ИЛИ соединены соответственно с входами первого регистра и счетчика импульсов, второй вход элемента И соединен с вторыми входами блока памяти, является вторым входом блока кодообразования,. второй и третий входы третьего элемента ИЛИ подключены к первому и второму входам второго регистра сдвига,выход которого соединен с вторым входом первого элемента ИЛИ, причем выходы дешифратора подключены к третьей группе входов блока комму,тации. Источники информации, принятые во внимание при экспертизе I. Авторское свидетельство СССР 407303, кл, G 06 F 11/08, 1971.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования псевдослучайных сигналов | 1984 |

|

SU1205262A2 |

| Устройство формирования систем двукратных производных кодовых дискретно-частотных сигналов | 2016 |

|

RU2626331C1 |

| СПОСОБ ТРАНСЛЯЦИОННОГО УСЛОЖНЕНИЯ НЕЛИНЕЙНЫХ РЕКУРРЕНТНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ В ВИДЕ КОДОВ КВАДРАТИЧНЫХ ВЫЧЕТОВ, СУЩЕСТВУЮЩИХ В ПРОСТЫХ ПОЛЯХ ГАЛУА GF(p), И УСТРОЙСТВО ДЛЯ ЕГО РЕАЛИЗАЦИИ | 2017 |

|

RU2669506C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| Устройство для формирования имитостойких последовательностей сигналов сложной формы | 1984 |

|

SU1203533A1 |

| Устройство для формирования элементов расширенных полей Галуа GF ( @ ) и кодовых последовательностей на их основе | 1987 |

|

SU1441413A1 |

| Устройство для формирования последовательности дискретно-частотных сигналов | 1991 |

|

SU1820393A1 |

| УСТРОЙСТВО ФОРМИРОВАНИЯ ИМИТОСТОЙКИХ СИСТЕМ ДИСКРЕТНО-ЧАСТОТНЫХ СИГНАЛОВ С ВРЕМЕННЫМ УПЛОТНЕНИЕМ ИНФОРМАЦИИ | 2011 |

|

RU2451327C1 |

| Устройство для формирования последовательностей дискретно-частотных сигналов | 1988 |

|

SU1541627A1 |

| УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ПЕРВООБРАЗНЫХ ЭЛЕМЕНТОВ КОНЕЧНЫХ ПОЛЕЙ | 1991 |

|

RU2020755C1 |

Йяг /

Авторы

Даты

1983-02-07—Публикация

1979-05-28—Подача