того, калибратор содержит дешифратор 9, преобразователи кодов 10 и 11, коммутатор 12, регулятор 13 опорного напряжения, перемножающие цифроаналоговые преобразователи 14

I

Изобретение относится к фазоиз- мерительной технике и предназначено для формирования в широком диапазоне частот двух или более синусоидальных напряжений либо напряжений любой другой формы с заданным значением их амплитуды и предизионно регулируемым фазовым сдвигом, и может быть использовано при создании многофазных систем с высокой точностью установки фазового сдвига между отдельными напряжениями, я качестве компенсирующего фазовращателя в фазометрах уравновешивания и в различных фазовых системах радиотехники, автоматики, связи, измерительной техники и црутк областях.

Цель изобретения - повышение точности задания сдвига фаз за счет Toroj что используется как смещение во времени моментов формирования дискретных значений напряжений определенного уровня при регулировании фазовых сдвигов большими ступенями (100, 10, 1°)s так и изменение уровня дискретных значений напряжений при регулировании фазовых сдвигов наименьшими ступенями (напр;имер, 0, О, 1 ), а также уменьшение аппаратурных затрат.

При преобразовании цифровых взвешенных кодов дискретных значений: текущих фаз в цифровые взвешенные коды напряжений вводится дополнительная коммутация наборов этих кодов напряжений, которые отличаются друг от друга на значения, соответствующие изменениямфазы на вводимую дополнительнзто наименьшую ступень.

Уменьшение фазовых погрешностей предлагаемого калибратора достига- ется за счет сокращения дополнитель ного канала аналогового сум1чатора.

и 15. Повышение точности задания сдвига фаз достигается за счет введения дешифратора 9, преобразователей кодов 10 и 11, коммутатора 12. 1 з.п. ф-лы, 1 ил.

Расширение функциональных возможностей, заключающееся в генерировании любой заданной формы выходных напряжений и безфазовом регулировании их амплитуды, осуществляется путем предварительной записи и циклического воспроизведения значений кодов напряжений заданных форм и амплитуд,, соответствующих дискрет- ньм выборкам через равные интервалы времени. Количество таких интервалов на период определяется минимальной дискретностью регулирования фазовых сдвигов путем смещения во времени моментов формирования дискретных значений,, Кроме того, безфазовая регулировка амплитуды выходных напряжений осуществляется путем вариации опорных напряжени. перемножающих цифроанагюговыз ; преобразователей.

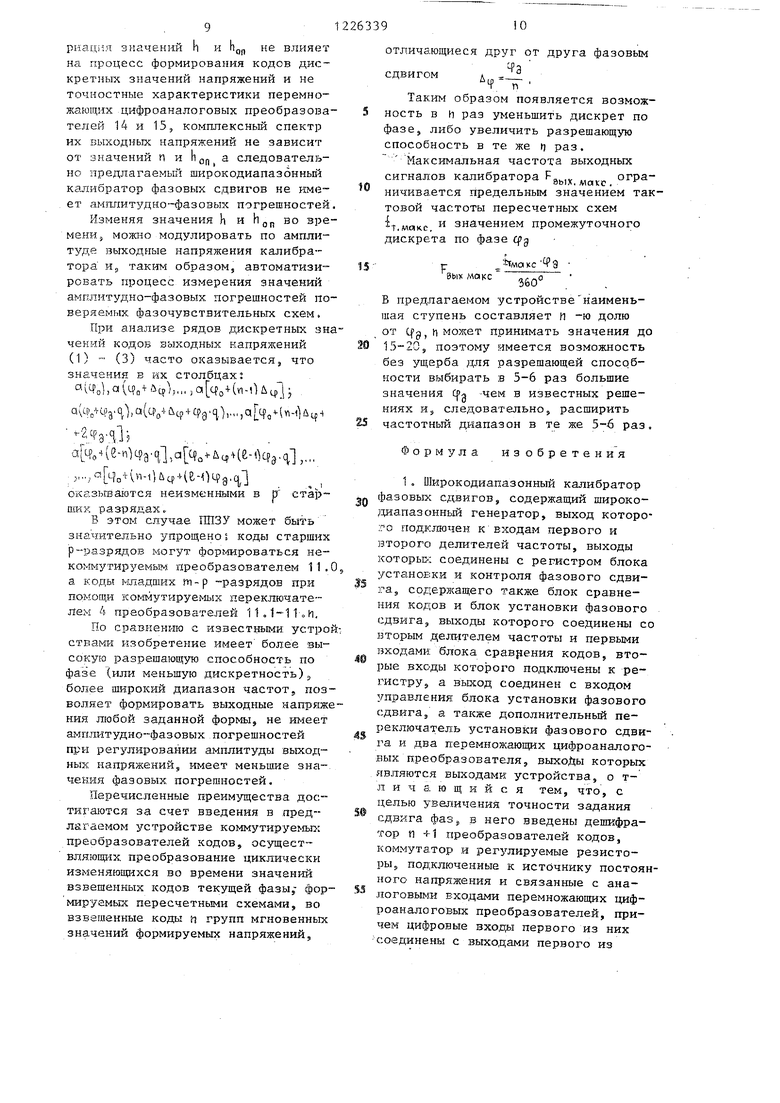

На чертеже представлена структурная схема широкодиапазонного калибратора фазовых сдвигов.

Калибратор содержит широкополосный генератор 1, пересчетные блоки 2 и 3, делители частоты, дополнительный переключатель 4 установки фазовых сдвигов, блок 5 установки и контроля фазовых сдвигов, в который входят блок 6 установки фазовых сдвигов, регистр 7, блок 8 сравнения кодов, кроме того в калибратор входят дешифратор 9, пер&программи- руемые запоминающие блоки (ППЗУ - преобразователи кодов) 10 и 11,коммутатор 12, регулятор 13 опорного напряжения, и два перемножающих циф- роаналоговых преобразователя (ПЦАП) 14 и 15.

Выход широкодиапазонного генера- тора 1 подключен к тактовым входам пересчетных блоков 2 и 3, Входы ввода информации одного из пересчетных блоков 3 поразрядно связаны с одно- именньми выходами блока 6 установки

3

фазового сдвига. К этим же выходам подсоединена первая группа входов блока 8 сравнения, Вторая группа вх ДОН подключена к вьгходам регистра 7 памяти, информационные входы которого соединены с выходами разрядов пересчетного блока 3, а вход записи связан с выходом заполнения пересчетного блока 2, в качестве которого может служить его старший разряд Выход блока 8 сравнения кодов под- ключен к входу блока 6 управления установки фазового сдвига. Информа- .ционные выходы разрядов пересчетного блока 2 соединены с входами преобразователя 10 кодов, выходы которого связаны с цифровыми входами перемножающего цифроаналогового преобразователя 14, выход которого является выходом опорного канала пшрокодиапазонного калибратора фазовых сдвигов. Информационные выходы разрядов пересчетного блока 3 подключены к информационным входам дешифратора 9, имеющего ц групп информационных выходов. К каждой группе выходов подсоединены входы преобразователей 11.1-11,h кодов выходы которых связаны с таким же количеством информационных входов коммутатора 12. Выходы этого коммутатора в свою очередт подключены к цифровьм входам перемножающего цифроаналогового преобразователя 15, выход которого является выходом регулируемого канала широ одиапазон- ного калибратора фазовых сдвигов, В устройство может быть введен некоммутируемый преобразователь 11,0 кодов, информационные входы которого соединены с выходами разрядов пересчетного блока 3, а выходы связаны с входами старших р разрядов перемножающего m -разрядного цифро- аналогового преобразователя. Остальные т-р разряды преобразователя подключены к выходам коммутатора 12, Одноименные входы управления дешифратора 9 и коммутатора 12 соединены между собой и связаны с дополнительным переключателем 4 установки фазового сдвига. Аналоговые входы перемножающих цифроаналоговых преобразователей 14 и 15 подключены к

движкам регулируемых резисторов регулятора 13, питаемого от источника постоянного опорного напряжения Uo.

263394

Устройство работает следующим образом.

Непрерывная последовательность импульсов , формируемых широкодиапа- 5 зонным генератором 1, поступает на тактовые входы пересчетных блоков 2 и 3. Частота повторения импульсов i генератора 1 превышает частоту выходных напряжений Fg, широко- 0 диапазонного калибратора фазовых сдвигов в Е раз ,

Т J

где I - коэффициент деления частоты пересчетных блоков 2 и 3 к максималь15 ное количество интервалов аппроксимации выходных напряжений, приходящихся на их период. Коэффициент деления частоты устанавливает также промежуточное значение дискрета ре20 гулирования фазовых сдвигов Cfg. Изменение фазовых сдвигов калибратора су| на значения, кратные cpj осуществляется путем вариации стационарных значений начальных фаз пересчет5 ных блоков 2 и 3, используемых как управляемые делители частоты

60° - , Я Э -Г-5 к -М э,

0 где k код старших разрядов фазового сдвига, задаваемый блоком 6 установки фазового сдвига и изменяющийся в пределах О - 2-1.

Для обеспечения высокой точности

5 воспроизведения дискретных значений выходных напряжений и высокой разрешающей способности по фазе значение В целесообразно увеличивать, а для расширения частотного диапазо0 на калибратора фазовых сдвигов значение I необходимо устанавливать как можно меньшим. Поэтому выбор значения 6 должен быть компромиссным .

5 Установка старших разрядов заданного значения фазового сдвига в калибраторе осуществляется цифровым взвешенным кодом при помощи блока 6 установки фазового сдвига. Теку0 щие значения кодов пересчетных блоков 2 VI Ъ mt) и Non W соответствуют в дискретном выражении значениям текутдих фаз Р (i) и Ф (t) выходных напряжений. Фазовый сдвиг

между выходными напряжениями определяется разностью абсолютных значений текущих фаз

(P(t)- P,Ji),

а следовательно, и разностью кодов пересчетных блоков

l((t)-Non(i)

Для установки заданного значения разности кодов и для контроля его при помощи блока 5 используются интервалы времени, в течение которых код одного из пересчетных блоков 2 обращается в нуль Нд (ig 0, т.е. интервалы, следующие за моментом заполнения этого пересчетного блока. При этом контроль установленного знчения фазового сдвига (разности кодов) осуществляется блоком 5 путем записи в регистр 7 в указанный интервал времени кода другого пересчетного блока 3. Блок 8 сравнения кодов осуществляет поразрядное сравнение кода, задаваемого блоком 6 установки фазового сдвига, с выходным кодом регистра 7. При неравенстве сравниваемых кодов при помощи блока 8 в момент заполнения пересчетного блока 2, т.е. когда оп (.о} О, формируется сигнал управления блоком 6 установки фазового сдвига. Этот блок осуществляет корректировку возникшего рассогласования, занося требуемое значение кода в пересчетиый блок 3, независимо от того произошел сбой в работе одного из пересчетных блоков или в блок 6 установки фазового сдвига занесено новое значение кода Контроль фазового сдвига и при необходимости его корректировка выполняются в каждом периоде выходной напряжений калибратора.

Выходы разрядов пересчетного блока 2 подключены к входам преобразователя 10 кодов, который преобразует дискретные значения кодов, выражающих текупще фазы выходного напряжения ,„ (i в строго им соответствующие коды мгновенных значений напряжения a(,n(-t) заданной формы. В качестве преобразователя 10 кодов может быть использован постоянный перепрограммируемьш запоминающий блок 10 - 11. п. Этот блок программируется, а также сменяется или коммутируется таким образом, чтобы имелись группы наборов мгновенных значений напряжений всех требуемых форм. При формировании синусоидальных сигналов запоминающий . блок программируется по выборкам гармонических функций

on(t) 2in «n.(.h

преобразователь 10 кодов или ПИЗУ выбирается таким образом,чтобы количество их адресных входов не превьшало количества разрядов пересчетных блоков 2 и 3, а разрядность по В 1ходу совпадала с разрядностью подсоединенного к нему интегрального перемножающего цифроаналогового преобразователя 14. В свою очередь количество разрядов интегрального цифроаналогового преобразователя 14 выбирается исходя из заданной точности воспроизведения мгновенных значений выходных напряжений.

Выходы разрядов пересчетнбго блока 3 канала с регулируемым фазовым сдвигом связаны с информационными входами дешифратора 9. Количество групп выходов дешифратора 9 также как и количество подключенных к ним преобразователей 11.1 - 11.и кодов определяется значением наименьшей ступени регулирования фазовых сдвигов д.

л fa

0

5

0

5

O

5

где п - любое целое число из натурального ряда.

Максимальное значение п ограничено разрешающей способностью выходного цифроаналогового преобразователя 15. Так для выходного гармонического напряжения значение ,

должно в несколько раз превышать разрешающую способность выходного преобразователя 15. Выходы-преобразователей соединены с группами входов коммутатора 12, выходы которого подключены к перемножающему цифроаналоговому преобразователю 15. Количество разрядов последнего, определяющее его разрешающую способность, должно быть достаточным для того, что.бы обеспечить требуемую точность воспроизведе«ия мгновенных значений выходного напряжения и для того, чтобы реализовать требуемое значение наименьшей ступени регулирования фазовых сдвигов д,.

Дешифратор 9 и коммутатор 12 управляются синхронно статическим кодом дополнительного переключате- ля 4 установки фазовых сдвигов. В первом положении переключателя выходы разрядов пересчетного блока 3 посредством дешифратора 9 подк.ггюча-| ются к входам преобразователя 11,1

кодов, а его выходы через коммутатор 12 соединены с цифровыми входами перемножающего цифроаналогово- го преобразователя 15. Остальные выходы дешифратора 9 и входы комму- 5 татора 12 отключены. Аналогично во втором полояГении переключателя 4 между выходами пересчетного блока 3 и цифровыми входами перемножающего цифроаналогового преобразователя 15, О оказывается включенным преобраз ова- тель 11.2 кодов и т.д. Так же как и в опорном канале, в качестве преобразователей 11.1-11.П кодов могут быть использованы перепрограммируемые запоминающие блоки. Преобразователи 10 и 11.1 кодов программируются одинаково, т.е. дискретным значениям аргумента Pit):

-Чб,о Ч з-Я Ч о 2 Э-И о 3 где (fg - начальньш сдвиг фаз в пределах О - , а 1 - любое целое число не более 6/3 (в соответствии

на их входах составляет tfg-c. Опрос дискретных значений кодов преобразователей 10 и 11 несинхронный-по каналам, так как в общем случае

несинхронно изменяются дискретные значения кодов пересчетных блоков 2 и 3. За счет сдвига дискретных значений кодов одной пересчетной схемы по отношению к другой, осуществляемого блоком 5 установки и контроля фазового сдвига, производится регулирование фазового сдвига промежуточными ступенями срд . На выходах преобразователей 11 и 10 также несинхронно происходит циклическая схема дискретных значений кодов напряжений, определяемых наборсж (1) для преобразователя 10 и одним из наборов (1) - (3) для преобразователей 11.1 - 11.и в зависимости от положения дополнительного переключателя 4 установки фазового сдвига наименьшими ступенями. Как следует из выражений (1) - (3) фазовые с теоремой Котельникова), должны со- сдвиги меящу напряжениями, дискрет15

20

30

40

ответствовать дискретные значения кодов напряжений а

Q(),)a((),..,,a c oЧe-lЦ.clз.

Преобразователь 11.2 кодов программируется таким образом, что набо-. ру дискретных значений аргумента ФС )

o S V 3 Ч o ч aЯ мЧ o

+ йцЧг-Оч,-я

Должен соответствовать набор дискрет- J5 ных значений кодов напряжений а (Р)-.

),a(ч,4йц,гCpзя),a()o.c),..,J.

,ч с йч - ЧЗ-я1- 2)

Аналогичным образом программируются остальные преобразователи кодов - набору дискретных значений аргумента f(. %Ч 1-Ойц,(1Лм М Э Д,Чо(-Ойч

-2 ,,., ,Ч о+() Ьч,4 (Й-О должен соответствовать набор дискретных значений напряжений с((Ф1:

a o4n-lU fl, + q)g C,Q tpoUvi-Ox

xuc +2c|g.(,,,,,a q o+h-i)ucp + (.a.(3)

В процессе работы пересчетных блоков 2 и 3 их выходные коды лически изменяются с шагом cfg. Учитывая то, что не все разряды пересчетных блоков могут быть подключены к входам преобразователей 10 и 11, шаг циклического изменения кодов

45

SO

ные значения которых они выражают, отличаются друг, от друга на угол uty, Следовательно, полный фазовый сдвиг, воспроизводимый широкодиапазонным калибратором фазовых сдвигов, может быть представлен выражением:

q) 4 H + 7

где i - код дополнительного переключателя 4 установки фазового сдвига наименьшими ступенями Лц,, ср - аддитивная погрешность фазиров- ки каналов калибратора, обусловленная неидентичностью ФЧХ выходных преобразователей 14 и 15.

Перемножающие цифроаналоговые преобразователи 14 и 15 преобразуют циклически изменяющиеся во времени цифровые коды, соответствующие дискретным значениям напряжений Яоп и а (.t) в аналоговые напряжения. Выходные напряжения преобразователей 14 и 15 определяются выражениями иоп -ао„1) Ьо„-и,

UU)a(t1.b.U, -де-1), .

о ,

53

опорное напряжение источника; Ьд„,Ь - коэффициенты деления напряжения регулируемым регулятором 13.

Регулировка амплитуды выходных напряжений широкодиапазонного калибратора фазовых сдвигов осуществляется путем изменения значений h и hgi, . Принимая во внимание, что вана их входах составляет tfg-c. Опрос дискретных значений кодов преобразователей 10 и 11 несинхронный-по каналам, так как в общем случае

0

0

5

5

O

ные значения которых они выражают, отличаются друг, от друга на угол uty, Следовательно, полный фазовый сдвиг, воспроизводимый широкодиапазонным калибратором фазовых сдвигов, может быть представлен выражением:

q) 4 H + 7

где i - код дополнительного переключателя 4 установки фазового сдвига наименьшими ступенями Лц,, ср - аддитивная погрешность фазиров- ки каналов калибратора, обусловленная неидентичностью ФЧХ выходных преобразователей 14 и 15.

Перемножающие цифроаналоговые преобразователи 14 и 15 преобразуют циклически изменяющиеся во времени цифровые коды, соответствующие дискретным значениям напряжений Яоп и а (.t) в аналоговые напряжения. Выходные напряжения преобразователей 14 и 15 определяются выражениями иоп -ао„1) Ьо„-и,

UU)a(t1.b.U, -де-1), .

о ,

3

опорное напряжение источника; Ьд„,Ь - коэффициенты деления напряжения регулируемым регулятором 13.

Регулировка амплитуды выходных напряжений широкодиапазонного калибратора фазовых сдвигов осуществляется путем изменения значений h и hgi, . Принимая во внимание, что варнац:1я значений h и hg не влияет на процесс формирования кодов дискретных значений напряжений и не точностные характеристики перемножающих цифроаналоговых преобразователей 14 и 15э комплексный спектр их выходных напряжений не зависит от значений г, и Ьд,, а следовательно предлагаемый широкодиапазонный калибратор фазовых сдвигов не имеет амплитудно-фазовых погрешностей

Изменяя значения К и hj, во времени j можно модулировать по амплитуде выходные напряжения калибратора Ид таким образом, автоматизировать процесс измерения значени амплитудно-фазовых погрешностей поверяемых фазочувствительных схем.

При анализе рядов дискретных знчений кодов выходных напряжений (1) (3) часто оказывается, что значения в их столбцах; «Wsl,a ( ucpV,,,,, а с|о-1-(п-0 Дц, j j

0,(u),,a(,.,.,(-(

2ФЭ-.У5 а.п(е-п).с|,,йчЧе-(.а1г...

. v,.,; - Lj -tVvvi)uq)4&-Ot.pg,q оказьшаются неизменными в р старшик разрядах.

В этом случае ГШЗУ может

значительно упрощено; коды старших р разрядов могут фор л1роваться некомму тируемым; преобразователем ГК а коды мпадпшх ш-р -разрядов при помощи коммутируемых переключателем 4 преобразователей 11ol-11.h,

По сравнению с известными устроствами изобретение имеет более высокую разрешающую способность по фаз е (или меньшую дискретность), более широкий диапазон частот, позволяет формировать выходные напряжния любой заданной формы, не имее т амплитудно-фазовых погрешностей при регулировании амплитуды выход- ньзх напряжений, имеет меньшие значекия фазовых погрешностей.

Перечисленные преимущества достигаются за счет введения в предлагаемом устройстве коммутируемых преобразователей кодов, осуществляющих преобразование циклически изменяющихся во времени значений взвешенных кодов текущей фазы, фор мируемых пересчетными схемами, во взвашенные коды п групп мгновенных значений формируемых напряжений.

отличающиеся друг от друга фазовым

сдвигом д . т п

Таким образом появляется возможность в и раз уменьшить дискрет по фазе, либо увеличить разрешающую способность в те же tj раз. Максш альная частота выходных сигналов калибратора Fg,j( j, огра- ничива.ется предельным значением тактовой частоты пересчетных схем i.j, .д. и значением промежуточного дискрета по фазе Cfg

Ьтмакс Э

F,

вык макс

360

0

$

5

В предлагаемом устройстве наименьшая ступень составляет ц -ю долю от Cfg, h может принимать значения до 15-20, поэтому имеется возможность без ущерба для разрешающей способности выбирать в 5-6 раз большие значения cjig -чем в известных решениях И; следовательно5 расширить частотный диапазон в те же 5-6 раз.

Формула изобретения

1 . П1ирокодиапазонный калибратор фазовых сдвигов, содержащий ширско- ;диапазонньш генератор, выход которого подключен к входам первого и второго делителей частоты, выходы которьк соединены с регистром блока установки и контроля фазового сдвига, содержащего также блок сравнения кодов и блок установки фазового сдвига, выходы которого соединены со вторым делителем частоты и первыми входами бхгока сравнения кодов, вторые входы которого подключены к регистру, а выход соединен с входом управления блока установки фазового сдвига, а также дополнительный переключатель установки фазового сдвига и два перемножающих цифроаналоговых преобразователя, выхоДы которых являются выходами устройства, о т- л и ч а ю щ и и с я тем, что, с целью увехсичения точности задания сдвига фаз 5 в него введены дешифратор п +1 преобразователей кодов, коммутатор и регулируемые резисторы, подключенные к источнику постоянного напряжения и связанные с аналоговыми входами перемножающих цифроаналоговых преобразователей, причем цифровые входы первого из ник соединены с выходами первого из

П

преобразователей кодов, входы которого подключены к разрядам первого

делителя частоты, а цифровые входы второго перемножающего цифроанало- гового преобразователя связаны с выходами коммутатора, между входами которого и одноименными выходами дешифратора включены остальные п преобразователей кодов, информационные входы дешифратора соединены с выходами разрядов второго делителя частоты, а одноименные входы управления дешифратора и коммутатора по- )азрядно подключены к дополнительному переключателю установки фазовых сдвигов.

Редактор Р. Цицика Заказ 2126/43

Составитель В. Шубин Техредл.Олейник Корректор А. Тяско

Тираж 7,28 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и oтJcpытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

12

2. Калибратор по п.1, о т л и- чающийся тем, что, с целью уменьшения аппаратурных затрат, в него введен некоммутируеилй преобразователь кодов, входы которого совместно с входами регистра и дешифратора подключены к выходам разрядов второго делителя частоты, а выходы - к входам р старших разрядов перемножающего цифроаналогового преобразователя, а m - р выходов коммутатора соединены с входами w р младших разрядов перемножающего цифроанапогового преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1976 |

|

SU702506A1 |

| Калибратор фазы | 1981 |

|

SU1078353A1 |

| Калибратор фазовых сдвигов | 1978 |

|

SU834596A1 |

| Регулируемая мера фазовых сдвигов | 1985 |

|

SU1347034A1 |

| Калибратор фазовых сдвигов | 1979 |

|

SU789891A1 |

| Регулируемая мера фазовых сдвигов | 1983 |

|

SU1129552A1 |

| Калибратор фазовых сдвигов | 1982 |

|

SU1045161A1 |

| Двухфазный генератор | 1983 |

|

SU1148001A1 |

| Цифровой калибратор фазы | 1986 |

|

SU1352402A1 |

Изобретение может быть использовано для бормирования в широком диапазоне частот двух или более синусоидальных напряжений, или напряжений любой другой формы с заданным значением их амплитуды и прецизион- но регулируемым фазовым сдвигом, а также при создании многофазных систем с высокой точностью установки фазового сдвига между отдельными напряжениями в качестве компенсирую щего фазовращателя в фазометрах уравновешивания. Цель изобретения - повышение точности задания сдвига фаз. Калибратор содержит широкополосный генератор 1, делители частоты 2 и 3, переключатель 4 установки фазовых сдвигов, в который входят; блок 6 установки фазовых сдвигов, регистр 7, блок 8 сравнения. Кроме

| ФАЗОВЫЙ КАЛИБРАТОР | 1972 |

|

SU434332A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1976 |

|

SU702506A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-11-20—Подача