Изобретение относится к информа- циопно-измерительной техиш е, в ча стности к фазовым измерениям.

Цель изобретения - повышение точности и уменьшение дискретности воспроизведения фазового сдвига в ши- .роком диапазоне частот.

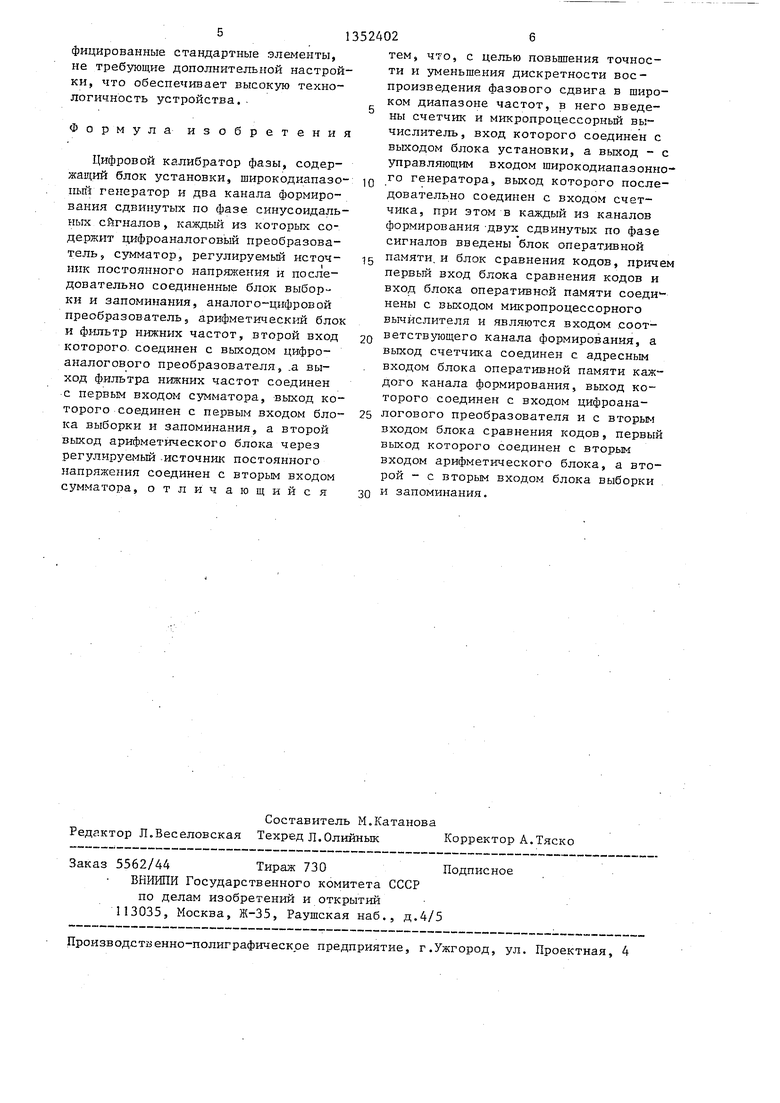

На чертеже приведена структурная схема устройства.

Цифровой калибратор фазы содержит блок 1 установки, который соединен с входом микропроцессорного вычислителя 2, выход которого соединен с управляющим входом широко- диапазонного генератора 3, последовательно соединенного со счетчиком 4, и два канала 5 и 6 формирования сдвинутых по фазе синусо1адальных сигналов, состоящие соответственно из блоков 7 и 8 сравнения кодов (ВСК), цифроаналоговых преобразователей ДАЛ 9 и 10, аналого-цифровых преобразователей АЦП 1 -и 12, арифмети- ческих блоков 13 и 4, управляемых фильтров 15 и 16 нюкних частот (ФНЧ) блоков 17 и 18 выборки и запоминания (БЕЗ), регулируемых источников 19 и 20 постоянного напряжения (ИПН) cyN MaTopoB 21 и 22 и блоков 23 и 24 оперативной памяти (БОП), прячем первые вход блока 7 (8) сравнения кодов и вход блока 23 (24) оперативной памяти соединены с выходом микропроцессорного вьнислителя 2, а выход счетчика 4 соединен с адресным входом блока 23 (24) оперативной памяти, выход которого соединен с входом ЦАП 9 (10) и с вторым входом блока 7 (8) сравнения кодов, один выход которого связан с арифметическим блоком 13 (14), а другой - с блоком 17 (18) выборки и запоминания, по-- следовательно соединенным с АЦП 11 (12), арифметическим блоком 13 (14) и ФНЧ 15 (16), второй вход которого соединен с выходом ЦАП 9 (10), а въкоц Ф1И 15 (16) соединен с первым входом сумматора 21 (22), выход которого Соединен с вторым входом блока 7 (18) выборки и запоминания, при этом второй выход арифметического блока 13 (14) через регулируемьй ИСТОЧН1СС 19 (20) постоянного напряжения соединен с вторым входом сумматора 21 (22), выход которого является выходом канала.

.Мшсропроцессорный вычислитель (МПВ), построенный на базе микропроцессорпого комплекта, соединен с блоком оперативной памяти таким образом, что исключает влияние вычис- лительиого блока на быстродействие .прибора, которое полностью определяется быстродействием блока оперативной памяти и на два порядка больше, чем у микропроцессорного вьр ислителя. При таком соединении после загрузки блока оперативной памяти необ- данными прибор работает без участия МЛВ, что позволяет получить МПВ такие функции, как контроль и

5 регулировка выходных параметров прибора, их автоматическое изменение по заданной программе и т.п.

Устройство работает следующим образом.

Q Информация о разности фаз if и частоте выходных сигналов F, содержащаяся в блоке 1 установки, считывается микропроцессорным вычислителем 2, который в зависимости от

5 программы вычисляет N значений

Y, v(x) УЗ V(x+ If), где Ч - требуемая разность фаз, а N - число значений функции, необходимых для аппроксимации одного периода ко0 лебаний с требуемым значением коэффициента нелинейных искажений. Для получения выходного сигнала синусо- идальной -формы вычисляются значения Y, sin(x), Yj sin(x +yO , где

X 2yi -Ft. и записьшаются в БОП 23 и 24 первого и второго каналов соответственно. При вычислении этих значений из их числа МПВ 2 находит мини

мальные абсолютные значения и их

коды К.д ог записывает соответственно в один из регистров БСК 7 и 8, первого и второго каналов. Затем микропроцессорный вычислитель 2

выдает код частоты на управляющий вход широкодиапазонного генератора 3, частота которого равна f F N. Тактовая частота поступает на счет- чик 4,. формирующий адреса БОП 23

и 24 первого и второго каналов. На вькодах БОП 23 и 24 присутствуют изменяющиеся во времени коды функции Y; и Y, 5 которые поступают соот-п ветственно на входы ЦАП 9 и 10. На

выходах ЦАП 9 и 10 формируются два аппроксимированных сту гшнчато-синусо- вдальных напряжения с регулируемой разностью фаз. Из этих напряжений управляемыми фильтрами 15 и 16 ниж3. 1

них частот вьиеляют основные гармоники, которые поступают через сумматоры 21 и 22 на выходы калибратора. Вследствие подключения комплексных нагрузок к выходньм клеммам калибратора, .дрейфа параметров элементов в его узлах, изменения частоты выходных сигналов, а также статических и динамических погрешностей формирования дискретных приращений выходных сигналов появляются дополнительные фазовые сдвиги сигналов и постоянное напряжение смещения. При этом выходные напряжения калибратора можно представить в виде:

ивых1 и 01+ (x+4(й) ,

и

6Ь(Х

2 Uo2+ Ui sin (x+if p+dcf l ,

где и

01

и 02 - 4 i ) , соответст

венно постоянные составляющие и дополнительныефазовые сдвиги выходных напряжений калибратора.

Устранение этих постоянных состав ляющих и дополнительных фазовых сдвигов выходных сигналов в каждом канале цифрового калибратора производится следующим образом,

Напряжение Ugj,,,- поступает на

вход блока 17 выборки и запоминания, в котором производится запоминание значений напряжения в моменты времени, определяемые блоком 7 сравнения кодов, который сравнивает коды с выхода блока 23 оперативной памяти с наименьшим кодом К,,, , записанным в одном из регистров БСК 7. В момент совпадения кодов выдается сигнал разрешения на блок 17 выборки и запоминания, а сам код поступает на вход арифметического блока 13.

За период запоминаются два значения напряжений:

Uoi +

и sin и.

и,- U,.sinv -.U,

S in л Ч , ,

S in -3 i, ,

где и.

« и,,,значения напряжении, соответствующие фазам О и 180.

Значение U sin ц соответствует минимальному коду К. .

rSo

с помощью аналого-цифрового преобразователя 11 напряжения Up и U преобразуются соответственно в коды Ко и К находит + К

160к

Арифметический блок 13 и

KO Кр,

к

Тйо

К,во+

01

вычитание кодов К и К

а затем производит сложение и

о -180 результате чего на его выходах формируют

ся суммарный Kf ды:

Кг. К +

и разностный Ко кок;вс, 2 и„,

Кр - Кд - K gj,2 Uoi s in J cf, ,

5

0

5

5

о

0

50

5

Из этих выражений следует, что коды К(- и Кр пропорциональны соответственно постоянной составляющей U, и дополнительному фазовому сдвигу выходного напряжения д с/, . Код KC управляет напряжением регулируемого источника 19 постоянного напряжения, поступающим на вход смещения сумматора 21, таким образом, чтобы выполнялось условие Up, -V О. Код К изменяет значение фазового сдвига, внр- симого управляемым (фильтром 15 нижних частот, таким образом, чтобы вьшолнялось условие л у - О. Аналогично производится коррекция .напря- женин Uj,j.

Применение изобретения позволяет повысить точность задаваемого фазового сдвига до 0,001°, так как применение микропроцессорного вычислителя позволяет вычислять значения ступеней аппроксимации с большой точностью; расширить частотный диапазон выходного сигнала и довести дискретность регулирования разности фаз до (1 О ) ,так как число ступеней аппроксимации изменяется только программно в зависимости от частоты выходного сигнала и требуемого коэффициента нелинейных искажений, поэтому достигается высокая точность установки абсолютных значений фазо- . вого сдвига в диапазоне частот от тысячных долей герца до десятков мегагерц, а также высокая точность формирования синусоидальной формы выходных сигналов; обеспечить его широкое применение для автоматической поверки фазометрических уст-. ройств, так как устройство, выполнен- ное на базе микропроцессора, является источником сигналов с программно-регулируемыми амплитудой, частотой, формой и фазовым сдвигом; использовать в приборе только унифицированные стандартные элементы, не требующие дополнительной настройки, что обеснечивает высокую технологичность устройства. .

Формула изобретения

Цифровой калибратор фазы, содержащий блок установки, широкодиапазоньй генератор и два канала формирования сдвинутых по фазе синусоидальных сигналов, каждый из которых содержит цифроаналоговый преобразователь, сумматор, регулируемый источник постоянного напряжения и последовательно соединенные блок выборки и запоминания, аналого-цифровой преобразователь, арифметический блок и фильтр нижних частот, второй вход которого, соединен с выходом цифро- аналогового преобразователя, .а выход фильтра нижних частот соединен с первым входом сумматора, выход которого соединен с первым входом блока выборки и запоминания, а второй выход арифметического блока через регулируемый -источник постоянного напряжения соединен с вторьм входом сумматора, отличающийся

Составитель М.Катанова Редактор Л.Веселовская Техред Л.Олийнык Корректор А.Тяско

Заказ 5562/44 Тираж 730Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул. Проектная, 4

: 52402

тем.

10

15

что, с целью повьшения точности и уменьшения дискретности воспроизведения фазового сдвига в широком диапазоне частот, в него введены счетчик и микропроцессорный вычислитель, вход которого соединен с выходом блока установки, а вькод - с управляющим входом широкодиапазонного генератора, выход которого последовательно соединен с входом счетчика, при этом в каждый из каналов формирования -двух сдвинутых по фазе сигналов введены блок оперативной памяти, и блок сравнения кодов, причем первый вход блока сравнения кодов и вход блока оперативной памяти соединены с выходом микропроцессорного вычислителя и являются входом соот2Q ветствующего канала формирования, а выход счетчика соединен с адресным входом блока оперативной памяти каждого канала формирования, выход которого соединен с входом цифроана25 логового преобразователя и с вторым входом блока сравнения кодов, первый выход которого соединен с вторым входом арифметического блока, а второй - с вторым входом блока выборки ,

30 и запоминания.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания фазового сдвига | 1990 |

|

SU1721537A1 |

| Калибратор фазовых сдвигов | 1979 |

|

SU789891A1 |

| Калибратор фазовых сдвигов | 1982 |

|

SU1045161A1 |

| Широкодиапазонный калибратор фазовых сдвигов | 1976 |

|

SU702506A1 |

| Цифровой генератор синусоидальных сигналов | 1984 |

|

SU1223328A1 |

| Цифровой калибратор фазы | 1984 |

|

SU1242848A1 |

| Калибратор напряжения | 1984 |

|

SU1244646A1 |

| Калибратор напряжения | 1982 |

|

SU1056151A1 |

| ЦИФРОВОЕ УСТРОЙСТВО ДЛЯ АДАПТИВНОЙ КОРРЕКЦИИ КВАДРАТУРНЫХ ДЕМОДУЛЯТОРОВ | 2000 |

|

RU2187140C2 |

| СПОСОБ ИЗМЕРЕНИЯ ФАЗОВОГО СДВИГА И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2099721C1 |

Изобретение относится к информационно-измерительной технике и может быть использовано в устройствах фазовых измерений. Цель изобретения - повышение точности и уменьшение , дискретности воспроизведения фазового сдвига в широком диапазоне час- тот - достигается за счет введения микропроцессорного вычислителя 2 и счетчика 4, а также введения новых фуьшциональных связей. Цифровой калибратор, кроме того, содержит блок 1 установки, широкодиапазонный генератор 3, два канала 5 и 6 формирования сдвинутых по фазе синусоидальных сигналов, состоящие из блоков 7 и 8 сравнения кодов, цифроаналогоп- вых 9 и 10 и аналого-цифровых И и 12 преобразователей, арифметических блоков 13 и 14, управляемых фильтров 15 и 16 нижних частот, блоков 17 и 18 выборки и запоминания, регулируемых источников 19 и 20 постоянного напряжения, сумматоров 21 и 22 и блоков 23 и 24 оперативной памяти. Использование предлагаемого калибратора в сравнении с известным позволяет повысить точность задаваемого фазового сдвига до 0,001, довести дискретность регулирования разности фаз до , обеспечить автоматическую проверку фазометричес- ких устройств, использовать только стандартные элементы и обеспечить высокую технологичность устройства 1 ил. (Л оо Сд к о ю

| Калибратор фазовых сдвигов | 1978 |

|

SU834596A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Генератор функций | 1979 |

|

SU798891A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-11-15—Публикация

1986-02-26—Подача