Изобретение относится к фазоиэме- рительной технике и предназначено для формирования двух синусорздальных напряжений лкЬо напряжений любой другой формы с заданным значением их амплитуды и прецизионно-регулируемым фазовым сдвигом между основными гармониками напряжений и может быть использовано для проверки фазоизмери- тельной и фазозадающей аппаратуры.

Цель изобретения - повышение точности воспроизведения абсолютных значений задаваемых фазовых сдвигов путем формирования выходных сигналов методом коррекции ступенчатых квазисинусоидальных напряжений с помощью линейной аппроксимации напряжений на кажд,ом интервале их формирования.

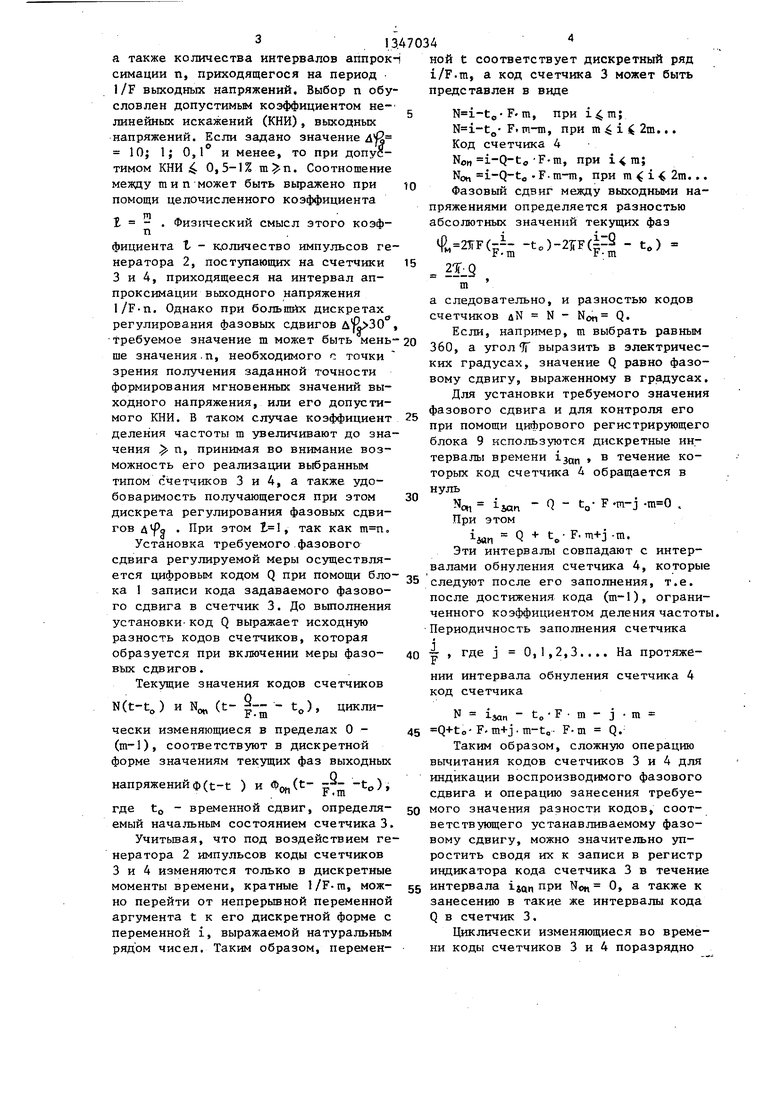

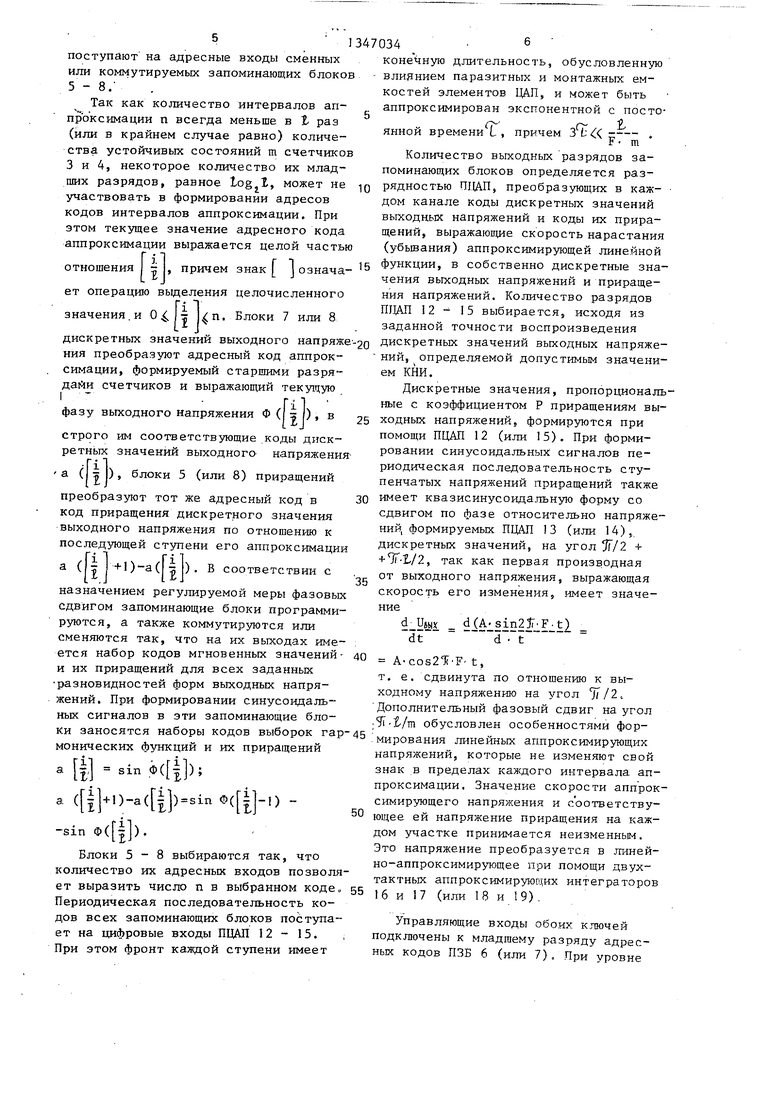

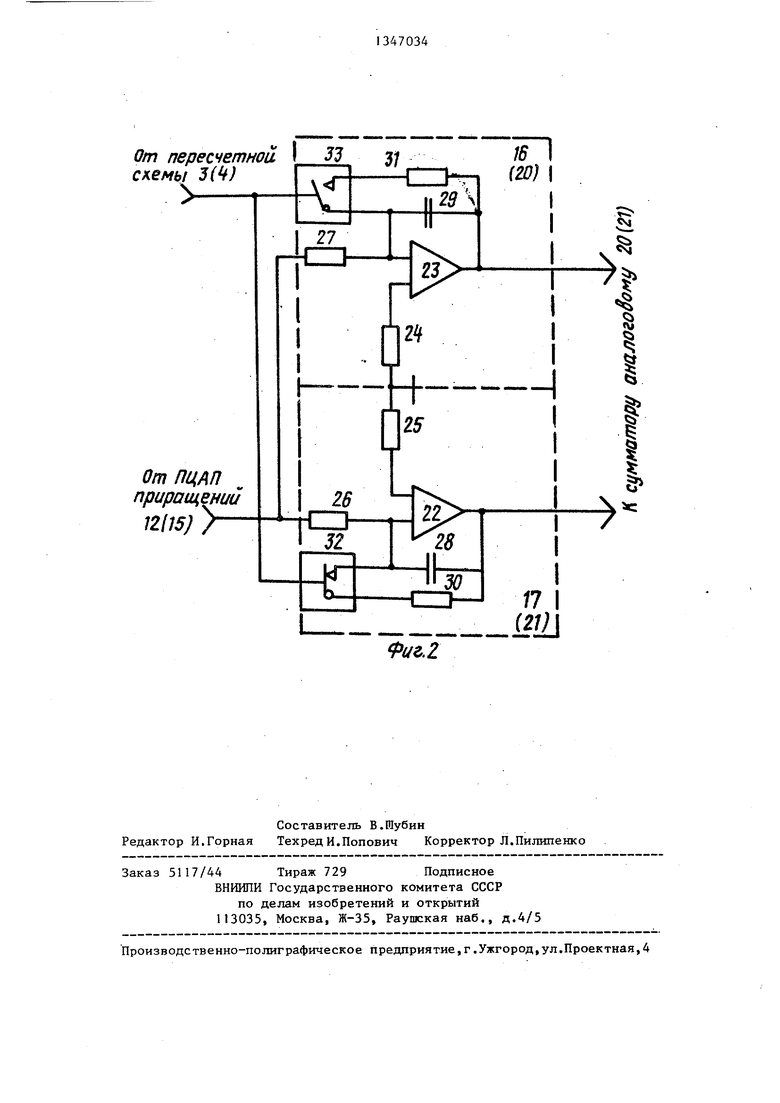

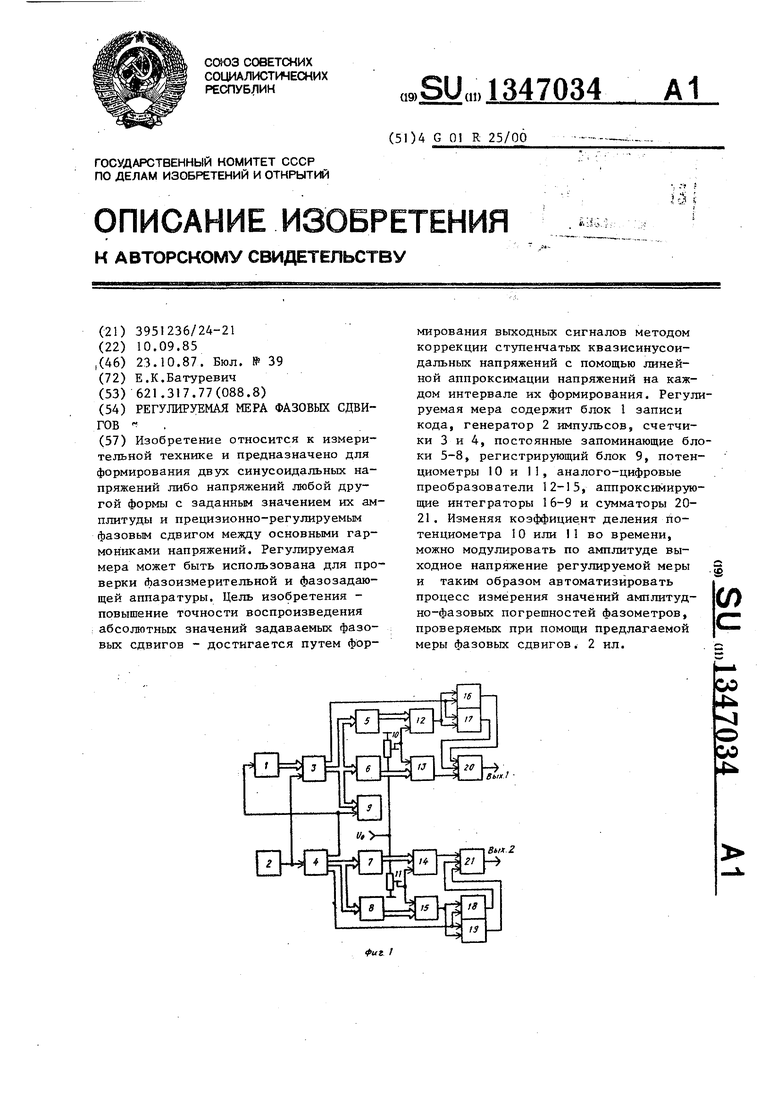

На фиг,1 представлена структурная схема регулируемой меры фазовых сдвигов; на фиг.2 - схема аппроксимирующих интеграторов.

Мера фазовых сдвигов содержит блок 1 записи кода, генератор 2 импуль- сов, счетчики 3 и 4, постоянные запоминающие блоки (ПЗБ) 5-8, регистриру- ,ющий блок 9, потенциометры 10 и 11, перемножающие цифроаналоговые преобразователи (ПЦАП) 2-15, аппроксими- Р5гющие интеграторы 16-19, сумматоры .20 и 21, При зтом выход генератора 2 импульсов соединен со счетными входами счетчиков 3 и 4, выход переполнения счетчика 4 соединен с входом бло- ка 1 и с входом управления регистрирующего блока 9, информационные выходы блока 1 записи кода соединены с информационными входами счетчика 3, информационные выходы счетчиков 3 и 4 соединены соответственно попарно с информационными входами ПЦАЛ 12, 13 и 14, 15,

Младший разряд счетчика 3 соединен с управляющими входами аппроксимирую- щих интеграторов 16 и 17, выход ПЦАП 12 соединен с информационными входами аппроксимирующих интеграторов 16 и 17, Каждый их двух потенциометров 10 и П подключен к шине источника постоянного напряжения Но. Выходы потенциометров 10 и 11 соединены соответственно с входами ПЦАП 12, 13 и 14,. 15, Младший разряд счетчика 4 соединен с управляющими входами аппрок- симирующих интеграторов 18 и 19, аналоговые входы которых соединены с выходом ПЦАП 15. Выходы аппроксимирующих интеграторов 18 и 19 соединены

с входами сумматора 21, первый вход которого соединен с выходом ПЦАП 14. Выходы аппроксимирующих интеграторов 6 и 17 соединены с входами сумматора 20, третий вход которого соединен с выходом ПЦАП 13, а выходы сумматоров 20 и 21 являются выходами меры фазовых сдвигов.

Аппроксимируювдие интеграторы состоят из операционных усилителей 22 и 23, .масштабных резисторов 24-27 (RM), интегрирующих конденсаторов

28и 29 (Си) и резисторов 30 и 31 разряда (Rp), а также нормально замкнутого ключа 32 и нормально разомкнутого ключа 33,

Входы управления обоих ключей 32 и 33 соединены между собой и подключены к младшему из разрядов счетчика 3 (или 4), соединенных с адресными входами ПЗБ 6 (или 8). Ключи 32 и 33 подсоединены параллельно интегрирующим конденсаторам 29 и 28 (Сц) через разрядные резисторы 30 и 31, Кроме того, интегрирующие конденсаторы

29и 28 включены в цепь обратной связи операционных усилителей 22 и 23, т,е, между их выходами и инверсным входом, К инверсные входам подключены также масштабные резисторы 26 и . 27. Вторыми выводами они связаны .между собой и подсоединены к ПЦАП 12 (или 15), Между прямьми выходами операционных усилителей 22 и 23 и общим корпусом включены вспомогательные балансовые резисторы с номиналом Кь,. Выходы, операционных усилителей 22 и 23 соединены с входами сумматора 20 (или 21),

Мера фазовых сдвигов работает следующим образом,

Непрерьшная последовательность импульсов генератора 2 поступает на счетные входы счетчиков 3 и 4. Частота повторения импульсов генератора 2 , превышает заданную частоту выходных напряжений .F регулируемой меры фазовых сдвигов в га раз

f,- m F, где m - коэффициент деления частоты

счетчиков 3 и 4 или количество их устойчивых состояний. Значение коэффициента деления частоты m выбирается исходя из.заданного значения дискрета регулирования фазовых сдвигов f|, 360

™Vfr

а также количества интервалов аппрокН симации п, приходящегося на период 1/F выходных напряжений. Выбор п обусловлен допустимьм коэффициентом не- линейных искажений (КНИ), выходных напряжений. Если задано значение 10; 1; 0,1 и менее, то при допустимом КНИ 4- 0,5-1% . Соотношение между тип может быть выражено при помощи целочисленного коэффициента

1 2 п

Физ1гческий смысл этого коэффициента t - количество импульсов генератора 2, поступающих на счетчики 15 3 и 4, приходящееся на интервал аппроксимации выходного напряжения 1/F-n. Однако при больших дискретах регулирования фазовых сдвигов , требуемое значение m может быть мень-20 ше значения.п, необходимого с точки зрения получения заданной точности формирования мгновенных значений выходного напряжения, или его допустимого КНИ. В таком случае коэффициент 25 деления частоты m увеличивают до значения п, принимая во внимание возможность его реализации выбранным типом счетчиков 3 и 4, а также удобоваримость получающегося при этом 30 дискрета регулирования фазовых сдвигов ipo . При этом , так как

Фазовый сдвиг между выходными н пряжениями определяется разностью абсолютных значений текущих фаз

(pi--t„)-21ГF(.)

- T-Q

m

а следовательно, и разностью кодов

счетчиков uN N - Non Q.

Если, например, m выбрать равны 360, а угол JT выразить в электриче ких градусах, значение Q равно фаз вому сдвигу, выраженному в градуса

Для установки требуемого значен фазового сдвига и для контроля его при помощи цифрового регистрирующе блока 9 используются дискретные ин тервалы времени 1зап течение ко

торых код счетчика нуль

4 обращается в

Non

- Q - tg F -m-j

Установка требуемого.фазового сдвига регулируемой меры осуществляется ЦИбЬрОВЫМ кодом О при помощи бло- ос

w.H м X f -Ч 1 35 следуют после его заполнения, т.е. ка 1 записи кода задаваемого фазовоian -о При этом

ijan Q .m+j-m. Эти интервалы совпадают с интер валами обнуления счетчика 4, котор

после достижения кода (т-1), огран ченного коэффициентом деления часто Периодичность заполнения счетчика

го сдвига в счетчик 3. До выполнени установки- код Q выражает исходную разность кодов счетчиков, которая образуется при включении меры фазовых сдвигов.

значения кодов

- 9. F-m

чески изменяющиеся в пределах О - (т-1), соответствуют в дискретной форме значениям текущих фаз выходны

Текущие N(t-t,) и N

(tсчетчиков

tj ) , ЦИКЛИнапряжений o(t-t ) и Ф,

oti

( --F ;-

где to - временной сдвиг, определяемый начальным состоянием счетчика 3. Учитьшая, что под воздействием генератора 2 импульсов коды счетчиков 3 и 4 изменяются только в дискретные моменты времени, кратные l/F-m, можно перейти от непрерывной переменной аргумента t к его дискретной форме с переменной i, выражаемой натуральным рядом чисел. Таким образом, переменной t соответствует дискретный ряд i/F.m, а код счетчика 3 может быть представлен в виде

N i-to-F. т, при 1414

N i-to- F.m-m, при m i 4 2m...

Код счетчика 4

Non i Q to F-m, при

NOH i-Q-to . F. m-m, при m i 2m. ..

Фазовый сдвиг между выходными напряжениями определяется разностью абсолютных значений текущих фаз

(pi--t„)-21ГF(.)

- T-Q

m

а следовательно, и разностью кодов

счетчиков uN N - Non Q.

Если, например, m выбрать равным 360, а угол JT выразить в электрических градусах, значение Q равно фазовому сдвигу, выраженному в градусах.

Для установки требуемого значения фазового сдвига и для контроля его при помощи цифрового регистрирующего блока 9 используются дискретные интервалы времени 1зап течение которых код счетчика нуль

4 обращается в

Non

- Q - tg F -m-j

ian -о При этом

ijan Q .m+j-m. Эти интервалы совпадают с интервалами обнуления счетчика 4, которые

следуют после его заполнения, т.е.

после достижения кода (т-1), ограниченного коэффициентом деления частоты. Периодичность заполнения счетчика

4 где j 0,1,2,3.... На протяжении интервала обнуления счетчика 4 код счетчика

N ijan -t,-F-m-j-ra

Q+to-F. m+j.m-to- F-m Q.

Таким образом, сложную операцию вычитания кодов счетчиков 3 и 4 для индикации воспроизводимого фазового сдвига и операцию занесения требуемого значения разности кодов, соответствующего устанавливаемому фазовому сдвигу, можно значительно упростить сводя их к записи в регистр индикатора кода счетчика 3 в течение

интервала при N0 О, а также к занесению в такие же интервагал кода Q в счетчик 3.

Циклически изменяющиеся во времени коды счетчиков 3 и 4 поразрядно

поступают на адресные входы сменных или коммутируемых запоминающих блоков 5-8/ .

Так как количество интервалов D

проксимации п всегда меньше в Ъ раз (или в крайнем случае равно) количества устойчивых состояний m счетчиков 3 и 4, некоторое количество их младших разрядов, равное tog 1, может не участвовать в формировании адресов кодов интервалов аппроксимации. При этом текущее значение адресного кода аппроксимации выражается целой частью

отношения :j , причем знак 1 означаL J ет операцию вьщеления целочисленного

,и О 4. т U п. Блоки 7 или 8

значения

дискретных значений выходного напряже-2о дискретных значений выходных напряжения преобразуют адресный код аппроксимации, формируемый старшими разря дайи счетчиков и выражающий текущую

фазу выходного напряжения Ф (I :х П в

. j

строго им соответствующие коды диск- ретных значений выходного напряженияа ( fl ) блоки 5 (или 8) приращений

преобразуют тот же адресный код в код приращения дискретного значения выходного напряжения по отношению к послед ующей ступени его аппроксимации

а (

)-я(|). в

соответствии с

НИИ, определяемой допустимым значением КИИ.

Дискретные значения, пропорциональные с коэффициентом Р приращениям вы- 25 ходных напряжений, формируются при помощи ПЦАП 12 (или 15). При формировании синусоидальных сигналов периодическая последовательность ступенчатых напряжений приращений также 30 имеет квазисинусоидальную форму со сдвигом по фазе относительно напряжений, формируемых ПЦАП 13 (или I4)s дискретных значений, на угол 1Г/2 + -ьТ-Ь/2, так как первая производная от выходного напряжения, выражающая скорость его изменения, имеет значение

35

назначением регулируемой меры фазовых сдвигом запоминающие блоки программируются, а также коммутируются или

сменяются так, что на их выходах име- ется набор кодов мгновенных значений- и их приращений для всех заданных разновидностей форм выходных напряжений. При формировании синусоидальных сигналов в эти запоминающие блоки заносятся наборы кодов выборок гар ионических функций и их приращений

а i sin .Ф(|);

а ()-а(|) з1пФ(|.,)-sin Ф(|).

Блоки 5-8 выбираются так, что количество их адресных входов позволяет выразить число п в выбранном коде., Периодическая последовательность кодов всех запоминающих блоков поступает на цифровые входы ПЦАП 12-15. При этом фронт каждой ступени имеет

конечную длительность, обусловленную влиянием паразитных и монтажных емкостей элементов 1ДАП, и может быть аппроксимирован экспонентной с постоГ- г- t

янной времени L, причем 3 L ,

г m

Количество выходных разрядов запоминающих блоков определяется разрядностью ПЦАП преобразующих в каж- дом канале коды дискретных значений выходных напряжений и коды их приращений, выражаюпще скорость нарастания (убьшания) аппроксимирующей линейной

функции, в собственно дискретные значения выходных напряжений и приращения напряжений. Количество разрядов ШЩ 12 - 15 выбирается, исходя из заданной точности воспроизведения

НИИ, определяемой допустимым значением КИИ.

Дискретные значения, пропорциональные с коэффициентом Р приращениям вы- ходных напряжений, формируются при помощи ПЦАП 12 (или 15). При формировании синусоидальных сигналов периодическая последовательность ступенчатых напряжений приращений также имеет квазисинусоидальную форму со сдвигом по фазе относительно напряжений, формируемых ПЦАП 13 (или I4)s дискретных значений, на угол 1Г/2 + -ьТ-Ь/2, так как первая производная от выходного напряжения, выражающая скорость его изменения, имеет значение

d У(ых d(A. sin23r.F.t} dt d t

A-cos2l( F- t,

T. e. сдвинута no отношению к выходному напряжению на угол /2, Дополнительный фазовый сдвиг на угол iST-f-./m обусловлен особенностями фор- мирования линейных аппроксимирующих напряжений, которые не изменяют свой знак в пределах каждого интервала аппроксимации. Значение скорости аппроксимирующего напряясения и соответствующее ей напряжение приращения на каждом участке принимается неизменным. Это напряжение преобразуется в линейно-аппроксимирующее при помощи двухтактных аппроксимируюгчих интеграторов 16 и 17 (или 18 и 19).

Управляющие входы обоих ключей подключены к младгаему разряду адресных кодов ПЗБ 6 (или 7). При уровне

логического нуля в этом разряде, характерном для каждого четного интервала аппроксимации, ключ 33 интегратора четных интервалов разомкнут, и на вькоде усилителя 23 формируется линейно нарастающий участок.

При том же уровне логического нуля на управляющем входе ключ 32 интегратора нечетных интервалов аппрок симации имеет нормально замкнутое состояние. Заряженный на предыдущем интервале конденсатор 28 разряжается по цепи через ключ 32 и разрядный резистор 30. При этом на выходе усилителя 22 формируется экспоненциально спадающее напряжение,

Б течение первого и каждого нечетного интервалов аппроксимации уровне логической 1 по управляющим входам

ключ 33 замыкается, а ключ 32 размыкается. В этом случае аппроксимирующий интегратор 17 (19) нечетных интервалов формирует линейно нарастающее напряжение, а интегратор четных интервалов - экспоненциально спадающее.

При изменении полярности напряжения приращений, вьщава.емого ПЦАЛ 12 (или 15), что эквивалентно перемене знака скорости аппроксимирующей функции и имеет место на интервале от максимального до минимального значений формируемого напряжения, аппроксимирующие интеграторы также изменяю полярность выходного напряжения и выдают линейно спадающее и экспоненциально нарастающее напряжения и т.д.

Параметры элементов аппроксимирующих интеграторов RM и С, а также значение коэффициента пропорциональности напряжения приращений Р подби- раются так, что к моменту завершения

каждого, например

1}

го интервала

аппроксимации, линейное напряжение на выходе интегратора равно дискретному значению напряжения последующег (fjf +)-го интервала аппроксимации.

Полученные напряжения дискретных значений выходных напряжений, линейно-аппроксимирующее и экспоненциально компенсирующее на каждом интервале аппроксимации суммируются при помощи сумматора 20 (или 21). При этом масштабные коэффициенты суммирования по входам, связанным с аппроксимиру

ющими интеграторами, подбираются так, что амплитуда линейно-аппроксимирующего напряжения, приведенная к выходу сумматора, точно соответствует ступени приращения на последующем интервале аппроксимации.

Значение разрядных резисторов аппроксимирующих интеграторов подбираются так, что постоянная времени цепи разряда Cf)

Тр Сп (Rp + RK), где R - сопротивление открытого

ключа 32 (33),

эквивалентна суммарной постоянной времени заряда паразитных и монтажных емкостей ПЦАЛ 13 (14) дискретных значений и П1ДАП 12 (15) приращений выходных напряжений.

На аналоговые входы обоих ПЦДП каждого канала поступает постоянное напряжение через потенциометр 10 (или 11) от источника опорного напряжения DO, ПЦАП 12 и 13 (или 14 и 15) преобразуют циклически изменяющиеся во времени цифровые коды, соответствующие дискретным значениям напряжений А ():р ) и их приращениям ДА( т ),

L -t-J.LiJ

в аналоговые напряжения, пропорциональные опорному напряжению Ц, и коэффициенту деления потенциометра 10 или ПК.

Выходное напряжение сумматора 20

(или 21) определяется выражением

1 -V f4l n;-cn

IX

X к- и„ .

Регулировка амплитуды выходных напряжений меры фазовых сдвигов осуществляется путем изменения значений

К. Учитьюая, что вариация значений К не оказьюает влияние на процесс формирования кодов дискретных значений напряжений и их приращений, на точностные характеристики ПЦАП, а

также на активные и реактивные составляющие параметров их звеньев, относительный комплексный спектр их выходных напряжений также не зависит от значений К, а следовательно, предлагаемая мера фазовых сдвигов свободна от амплитудно-фазовых погрешностей.

Изменяя значения К во времени, можно модулировать по амплитуде выходные напряжения меры фазовых сдвигов и таким образом автоматизировать процесс измерения значений амплитудно-фазовых horpemHOCTeft фазометров, проверяемых при помощи предлагаемой меры фазовых сдвигов.

Формула изобретения

Регулируемая мера фазовых сдвигов, содержащая первый и второй счетчики, счетные входы которых объединены и соединены с выходом генератора импульсов, блок записи кода, выходы ко- 15 которых соединены с выходом третьего

торого подключены к входам Предустановка первого счетчика, информационные вькоды которого соединены через первый постоянный запоминающий

перемножающего цифроаналогового преобразователя, выходы первого и второго аппроксимирующих интеграторов соединены соответственно с первым и втоблок с информационными входами перво- 20 рым входами первого сумматора, трего перемножающего аналого-цифрового преобразователя и непосредственно с информационным входом регистрирующего блока, управляющий вход которого соединен с входом блока записи кода и выходом второго счетчика, информационные выходы которого через второе постоянное запоминающее устройство подключены к информационным входам второго перемножающего цифроаналогового преобразователя, аналоговые вхо- дь1 первого и второго перемножающих цифроаналоговых преобразователей через соответствующие регулируемые потенциометры соединены с источником опорного напряжения, отличающаяся тем, что, с целью повышения точности, в нее введены третий и

четвертый постоянные запоминающие блоки, третий и четвертый перемножающие цифроаналоговые преобразователи, четыре аппроксимирующих интегратора и два сумматора, причем аналоговые входы третьего и четвертого перемножающих цифроаналоговых преобразователей соответственно i соединены с выходом первого и второго потенциометров, младший разряд первого счетчика соединен с входами управления первого и второго аппроксимирующих интеграторов, информационные входы

перемножающего цифроаналогового преобразователя, выходы первого и второго аппроксимирующих интеграторов соединены соответственно с первым и втотий вход которого соединен с вькодом первого перемножающего цифроаналогового преобразователя, младший разряд второго счетчика подключен к входам

управления третьего и четвертого аппроксимирующих интеграторов, информационные входы которых соединены с выходом четвертого перемножающего цифроаналогового преобразователя, выходы третьего и четвертого интеграторов подключены соответственно к первому и второму входам второго сумматора, третий вход которого соединен с выходом второго перемножающего цифроаналогового преобразователя, а выходы первого и второго сумматоров являются соответственно первым и вторым выходами регулируемой меры.

.

| название | год | авторы | номер документа |

|---|---|---|---|

| Широкодиапазонный калибратор фазовых сдвигов | 1987 |

|

SU1525614A1 |

| Широкодиапазонный калибратор фазовых сигналов | 1984 |

|

SU1226339A1 |

| Цифровой автокомпенсационный фазометр | 1983 |

|

SU1166010A1 |

| Радиоимпульсный фазометр | 1985 |

|

SU1257558A1 |

| Датчик фазы | 1986 |

|

SU1370598A1 |

| Преобразователь угла поворота вала в код | 1987 |

|

SU1478331A1 |

| Способ управления многофазным инвертором и устройство для его осуществления | 1984 |

|

SU1458951A1 |

| Аналого-цифровое устройство для решения системы дифференциальных уравнений | 1987 |

|

SU1462378A1 |

| ДВУХФАЗНЫЙ ГЕНЕРАТОР ГАРМОНИЧЕСКИХ СИГНАЛОВ | 1990 |

|

RU2033684C1 |

| Функциональный генератор | 1983 |

|

SU1141427A1 |

Изобретение относится к измерительной технике и предназначено для формирования двух синусоидальньпс напряжений либо напряжений любой другой формы с заданным значением их амплитуды и прецизионно-регулируемым фазовым сдвигом между основными гармониками напряжений. Регулируемая мера может быть использована для проверки фазоизмерительной и фазозадаю- щей аппаратуры. Цель изобретения - повышение точности воспроизведения абсолютных значений задаваемых фазовых сдвигов - достигается путем формирования выходных сигналов методом коррекции ступенчатых квазисинусоидальных напряжений с помощью линейной аппроксимации напряжений на каждом интервале их формирования. Регулируемая мера содержит блок 1 записи кода, генератор 2 импульсов, счетчики 3 и 4, постоянные запоминающие блоки 5-8, регистрирующий блок 9, потенциометры 10 и II, аналого-цифровые преобразователи 12-15, аппроксимирующие интеграторы 16-9 и сумматоры 20- 21. Изменяя коэффициент деления lio- тенциометра 10 или II во времени, можно модулировать по амплитуде выходное напряжение регулируемой меры и таким образом автоматизировать процесс измерения значений амплитудно-фазовых погрешностей фазометров, проверяемых при помощи предлагаемой меры фазовых сдвигов. 2 ил. i (Л Й6/Х/ : 4 О СО 4 StfJT 2

Авторы

Даты

1987-10-23—Публикация

1985-09-10—Подача