Изобретение относится к измеритеной технике и может быть применено для определения шероховатости поверностей при использовании его в различных областях промьппленности.

Целью изобретения является повышение точности и быстродействия измрений за счет автоматизированного измерения средней разности межд,у пятью самыми большими выступами и пятью самыми большими впадинами измеряемой поверхности в пр.еделах одной базовой длины.

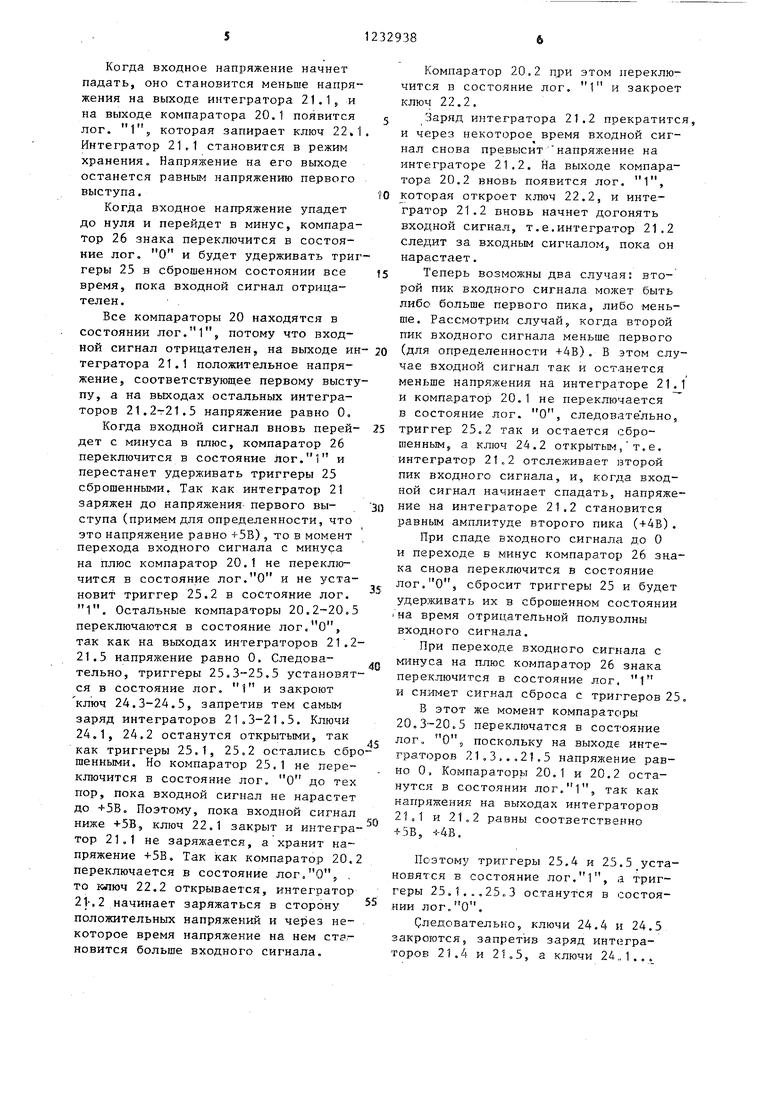

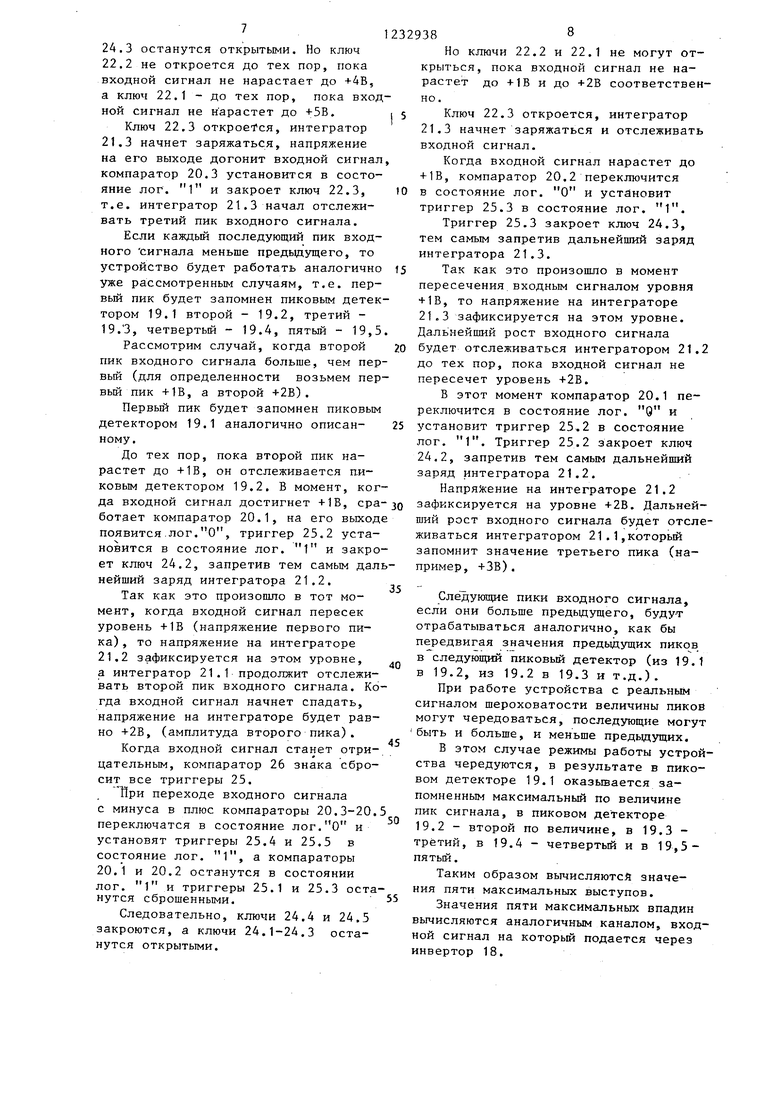

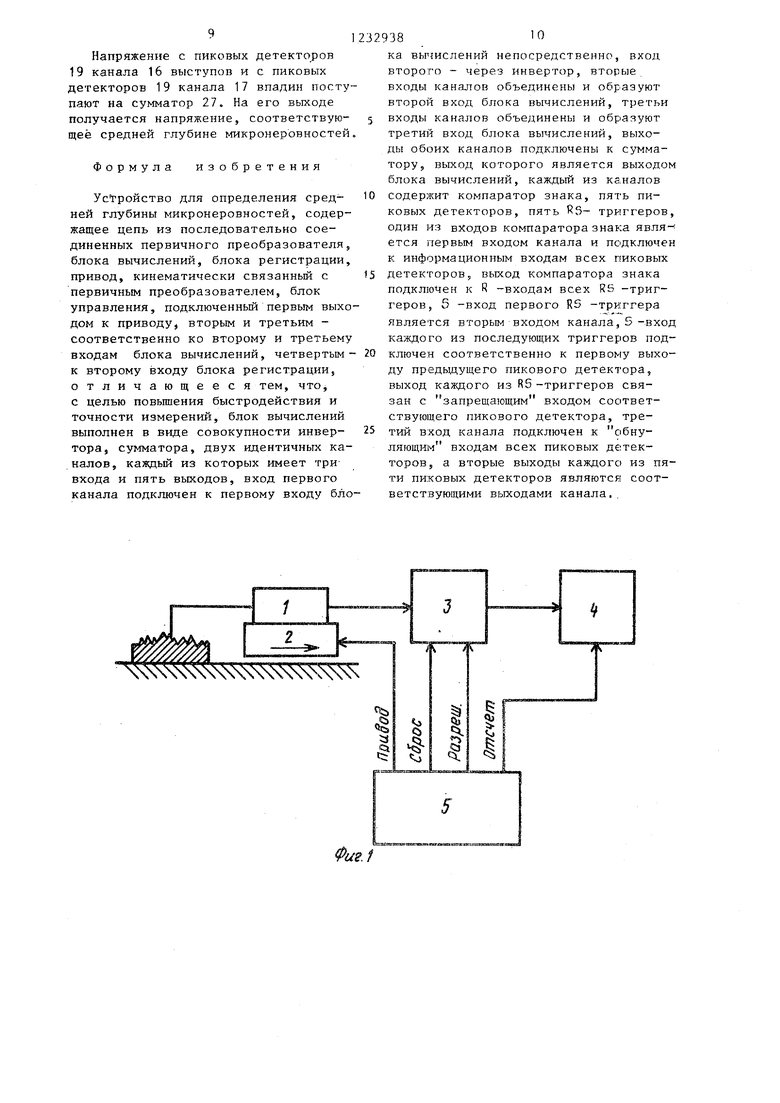

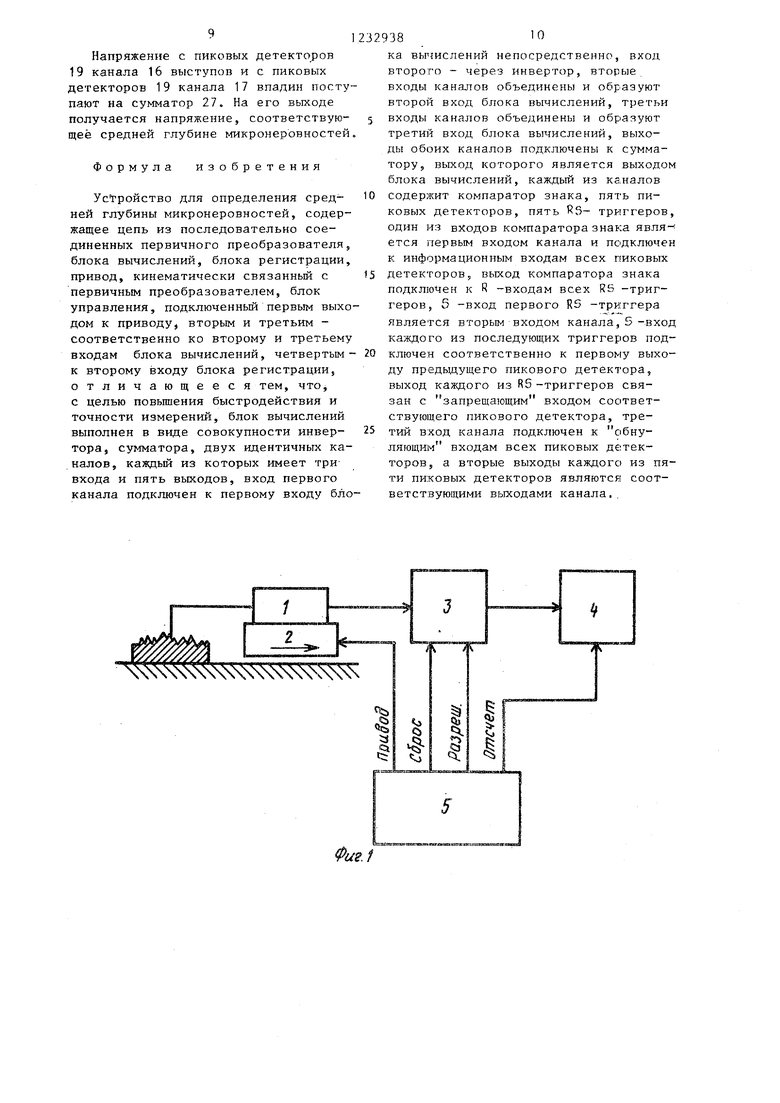

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - прин- ципиальная схема блока управления; на фиг, 3 - функциональная схема блока вычисления; на фиг. 4 - принципиальная схема одного канала блока вычислений.

Устройство содержит первичньй преобразователь 1 и привод 2, которьм перемещает первичньй преобразовател 1 по контролируемой поверхности (фиг.

Вход блока 3 вычисления подключе к выходу первичного преобразователя 1. Выход блока 3 вычислений подключен ко входу блока 4 регистрации. Блок 5 управления соединен с приводом 2, с блоком 3 вычислений и бло- ком А регистрации.

Блок 5 управления (фиг.2) содержит тактовьш генератор 6, делитель частоты, двоично-десятичный счетчик 8, дешифратор 9, кнопку 10 Пуск с нагрузочным резистором 11, конденсатор 12 с зарядным резистором 13, триггер 14 и усилитель 15 мощности.

Блок 3 вычислений (фиг.З) содержит два идентичных канала, один - для вычисления высоты пяти наибольших выступов, другой для вычисления глубины пяти наибольших впадин.

-г .

Первый вход блока 3 вычислении (фиг.З) подключен ко входу канала 1 выступов непосредственно, а ко вход канала 17 впадин через инвертор 18. Канал 16 выступов содержит пять пиковых детекторов 19,1...19.5, на вход которых подается сигнал с выхода первичного преобразователя 1 (фиг.4).

rfi

Каждый из пиковых детекторов 19 состоит из компаратора 20, интегра- тора 21, зарядного ключа 22, обнуляющего ключа 23, запрещающего ключа 24.

s

О

И 20

25 30

5

0

O

Канал 16 выступов содержит пять КЭ-триггеров 25. Выход каждого из них связан с запрещающим ключом 24 соответствующего ему пикового детектора 19. Входы запрещающих ключей 24 в каждом из пиковых детекторов являются запрещающими входами последних.

Вход R каждого триггера 25 связан с выходом компаратора 26 знака, а вход 5 каждого триггера 25 связан с выходом компаратора 20 предыдущего пикового детектора 19.

Выходы компараторов 20 являются первыми выходами пиковых детекторов. Вход 5 триггера 25,1 подключен к второму входу блока 3 вычислений.

Выходы всех пиковых детекторов канала 16 выступов (фиг.З), а также канала 17 впадин, являющиеся вторыми выходами пиковых детекторов, подключены к входу сумматора 27.

Запрещающие ключи 24 пиковых детекторов 19 соединены с источником отрицательного напряжения резистор 28 для заряда интеграторов 21 с общим проводом через диод 29 для ограничения напряжения на ключах 22 и 24.

Устройство (фиг.1) работает следующим образом.

В начале измерения блок 5 управления подает питание на электродвигатель привода 2.

При зтом привод 2 начинает перемещать , первичный прео.бразователь 1 по измеряемой поверхности. На выходе преобразователя 1 появляется напряжение, соответствующее неровностям поверхности, которое подается на вход блока 3 вычислений. Через некоторое время после подачи питания на привод 2 блок 5 управления формирует сигнал сброса для блока 3 вычислений, а затем подает сигнал оазрешения вычисления.

Блок 3 вычислений начинает обрабатывать сигнал с выхода преобразо-. вателя 1. Через заданное время блок 5 управления прерывает сигнал разрешения и выдает импульс отсчета,.ко- торьй фиксирует в блоке 4 регистрации выходной сигнал блока 3 вычислений.. На этом измерение заканчивается.

Блок 5 управления (фиг.2) работает следующим образом.

При нажатии кнопки 10 Пуск на выходе триггера 14 устанавливается высокий уровень напряжения. Через усилитель 15 мощности это напряжение подается на электродвигатель првода 2. При этом привод 2 начинает перемещение преобразователя 1 по измеряемой поверхности.

Одновременно высокий уровень напряжения на выходе триггера 14 разблокирует делитель 7 частоты и дво- ично-десятичньй счетчик 8, Делитель 7 частоты начинает считать импульсы тактового генератора 6.

Каждьй десятый импульс тактового генератора продвигает двоично- десятичный счетчик 8. Состояние тре младших разрядов счетчика 8 расшифровывается дешифратором 9, который формирует низкий уровень на выходе Сброс на время первого такта счетчика 8 и высокий уровень на выходе Разрешение на время тактов со второ по седьмой.При достижении счетчиком восьмого такта на выходе Отсчет появляется высокий уровень напряжения. Одновременно на инверсном выходе старшего разряда счетчика 8 появляется низкий уровень, который поступает на триггер 14 и устанавливает на его выходе низкий уровень При этом сбрасывается делитель 7 частоты и счетчик 8, прерывается сигнал Отсчет, а также снимается питание с электродвигателя привода 2 (через усилитель 15 мощности), т.е. схема возвращается в исходное состояние.

Блок 3 вычислений при работе канла 16.выступов (фиг,4) функционируе следующим образом.

Момент времени, когда выходное нпряжение преобразователя 1 переходи через ноль (с минуса на плюс),выбирается в качестве исходного.

Когда на входе канала 16 выступов минус, компаратор 26 знака выдает лог. О и удерживает все пять R5 - триггеров 25 в сброшенном состоянии.

Когда знак входного напряжения ме-50 жение нарастает, напряжение на пыняется на плюс, компаратор 26 знака переключается в лог. 1 и перестает удерживать RS -триггеры 25 в сброшенном состоянии.

Так как в исходном состоянии на выходе всех интеграторов 21 напряжение равно нулю (они предварительно сброшены с помощью ключей 23 по

12329384

сигналу Сброс блока 5 управления), то на неинвертирующих входах всех компараторов 20 напряжение равно нулю, и при смене полярности входного

напряжения с минуса на плюс все компараторы 20 переключаются в лог. О. При этом все R5 -триггеры 25 устанавливаются в лог. 1, кроме триггера 25.1, так как на его 5 -вход

на время вычисления подана лог. 1 (с выхода Разрешение блока 5 управления) .

Лог. 1 с триггеров 25. 2-25.5 поступает на ключи 24.2-24.5, которые запрещают заряд интеграторов 21.2-21.5.

Так как триггер 25.1 остался сброшенным, то лог. О с его выхода открывает ключ 24, разрешая тем самым заряд интегратора 21.1.

Так как на выходе компараторов

20.1 появился лог. О в момент перехода входного напряжения с мину 0

0

5

са на плюс, то этот лог. О открывает зарядньи ключ 22, соединенный по- 5 следовательно с ключом 24.1.

Так как ключ 24,1 открыт, то ток, поступающий от источника отрицательного напряжения питания через резистор 28, заряжает интегратор 21,1 и напряжение на выходе последнего нарастает в сторону положительных значений .

Если скорость нарастания напряжения на выходе интегратора 21.1 больше, чем скорость нарастания входного сигнала, то через некоторое время напряжение на выходе интегратора 21,1 станет больше входного сигнала и компаратор 20.1 переключится в состояние лог.1, которая закроет ключ 22.1, Заряд интегратора прекратится. Через некоторое время входное напряжение превысит напряжение на выходе интегратора 21.1. На выходе компаратора 21.1 снова появится лог, О, который откроет ключ 22,1,

Интегратор 21.1 вновь начнет заряжаться .

Таким образом, пока входное напря5

ходе интегратора 21.1 следит за ним.

Рассмотрим момент, когда входное напряжение перестанет нарастать (вершина первого выступа).

Так как полярность зарядного тока интегратора 21.1 неизменна, то отследить спад входного напряжения сигнала он ие может.

Когда входное напряжение начнет падать, оно становится меньше напряжения на выходе интегратора 21.1 и на выходе компаратора 20.1 появится лог. I, которая запирает ключ Интегратор 2К1 становится в режим хранения Напряжение на его выходе останется равным напряжению первого выступа.

Когда входное напряжение упадет до нуля и перейдет в минус, компаратор 26 знака переключится в состояние лог. О и будет удерживать триггеры 25 в сброшенном состоянии все время, пока входной сигнал отрицателен.

Все компараторы 20 находятся в состоянии лог.1, потому что входной сигнал отрицателен, на выходе ий тегратора 21.1 положительное напряжение, соответствующее первому выступу, а на выходах остальных интеграторов 21.2-21.5 напряжение равно О,

Когда входной сигнал вновь перей- дет с минуса в плюс, компаратор 26 переключится в состояние лог.1 и перестанет удерживать триггеры 25 сброшенными. Так как интегратор 21 заряжен до напряжения первого вы- ступа (примем для определенности, что это напряжение равно +5В), то в момент перехода входного сигнала с минуса на плюс компаратор 20.1 не переключится в состояние лог.О и не уста

новит триггер 25.2 в состояние лог. 1. Остальные компараторы 20.2-20.5

переключаются в состояние лог.

О

так как на выходах интеграторов 21.2- 21.5 напряжение равно 0. Следова- тельно, триггеры 25,3-25.5 установятся в состояние лог, 1 и закроют ключ 24.3-24.5, запретив тем самым заряд интеграторов ,5. Ключи 24.1, 24.2 останутся открытыми, так как триггеры 25.1, 25,2 остались сброшенными. Но компаратор 25.1 не переключится в состояние лог. О до тех пор, пока входной сигнал не нарастет до . Поэтому, пока входной сигнал ниже 4-5В, ключ 22.1 закрыт и интегратор 21.1 не заряжается, а хранит напряжение 4-5Во Так как компаратор 20.2 переключается в состояние лог.О, . то ключ 22.2 открывается, интегратор 2|-. 2 начинает заряжаться в сторону положительных напряжений и через некоторое время напряжение на нем становится больше входного сигнала.

10

5

0

5 о

S

Компаратор 20,2 при этом переключится в состояние лог, 1 и закроет ключ 22,2,

Заряд интегратора 21.2 прекратится, и через некоторое время входной сигнал снова превысит напряжение на интеграторе 21,2. На выходе компаратора 20,2 вновь появится лог. 1, которая откроет ключ 22.2, и интегратор 21,2 вновь начнет догонять входной сигнал, т.е.интегратор 21.2 следит за входным сигналом, пока он нарастает,

Теперь возможны два случая: второй пик входного сигнала может быть либо больше первого пика, либо меньше. Рассмотрим случай, когда второй пик входного сигнала меньше первого (для определенности +4В), В этом случае входной сигнал так и останется меньше напряжения на интеграторе 21,1 и компаратор 20,1 не переключается в состояние лог, О, следовательно, триггер 25.2 так и остается сброшенным, а ключ 24,2 открыть }, т. е. интегратор 21.2 отслеживает 1зторой пик входного сигнала, и, когда входной сигнал начинает спадать, напряжение на интеграторе 21,2 становится равным амплитуде второго пика (+4В),

При спаде входного сигнала до О и переходе в минус компаратор 26 знака снова переключится в состояние лог, сбросит триггеры 25 и будет удер:жинать их в сброшенном состоянии 1 на время отрицательной полуволны входного сигнала.

При переходе входного сигнала с минуса на плюс компаратор 26 знака переключится в состояние лог. 1 и сн:нмет сигнал сброса с триггеров 25.

В этот же момент компаратсфы 20.3-20,5 переключатся в состояние лог. О поскольку на выходе интеграторов 21,3,.,21,5 напряжение равно О, Компараторы 20,1 и 20.2 останутся в состоянии лог/Ч, так как напряжения на выходах интеграторов 21 И и 21.2 равны соответственно fSB, -4В.

Поэтому триггеры 25,4 и 25,5 установятся в состояние лог,1, а триггеры 25,1.., останутся в состоянии лог.О,

Следовательно, ключи 24,4 и 24,5 закроются, запретив заряд интезгра- торов 21,4 и 21 „5, а ключи 24,. 1.,,

24,3 останутся открытыми. Но ключ

22.2не откроется до тех пор, пока входной сигнал не нарастает до +4В,

а ключ 22.1 - до тех пор, пока входной сигнал не нарастет до +5В. Ключ 22.3 откроемся, интегратор

21.3начнет заряжаться, напряжение

на его выходе догонит входной сигнал компаратор 20.3 установится в состояние лог. 1 и закроет ключ 22.3, т.е. интегратор 21.3 начал отслеживать третий пик входного сигнала.

Если каждый последующий пик входного сигнала меньше предыдущего, то устройство будет работать аналогично уже рассмотренным случаям, т.е. первый пик будет запомнен пиковым детектором 19.1 второй - 19.2, третий - 19.3, четвертью - 19.4, пятый - 19,5

Рассмотрим случай, когда второй пик входного сигнала больше, чем пер- вьм (для определенности возьмем пер- вьш пик +1В, а второй +2В).

Первый пик будет запомнен пиковым детектором 19.1 аналогично описанному.

До тех пор, пока второй пик нарастет до +1В, он отслеживается пиковым детектором 19.2. В момент, ког

да входной сигнал достигнет +1В, ера-зо зафиксируется на уровне +2В. Дальнейботает компаратор 20.1, на его выходе появится.лог.О, триггер 25.2 установится в состояние лог. 1 и закроет ключ 24.2, запретив тем самым дальнейший заряд интегратора 21.2.

Так как это произошло в тот момент, когда входной сигнал пересек уровень +1В (напряжение первого пика) , то напряжение на интеграторе 21.2 зафиксируется на этом уровне, а интегратор 21.1 продолжит отслеживать второй пик входного сигнала. Когда входной сигнал начнет спадать, напряжение на интеграторе будет равно +2В, (амплитуда второго пика).

Когда входной сигнал станет отрицательным, компаратор 26 знака сбросит все триггеры 25.

При переходе входного сигнала с минуса в плюс компараторы 20.3-20.5 переключатся в состояние лог.О и установят триггеры 25.4 и 25.5 в состояние лог. 1, а компараторы 20.1 и 20.2 останутся в состоянии

лог. 1 и триггеры 25.1 и 25.3 останутся сброшенными.

Следовательно, ключи 24.4 и 24.5 закроются, а ключи 24.1-24.3 останутся открытыми.

to

.

20

2329388

Но ключи 22.2 и 22.1 не могут открыться, пока входной сигнал не нарастет до +1В и до +2В соответственно.

Ключ 22.3 откроется, интегратор 21.3 начнет заряжаться и отслеживать входной сигнал.

Когда входной сигнал нарастет до +1В, компаратор 20.2 переключится в состояние лог. О и установит триггер 25.3 в состояние лог. 1.

Триггер 25.3 закроет ключ 24.3, тем самым запретив дальнейший заряд интегратора 21.3.

Так как это произошло в момент пересечения входным сигналом уровня +1В, то напряжение на интеграторе 21.3 зафиксируется на этом уровне. Дальнейший рост входного сигнала будет отслеживаться интегратором 21.2 до тех пор, пока входной сигнал не пересечет уровень +2В.

В этот момент компаратор 20.1 переключится в состояние лог. Q и установит триггер 25,2 в состояние лог. 1. Триггер 25.2 закроет ключ 24.2, запретив тем самым дальнейший заряд интегратора 21.2.

Напря5кение на интеграторе 21.2

15

25

5

0

5

0

5

ший рост входного сигнала будет отслеживаться интегратором 21.1,который запомнит значение третьего пика (например, + ЗВ).

Следующие пики входного сигнала, если они больше предыдущего, будут отрабатываться аналогично, как бы передвигая значения предыдущих пиков в следующий пиковый детектор (из 19.1 в 19.2, из 19.2 в 19.3 и т.д.).

При работе устройства с реальным сигналом шероховатости величины пиков могут чередоваться, последующие могут быть и больше, и меньше предыдущих.

В этом случае режимы работы устройства чередуются, в результате в пиковом детекторе 19.1 оказьшается запомненным максимальный по величине пик сигнала, в пиковом детекторе 19.2 - второй по величине, в 19.3 - третий, в 19.4 - четвертый и в 19,5- пятый.

Таким образом вычисляются значения пяти максимальных выступов.

Значения пяти максимальных впадин вычисляются аналогичным каналом, входной сигнал на который подается через инвертор 18.

Напряжение с пиковых детекторов 19 канала 16 выступов и с пиковых детекторов 19 канала 17 впадин поступают на сумматор 27. На его выходе получается напряжение, соответствующее средней глубине микронеровностей

Формула изобретения

Ус гройство для определения ср)ед- ней глубины микронеровностей, содержащее цепь из последовательно соединенных первичного преобразователя, блока вычислений, блока регистрации, привод, кинематически связанный с первичным преобразователем, блок управления, подключенный первым выходом к приводу вторым и третьим - соответственно ко второму и третьему входам блока вычислений, четвертым- к второму входу блока регистрации, отличающееся тем, что, с целью повьшения быстродействия и точности измерений, блок вычислений выполнен в виде совокупности инвертора j сумматора, двух идентичных каналов, каждый из которых имеет три входа и пять выходов, вход первого канала подключен к первому входу бло3293810

ка вьпшслений непосредственно, вход второго - через инвертор, вторые входы каналов объединены и образуют второй вход блока вычислений, третьи

5 входы каналов объединены и образуют третий вход блока вычислений, выходы обоих каналов подключены к сумматору, выход которого является выходом блока вычислений, каждый из каналов

0 содержит компаратор знака, пять пиковых детекторов, пять R5 триггеров, один из входов компаратора знака я впя- ется первым входом канала и подключен к информационным входам всех пиковых

5 детекторов, выход компаратора знака подключен к R -входам всех RS -триггеров, 6 -вход первого RS -триггера является вторым входом канала,5 -вход каждого из последующих триггеров под0 ключен соответственно к первому выходу предыдущего пикового детектора, выход каждого из R5 -триггеров связан с запрещающим входом соответствующего пикового детектора, тре5 тий вход канала подключен к обнуляющим входам всех пиковых детекторов, а вторые выходы каждого из пяти пиковых детекторов являются соответствующими выходами канала,.

6iiod

Разреа. сброс

. Сброс

Ьиод

R

R ZI

R

difxod Ч)

К

R

1

R

Z к

Фия.З

Вход

Роз шбние cSpoc

ш

tS5

ФшЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля чувствительности побочных и интермодуляционных каналов в радиоприемниках | 1987 |

|

SU1425858A1 |

| МОДУЛЯЦИОННЫЙ РАДИОМЕТР | 2001 |

|

RU2187824C1 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КОЭФФИЦИЕНТА ЗАТУХАНИЯ МЕЖДУ АНТЕННАМ | 1995 |

|

RU2127889C1 |

| Измеритель скорости звука | 1990 |

|

SU1758444A1 |

| Способ преобразования временного сдвига между двумя сигналами и устройство для его осуществления | 1989 |

|

SU1723560A1 |

| ВОЗБУДИТЕЛЬ РАДИОПРИЕМНИКА | 1990 |

|

RU2119250C1 |

| Устройство для обработки сигнала лазерного доплеровского анемометра | 1987 |

|

SU1525579A1 |

| Устройство для определения показателей гемодинамики | 1989 |

|

SU1828740A1 |

| Устройство для распознавания сигналов объектов | 1989 |

|

SU1674183A1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

Изобретение относится к измерительной технике и может использоваться для определения шероховатости в различных областях промьшшен- ности. Целью изобретения является ловышение точности и быстродействия измерений за счет автоматизированного измерения средней разности между пятью самыми большими выступами и пятью самыми большими впадинами измеряемой поверхности в пределах одной базовой длины. В процессе измерения привод перемещает первичньй преобразователь по измеряемой поверхности. Напряжение, пропорциональное неровностям поверхности, подается в блок вычислений и регистрируется в блоке регистрации. Работа устройства синхронизируется блоком управления. Блок вычислений включает в себя два идентичных канала, на вход первого из которых сигнал с преобразователя поступает непосредственно, на вход второго - через инвертор. Каждый из каналов включает пять пиковых детекторов и пять триггеров. В зависимости от величины выступов (впадин) контролируемой поверхности на выходах пиковых детекторов, канала выступов и канала впадин появляются напряжения, пропорциональные пяти максимальным выступам и пя- - ти максимальным впадинам на заданной базовой длине. Указанные сигналы суммируются сумматором, на выходе которого получается напряжение, соответствующее средней глубине микронеровностей. 4 ил. i ю САЭ to СО со оо

Редактор Н. Егорова

Составитель К) Петраковский

Техред О.СопкеКорректор И.Эрдейк

Заказ 2151 ff QТираж 670Подписное

ВНИИПИ Государственного комитета СССР

по делаем Нзобретений и открытий 113035, Москва, Ж-ЗЗ, Раушская наб., д„ 4/5

Производственно-полиграфическое предприятие, т, Ужгород, ул. Проектная, 4

| Способ определения абразивныхВКлючЕНий HA пОВЕРХНОСТи дЕТАлЕй | 1976 |

|

SU800606A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ИМИТАТОР СИГНАЛОВ МОСТОВЫХ ТЕНЗОРЕЗИСТОРНЫХ ДАТЧИКОВ | 2016 |

|

RU2620895C1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-05-23—Публикация

1984-12-13—Подача