Изобретение относится к измерительной технике и предназначено для преобразования временного сдвига между сигналами в интервал времени.

Устройство для реализации способа содержит два одинаковых канала преобразования, включающие нормализаторы уровня сигналов, преобразователи напряжение- ток и общую часть, состоящую из формирователя, одновибратора, двух ключей, интегрирующего конденсатора, нуль-орга на, двух триггеров, блока управления и устройства для измерения интервала времени

1.

Недостатками известного способа и устройства являются низкое быстродействие, вызванное необходимостью приведения входных сигналов к одному уровню, и невозможность измерения временных сдвигов между одиночными сигналами,

Наиболее близким к предлагаемому по технической сущности способу является способ преобразования временного сдвига между двумя сигналами, основанный на па- .раллельном интегрировании неинвертированных входных сигналов, причем время интегрирования входных сигналов больше длительности фронтов и ожидаемой длительности между сигналами, затем инвертировании входных сигналов, масштабном преобразовании по амплитуде и их интегрировании, формировании начала и конца выходного временного интервала при достижении проинтегрированными инвертированными сигналами нулевого уровня

И.

Устройство для реализации способа содержит два одинаковых канала преобразования, каждый из которых содержит интегратор, электронный ключ, компаратор, масштабный инвертор и коммутатор, а также логический элемент Неравнозначность и блок управления 2.

Недостатком известного способа и устройства является невозможность измерения временных сдвигов между одиночными сигналами треугольной или трапецеидальной формы с вершиной малой длительности, а также невозможность определения последовательности поступления входных сигналов.

Цель изобретения - расширение функциональных возможностей.

Цель достигается тем, что в способе преобразования временного сдвига между двумя сигналами, основанном на параллельном интегрировании сигналов, за время интегрирования сигналов, большее длительности фронтов и ожидаемой длительности между сигналами, инвертировании сигналов, масштабном преобразовании по амплитуде и их интегрировании, формировании начала и конца выходного временного интервала при достижении

проинтегрированными инвертированными сигналами нулевого уровня, проводят параллельное преобразование мгновенных значений входных сигналов путем отслеживания входных сигналов до достижения мак0 симального значения и запоминания этого значения на определенное время, а затем проводят параллельное интегрирование преобразованных сигналов, а также определяют последовательность поступления

5 входных сигналов.

Способ реализуется устройством, содержащим два одинаковых канала, каждый из которых содержит интегратор, электронный ключ, компаратор, масштабный инвер/0 тор и коммутатор, а также логический

элемент Неравнозначность и блок управления, выход масштабного инвертора присоединен к второму входу коммутатора, выход которого подключен к входу интегра5 тора и электронного ключа, выходы которых объединены и подключены к входу компаратора, а входы компараторов обоих канала присоединены к первому и второму входам, элемента Неравнозначность, при этом

0 первый выход блока управления соединен с управляющими входами коммутаторов и входами стробирования компараторов обоих каналов, а второй его выход соединен с управляющими входами электронных клю5 чей обоих каналов, в которое дополнительно введены устройство для определения последовательности поступления входных сигналов и индикатор, а каждый из каналов дополнительно содержит пиковый детек0 тор, причем к входу каждого канала подключен вход пикового детектора, выход которого присоединен к входу масштабного инвертора и первому входу коммутатора, а второй вход блока управления соединен с

5 управляющими входами пиковых детекторов обоих каналов, входы устройства для определения последовательности поступления входных сигналов подключены к выходу пикового детектора каждого из

0 каналов, а выход устройства присоединен к входу индикатора.

Заявленная совокупность существенных признаков не известна ни из аналогов, ни из прототипа, позволяет достичь постав5 ленную цель и, следовательно, соответству,- ет критерию существенные отличия.

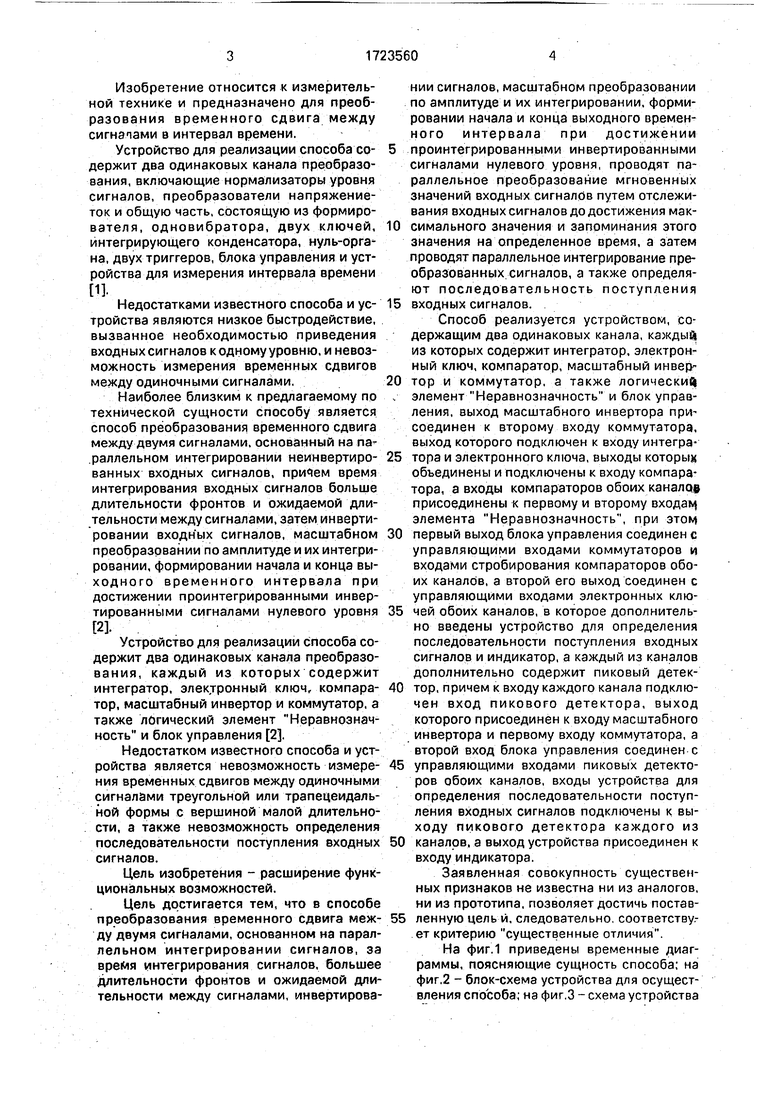

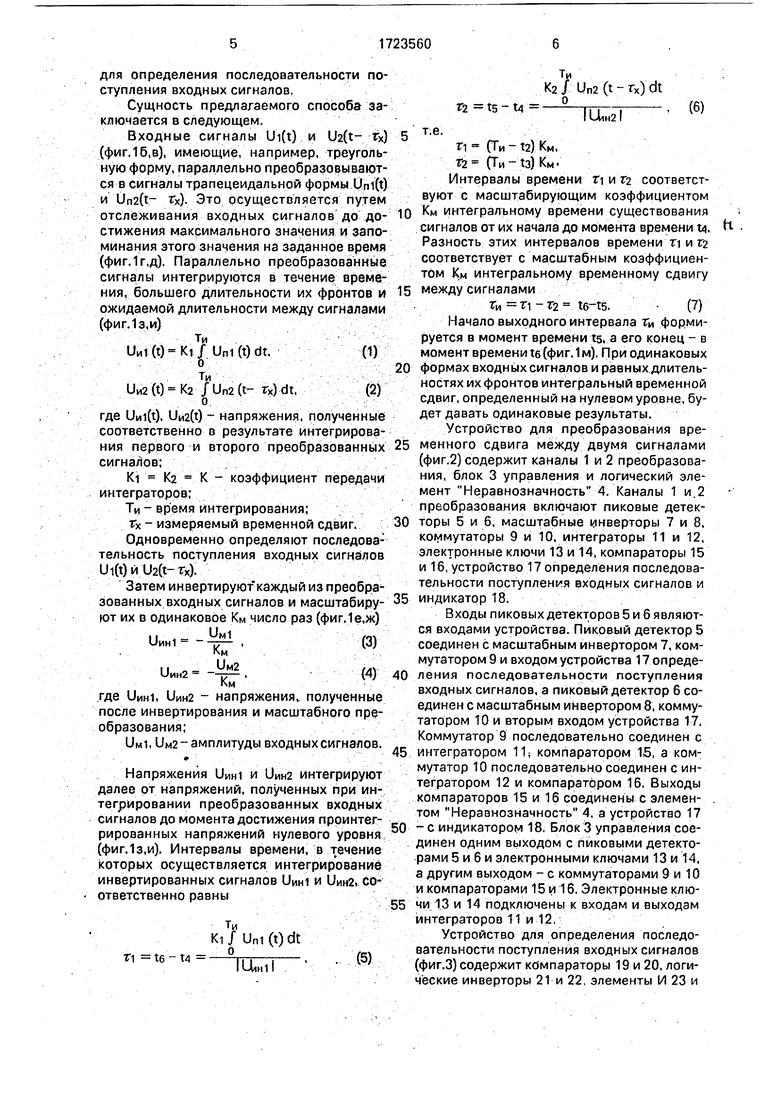

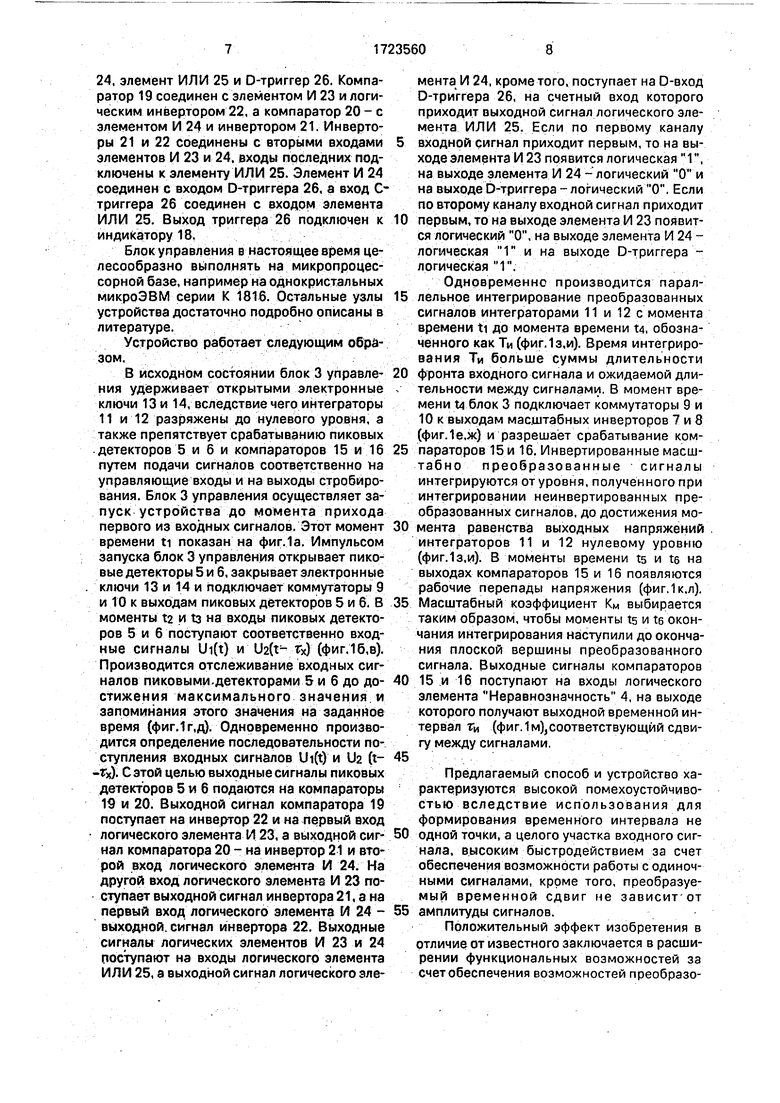

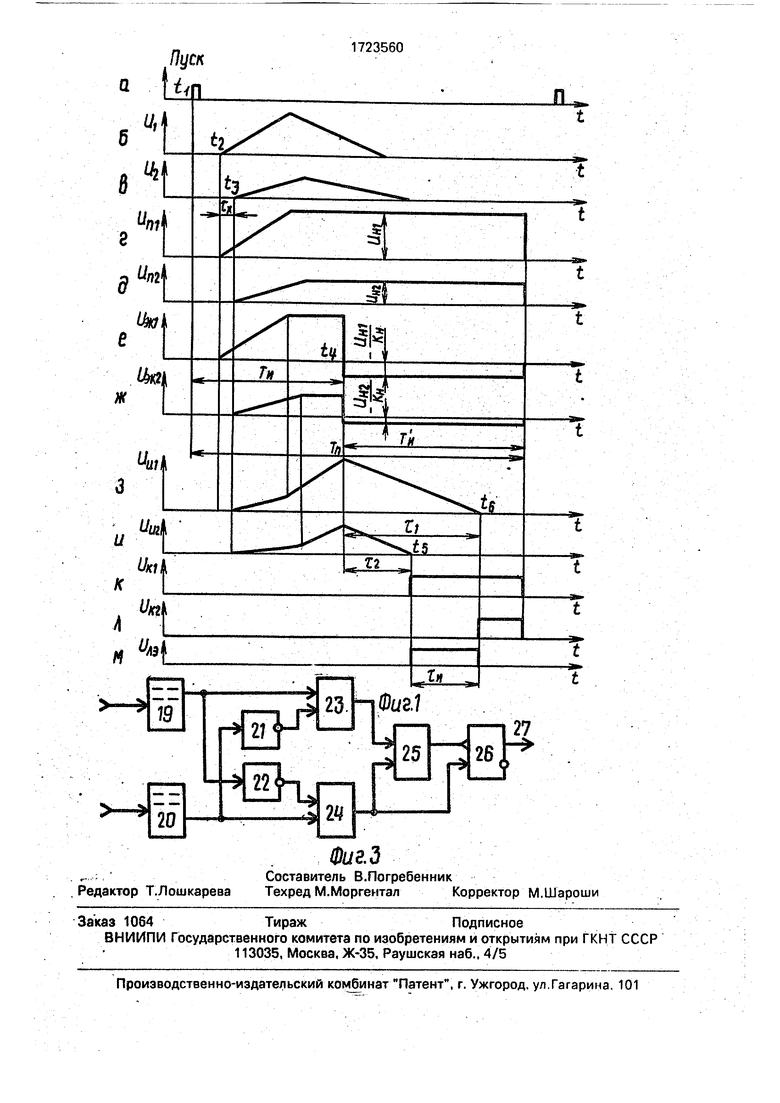

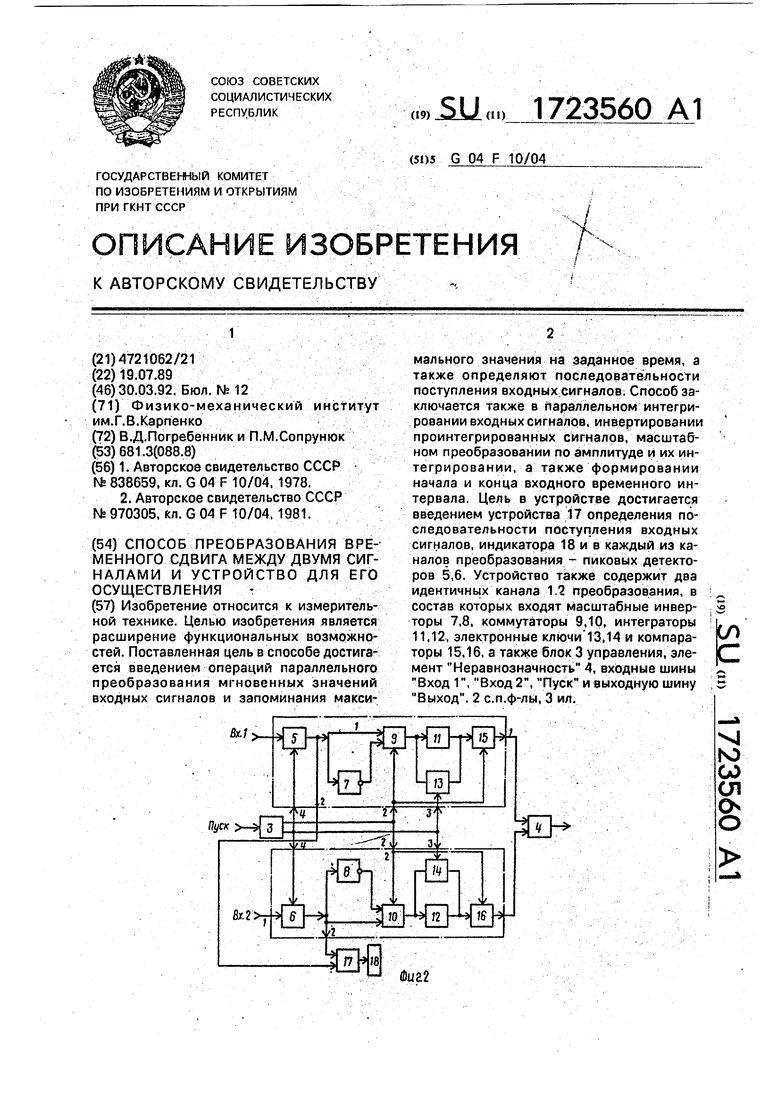

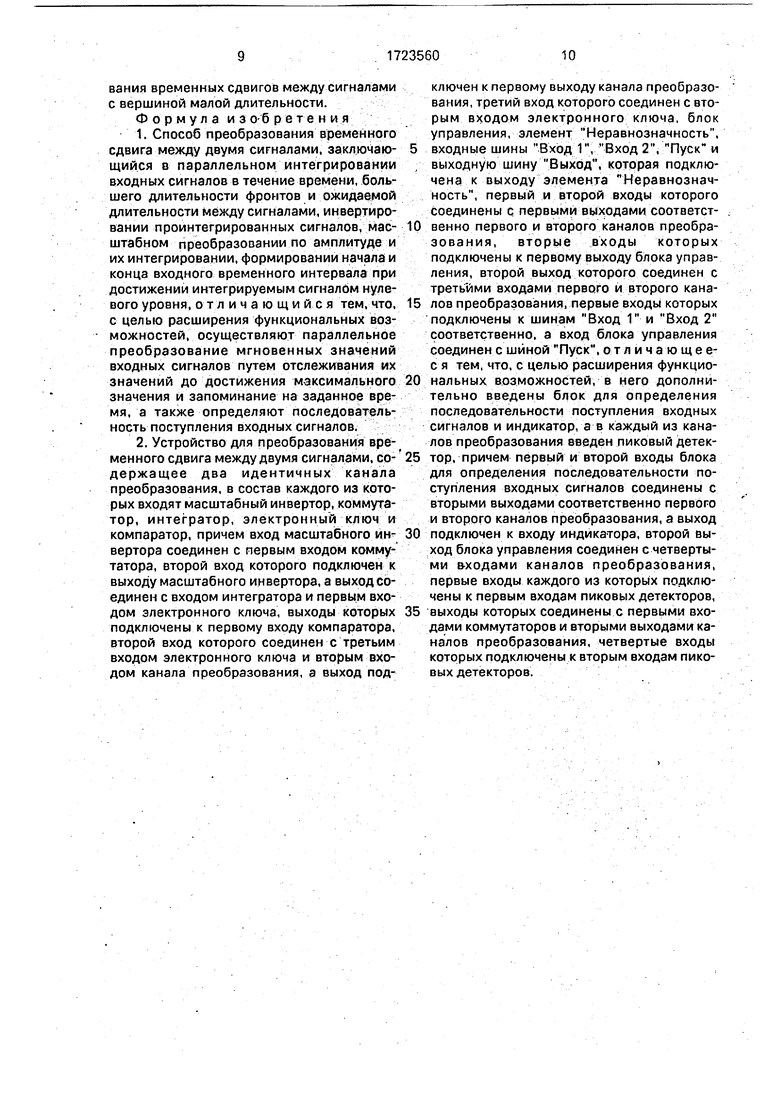

На фиг.1 приведены временные диаграммы, поясняющие сущность способа; на фиг.2 - блок-схема устройства для осуществления способа; на фиг.З - схема устройства

для определения последовательности поступления входных сигналов.

Сущность предлагаемого способа заключается в следующем.

Входные сигналы lh(t) и U2(t- TX) (фиг.1б,в), имеющие, например, треугольную форму, параллельно преобразовываются в сигналы трапецеидальной формы Oni(t) и Un2(t- гх). Это осуществляется путем отслеживания входных сигналов до достижения максимального значения и запоминания этого значения на заданное время (фиг.1г,д). Параллельно преобразованные сигналы интегрируются в течение време- ния, большего длительности их фронтов и ожидаемой длительности между сигналами (фиг.Чз.и)

Uni(t)Ki/Uni(t)dt,(1)

. ти . .; - . . v ; ;; иИ2 (t) К2 / Una (t- rx) dt,(2)

.° . ::

где UMi(t), Un2(t) - напряжения, полученные соответственно в результате интегрирования первого и второго преобразованных сигналов;

Ki Кг .. К - коэффициент передачи интеграторов;

Ти - время интегрирования;

гх - измеряемый временной сдвиг.

Одновременно определяют последова-- тельность поступления входных сигналов

Ul(t)liU2(t-rx).

Затем инвертируют каждый из преобразованных входных сигналов и масштабируют их в одинаковое Км число раз (фигЛе.ж) UM1

Уин -

иин2 КмUM2

Км

О) (4)

где UHHI, 11ин2 - напряжения, полученные после инвертирования и масштабного преобразования;

UM1, UM2- амплитуды входных сигналов. . -

Напряжения 11ин1 и 1)ин2 интегрируют далее от напряжений, полученных при интегрировании преобразованных входных сигналов до момента достижения проинтегрированных напряжений нулевого уровня (фиг.1з,и). Интервалы времени, в течение которых осуществляется интегрирование инвертированных сигналов 11ин1 и Оин2. со ответственно равны

Ki/ Uni(t)dt

T1 t6 - t4 °|. ij

IU)Hll

2/Ur

T2 tg-t4

K2 / Un2 (t - ГХ) dt :lU,H2l

т.е.

ri- (TM-t2)KM,

Т2 (Ти- .1з)КмИнтервалы времени ri и Г2 соответствуют с масштабирующим коэффициентом

10 Км интегральному времени существования сигналов от их начала до момента времени t4. tl Разность этих интервалов времени л и Г2 соответствует с масштабным коэффициентом Км интегральному временному сдвигу

15 между сигналами

Ги Г1 - Г2 t6-t5. (7)

Начало выходного интервала ги формируется в момент времени ts, а его конец - в момент времени te(фиг. 1 м). При одинаковых

20 формах входных сигналов и равных длительностях их фронтов интегральный временной сдвиг, определенный на нулевом уровне, бу- дет давать одинаковые результаты.

Устройство для преобразования вре25 менного сдвига между двумя сигналами (фиг.2) содержит каналы 1 и 2 преобразования, блок 3 управления и логический элемент Неравнозначность 4. Каналы 1 и.2 преобразования включают пиковые детек30 торы 5 и 6, масштабные инверторы 7 и 8, коммутаторы 9 и 10, интеграторы 11 и 12, электронные ключи 13 и 14, компараторы 15 и 16, устройство 17 определения последовательности поступления входных сигналов и

35 индикатор 18.

Входы пиковых детекторов 5 и 6 являются входами устройства. Пиковый детектор 5 соединен с масштабным инвертором 7, коммутатором 9 и входом устройства 17 опреде40 ления последовательности поступления входных сигналов, а пиковый детектор 6 соединен с масштабным инвертором 8, коммутатором 10 и вторым входом устройства 17. Коммутатор 9 последовательно соединен с

45 интегратором 11; компаратором 15, а коммутатор 10 последовательно соединен с интегратором 12 и компаратором 16. Выходы компараторов 15 и 16 соединены с элемен- . том Неравнозначность 4, а устройство 17

50 - с индикатором 18. Блок 3 управления сое- . динен одним выходом с пиковыми детекторами 5 и 6 и электронными ключами 13 и 14, а другим выходом - с коммутаторами 9 и 10 и компараторами 15 и 16. Электронные клю55 чи 1.3 и 14 подключены к входам и выходам интеграторов 11 и 12.

Устройство для определения последовательности поступления входных сигналов (фиг.З) содержит компараторы 19 и 20, логические инверторы 21 и 22, элементы И 23 и

4, элемент ИЛИ 25 и D-триггер 26. Компаратор 19 соединен с элементом И 23 и логиеским инвертором 22, а компаратор 20 - с элементом И 24 и инвертором 21. Инверторы 21 и 22 соединены с вторыми входами элементов И 23 и 24, входы прследних подключены к элементу ИЛИ 25. Элемент И 24 соединен с входом D-триггера 26, а вход С- триггера 26 соединен с входом элемента ИЛИ 25. Выход триггера 26 подключен к индикатору 18,

Блок управления в настоящее время целесообразно выполнять на микропроцессорной базе, например на однокристальных микроЭВМ серии К 1816. Остальные узлы устройства достаточно подробно описаны в литературе.

Устройство работает следующим образом. ; - . .. . : ,. ...;

В исходном состоянии блок 3 управления удерживает открытыми электронные ключи 13 и 14, вследствие чего интеграторы 11 и 12 разряжены до нулевого уровня, а также препятствует срабатыванию пиковых детекторов 5 и 6 и компараторов 15 и 16 путем подачи сигналов соответственно на управляющие входы и на выходы стробиро- вания. Блок 3 управления осуществляет запуск устройства до момента прихода первого из входных сигналов. Этот момент времени ti показан на фиг.1а. Импульсом запуска блок 3 управления открывает пико- вые детекторы 5 и 6, закрывает электронные ключи 13 и 14 и подключает коммутаторы 9 и 10 к выходам пиковых детекторов 5 и 6. В моменты t2 и ta на входы пиковых детекторов 5 и 6 поступают соответственно входные сигналы Ui(t) и l)2(t- Тх) (фиг.1б,в). Производится отслеживание входных сигналов пиковыми,детекторами 5 и 6 до достижения максимального значения и запоминания этого значения на заданное время (фиг. 1 г,д). Одновременно производится определение последовательности поступления входных сигналов Ui(t) и U2 (t- гх). Сэтой целью выходные сигналы пиковых детекторов 5 и 6 подаются на компараторы 19 и 20. Выходной сигнал компаратора 19 поступает на инвертор 22 и на первый вход логического элемента И 23, а выходной сигнал компаратора 20 - на инвертор 21 и второй вход логического элемента И 24. На другой вход логического элемента И 23 поступает выходной сигнал инвертора 21, а на первый вход логического элемента И 24 - выходной, сигнал инвертора 22. Выходные сигналы логических элементов И 23 и 24 поступают на входы логического элемента ИЛИ 25, а выходной сигнал логического элемента И 24, кроме того, поступает на D-вход D-триггера 26, на счетный вход которого приходит выходной сигнал логического элемента ИЛИ 25. Если по первому каналу

входной сигнал приходит первым, то на выходе элемента И 23 появится логическая 1, на выходе элемента И 24 -логический О и на выходе D-триггера - логический О. Если по второму каналу входной сигнал приходит

первым, то на выходе элемента И 23 появится логический О, на выходе элемента И 24 - логическая Г и на выходе D-триггера - логическая Г.

Одновременно производится параллельное интегрирование преобразованных сигналов интеграторами 11 и 12 с момента времени ti до момента времени t4, обозначенного как Ти (фиг,1з,и). Время интегрирования Ти больше суммы длительности

фронта входного сигнала и ожидаемой длительности между сигналами. В момент времени ti блок 3 подключает коммутаторы 9 и 10 к выходам масштабных инверторов 7 и 8 (фиг.1е,ж) и разрешает срабатывание компараторов 15 и 16. Инвертированные масштабно преобразованные сигналы интегрируются от уровня, полученного при интегрировании неинвертированных преобразованных сигналов, до достижения момента равенства выходных напряжений интеграторов 11 и 12 нулевому уровню (фиг.1з,и). В моменты времени ts и te на выходах компараторов 15. и 16 появляются рабочие перепады напряжения (фиг.1к,л).

Масштабный коэффициент Км выбирается таким образом, чтобы моменты ts и te окончания интегрирования наступили до окончания плоской вершины преобразованного сигнала. Выходные сигналы компараторов

15 и 16 поступают на входы логического элемента Неравнозначность 4, на выходе которого получают выходной временной интервал ти (фиг. 1м),соответствующйй сдвигу между сигналами.

Предлагаемый способ и устройство ха- растеризуются высокой помехоустойчивостью вследствие использования для формирования временного интервала не

одной точки, а целого участка входного сигнала, высоким быстродействием за счет обеспечения возможности работы с одиночными сигналами, кроме того, преобразуемый временной сдвиг не зависит от

амплитуды сигналов.

Положительный эффект изобретения в отличие от известного заключается в расширении функциональных возможностей за счет обеспечения возможностей преобразования временных сдвигов между сигналами с вершиной малой длительности. Формула изо-бретения

1.Способ преобразования временного сдвига между двумя сигналами, заключающийся в параллельном интегрировании входных сигналов в течение времени, большего длительности фронтов и ожидаемой длительности между сигналами, инвертировании проинтегрированных сигналов, масштабном преобразовании по амплитуде и их интегрировании, формировании начала и конца входного временного интервала при достижении интегрируемым сигналим нулевого уровня, о т л и ч а ю щ и и с я тем, что, с целью расширения функциональных возможностей, осуществляют параллельное преобразование мгновенных значений входных сигналов путем отслеживания их значений до достижения максимального значения и запоминание на заданное время, а также определяют последовательность поступления входных сигналов.

2.Устройство для преобразования временного сдвига между двумя сигналами, содержащее два идентичных канала преобразования, в состав каждого из которых входят масштабный инвертор, коммутатор, интегратор, электронный ключ и компаратор, причем вход масштабного ин вертора соединен с первым входом коммутатора, второй вход которого подключен к выходу масштабного инвертора, а выход соединен с входом интегратора и первым входом электронного ключа, выходы которых подключены к первому входу компаратора, второй вход которого соединен с третьим входом электронного ключа и вторым входом канала преобразования, а выход подключен к первому выходу канала преобразования, третий вход которого соединен с вторым входом электронного ключа, блок управления, элемент Неравнозначность.

входные шины Вход Г, Вход 2, Пуск и выходную шину Выход, которая подключена к выходу элемента Неравнозначность, первый и второй входы которого соединены с первыми выходами соответственно первого и второго каналов преобразования, вторые входы которых подключены к первому выходу блока управления, второй выход которого соединен с третьими входами первого и второго каналов преобразования, первые входы которых подключены к шинам Вход 1 и Вход 2 соответственно, а вход блока управления соединен с шиной Пуск, о т л и ч а ю щ е е- ся тем, что, с целью расширения функциональных возможностей, в него дополнительно введены блок для определения последовательности поступления входных сигналов и индикатор, а в каждый из каналов преобразования введен пиковый детектор, причем первый и второй входы блока для определения последовательности поступления входных сигналов соединены с вторыми выходами соответственно первого и второго каналов преобразования, а выход

подключен к входу индикатора, второй выход блока управления соединен с четвертыми в-ходами каналов преобразования, первые входы каждого из которых подключены к первым входам пиковых детекторов,

выходы которых соединены с первыми входами коммутаторов и вторыми выходами каналов преобразования, четвертые входы которых подключены к вторым входам пиковых детекторов.

Редактор Т.Лошкарева

Фиг.З

Составитель В.Погребенник

Техред М.МоргеиталКорректор М.Шароши

| название | год | авторы | номер документа |

|---|---|---|---|

| Способ преобразования временного сдвига между двумя сигналами и устройство для его осуществления | 1981 |

|

SU970305A1 |

| Аналого-цифровой интегратор | 1981 |

|

SU1013978A1 |

| Устройство для измерения вихревого компонента скорости потока | 1984 |

|

SU1265619A1 |

| Устройство для измерения вихревого компонента скорости потока | 1982 |

|

SU1016746A1 |

| Устройство для учета движущихся объектов | 1985 |

|

SU1305740A1 |

| Преобразователь активной мощности в цифровой код | 1985 |

|

SU1275308A1 |

| Двухтактный измеритель энергии одиночных импульсов | 1990 |

|

SU1721520A1 |

| ЦИФРОАНАЛОГОВЫЙ ФАЗОВРАЩАТЕЛЬ | 1992 |

|

RU2023273C1 |

| Способ измерения среднего значения напряжения произвольной формы и устройство для его осуществления | 1983 |

|

SU1150561A1 |

| Генератор сигналов для формирования управляющих токов доменной памяти | 1989 |

|

SU1725255A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для измерения интервалаВРЕМЕНи МЕжду дВуМя СигНАлАМи | 1978 |

|

SU838659A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Способ преобразования временного сдвига между двумя сигналами и устройство для его осуществления | 1981 |

|

SU970305A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-03-30—Публикация

1989-07-19—Подача