Устройство относится к вычислительной технике и может быть использовано при автоматизации выбора очередной программы, задания из инфор- мационно-связанного набора программ, заданий для решения в управляющей многопроцессорной вычислительной системе .

Цель изобретения - повышение быстродействия устройства.

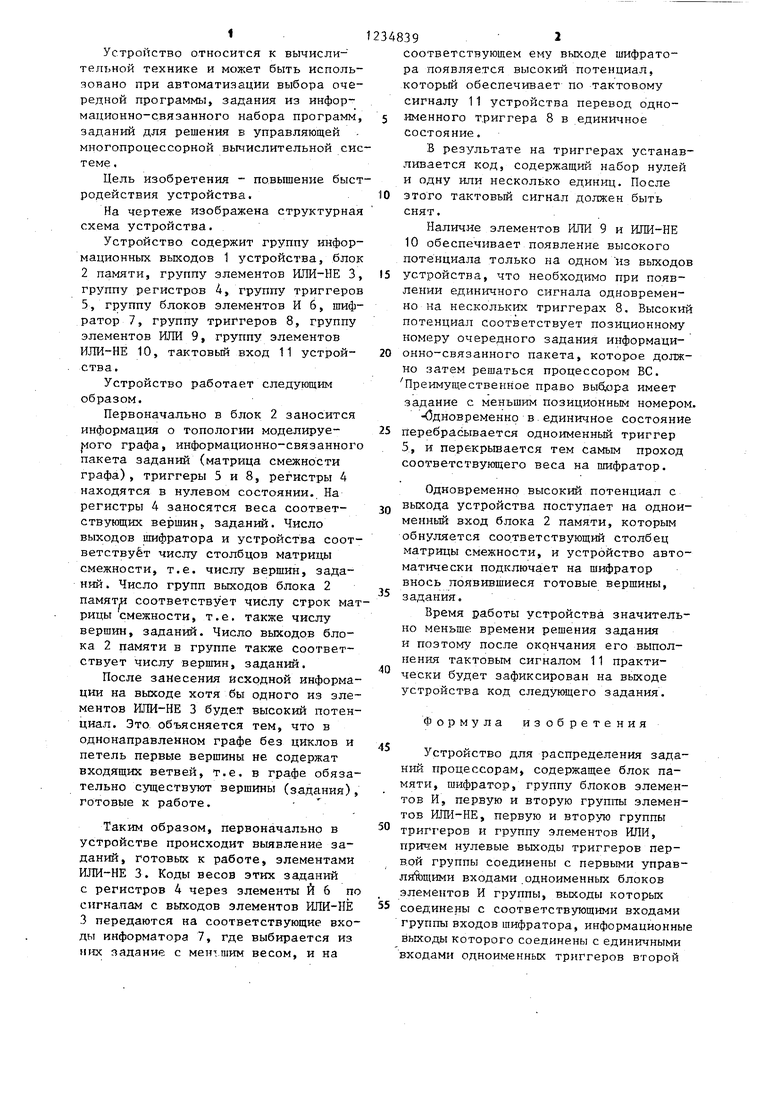

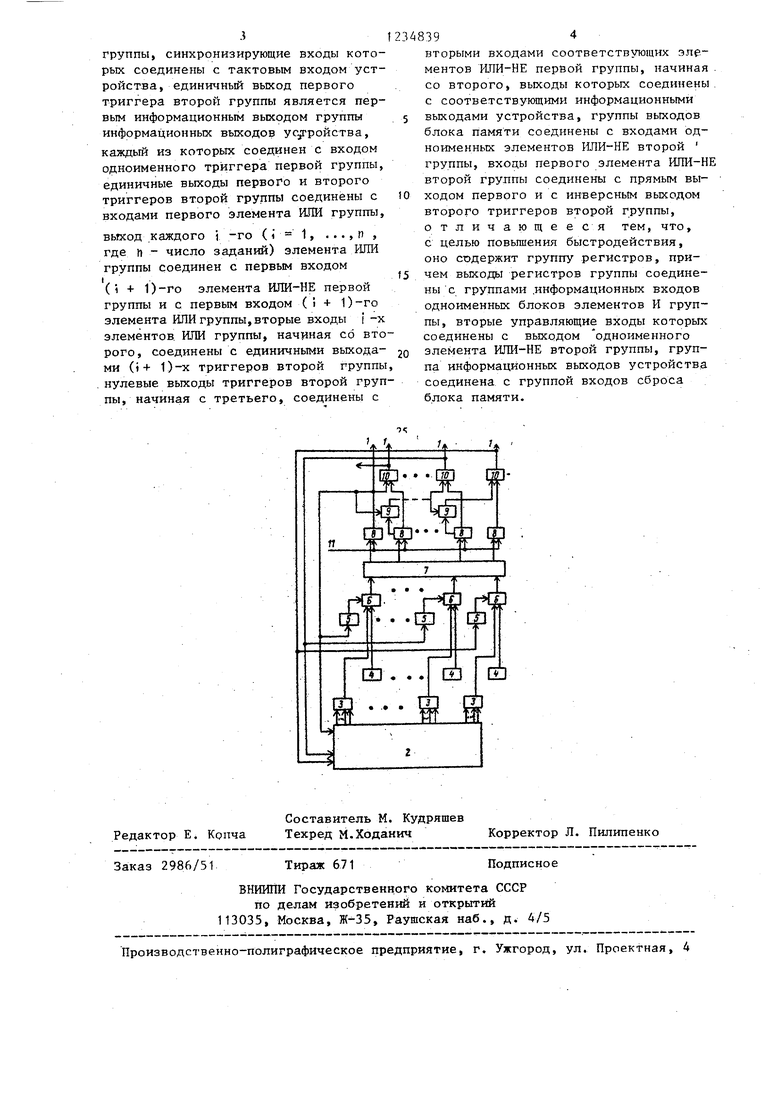

На чертеже изображена структурная схема устройства.

Устройство содержит группу информационных выходов 1 устройства, блок 2 памяти, группу элементов ИЛИ-НЕ 3, группу регистров 4, группу триггеров 5, группу блоков элементов И 6, шифратор 7, группу триггеров 8, группу элементов ИЛИ 9, группу элементов ИЛИ-НЕ 10, тактовый вход 11 устройства.

Устройство работает следующим образом.

Первоначально в блок 2 заносится информация о топологии моделируе- jyioro графа, информационно-связанного пакета заданий (матрица смежности графа), триггеры 5 и 8, регистры 4 находятся в нулевом состоянии. На регистры 4 заносятся веса соответствующих вершин заданий. Число выходов шифратора и устройства соответствует числу столбцов матрицы смежности, т.е. числу вершин, заданий . Число групп выходов блока 2 памяти соответствует числу строк матрицы смежности, т.е. также числу вершин, заданий. Число вьссодов блока 2 памяти в группе также соответствует числу вершин, заданий.

После занесения исходной информации на выходе хотя бы одного из элементов Ш1И-НЕ 3 будет высокий потенциал. Это объясняется тем, что в однонаправленном графе без циклов и петель первые вершины не содержат входящих ветвей, т.е. в графе обязательно существуют вершины (задания), готовые к работе.

Таким образом, первоначально в устройстве происходит выявление заданий, готовых к работе, элементами ИЛИ-НЕ 3. Коды весов этих заданий с регистров 4 через элементы И 6 по сигналам с выходов элементов ИЛИ-НЕ 3 передаются на соответствующие входы информатора 7, где выбирается из мих падание с мен -.шим; весом, и на

соответствующем ему выходе шифратора появляется высокий потенциал, который обеспечивает по тактовому сигналу 11 устройства перевод одноименного триггера 8 в единичное состояние,

В результате на триггерах устанавливается код, содержащий набор нулей и одну или несколько единиц. После

этого тактовьш сигнал должен быть снят.

Наличие элементов ИЛИ 9 и ИЛИ-НЕ 10 обеспечивает появление высокого потенциала только на одном из выходов

устройства, что необходимо при появлении единичного сигнала одновременно на нескольких триггерах 8. Высокий потенциал соответствует позиционному номеру очередного задания информационно-связанного пакета, которое должно затем решаться процессором ВС. Преимущественное право имеет задание с меньшим позиционнЕзГм номером.. -Одновременно в.единичное состояние

перебрасывается одноименный триггер 5, и перекрьшается тем самым проход соответствующего веса на шифратор.

Одновременно высокий потенциал с выхода устройства поступает на одноименный вход блока 2 памяти, которым обнуляется соответствующий столбец матрицы смежности, и устройство автоматически подключает на шифратор внось появившиеся готовые вершины, задания.

Время работы устройства значительно меньше времени решения задания и поэтому после окончания его выполнения тактовым сигналом 11 практи

чески будет зафиксирован на выходе устройства код следукчцего задания.

Формула изобретения

Устройство для распределения заданий процессорам, содержащее блок памяти, шифратор, группу блоков элементов И, первую и вторую группы элементов ИЛИ-НЕ, первую и вторую группы триггеров и группу элементов ИЛИ, причем нулевые выходы триггеров первой группы соединены с первыми управлявшими входами .одноименных блоков элементов И группы, вькоды которых

соединены с соответствующими входами группы входов шифратора, информационные выходы которого соединены с единичными входами одноименных триггеров второй

-

группы, синхронизирующие входы которых соединены с тактовым входом устройства, единичный выход первого триггера второй группы является первым информационным выходом группы информационных выходов ус- ройства, каждый из которых соединен с входом одноименного триггера первой группы, единичные выходы первого и второго триггеров второй группы соединены с входами первого элемента ИЛИ группы,

выход каждого i -го (i 1, . .., п , где п - число заданий) элемента ИЛИ группы соединен с первым входом

(i + 1)-го элемента Ш1И-НЕ первой группы и с первым входом (i + 1)-го элемента ИЛИ грзшпы, вторые входы i -х элементов. ИЛИ группы, начиная со второго, соединены с единичными выходами (+ 1)-х триггеров второй группы нулевые выходы триггеров второй группы, начиная с третьего, соединены с

8394

вторыми входами соответствующих элр- ментов ИЛИ-НЕ первой группы, начиная . со второго, выходы которых соеди 1ены с соответствующими информационными выходами устройства, группы выходов блока памяти соединены с входами одноименных элементов ИЛИ-НЕ второй группы, входы первого элемента ИЛИ-НЕ второй группы соединены с прямым вы-

ходом первого и с инверсным выходом второго триггеров второй группы, отличающееся тем, что, с целью повьшения быстродействия, оно содержит группу регистров, причем выходы регистров группы соединены с группами .информационных входов одноименных блаков элементов И группы, вторые управляющие входы которых соединены с выходом одноименного

элемента ИЛИ-НЕ второй группы, группа информационных выходов устройства соединена с группой входов сброса блока памяти.

Ф

ТГ- Д, гЧр

/R- I i

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заданий процессорам | 1981 |

|

SU1001101A1 |

| Устройство для анализа параметров графа | 1988 |

|

SU1681312A1 |

| Устройство для решения комбинаторнологических задач на графах | 1990 |

|

SU1709349A1 |

| Устройство для моделирования сетевых графов | 1983 |

|

SU1151979A1 |

| Устройство для определения максимальных путей в графах | 1986 |

|

SU1383386A1 |

| Устройство для распределения заданий процессорам | 1980 |

|

SU940164A1 |

| Устройство для моделирования графов | 1984 |

|

SU1218392A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

| Устройство для определения максимальных путей в графах | 1984 |

|

SU1280380A2 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1441399A1 |

Устройство для распределения заданий процессорам откосится к области вычислительной техники и может быть использовано при организации вычислительного процесса по обработке пакета информационно-связанных заданий в многопроцессорной (многомашинной) вьтислительной системе. Цель изобретения - повышение быстродействия. Указанная цель достигается тем, что устройство содержит блок памяти (матрицу триггеров), шифратор, две группы элементов ИЛИ-НЕ, две группы триггеров, группу элементов И и группу элементов ИЛИ с соответствующими связями. Новым в .устройстве является то, что в него введена группа регистров. Устройство может функционировать в режиме, при котором обеспечивается реализация пакета информационно-связанных задач с минимальным средним временем ответа для заданий данного пакета. 1 ил. f СП

Редактор E. Копча

Составитель М. Кудряшев

Техред М.Ходанич Корректор Л. Пилипенко

Заказ 2986/51

Тираж 671

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Подписное

| Устройство для выбора задач в целевой системе обработки данных | 1976 |

|

SU664175A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1981 |

|

SU1001101A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-12-06—Подача