Изобретение относится к вычислительной технике, радиотехнике и технической физике и может быть использовано для отображения телевизионной и других видов информации.

Цель изобретения - повышение быстродействия устройства.

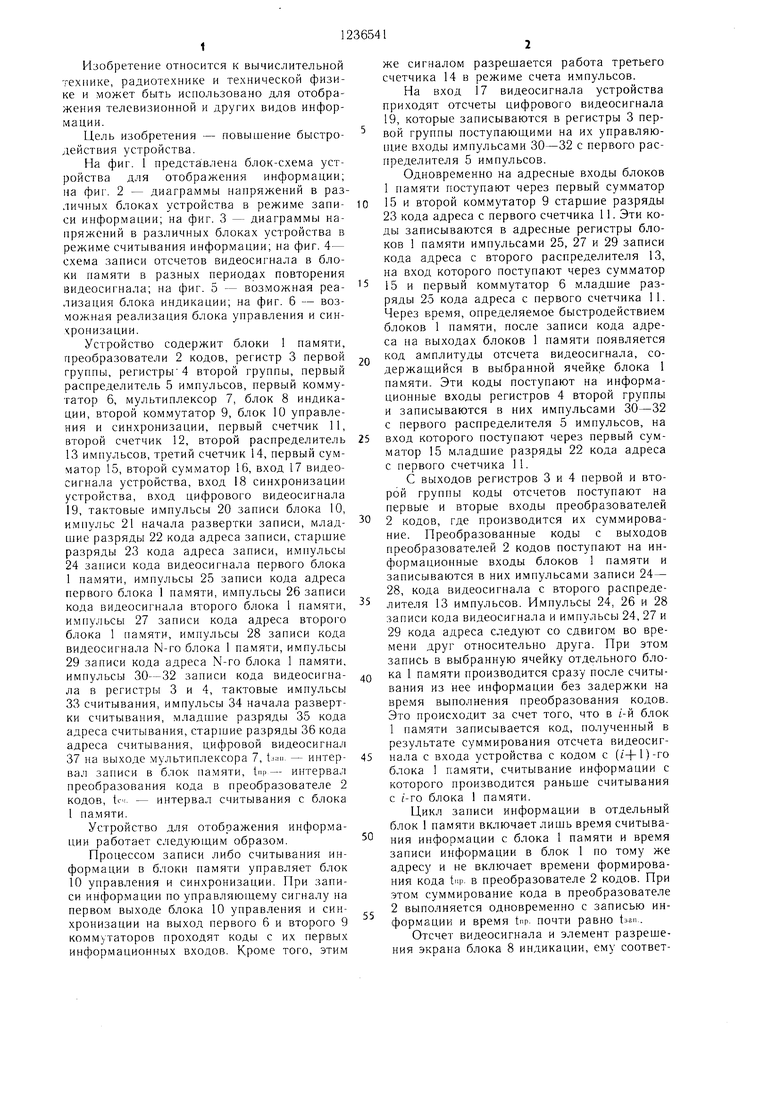

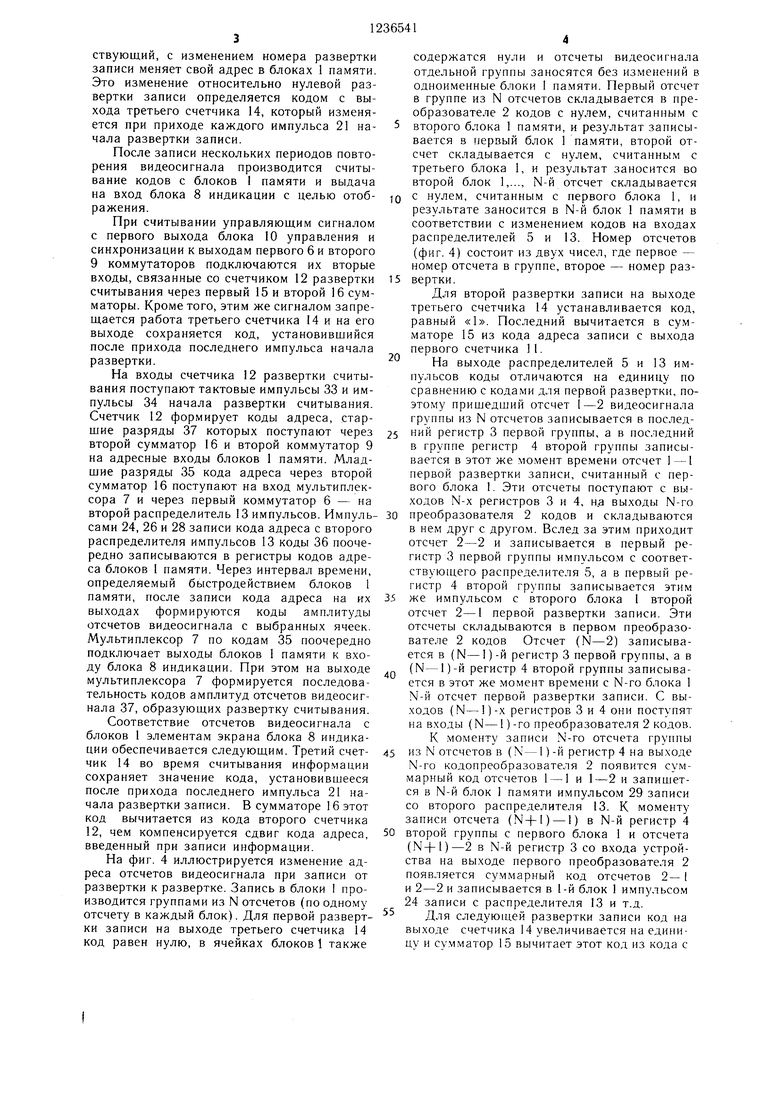

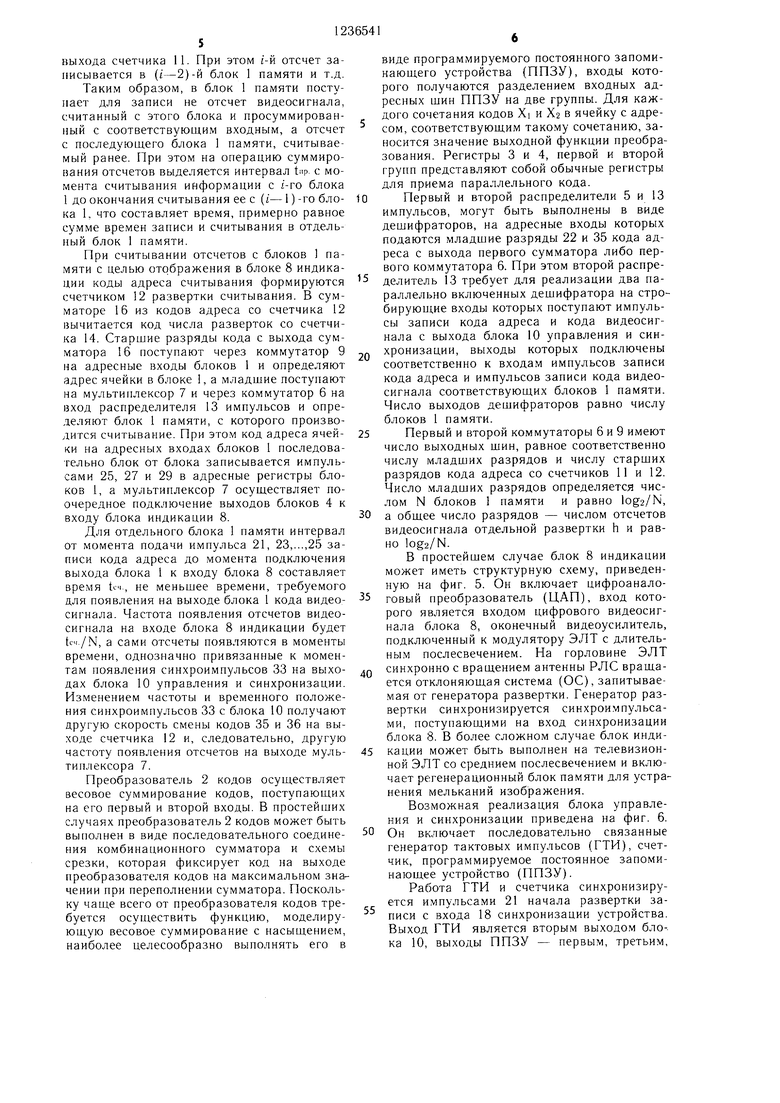

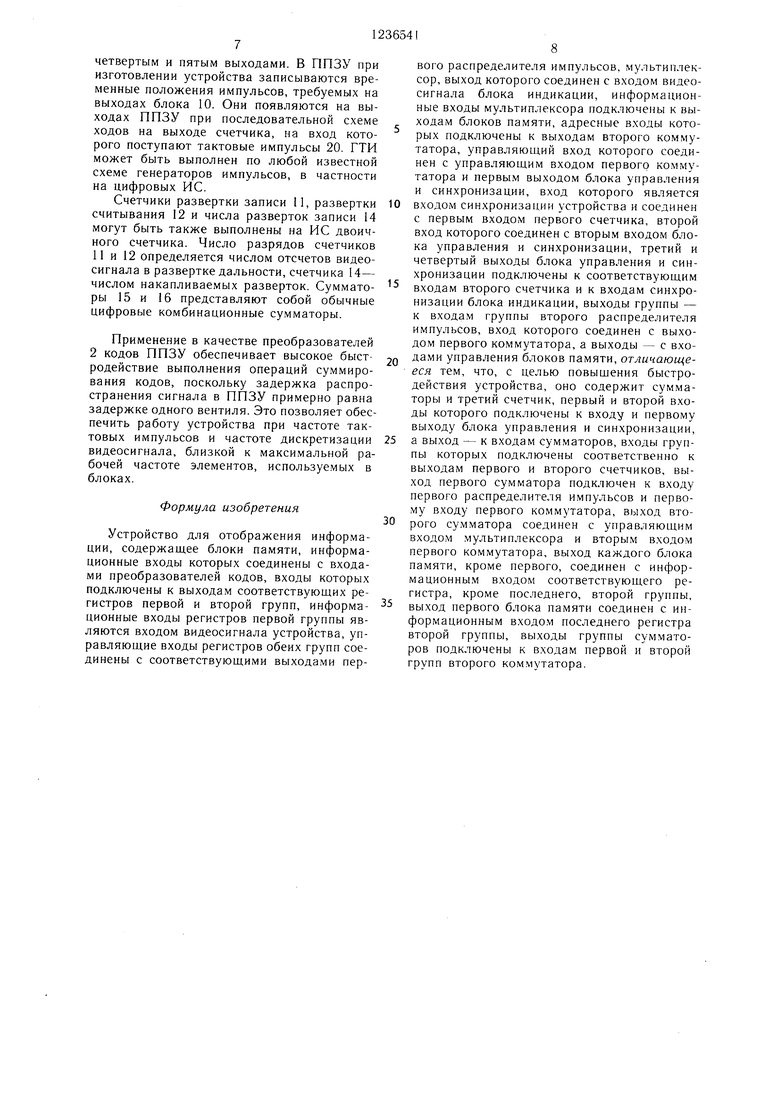

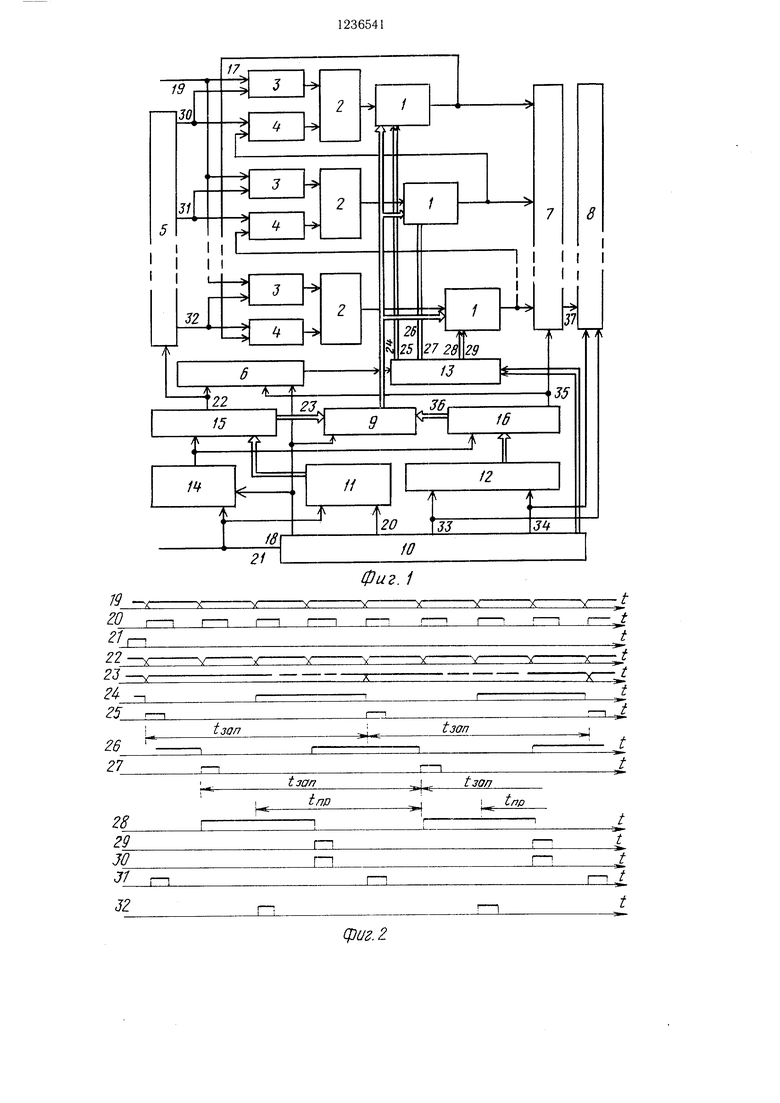

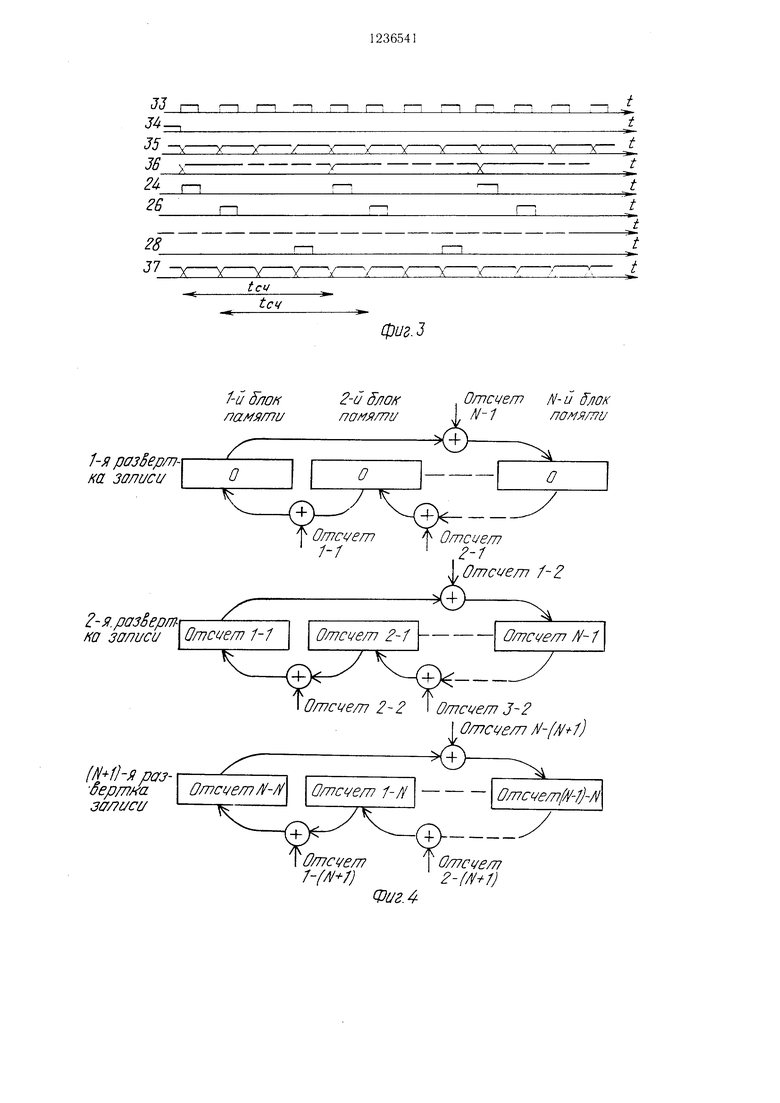

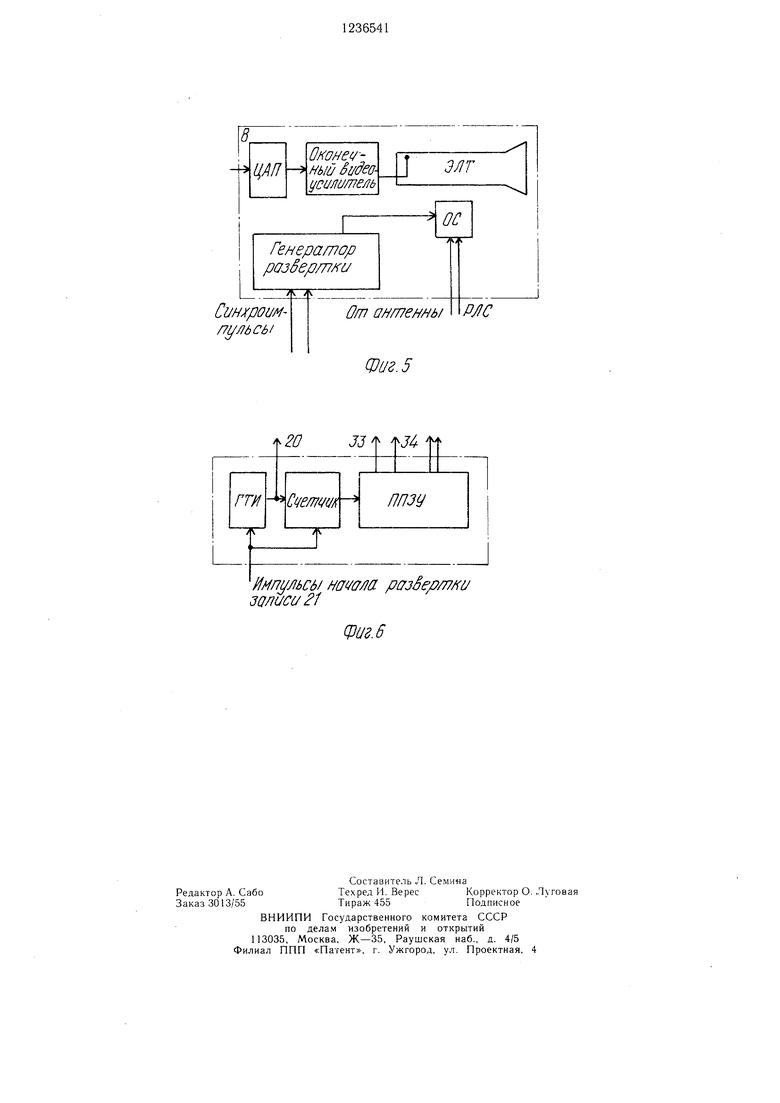

На фиг. 1 представлена блок-схема устройства для отображения информации; на фиг. 2 - диаграммы напряжений в различных блоках устройства в режиме записи информации; на фиг. 3 - диаграммы напряжений в различных блоках устройства в режиме считывания информации; на фиг. 4- схема записи отсчетов видеосигнала в блоки памяти в разных периодах повторения видеосигнала; на фиг. 5 - возможная реализация блока индикации; на фиг. 6 - возможная реализация блока управления и синхронизации.

Устройство содержит блоки 1 памяти, преобразователи 2 кодов, регистр 3 первой группы, регистры 4 второй группы, первый распределитель 5 импульсов, первый коммутатор 6, мультиплексор 7, блок 8 индикации, второй коммутатор 9, блок 10 управления и синхронизации, первый счетчик 11, второй счетчик 12, второй распределитель 13 импульсов, третий счетчик 14, первый сумматор 15, второй сумматор 16, вход 17 видеосигнала устройства, вход 18 синхронизации устройства, вход цифрового видеосигнала 19, тактовые импульсы 20 записи блока 10, импульс 21 начала развертки записи, младшие разряды 22 кода адреса записи, старшие разряды 23 кода адреса записи, импульсы 24 записи кода видеосигнала первого блока 1 памяти, импульсы 25 записи кода адреса первого блока 1 памяти, импульсы 26 записи кода видеосигнала второго блока 1 памяти, импульсы 27 записи кода адреса второго блока 1 памяти, импульсы 28 записи кода видеосигнала N-ro блока 1 памяти, импульсы 29 записи кода адреса N-ro блока 1 памяти, импульсы 30-32 записи кода видеосигнала в регистры 3 и 4, тактовые импульсы 33 считывания, импульсы 34 начала развертки считывания, младшие разряды 35 кода адреса считывания, старшие разряды 36 кода адреса считывания, цифровой видеосигнал 37 на выходе мультиплексора 7, tjan, - интервал записи в блок памяти, tnp- интервал преобразования кода в преобразователе 2 кодов, tc4. - интервал считывания с блока 1 памяти.

Устройство для отображения информации работает следующим образом.

Процессом записи либо считывания информации в б. 1оки памяти управляет блок 10 управления и синхронизации. При записи информации по управляюшему сигналу на первом выходе блока 10 управления и синхронизации на выход первого 6 и второго 9 коммутаторов проходят коды с их первых информационных входов. Кроме того, этим

0

5

0

5

0

5

5

0

5

же сигналом разрешается работа третьего счетчика 14 в режиме счета импульсов.

На вход 17 видеосигнала устройства приходят отсчеты цифрового видеосигнала 19, которые записываются в регистры 3 первой группы поступающими на их управляющие входы импульсами 30-32 с первого распределителя 5 импульсов.

Одновременно на адресные входы блоков

1памяти поступают через первый сумматор 15 и второй коммутатор 9 старшие разряды 23 кода адреса с первого счетчика 11. Эти коды записываются в адресные регистры блоков 1 памяти импульсами 25, 27 и 29 записи кода адреса с второго распределителя 13, на вход которого поступают через сумматор 15 и первый коммутатор 6 младшие разряды 25 кода адреса с первого счетчика 11. Через время, определяемое быстродействием блоков 1 памяти, после записи кода адреса на выходах блоков 1 памяти появляется код амплитуды отсчета видеосигнала, содержащийся в выбранной ячейкр блока 1 памяти. Эти коды поступают на информационные входы регистров 4 второй группы и записываются в них импульсами 30-32 с первого распределителя 5 импульсов, на вход которого поступают через первый сумматор 15 младщие разряды 22 кода адреса с первого счетчика 11.

С выходов регистров 3 и 4 первой и второй группы коды отсчетов поступают на первые и вторые входы преобразователей

2кодов, где производится их суммирование. Преобразованные коды с выходов преобразователей 2 кодов поступают на информационные входы блоков 1 памяти и записываются в них импульсами записи 24- 28, кода Ешдеосигнала с второго распределителя 13 импульсов. Импульсы 24, 26 и 28 записи кода видеосигнала и импульсы 24, 27 и 29 кода адреса следуют со сдвигом во времени друг относительно друга. При этом запись в выбранную ячейку отдельного блока 1 памяти производится сразу после считывания из нее информации без задержки на время выполнения преобразования кодов. Это происходит за счет того, что в i-й блок

1памяти записывается код, полученный в результате суммирования отсчета видеосигнала с входа устройства с кодом с (г-|-1)-го блока 1 памяти, считывание информации с которого производится раньше считывания с г -го блока 1 памяти.

Цикл записи информации в отдельный блок 1 памяти включает лищь время считывания информации с блока 1 памяти и время записи информации в блок 1 по тому же адресу и не включает времени формирования кода tnp. в преобразователе 2 кодов. При этом суммирование кода в преобразователе

2выполняется одновременно с записью информации и время tnp. почти равно tsan,.

Отсчет видеосигнала и элемент разрешения экрана блока 8 индикации, ему соответствующии, с изменением номера развертки записи меняет свой адрес в блоках 1 памяти. Это изменение относительно нулевой развертки записи определяется кодом с выхода третьего счетчика 14, который изменяется при приходе каждого импульса 21 начала развертки записи.

После записи нескольких периодов повторения видеосигнала производится считывание кодов с блоков памяти и выдача на вход блока 8 индикации с целью отображения.

При считывании управляющим сигналом с первого выхода блока 10 управления и синхронизации к выходам первого 6 и второго 9 коммутаторов подключаются их вторые входы, связанные со счетчиком 12 развертки считывания через первый 15 и второй 16 сумматоры. Кроме того, этим же сигналом запрещается работа третьего счетчика 14 и на его выходе сохраняется код, установившийся после прихода последнего импульса начала развертки.

На входы счетчика 12 развертки считывания поступают тактовые импульсы 33 и импульсы 34 начала развертки считывания. Счетчик 12 формирует коды адреса, стар10

содержатся нули и отсчеты видеосигнала отдельной группы заносятся без изменений в одноименные блоки 1 па.мяти. Первый отсчет в группе из N отсчетов складывается в преобразователе 2 кодов с нулем, считанным с второго блока 1 памяти, и результат записывается в первый блок 1 памяти, второй отсчет складывается с нулем, считанным с третьего блока 1, и результат заносится во второй блок 1,..., N-й отсчет складывается с нулем, считанным с первого блока 1, и результате заносится в N-й блок 1 памяти в соответствии с изменением кодов на входах распределителей 5 и 13. Номер отсчетов (фиг. 4) состоит из двух чисел, где первое - номер отсчета в группе, второе - номер раз- 15 вертки.

Для второй развертки записи на выходе третьего счетчиКа 14 устанавливается код, равный «1. Последний вычитается в сумматоре 15 из кода адреса записи с выхода первого счетчика 1 1.

На выходе распределителей 5 и 13 импульсов коды отличаются на единицу по сравнению с кодами для первой развертки, поэтому пришедший отсчет 1-2 видеосигнала группы из N отсчетов записывается в послед20

шие разряды 37 которых поступают через 25 ний регистр 3 первой группы, а в последний

второй сумматор 16 и второй коммутатор 9 на адресные входы блоков 1 памяти. Младшие разряды 35 кода адреса через второй сумматор 16 поступают на вход мультиплексора 7 и через первый коммутатор 6 - на

в группе регистр 4 второй группы записывается в этот же момент времени отсчет I - 1 первой развертки записи, считанный с первого блока 1. Эти отсчеты поступают с выходов N-X регистров 3 и 4, н.а выходы N-ro

второй распределитель 13 импульсов. Импуль- 30 преобразователя 2 кодов и складываются

35

40

сами 24, 26 и 28 записи кода адреса с второго распределителя импульсов 13 коды 36 поочередно записываются в регистры кодов адреса блоков 1 памяти. Через интервал времени, определяемый быстродействием блоков 1 памяти, после записи кода адреса на их выходах формируются коды амплитуды отсчетов видеосигнала с выбранных ячеек. Мультиплексор 7 по кодам 35 поочередно подключает выходы блоков I памяти к входу блока 8 индикации. При этом на выходе мультиплексора 7 формируется последовательность кодов амплитуд отсчетов видеосигнала 37, образующих развертку считывания.

Соответствие отсчетов видеосигнала с блоков 1 элементам экрана блока 8 индикации обеспечивается следующим. Третий счетчик 14 во время считывания инфор.мации сохраняет значение кода, установившееся после прихода последнего импульса 21 начала развертки записи. В сумматоре 16 этот код вычитается из кода второго счетчика 12, чем компенсируется сдвиг кода адреса, введенный при записи информации.

На фиг. 4 иллюстрируется изменение адреса отсчетов видеосигнала при записи от развертки к развертке. Запись в блоки 1 производится группами из N отсчетов (по одному отсчету в каждый блок). Для первой разверт- ки записи на выходе третьего счетчика 14 код равен нулю, в ячейках блоков 1 также

в нем друг с другом. Вслед за этим приходит отсчет 2-2 и записывается в первый регистр 3 первой группы импульсом с соответ- ствуюш,его распределителя 5, а в первый регистр 4 второй группы записывается этим же импульсом с второго блока 1 второй отсчет 2-I первой развертки записи. Эти отсчеты складываются в первом преобразователе 2 кодов Отсчет (N-2) записывается в (N-1)-й регистр 3 первой группы, а в (N-1)-й регистр 4 второй группы записывается в этот же момент времени с N-ro блока 1 N-й отсчет первой развертки записи. С выходов (N-1)-х регистров 3 и 4 они поступят на входы (N-1)-го преобразователя 2 кодов. К моменту записи N-ro отсчета группы 45 из N отсчетов в (N-1)-й регистр 4 на выходе N-ro кодопреобразователя 2 появится суммарный код отсчетов 1 - 1 и 1-2 и запишется в N-й блок 1 памяти импульсом 29 записи со второго распределителя 13. К моменту записи отсчета (N-|-l) - 1) в N-й регистр 4 второй группы с первого блока 1 и отсчета (N+1)-2 в N-й регистр 3 со входа устройства на выходе первого преобразователя 2 появляется суммарный код отсчетов 2- 1 и 2-2 и записывается в 1-й блок 1 импульсом 24 записи с распределителя 13 и т.д.

Для следующей развертки записи код на выходе счетчика 14 увеличивается на единицу и сумматор 15 вычитает этот код из кода с

50

10

36541

4

содержатся нули и отсчеты видеосигнала отдельной группы заносятся без изменений в одноименные блоки 1 па.мяти. Первый отсчет в группе из N отсчетов складывается в преобразователе 2 кодов с нулем, считанным с второго блока 1 памяти, и результат записывается в первый блок 1 памяти, второй отсчет складывается с нулем, считанным с третьего блока 1, и результат заносится во второй блок 1,..., N-й отсчет складывается с нулем, считанным с первого блока 1, и результате заносится в N-й блок 1 памяти в соответствии с изменением кодов на входах распределителей 5 и 13. Номер отсчетов (фиг. 4) состоит из двух чисел, где первое - номер отсчета в группе, второе - номер раз- 15 вертки.

Для второй развертки записи на выходе третьего счетчиКа 14 устанавливается код, равный «1. Последний вычитается в сумматоре 15 из кода адреса записи с выхода первого счетчика 1 1.

На выходе распределителей 5 и 13 импульсов коды отличаются на единицу по сравнению с кодами для первой развертки, поэтому пришедший отсчет 1-2 видеосигнала группы из N отсчетов записывается в послед20

в группе регистр 4 второй группы записывается в этот же момент времени отсчет I - 1 первой развертки записи, считанный с первого блока 1. Эти отсчеты поступают с выходов N-X регистров 3 и 4, н.а выходы N-ro

0 преобразователя 2 кодов и складываются

5

0

в нем друг с другом. Вслед за этим приходит отсчет 2-2 и записывается в первый регистр 3 первой группы импульсом с соответ- ствуюш,его распределителя 5, а в первый регистр 4 второй группы записывается этим же импульсом с второго блока 1 второй отсчет 2-I первой развертки записи. Эти отсчеты складываются в первом преобразователе 2 кодов Отсчет (N-2) записывается в (N-1)-й регистр 3 первой группы, а в (N-1)-й регистр 4 второй группы записывается в этот же момент времени с N-ro блока 1 N-й отсчет первой развертки записи. С выходов (N-1)-х регистров 3 и 4 они поступят на входы (N-1)-го преобразователя 2 кодов. К моменту записи N-ro отсчета группы 5 из N отсчетов в (N-1)-й регистр 4 на выходе N-ro кодопреобразователя 2 появится суммарный код отсчетов 1 - 1 и 1-2 и запишется в N-й блок 1 памяти импульсом 29 записи со второго распределителя 13. К моменту записи отсчета (N-|-l) - 1) в N-й регистр 4 второй группы с первого блока 1 и отсчета (N+1)-2 в N-й регистр 3 со входа устройства на выходе первого преобразователя 2 появляется суммарный код отсчетов 2- 1 и 2-2 и записывается в 1-й блок 1 импульсом 24 записи с распределителя 13 и т.д.

Для следующей развертки записи код на выходе счетчика 14 увеличивается на единицу и сумматор 15 вычитает этот код из кода с

0

выхода счетчика 11. При этом ьй отсчет записывается в (г-2)-и блок 1 памяти и т.д.

Таким образом, в блок 1 памяти поступает для записи не отсчет видеосигнала, считанный с этого блока и просуммированный с соответствующим входным, а отсчет с последующего блока 1 памяти, считываемый ранее. При этом на операцию суммиро- )ания отсчетов выделяется интервал с момента считывания информации с /-го блока 1 до окончания считывания ее с (/- 1) -го бло- ка 1, что составляет время, примерно равное сумме времен записи и считывания в отдельный блок 1 памяти.

При считывании отсчетов с блоков 1 памяти с целью отображения в блоке 8 индикации коды адреса считывания формируются счетчиком 12 развертки считывания. В сумматоре 16 из кодов адреса со счетчика 12 вычитается код числа разверток со счетчика 14. Старшие разряды кода с выхода сумматора 16 поступают через коммутатор 9 на адресные входы блоков 1 и определяют адрес ячейки в блоке 1, а младшие поступают на мультиплексор 7 и через коммутатор 6 на вход распределителя 13 импульсов и определяют блок 1 памяти, с которого производится считывание. При этом код адреса ячей- ки на адресных входах блоков 1 последовательно блок от блока записывается импульсами 25, 27 и 29 в адресные регистры блоков 1, а мультиплексор 7 осуществляет поочередное подключение выходов блоков 4 к входу блока индикации 8.

Для отдельного блока 1 памяти интервал от момента подачи импульса 21, 23,...,25 записи кода адреса до момента подключения выхода блока 1 к входу блока 8 составляет время tc i., не меньшее времени, требуемого для появления на выходе блока 1 кода видео- сигнала. Частота появления отсчетов видеосигнала на входе блока 8 индикации будет tc-4./N, а сами отсчеты появляются в моменты времени, однозначно привязанные к моментам появления синхроимпульсов 33 на выхо- дах блока 10 управления и синхронизации. Изменением частоты и временного положения синхроимпульсов 33 с блока 10 получают другую скорость смены кодов 35 и 36 на выходе счетчика 12 и, следовательно, другую частоту появления отсчетов на выходе муль- тинлексора 7.

Преобразователь 2 кодов осушествляет весовое суммирование кодов, поступающих на его первый и второй входы. В простейших случаях преобразователь 2 кодов может быть выполнен в виде последовательного соедине- ния комбинационного сумматора и схемы срезки, которая фиксирует код на выходе преобразователя кодов на максимальном значении при переполнении сумматора. Поскольку чаще всего от преобразователя кодов требуется осуществить функцию, моделирующую весовое суммирование с насыщением, наиболее целесообразно выполнять его в

виде программируемого постоянного запоминающего устройства (ПИЗУ), входы которого получаются разделением входных адресных шин ППЗУ на две группы. Для каждого сочетания кодов Xi и Х2 в ячейку с адресом, соответствующим такому сочетанию, заносится значение выходной функции преобразования. Регистры 3 и 4, первой и второй групп представляют собой обычные регистры для приема параллельного кода.

Первый и второй распределители 5 и 13 импульсов, могут быть выполнены в виде дешифраторов, на адресные входы которых подаются младщие разряды 22 и 35 кода адреса с выхода первого сумматора либо первого коммутатора 6. При этом второй распределитель 13 требует для реализации два параллельно включенных дешифратора на стро- бирующие входы которых поступают импульсы записи кода адреса и кода видеосигнала с выхода блока 10 управления и синхронизации, выходы которых подключены соответственно к входам импульсов записи кода адреса и импульсов записи кода видеосигнала соответствующих блоков 1 памяти. Число выходов дешифраторов равно числу блоков 1 памяти.

Первый и Е5торой коммутаторы 6 и 9 имеют число выходных щин, равное соответственно числу младших разрядов и числу старщих разрядов кода адреса со счетчиков 11 и 12. Число младших разрядов определяется числом N блоков 1 памяти и равно log2/N, а общее число разрядов - числом отсчетов видеосигнала отдельной развертки h и равно log2/N.

В простейшем случае блок 8 индикации может иметь структурную схему, приведенную на фиг. 5. Он включает цифроанало- говый преобразователь (ЦАП), вход которого является входом цифрового видеосигнала блока 8, оконечный видеоусилитель, подключенный к модулятору ЭЛТ с длительным послесвечением. На горловине ЭЛТ синхронно с вращением антенны РЛС вращается отклоняющая система (ОС), запитывае- мая от генератора развертки. Генератор развертки синхронизируется синхроимпульсами, поступаюилими на вход синхронизации блока 8. В более сложном случае блок индикации может быть выполнен на телевизионной ЭЛТ со среднием послесвечением и включает регенерационный блок памяти для устранения мельканий изображения.

Возможная реализация блока управления и синхронизации приведена на фиг. 6. Он вк.лючает последовательно связанные генератор тактовых импульсов (ГТИ), счетчик, программируемое постоянное запоминающее устройство (ППЗУ).

Работа ГТИ и счетчика синхронизируется импульсами 21 начала развертки записи с входа 18 синхронизации устройства. Выход ГТИ является вторым выходом блока 10, выходы ППЗУ - первым, третьим.

четвертым и пятым выходами. В ППЗУ при изготовлении устройства записываются временные положения импульсов, требуемых на выходах блока 10. Они появляются на выходах ППЗУ при последовательной схеме ходов на выходе счетчика, на вход которого поступают тактовые импульсы 20. ГТИ может быть выполнен по любой известной схеме генераторов импульсов, в частности на цифровых ИС.

Счетчики развертки записи 11, развертки считывания 12 и числа разверток записи 14 могут быть также выполнены на ИС двоичного счетчика. Число разрядов счетчиков 11 и 12 определяется числом отсчетов видеосигнала в развертке дальности, счетчика 14- числом накапливаемых разверток. Суммато- ры 15 и 16 представляют собой обычные цифровые комбинационные сумматоры.

Применение в качестве преобразователей 2 кодов ППЗУ обеспечивает высокое быстродействие выполнения операций суммирования кодов, поскольку задержка распространения сигнала в ППЗУ примерно равна задержке одного вентиля. Это позволяет обеспечить работу устройства при частоте тактовых импульсов и частоте дискретизации видеосигнала, близкой к максимальной рабочей частоте элементов, используемых в блоках.

Формула изобретения

Устройство для отображения информации, содержащее блоки памяти, информационные входы которых соединены с входами преобразователей кодов, входы которых подключены к выходам соответствующих регистров первой и второй групп, информа- ционные входы регистров первой группы являются входом видеосигнала устройства, управляющие входы регистров обеих групп соединены с соответствующими выходами пер0

0

5

0

вого распределителя импульсов, мультиплексор, выход которого соединен с входом видеосигнала блока индикации, информационные входы мультиплексора подключены к выходам блоков памяти, адресные входы которых подключены к выходам второго коммутатора, управляющий вход которого соединен с управляющим входом первого коммутатора и первым выходом блока управления и синхронизации, вход которого является входом синхронизации устройства и соединен с первым входом первого счетчика, второй вход которого соединен с вторым входом блока управления и синхронизации, третий и четвертый выходы блока управления и синхронизации подключены к соответствующим входам второго счетчика и к входам синхронизации блока индикации, выходы группы - к входам группы второго распределителя импульсов, вход которого соединен с выходом первого коммутатора, а выходы - с входами управления блоков памяти, отличающееся тем, что, с целью повыщения быстродействия устройства, оно содержит сумматоры и третий счетчик, первый и второй входы которого подключены к входу и первому выходу блока управления и синхронизации, а выход - к вход,ам сумматоров, входы группы которых подключены соответственно к выходам первого и второго счетчиков, выход первого сумматора подключен к входу первого распределителя импульсов и первому входу первого коммутатора, выход второго сумматора соединен с управляющим входом мультиплексора и вторым входом первого коммутатора, выход каждого блока памяти, кроме первого, соединен с информационным входом соответствующего регистра, кроме последнего, второй группы, выход первого блока памяти соединен с информационным входом последнего регистра второй группы, выходы группы сумматоров подключены к входам первой и второй групп второго коммутатора.

.

21 r-.

2 25

tsan

26 27

tsan

inD

28 29 JG

L J2

сриг.г

фиг. 1

t

- 4«etjon

tsan

tnp

jn.

/

2 26

-CTL

1-я роз беpm- на золис1/

2-я.розёерш- на записи

фиг.З

Н+И-я pajоерглн а

+к-

2-2

0/77С1 е/77

JS- Ч- )-

OiT7c e/nf//-j)

Omcve/T

OiT7c e/nf//-j)

Фиг. 4

0/77Cf e/77

)

3flT

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал | 1983 |

|

SU1124452A1 |

| Устройство для индикации | 1984 |

|

SU1236540A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Устройство для отображения информации | 1986 |

|

SU1432594A1 |

| Формирователь кодов радиально-круговой развертки для индикатора кругового обзора | 1986 |

|

SU1401422A2 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

| Устройство для формирования векторов на экране телевизионного индикатора | 1988 |

|

SU1506477A1 |

| Способ формирования изображения на матричной газоразрядной индикаторной панели | 1985 |

|

SU1300658A1 |

| Устройство для формирования кодов радиально-круговой развертки | 1987 |

|

SU1413663A1 |

| Способ селективной записи импульсных процессов и устройство для его осуществления | 1988 |

|

SU1636800A1 |

Изобретение относится к вычислительной технике и может быть использовано для отображения телевизионной и других видов информации. Цель изобретения - повышение быстродействия. Устройство содержит блоки памяти, преобразователи кодов, регистры первой и второй групп, распределители импульсов, коммутаторы, мультиплексор, блок индикации, блок управления и синхронизации, три счетчика, сумматоры, 6 ил. ГчЭ со О) ел 4

Фиг. 5

ИИП1/МС6/ HOi/OM pffj6e/}/77/iU

запасе/ 21

Фиг. 6

| Устройство для отображения информации на экране электроннолучевой трубки | 1974 |

|

SU596982A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для отображения радиолокационной информации на экране электронно-лучевой трубки | 1980 |

|

SU938309A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1986-06-07—Публикация

1984-07-10—Подача