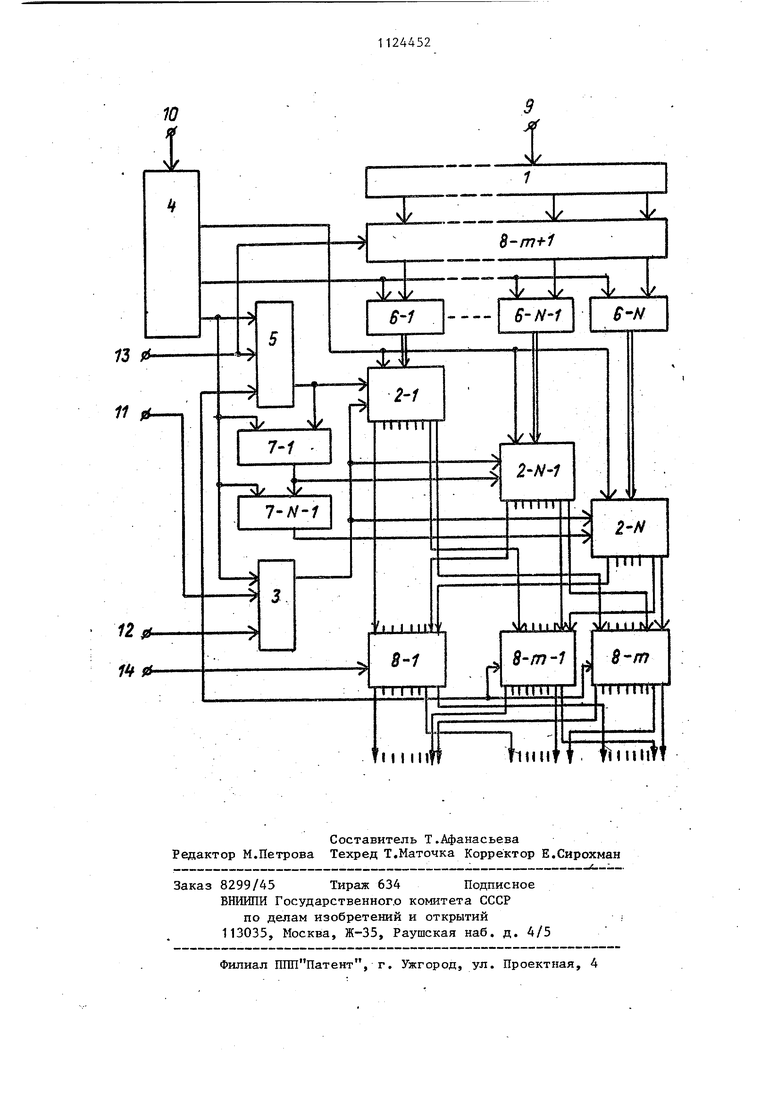

Изобретение относится к технической физике, автоматике, телевидению и вычислительной технике и может быт использовано в устройствах воспроизведения полутоновых изображений на матричных индикаторных панелях, например газоразрядных индикаторных панелях переменного тока, Известен многоканальньй преобразо ватель амплитуды телевизионного сигнала во временной интервал, содержащий многоканальный амплитудный тор, генератор поддерживающих и гася щих импульсов, первый выход которого соединен с входом распределителя импульсов, счетчик импульсов, формирователь импульсов записи и считывания, подключенный входами и выхода ми многоканального амплитудного селектора, и W идентичных каналов преобразования, каждьш из которых состо ит из плазменной индикаторной панели, кольцевого коммутатора и блока считывания, причем горизонтальные ши ны плазменной индикаторной панели , соединены с выходами кольцевого коммутатора, вертикальные шины - с выходами распределителя импульсов, а блок считывания оптически связан с плазменной индикаторной панелью, при этом суммирук)щий вход и коммутируемьй вход кольцевого коммутатора соединены соответственно с вторым выходом генератора поддерживающих и гасящих импульсов и с одним из N выходов формирЬвателя импульсов записи и считывания, а управляющий вход кольцевого коммутатора соединен с выходом счетчика импульсов lj . Недостатком данного устройства яв л .ется низкое быстродействие считыв.ния информации. Известен также многоканальный пре образователь амплитуды телевизионного сигнала во временной интервал, со держащий аналого-цифровой преобразователь, выходом соединенный с буферным запоминающим устройством СЗУ) емкостью в одну строку, выходные шины которого соединены с первыми вход ми многоканального блока сравнения, вторые входы которого являются входа ми кодов номера градаций, выходные шины многоканального блока сравнения соединены с входам блоков памяти, число которых равно числу градаций яркости, а объем каждого из них равен числу ячеек экрана матричного и 1дикатора 2J . Недостатком этог( устройства является низкое быстродействие считывания информации, что вызвано тем, что информация считывается отдельно для каждой градации. Наиболее близким по технической сущности к предлагаемому является многоканальньй преобразователь амплитуды телевизионного сигнала во временной интервал, содержащий N разрядный аналого-цифровой преобразователь, вход которого является входом телевизионного сигнала, N блоков памяти, входами старших разрядов кода адреса соединенных с выходами первого коммутатора, первьй и второй информационные входы которого являются входами сигналов кода адреса строки записи и кода адреса строки считывания соответственно, а управляющий вход подключен к первому выходу блока управления и управляющему вйоду второго коммутатора, первый и второй информационные входы которого являются входами сигналов кода группы записи и кода разряда считывания соответственно, а выход подключен к входам fflaдшeгo разряда кода адреса N блоков памяти, входы записи которых объединены и подключены к третьему выходу блока управления, вторым выходом соединенного с управляющими входами М регистров, выход каждого из которых подключен к информационным входам соответствующих блоков памяти. Устройство также содержит буферное запоминающее устройство, информационные входы которого подключены к выходам соответствующих блоков памяти, а вход управления - к выходу блока управления, при этом выходы буферного запоминающего устройства являются выходными информационными шинами, а выходные шины N -разрядного аналого-цифрового преобразователя подключены к информационным входам регистров . Недостатком известного устройства является низкое быстродействие, вызванное тем, что дпя считывания одного разряда кода яркости и записи его в буферное запоминающее устройство необходимо не менее тактов. Считывание с блоков памяти может производиться лишь после накопления кодов яркости ячеек строки. Запись следующей строки не может производиться пока не преобразуются в яр3кость все разряды предыдущей, что требует интервала времени не менее длительности строки. Поэтому из-за низкого быстродействия теряется каждая вторая строка видеосигнала и йыходное изображение имеет всего 256 строк (вместо 512), что ух дшает его качество. Цель изобретения - повышение быст родействия преобразования информации. Поставленная цель достигается тем что в многоканальный преобразователь амплитуды телевизионного сигнала во , временной интервал, содержащий М разрядный аналого-цифровой преобразо ватель, вход которого является входом телевизионного сигнала, блок управления, первьй выход которого подключен к управляющим входам первого и второго коммутаторов, второй выход - к управляющим входам N регистров, а третий вь1ход - к входам записи N блоков памяти, П) выходов i -го (,...,N) регистра соединены с соответствующими информационными t входами i -го блока памяти, входы старших разрядов N блоков памяти объединены и подключены к выходу первого коммутатора, первый и второй информационные входы которого являются соответственно входами сигналов кода адреса строки записи и кода адреса строки считывания, вход младшего разряда первого блока памяти поДключен к выходу второго коммутатора, первый и второй информационные входы которого являются входами сигналов кода группы записи и кода разряда считывания, введены (т+1) блоков сдвига и (N-1) сумматоров, при этом 1-й информационный выход каждого бло ка памяти подключен к информацио1у1ым входам 1-го ,..., ) блока сдвига входы управления т блоков сдвига объединены с вторым информационным входом второго коммутатора, информационные входа ()-го блока сдвига подключены к соответствунлцим выходам VI -разрядного аналого-цифрового преобразователя, выходы - к информационньм входам соответствующих N регистров, вход управления объединен с первым информационным вх дом второго коммутатора, (N-1) сумматоров соединены последовательно, вторые входы их объединены с управляквднм входом первого коммутатора. 52 вход первого сумматора подключен к выходу второго коммутатора, а выход к входу младщёго разряда второго блока памяти, вькод второго сумматора соединен с входом младшего разряда третьего блока памяти, а выход (Ы-1)-го сумматора - с входом кпадшего разряда N-го блока памяти. На чертеже представлена структурная электрическая схема предлагаемого преобразователя. Преобразователь содержит М -разрядный аналого-цифровой преобразователь (АЦП) 1, блоки 2-1 - 2-N памяти, первый коммутатор 3, блок 4 управления, второй коммутатор 5, регистры 6-1 - б-И, сумматоры 7-1 - 7-N-1, , блоки 8-1 - 8-)п+1 сдвига. На вход 9 поступает телевизионный сигнал, на вход 10 - синхросигнал, на вход 11 сигнал кода адреса строки записи, на вход 12 - сигнал кода адреса строки считьгоания, на вход 13 - сигнал кода группы записи, на вход 14 сигнал кода разряда считывания. Устройство работает следующим образом. I На вход 9 многоканального преоб- разователя последовательно, строка за строкой поступает телевизионный сигнал, амплитуды отсчетов которого пропорциональны яркостям соответствующих ячеек матричного индикатора. N разрядный АЦП 1 преобразует амплитуды отсчетов видеосигнала в N -разрядные коды, которые записываются в блоки 2-1 - 2-N памяти емкостью в число ячеек экрана матричного индикатора каждый. Согласование высокой частоты смены кодов отсчетов телевизионного сигнала с низким быстрог действием блоков 2-1 - 2-N памяти производится с помощью регистров 6-1 - 6-Н длиной ft) п/Ц, где Ч - число элементовразрешения в строке. Запись разрядов кодов яркости в регистры 6-1 - 6-N производится тактовыми импульсами, поступающими с второго выхода блока 4 управления. При заполнёнии регистров 6-t - б-Н коды с их выходов переписываются в блоки 2-1 - 2-N памяти импульсами записи, поступаизщими с третьего выхода блока 4 управления. Адрес записи и считывания информации с блоков 2-1 - 2-Й памяти определяется кодами на выходах первого и второго коммутаторов 3 и 5. На выходе первого коммутат(ра 3присутствуют старшие разряды, а на выходе второго коммутатора 5 младшие разряды кодов адреса. При этом сигнал с первого выхода блока 4управления на управляющих входах первого и второго коммутаторов 3 и 5определяет, с какого входа пропускаются коды на выход логической единице соответствует прохождение кодов с первых входов на выходы первого и второго коммутаторов 3 и логическому нулю - с вторьк входов на их выходы, Синхронизадая работы многоканального преобразователя телевизионного сигнала во временной и тервал с моментами поступления телевизионного сигнала и моментами смены кодов на информационных -входах первого и второго коммутаторов 3 и 5 производится импульсами синхронизации (например, строчными импульсами поступающими на вход 10 блока 4 упр ления. Запись информации производит ся по сигналам кодов адресов на информационных входах первого и второ го коммутаторов 3 и 5. Если входной телевизионный сигнал поступает в телевизионном стандарте (со строчно кадровым разложением), коды адреса могут формироваться блоком развертки записи (на чертеже не показан), который включает последовательно соединенные счетчик групп и счетчик строк записи, на счетный вход перво го поступают тактовые и myльcы, а на вход обнуления - кадровые синхроимпульсы. Со счетчика групп снимается код группы, который поступает по входу 13 на первый информационньй вход второго коммутатора 5, а со счетчика строк-снимается код .а реса строки при записи, который поступает по входу 11 на первый инфор мационный вход первого комм татора Запись информации в блоки 2-1 -2-il памяти может производиться и со скоростью, отличной от параметров т левизионного сигнала., например боле низкой. Соответственно меняется ско рость смены кодов на входе 11 сигна ла кода адреса строки при записи и на входе 13 сигнала кода группы при записи. Старшие разряды кода адреса записи и считывания, которые присутст Бук№. на выходе первого ком гутатора .представляют собой адрес с участка блоков 2-1 - 2-Нпа№1ТИ, в которые заносятся коды яркости ячеек одной строки, а младшие, присутствующие на выходе второго коммутатора 5 -. в адрес ячейки блоков 2-1 - 2-N памяти внутри участка, по которому записываются коды яркости ячеек группы. ) В зависимости от кода сдвига коды амплитуды отсчетов видеосигнала с шин N -разрядного ЛЦГ1 1 поступают либо на входы одноименных регистров 6-1 - 6-N (код сдвига 00),-либо со сдвигом, определяемь м величиной кода сдвига, при этом коды с шин старших разрядов N -разрядного АЦП 1 перекоммутируются на входы регистров 6-1 - 6-N с меньшими номерами. При записи информации в блоки 2-1 2-W памяти логическая единица с первого выхода блока 4 управления поступает на первые входы сумматоров 7-1 7-N-1,4To выбывает изменение значения младших разрядов кода адреса на входе каждого последующего блока памяти на единицу по сравнению со значением кодов на входе предьщущего- блока 2-i-1 памяти, В качестве примера записи информации в ячейки блоков 2-) памяти рассмотрим случай, когда сумматоры 7-1 7-N-1 вычитают из значения кодов на вторых выходах единицу,поступающую на первые их входы. При приходе на вход М-разрядного АЦП 1 строки телевизионт ного сигнала информация в блоки 2-1 2-М памяти записывается N группами по Vi отсчетов за N тактов. Для первой группы код на первом информационном входе второго коммутатора 5 и на входе управления блока 8-fn+1 сдвига устанавливается равным нулю. Блок 8-1п+1 сдвига не производит при этом сдвиг кодов, коды с шины первого разряда М -разрядного АЦП 1 поступят Иа вход первого регистра 6-1, с шины второго разряда - на вход второго регистра 6-2 и т,д, и будут записываться в регистры 6- ( тактовыми импульсами, поступающими на их управляющие входы с второго выхода блока 4 управления. При заполнении регистров 6- коды с их выходов записываются в одноименные блоки памяти импульсами записи, поступающими с тре-. тьего выхода блока управ.пения. При этом первый разряд запишется в первую я хейку первого блока 2-1 памяти, второй разряд - во вторую ячейку второго блока 2-2 и т,д,,М -и разряд запишется в Н -ш ячейку блок 2-Мпамяти. При записи второй группы код на иервом информационном вхо де второго кокгмутатора 5 увеличивае ся на единицу и блок сдвига п рекоммутирует выходные шины N-разря ного АЦП 1 на входы регистров 6-1 таким образом, что коды с выходной ны первого разряда N -разрядного АЦ 1 поступят на вход второго регистра 6-2, коды с выходной шины второго разряда АЦП 1 поступят на вход третьего регистра 6-3, коды с 1Ш1Ны N разряда поступят на вход первого ре гистра 6-1. При заполнении регистро информация с их выходов переписывается в блоки 2-4 памяти импульсом записи. При этом первьм разряд кодов амплитуды отсчетов телевизион ного сигнала второй группы запишется с второго регистра 6-2 в первую ячейку второго блока2-2 памяти, вт рой разряд кодов отсчетов второй гр пы запишется с третьего регистра 6-3 во вторую ячейку третьего блока 2-3 памяти, а М -и разряд кодов отсчетов второй группы запишется в N ячейку первого блока 2-1 памяти. При записи N -и группы отсчетов телевизионного сигнала код на первом информационном входе второго коммут тора 5 примет максимальное значение и блок 8-1W-1 сдвига перекоммутирует коды с выходных шин К -разрядного АЦП 1 на входы регистров 6-4 таким образом, что Первьй разряд кода запишется в регистр 6-N, второй разряд - в регистр 6-1 и ТоД, С приходом импульса записи информация запи Ьется в блоки 2- i памяти так, что первый разряд кодов амплитуд отсчетов телевизионного сигнала N-и груп пы с регистра 6-N запишется в перву ячейку блока 2-N памяти, второй разряд кодов ат-шлитуд отсчетов N-и группы - во вторую.ячейку блока 2-1 памяти и т.д. I Таким образом, в первой ячейке всех блоков 2- будет записан первый разряд кодов амплитуды всех отсчетов данной строки, во второй яче ке блоков 2- i памяти - второй разряд кодов амплитуд всех отсчетов, в N-и ячейке блоков 2-i памяти - N разряд. Однако все разрпцы, кроме .первого, будут записаны со сдвигом зависящим от номера разряда. 528 На этом завершается запись кодов амплитуд отсчетов телевизионного сигнала строки, код адреса которой был установлен на первом информащ{онном входе первого коммутатора 3. При приходе телевизионного сигнала новой строки операции повторяются для нового участка блока 2-i памяти, адрес которого устанавливается на первом информационном входе первого ком гyтaтopa 3, и таким образом записы-. Баются коды яркости всех ячеек экрана матричного индикатора. В примере управления состоянием ячеек при модуляции яркости с помощью многоканального преобразователя изображение формируется за время кадра, при этом частота кадров должна быть достаточно высокой (например, 50 Гц) для исключения мелькаг НИИ изображения. Весь кадр разбивается на интервалы, количество которых равно числу разрядов кода яркости N , а длительности соотносятся как 1:2:4... Свечением ячеек в самом коротком интервале управляют первым разрядом, в самом длинном - N -м разрядом. Таким образом, в течение кадра к одной и той же строке обращаются N раз, однако ячейки каждый раз управляются новым разрядом. Для N -8 сече-, тание различных интервалов дает 256 разных длительностей и значит 256 градаций яркости, что обеспечивает вое-. произведение высококачественного изображения. Максимальной яркости соответствует код 111... 1, когда ячейка горит во всех интервалах, коду 000...01 соответствует максимальный временной интервал свечения ячейки. Программу изменеш1я кодов на вто- . рых информационных входах первого и второго коммутато)ов 3 и 5 при считывании формирует блок развертки считывания, включакхций счетчик разрядов, выходом подключенный к счетчику строк и кодопреобразователю, хранящему коды весов разрядов. Выходы счетчика строк и кодопреобразователя подключены к входам сумматора, выход которого является выходом блока. Каждому значению кода на выходе счетчика разядов соответствует код на выходе Kof допреобразователя (следовательно, код адреса строки, состоянием ячеек которой необходимо управлять в.данньс. момент времени) и разряд кода яркости, который извлекается из блоков 91 2-4 памяти. После появления Я чисел на выходе кодопреобразователя изменяется на единицу код на выходе счет чика строк и процесс выбора N разряДОН производится для следующей труп пы из N строк, смещенных на единицу относительно предьщущих строк. При считывании кодов цля преобразования их в длительность свечения ячеек матричного индикатора на управляющие входы первого и второго коммутаторов 3 и 5 и первые входы сумматоров 7-1 - 7-М-1 поступает логический нуль. При этом младшие разряды кода адреса считывания с второго информащюнного входа второго коммутатора 5 (код разряда) проходят через сумматоры 7-1 - 7-N-1 на входы младших разрядов кода адреса всех блоков 2-1 - 2-N памяти без изменений. Таким образом, считывание производится с одноименных ячеек всех блоков 2-1 - 2-Мпамяти и на их выходных шинах появляется выбранный разряд кодов яркостей ячеек стро ки, код адреса которой установлен на втором информационном входе коммутатора 3, В отдельном блоке 2- памяти записаны разряды кодов яркости, относящиеся к различным группам ячеек строки матричного индикатора (так, в первом блоке 2-1 памяти записан первый разряд кода яркости первой группы ячеек, второй разряд N -и груп пы, третий - (Н-1)-й,...,и-й разряд второй группы, что является результатом прохождения кодов через блок 8-1П+1 сдвига. Для получения на выход ных информационных шинах многоканал ного преобразователя разрядов кода яркости, соответствующих ячейкам мат ричного индикатора, блоки 8-1 - 8-т сдвига, осуществляют циклический сдви информации в обратном направлении. 10 Например, для первого разряда кода яркости, который записан в блоки 2-12-N памяти в неискаженной форме, циклический сдвиг не требуется (код сдвига 00) и коды передаются с.выходных шин б.лбка 2-1 памяти на первую группу из подряд расположенных выходных шин, с выходных шин блока 2-2 памяти - на вторую группу подряд расположенных шин и т.д. Для второго разряда кода яркости требуется сдвиг на один шаг влево, поскольку втброй разряд первой группы находится в блоке 8-2 памяти и на блоки сдвига 8- i пос-тупает. код 01. При этом коды с выходных шин блока 2-2 памяти поступают на первую группу из m подряд paсположенных выходных шин, с выходных шин блока 2-3 памяти - на вторую группу mподряд расположенных выходных шин, с выходных шин блока 2-1 памяти на N -ю группу выходных шин. Для третьего разряда кода яркости требуется сдвиг на два шага влево, поскольку третий разряд первой группы находится в блоке 2-3 памяти и на блоки сдвига 8-1 - ) поступает код to и т.д. Выполнение описанной операщи обеспечивается тем, что первые информационные входы блоков 8-1 8-}псдвига подключены к соответствующим информационным выходам блока 2-1 памяти. Аналогично вторые информационные входы блоков 8-1 - 8-т сдвига подключены к соответствуклцим информационным выходам блока 2-2 памяти и т.д. Таким образом, многоканальный преобразователь амплитуды телевизионного сигнала во временной интервал позволяет получать на выходе за один такт ту же информацию, которая получается в известном преобразователе за N тактов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Телевизионное воспроизводящее устройство | 1981 |

|

SU1109950A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Устройство для индикации | 1984 |

|

SU1236540A1 |

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

| Устройство для отображения информации | 1986 |

|

SU1432594A1 |

| Устройство воспроизведения изображений | 1979 |

|

SU873461A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

| Устройство для отображения информации | 1984 |

|

SU1236541A1 |

| Устройство для контроля многопроводного кабеля | 1986 |

|

SU1352415A1 |

| Запоминающее устройство | 1987 |

|

SU1413674A1 |

МНОГОКАНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ Амплитуда ТЕЛЕВИЗИОННОГО СИГНАЛА ВО ВРЕМЕННОЙ ИНТЕРВАЛ, содержащий N разрядный аналого-цифровой преобразователь, ВХОД которого является входом телевизионного сигнала, блок управления, первый выход которЬго подключен к управляющим входам первого и второго коммутаторов, второй выход - к управляющим входа И регистров , а третий выход - к входам записи N блоков памяти, m выходов 4 fo

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Многоканальный преобразователь амплитуды импульсов во временной интервал | 1975 |

|

SU666660A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

Авторы

Даты

1984-11-15—Публикация

1983-04-11—Подача