1

(Л

to ел

;О 4

го по четперт1,1й блоки - 4 оперативной памяти, датчик 5 кодов яркости, формирователи адреса записи по координатам Y 6 и X 7, формирователь 8 телевизионной развертки, блок 9 буферной памяти, блок 10 индикации, с первого по четвертый умножители 11 - 14, первый 15 и второй 19 распределители импульсов, первый коммутатор 16, элемент НЕ 17, сумматор 18, второй коммутатор 20 с соответствующими связями. Повышение точности отображения достигается за счет раздельной записи взвешенных кодов яркости точек в блоки 1 - 4 оперативной памят, таким образом, что отсутствуют потери информации, возникающие при дискретизации математических координат отсчетов при формировании растрового массива. 4 ил.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения информации | 1989 |

|

SU1695373A1 |

| Устройство для считывания графической информации | 1987 |

|

SU1564661A1 |

| Устройство для отображения информации на экране видеоконтрольного блока | 1988 |

|

SU1562954A1 |

| Устройство для формирования векторов на экране телевизионного индикатора | 1988 |

|

SU1506477A1 |

| Устройство для отображения векторных диаграмм на экране электронно-лучевой трубки | 1988 |

|

SU1541663A1 |

| Устройство для отображения информации на экране телевизионного индикатора | 1986 |

|

SU1695372A1 |

| Устройство для индикации | 1984 |

|

SU1236540A1 |

| УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ДВУМЕРНОЙ СВЕРТКИ | 1992 |

|

RU2042209C1 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1777651A3 |

| Устройство для отображения информации на экране телевизионного индикатора | 1984 |

|

SU1292029A1 |

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении устройств отображения с телевизионным методом построения изображения. Цель изобретения - повышение точности устройства. Устройство содержит с перво

1

Изобретение относится к вычислительной технике и автоматике и может быть использовано при построении устройств отображения с телевизионным методом формирования изображения.

Цель изобретения - повышение точности устройства.

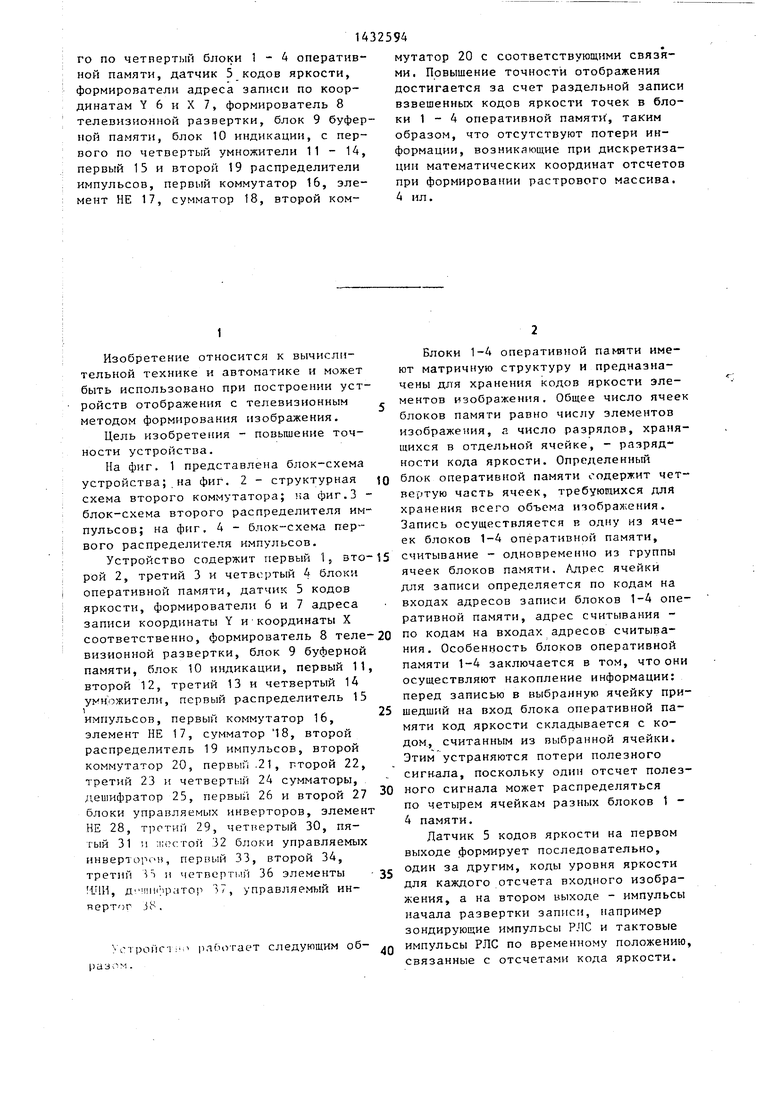

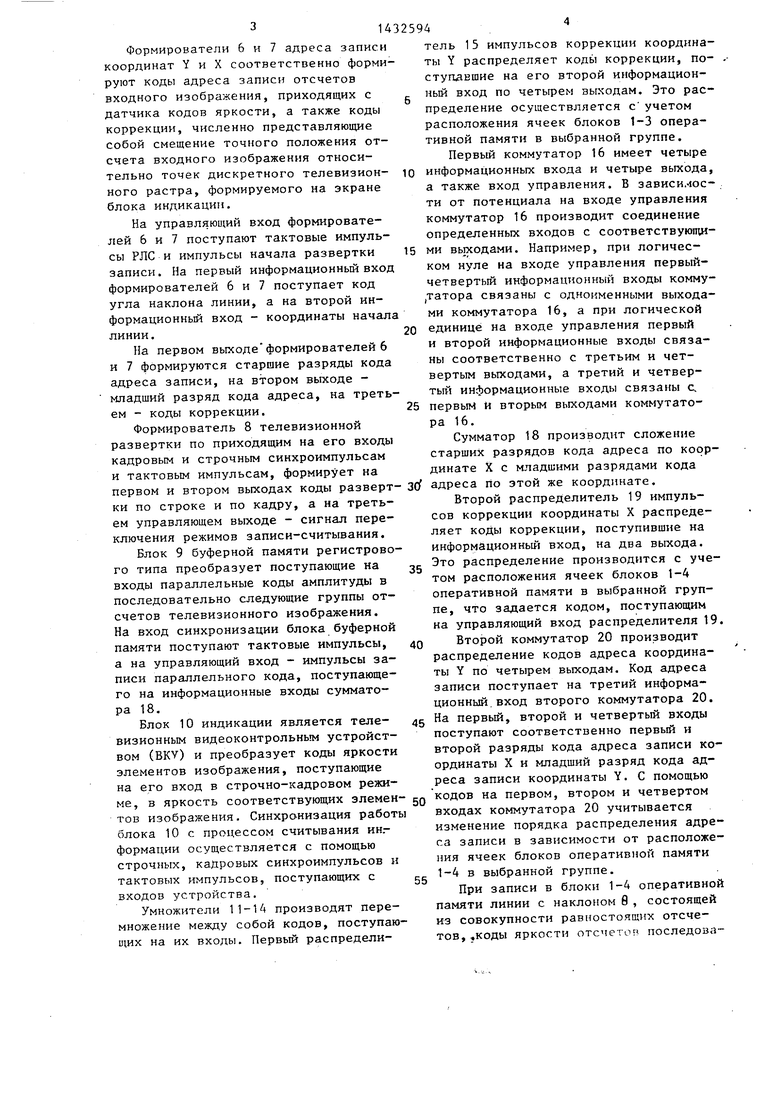

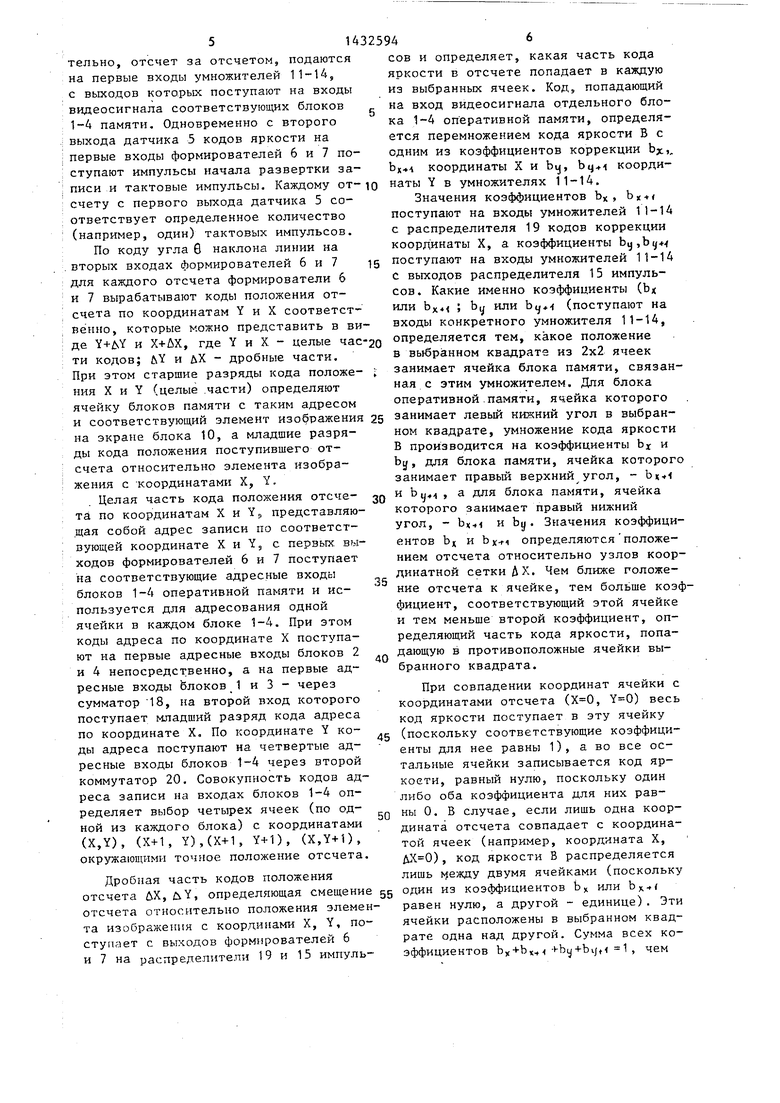

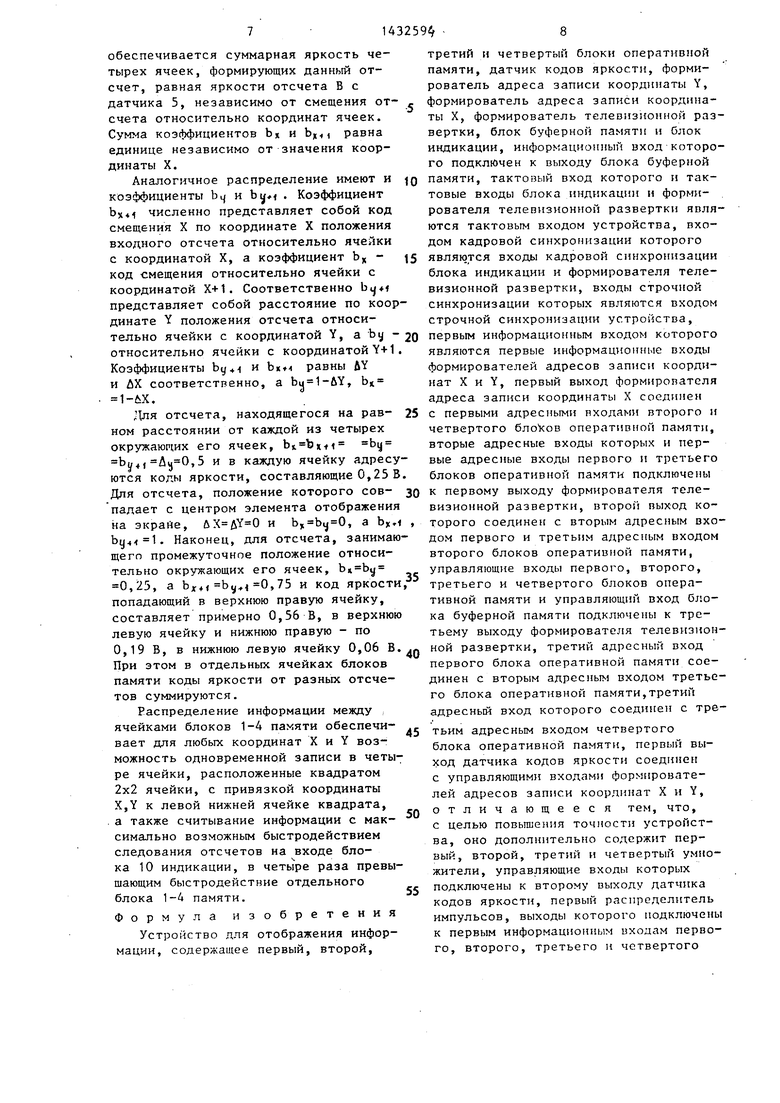

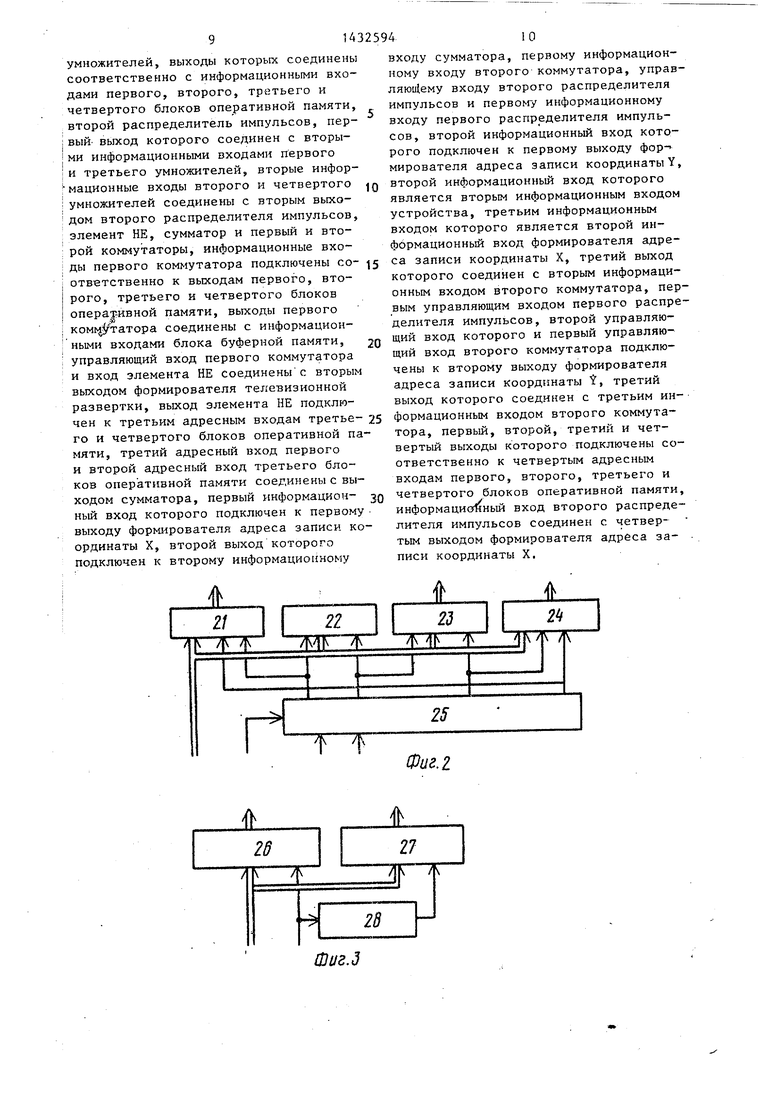

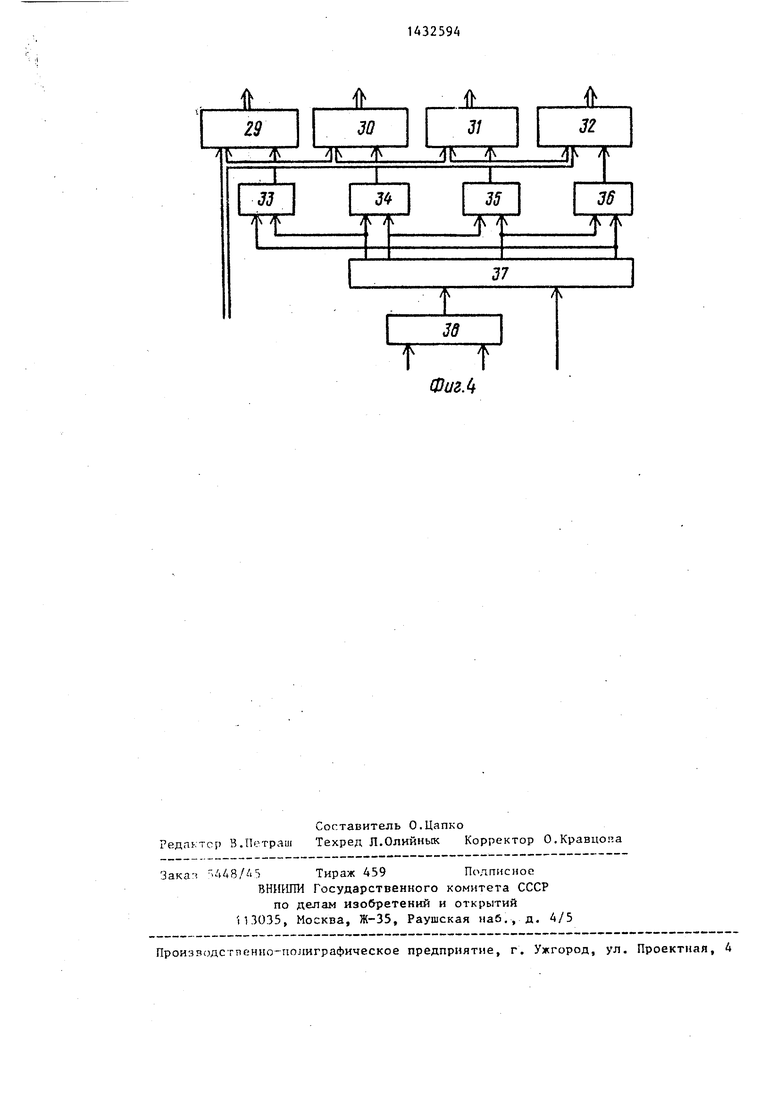

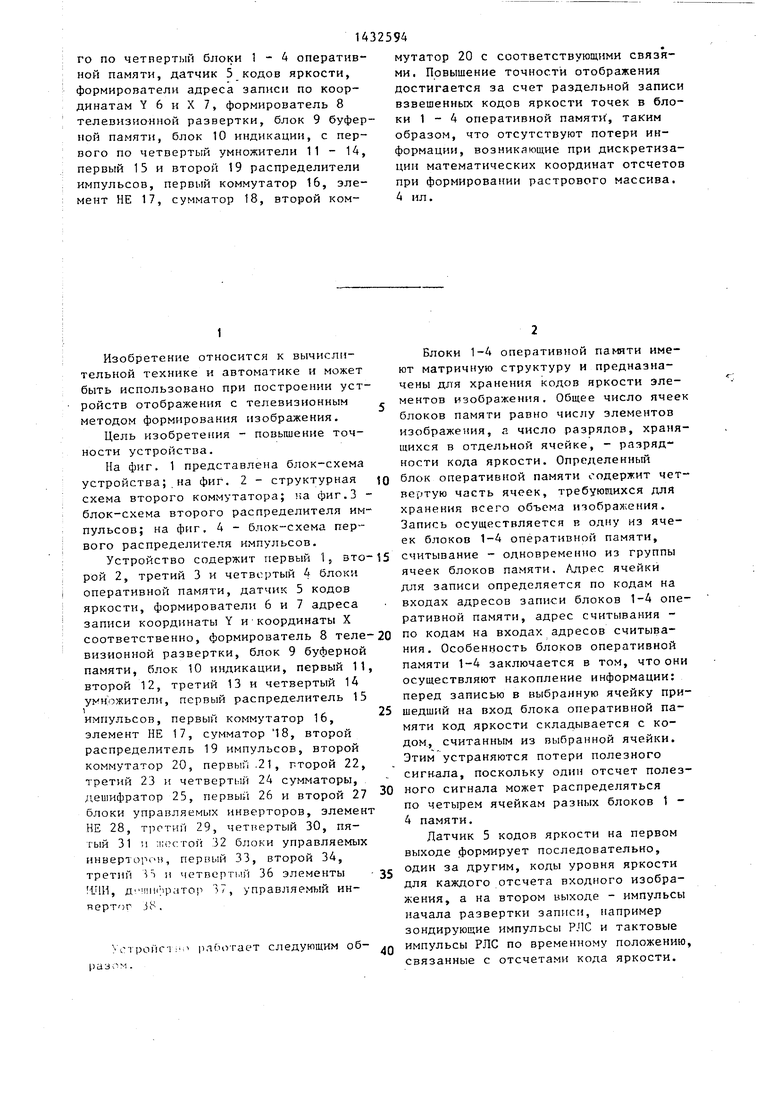

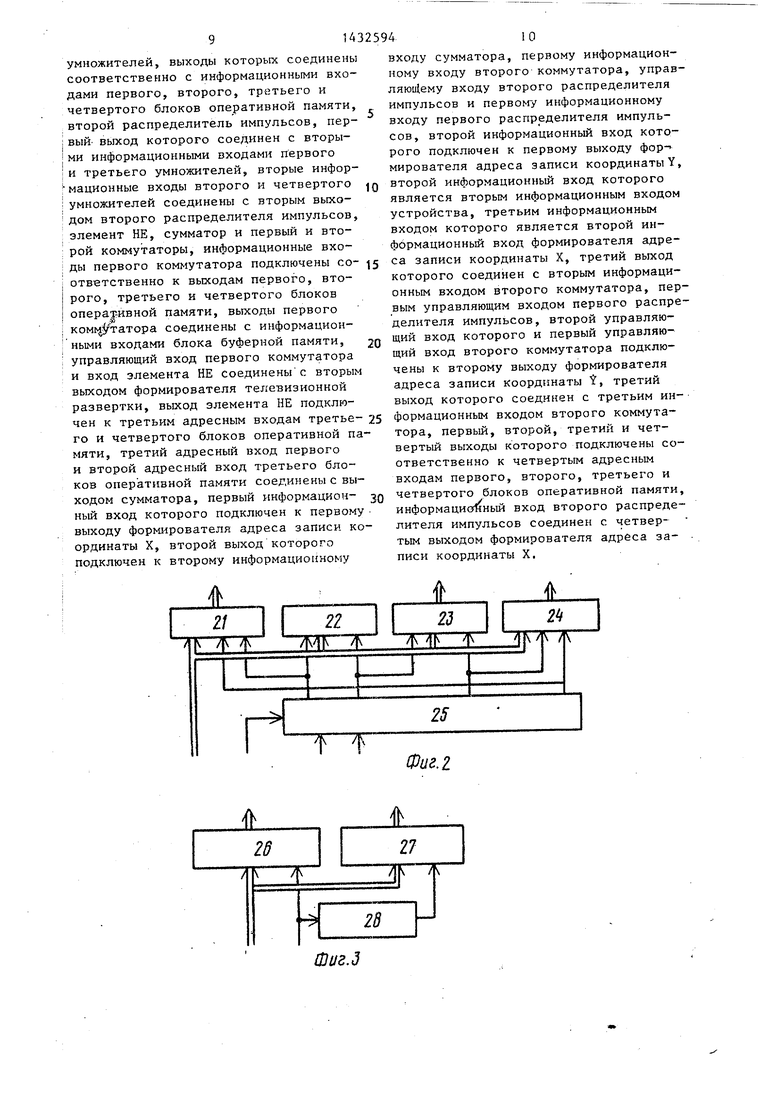

На фиг. 1 представлена блок-схема устройства; на фиГ. 2 - структурная схема второго коммутатора; ;а фиг.З - блок-схема второго распределителя импульсов; на фиг. 4 - блок-схема первого распределителя импульсов.

Устройство содержит первый If второй 2, третий 3 и четвертый 4 блоки оперативной памяти, датчик 5 кодов яркости, формирователи 6 и 7 адреса записи координаты Y икоординаты X соответственно, формирователь 8 телевизионной развертки, блок 9 буферной памяти, блок 10 индикации, первый 11, второй 12, третий 13 и четвертый 14

умнЪжители, первый распределитель 15

1

импульсов, первый коммутатор 16,

элемент НЕ 17, сумматор 18, второй распределитель 19 импульсов, второй коммутатор 20, первый.21, гторой 22, третий 23 и четвертьлй 24 сумматоры, , дешифратор 25, первый 26 и второй 27 блоки управляемых инверторов, элемент НЕ 28, третий 29, четвертый 30, пя- гый 31 я -иес.той 32 блоки управляемых инверто ргм), первый 33, второй 34, третий -i) и четвсрт1,1й 36 элементы МЧИ, (Ьратор 37, управляемый ин- лерт )Г J8,

роист ) :1 рлОотает следующим об- .Q разом.

Блоки 1-4 оператив1 ой памяти имеют матричную структуру и предназначены для хранения кодов яркости элементов изображения. Общее число ячеек блоков памяти равно числу элементов изображения, а число разрядов, хранящихся в отдельной ячейке, - разрядности кода яркости. Определенньй блок оперативной памяти содержит четвертую часть ячеек, требующихся для хранения всего объема изобрах;ения. Запись осуществляется в одну из ячеек блоков 1-4 оперативной памяти, считывание - одновремевою из группы ячеек блоков памяти. Адрес ячейки для записи определяется по кодам на входах адресов записи блоков 1-4 оперативной памяти, адрес считывания - по кодам на входах адресов считывания. Особенность блоков оперативной памяти 1-4 заключается в том, что они осуществляют накопление информации: перед записью в выбранную ячейку пришедший на вход блока оперативной памяти код яркости складывается с кодом, считанным из выбранной ячейки. Этим устраняются потери полезного сигнала, поскольку один отсчет полезного сигнала может распределяться по четырем ячейкам разных блоков 1 - 4 памяти.

Датчик 5 кодов яркости на первом выходе формирует последовательно, один за другим, коды уровня яркости для каждого отсчета входного изображения, а на втором выходе - импульсы начала развертки записи, например зондирующие импульсы РЛС и тактовые импульсы РЛС по временному положению, связанные с отсчетами кода яркости.

Формирователи 6 и 7 адреса записи координат Y и X соответственно формируют коды адреса записи отсчетов входного изображения, приходящих с датчика кодов яркости, а также коды коррекции, численно представляющие собой смещение точного положения отсчета входного изображения относительно точек дискретного телевизионного растра, формируемого на экране блока индикации.

На управляющий вход формирователей 6 и 7 поступают тактовые импульсы РЛС и импульсы начала развертки записи. На первый информационный вход формирователей 6 и 7 поступает код угла наклона линии, а на второй ин- формационньй вход - координаты начала линии.

На первом вьгеоде формирователей 6 и 7 формируются старшие разряды кода адреса записи, на втором выходе - младший разряд кода адреса, на третьем - коды коррекции.

Формирователь 8 телевизионной развертки по приходящим на его входы кадровым и строчным синхроимпульсам и тактовым импульсам, формирует на

тель 15 импульсов коррекции к ты Y распределяет коды коррекц ступавшие на его второй информ ный вход по четьфем выходам. Э пределение осуществляется с уч расположения ячеек блоков 1-3 тивной памяти в выбранной груп Первый коммутатор 16 имеет

10 информационных входа и четыре а также вход управления. В зав ти от потенциала на входе упра коммутатор 16 производит соеди определенных входов с соответс

15 ми вьгходами. Например, при лог ком нуле на входе управления п четвертый информацтюннь й входы ,татора связаны с одноименными ми коммутатора 16, а при логич

20 единице на входе управления пе и второй информационные входы ны соответственно с третьим и вертым вьпсодами, а третий и че тый информационные входы связа

25 первым и вторьгм выходами комму ра 16.

Сумматор 18 производит слож старших разрядов кода адреса п динате X с младшими разрядами

первом и втором выходах коды разверт- 3Cf адреса по этой же координате.

ки по строке и по кадру, а на третьем управляющем выходе - сигнал переключения режимов записи-считывания.

Блок 9 буферной памяти регистрового типа преобразует поступающие на входы параллельные коды амплитуды в последовательно следующие группы отсчетов телевизионного изображения. На вход синхронизации блока буферной памяти поступают тактовые импульсы, а на управляющий вход - импульсы записи параллельного кода, поступающего на информационные входы сумматора 18.

Блок 10 индикации является телевизионным видеоконтрольным устройством (BKV) и преобразует коды яркости элементов изображения, поступающие на его вход в строчно-кадровом режиме, в яркость соответствующих элеме тон изображения. Синхронизация рабо блока 10 с процессом считывания информации осуществляется с помощью строчных, кадровых синхроимпульсов тактовых импульсов, поступающих с входов устройства.

Умножители 11-14 производят перемножение между собой кодов, поступащих на их входы. Первый распредели

тель 15 импульсов коррекции координаты Y распределяет коды коррекции, поступавшие на его второй информацион- ный вход по четьфем выходам. Это распределение осуществляется с учетом расположения ячеек блоков 1-3 оперативной памяти в выбранной группе. Первый коммутатор 16 имеет четыре

информационных входа и четыре выхода, а также вход управления. В зависимое-, ти от потенциала на входе управления коммутатор 16 производит соединение определенных входов с соответствующими вьгходами. Например, при логическом нуле на входе управления первый- четвертый информацтюннь й входы комму- ,татора связаны с одноименными выходами коммутатора 16, а при логической

единице на входе управления первый и второй информационные входы связаны соответственно с третьим и четвертым вьпсодами, а третий и четвертый информационные входы связаны с,

первым и вторьгм выходами коммутатора 16.

Сумматор 18 производит сложение старших разрядов кода адреса по координате X с младшими разрядами кода

5

0

g ов на первом, входах коммутатора

Второй распределитель 19 импульсов коррекции координаты X распределяет коды коррекции, поступившие на информационный вход, на два выхода. Это распределение производится с учетом расположения ячеек блоков 1-4 оперативной памяти в выбранной группе, что задается кодом, поступающим на управляющий вход распределителя 19.

Второй коммутатор 20 производит распределение кодов адреса координаты Y по четырем выходам. Код адреса записи поступает на третий информационный, вход второго коммутатора 20. 5 На первый, второй и четвертый входы поступают соответственно первый и второй разряды кода адреса записи координаты X и младший разряд кода адреса записи координаты Y. С помощью втором и четвертом

20 учитывается

изменение порядка распределения адреса записи в зависимости от расположения ячеек блоков оперативной памяти 1-4 в выбранной группе.

При записи в блоки 1-4 оперативной памяти линии с наклоном 9, состоящей из совокупности равностоящих отсчетов, «коды яркости отсчетов последова5

сов и определяет, какая часть кода яркости в отсчете попадает в кажду из выбранных ячеек. Код, попадающи на вход видеосигнала отдельного бл ка 1-4 оперативной памяти, определ ется перемножением кода яркости В одним из коэффициентов коррекции Ъ Ь)(л координаты X и bi, bij+i коорд наты Y в умножителях 11-14.

Значения коэффициентов Ъх, поступают на входы умножителей 11с распределителя 19 кодов коррекци координаты X, а коэффициенты Ьу,Ьц поступают на входы умножителей 11с выходов распределителя 15 импуль сов. Какие именно коэффициенты (Ьх

тельно, отсчет за отсчетом, подаются на первые входы умножителей 11-14, с выходов которых поступают на входы видеосигнала соответствующих блоков 1-4 памяти. Одновременно с второго выхода датчика 5 кодов яркости на первые входы формирователей 6 и 7 поступают импульсы начала развертки записи и тактовые импульсы. Каждому от- ю счету с первого выхода датчика 5 соответствует определенное количество (например, один) тактовых импульсов.

По коду угла 6 наклона линии на вторых входах формирователей 6 и 7 для каждого отсчета формирователи 6 и 7 вырабатывают коды положения отсчета по координатам Y и X соответственно, которые можно представить в виде Y+AY и Х+ЛХ, где Y и X - целые час-2о определяется тем, какое положение ти кодов; &Y и дХ - дробные части. При этом старшие разряды кода положения X и Y (целые .части) определяют ячейку блоков памяти с таким адресом

15

или Ьх4 ; by или bijti (поступают н входы конкретного умножителя 11-14

в выбранном квадрате из 2x2 ячеек занимает ячейка блока памяти, связ ная с этим умножителем. Для блока оперативной.памяти, ячейка которог

и соответствующий элемент изображения 25 занимает левый нижний угол в выбранна экране блока 10, а младшие разряды кода положения поступившего отсчета относительно элемента изображения с -координатами X, Y.

Целая часть кода положения отсчета по координатам X и Yp представляю- .щая собой адрес записи по соответствующей координате X и Y, с первык. выходов формирователей 6 и 7 поступает на соответствующие адресные входы блоков 1-4 оперативной памяти и используется для адресования одной ячейки в каждом блоке 1-4. При этом коды адреса по координате X поступают на первые адресные входы блоков 2 и 4 непосредственно, а на первые адресные входы блоков 1 и 3 - через сумматор 18, на второй вход которого поступает младший разряд кода адреса по координате X. По координате Y коды адреса поступают на четвертые адресные входы блоков 1-4 через второй коммутатор 20. Совокупность кодов адреса записи на входах блоков 1-4 определяет выбор четырех ячеек (по одной из ка одого блока) с координатами (X,Y), (Х+1, Y),(X+1, Y+1), (X,Y+1), окружающими точное положение отсчета.

Дробная часть кодов положения

30

35

40

45

50

ном квадрате, умножение кода яркости В производится на коэффициенты bj и , для блока памяти, ячейка которого занимает правый верхний угол, - Ъ и , а для блока памяти, ячейка которого занимает правый нижний угол, - и by. Значения коэффициентов bj( и Ьх-м определяются положением отсчета относительно узлов координатной сетки ДХ. Чем ближе положение отсчета к ячейке, тем больше коэф фициент, соответствующий этой ячейке и тем меньще второй коэффициент, определяющий часть кода яркости, попадающую в противоположные ячейки выбранного квадрата.

При совпадении координат ячейки с координатами отсчета (, ) весь код яркости поступает в эту ячейку (поскольку соответствующие коэффициенты для нее равны 1), а во все остальные ячейки записывается код яркости, равный нулю, поскольку один либо оба коэффициента для них равны 0. В случае, если лишь одна координата отсчета совпадает с координатой ячеек (например, координата X, ), код яркости В распределяется лишь к;ежду двумя ячейками (поскольку

отсчета ЛХ, Y, определяющая смещение 55 один из коэффициентов Ь или Ьх-.( отсчета относительно положения элемен- равен нулю, а другой - единице). Эти та изображения с координами X, Y, по- ячейки расположены в выбранном квад- ступает с выходов формирователей 6 и 7 на распределители 19 и 15 импульрате одна над другой. Сумма всех коэффициентов bx+b, +by+bijH 1 , чем

325946

сов и определяет, какая часть кода яркости в отсчете попадает в каждую из выбранных ячеек. Код, попадающий на вход видеосигнала отдельного блока 1-4 оперативной памяти, определяется перемножением кода яркости В с одним из коэффициентов коррекции Ъу.,, Ь)(л координаты X и bi, bij+i координаты Y в умножителях 11-14.

Значения коэффициентов Ъх, поступают на входы умножителей 1114 с распределителя 19 кодов коррекции координаты X, а коэффициенты Ьу,Ьц+4 поступают на входы умножителей 1114 с выходов распределителя 15 импуль сов. Какие именно коэффициенты (Ьх

ю

2о определяется тем, какое положение 15

определяется тем, какое положение

или Ьх4 ; by или bijti (поступают на входы конкретного умножителя 11-14,

определяется тем, какое положение

в выбранном квадрате из 2x2 ячеек занимает ячейка блока памяти, связанная с этим умножителем. Для блока оперативной.памяти, ячейка которого

0

5

0

5

0

ном квадрате, умножение кода яркости В производится на коэффициенты bj и , для блока памяти, ячейка которого занимает правый верхний угол, - Ъ и , а для блока памяти, ячейка которого занимает правый нижний угол, - и by. Значения коэффициентов bj( и Ьх-м определяются положением отсчета относительно узлов координатной сетки ДХ. Чем ближе положение отсчета к ячейке, тем больше коэффициент, соответствующий этой ячейке и тем меньще второй коэффициент, определяющий часть кода яркости, попадающую в противоположные ячейки выбранного квадрата.

При совпадении координат ячейки с координатами отсчета (, ) весь код яркости поступает в эту ячейку (поскольку соответствующие коэффициенты для нее равны 1), а во все остальные ячейки записывается код яркости, равный нулю, поскольку один либо оба коэффициента для них равны 0. В случае, если лишь одна координата отсчета совпадает с координатой ячеек (например, координата X, ), код яркости В распределяется лишь к;ежду двумя ячейками (поскольку

один из коэффициентов Ь или Ьх-.( равен нулю, а другой - единице). Эти ячейки расположены в выбранном квад-

рате одна над другой. Сумма всех коэффициентов bx+b, +by+bijH 1 , чем

обеспечивается суммарная яркость четырех ячеек, формирующих данный отсчет, равная яркости отсчета В с датчика 5, независимо от смещения от- счета относительно координат ячеек. Сумма коэффициентов Ьц и Ь, равна единице независимо от значения координаты X.

Аналогичное распределение имеют и коэффициенты Ьц и Ь, . Коэффициент bx4i численно представляет собой код смещения X по координате X положения входного отсчета относительно ячейки с координатой X, а коэффициент Ь - код смещения относительно ячейки с координатой Х+1. Соответственно представляет собой расстояние по координате Y положения отсчета относительно ячейки с координатой Y, а by - относительно ячейки с координатой Y+1 Коэффициенты by+i и равны fiY и ДХ соответственно, а , Ьц 1-6Х.

1ля отсчета, находящегося на рав- ном расстоянии от каждой из четырех окружаюпщх его ячеек, bj.bxf У Ьу, ,5 и в каждую ячейку адресуются коды яркости, составляющие 0,25 В Для отсчета, положение которого сов- падает с центром элемента отображения на экрайе, и b,b(, а Ь . Наконец, для отсчета, занимающего промежуточное положение относительно окружающих его ячеек, 0,25, а Ьх + Ьу 0,75 и код яркости попадающий в верхнюю правую ячейку, составляет примерно 0,56 В, в верхнюю левую ячейку и нижнюю правую - по 0,19 В, в нижнюю левую ячейку 0,06 В. При этом в отдельных ячейках блоков памяти коды яркости от разных отсчетов суммируются.

Распределение информации между ячейками блоков 1-4 памяти обеспечивает для любых координат X и Y возможность одновременной записи в четы

2x2 ячейки, с привязкой координаты X,Y к левой нижней ячейке квадрата, а также считывание информации с максимально возможным быстродействием следования отсчетов на входе блока 10 индикации, в четыре раза превышающим быстродейстрше отдельного блока 1-4 памяти. Формула изобретения

Устройство для отображения информации, содержащее первый, второй.

-

Q 5 0

5 О ,

5

0

5

0

5

третий и четвертый блоки оперативной памяти, датчик кодов яркости, формирователь адреса записи координаты Y, формирователь адреса записи координаты X, формирователь телевизионной развертки, блок буферной памяти и блок индикации, информационный вход которого подключен к выходу блока буферной памяти, тактовый вход которого и тактовые входы блока индикации и формирователя телевизионной развертки являются тактовым входом устройства, входом кадровой синхронизации которого являются входы кадровой синхронизации блока индикации и формирователя телевизионной развертки, входы строчной синхронизации которых являются входом строчной синхронизации устройства, первым информационным входом которого являются первые информационные входы формирователей адресов записи координат X и Y, первый выход формирователя адреса записи координаты X соединен с первыми адресными пходами второго и четвертого бло ков оперативной памяти, вторые адресные входы которых и первые адресные входы первого и третьего блоков оперативной памяти подключены к первому выходу формирователя телевизионной развертки, второй выход которого соединен с вторым адресным входом первого и третьим адресным входом второго блоков оперативной памяти, управляющие входы первого, второго, третьего и четвертого блоков оперативной памяти и управляющий вход блока буферной памяти подключены к третьему выходу формирователя телевизионной развертки, третий адресный вход первого блока оперативной памяти соединен с вторым адресным входом третьего блока оперативной памяти,третий адресный вход которого соединен с третьим адресным входом четвертого блока оперативной памяти, первый выход датчика кодов яркости соединен с управляющими входами формирователей адресов записи координат X и Y, отличающееся тем, что, с целью пoвьщJeн я точности устройства, оно дополнительно содержит первый, второй, третий и четвертый умножители, управляющие входы которых подключены к второму выходу датчика кодов яркости, первый распределитель импульсов, выходы которого подключены к первым информационным входам первого, второго, третьего и четвертого

умножителей, выходы которых соединены соответственно с информационными входами первого, второго, третьего и четвертого блоков оперативной памяти, второй распределитель импульсов, пер- ;вый- выход которого соединен с вторы- i ми информационными входами Первого , и третьего умножителей, вторые инфор- мационные входы второго и четвертого умножителей соединены с вторым выходом второго распределителя импульсов, элемент НЕ, сумматор и первый и второй коммутаторы, информационные входы первого коммутатора подключены соответственно к выходам первого, второго, третьего и четвертого блоков операт-ивной памяти, выходы первого ком1 татора соединены с информационными входами блока буферной памяти, управляющий вход первого коммутатора и вход элемента НЕ соединены с вторым выходом формирователя техгевизионной развертки, выход элемента НЕ подключен к третьим адресным входам третье- го и четвертого блоков оперативной памяти, третий адресный вход первого и второй адресный вход третьего блоков оперативной памяти соединены с выходом сумматора, первый информацией- ный вход которого подключен к первому выходу формирователя адреса записи координаты X, второй выход которого подключен к второму информационному

JL

Шаг.З

0

5

5 о

0

входу сумматора, первому информационному входу второго коммутатора, управ- входу второго распределителя импульсов и первому информационному входу первого распределителя импульсов, второй информационный вход которого подключен к первому выходу фор- мирователя адреса записи координаты Y, второй информационный вход которого является вторым информационным входом устройства, третьим информационным входом которого является второй ин- фбрмационньй вход формирователя адреса записи координаты X, третий выход которого соединен с вторым информационным входом второго коммутатора, первым управляющим входом первого распределителя импульсов, второй управляющий вход которого и первый управляющий вход второго коммутатора подключены к второму выходу формирователя адреса записи координаты t, третий выход которого соединен с третьим информационным входом второго коммутатора, первый, второй, третий и четвертый выходы которого подключены соответственно к четвертым адресным входам первого, второго, третьего и четвертого блоков оперативной памяти, информационный вход второго распределителя импульсов соединен с четвертым выходом формирователя адреса за- писи координаты X.

1

JL

А

1

Д.

А

Т Т

Фиг А

| Патент США Р 4128838, кл | |||

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чугунный экономайзер с вертикально-расположенными трубами с поперечными ребрами | 1911 |

|

SU1978A1 |

| СПОСОБ ПРЕДВАРИТЕЛЬНОЙ ОБРАБОТКИ ЦЕЛЫХ ГРОЗДЕЙ ВИНОГРАДА | 1993 |

|

RU2073988C1 |

| Приспособление для изготовления в грунте бетонных свай с употреблением обсадных труб | 1915 |

|

SU1981A1 |

Авторы

Даты

1988-10-23—Публикация

1986-12-15—Подача