Изобретение относится к вычислительной технике и может использоваться для обработки информации в caмoнacтpaивг ющиxcя системах для обработки информации перцептронного типа.

Цель изобретения - повышение точности и расширение функциональных возможностей путем использования информации о приближенной модели объекта.

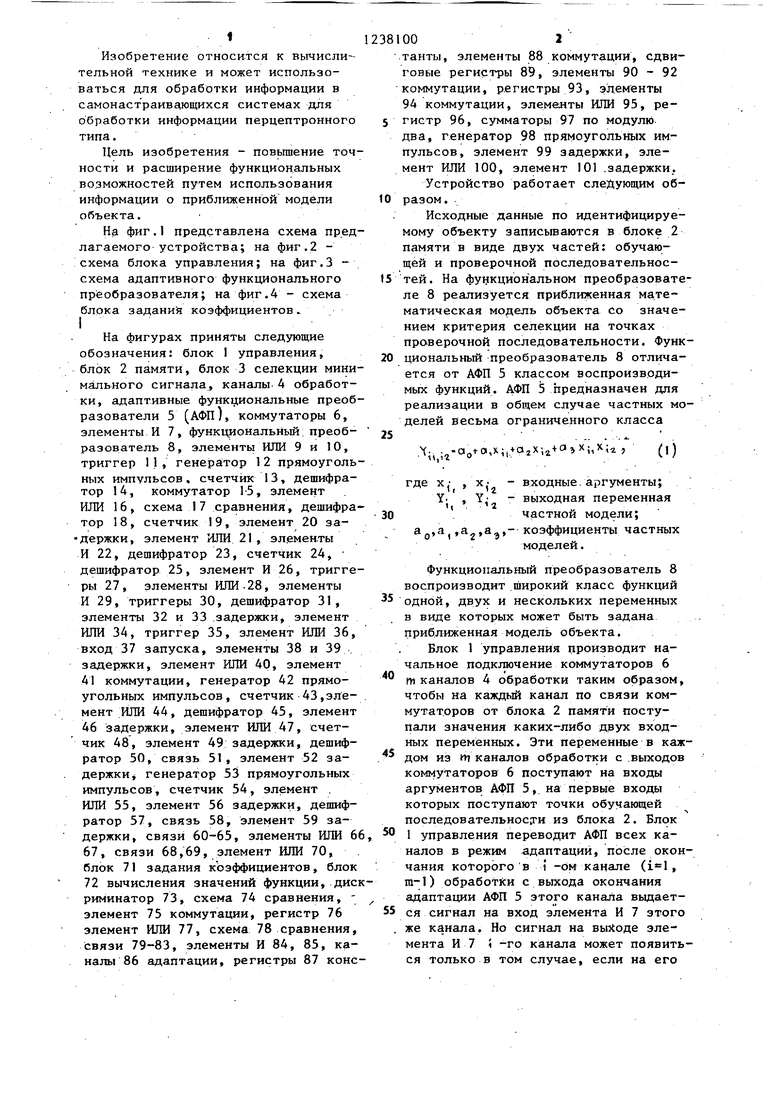

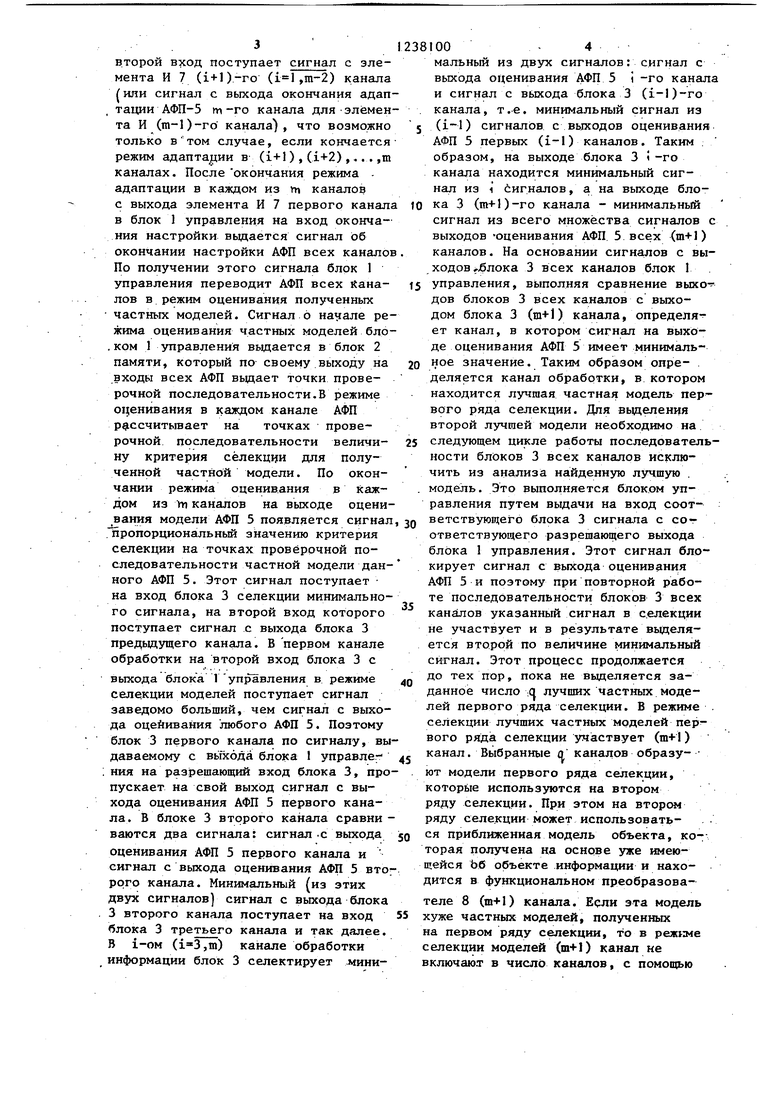

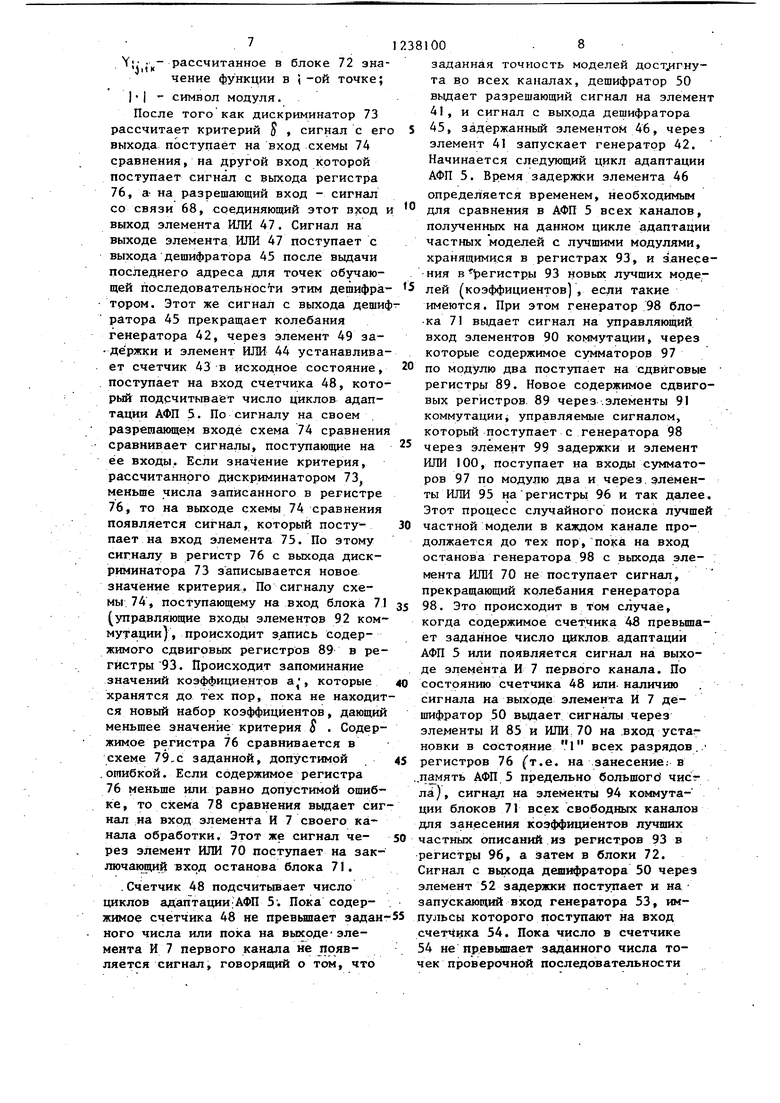

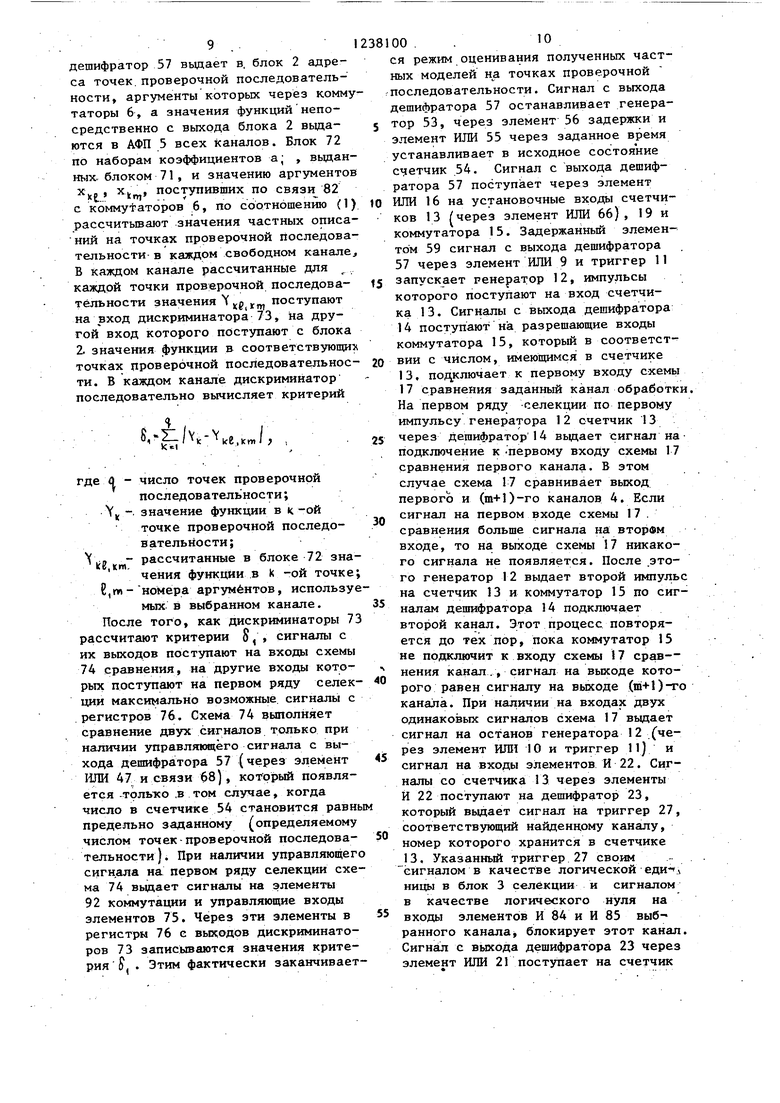

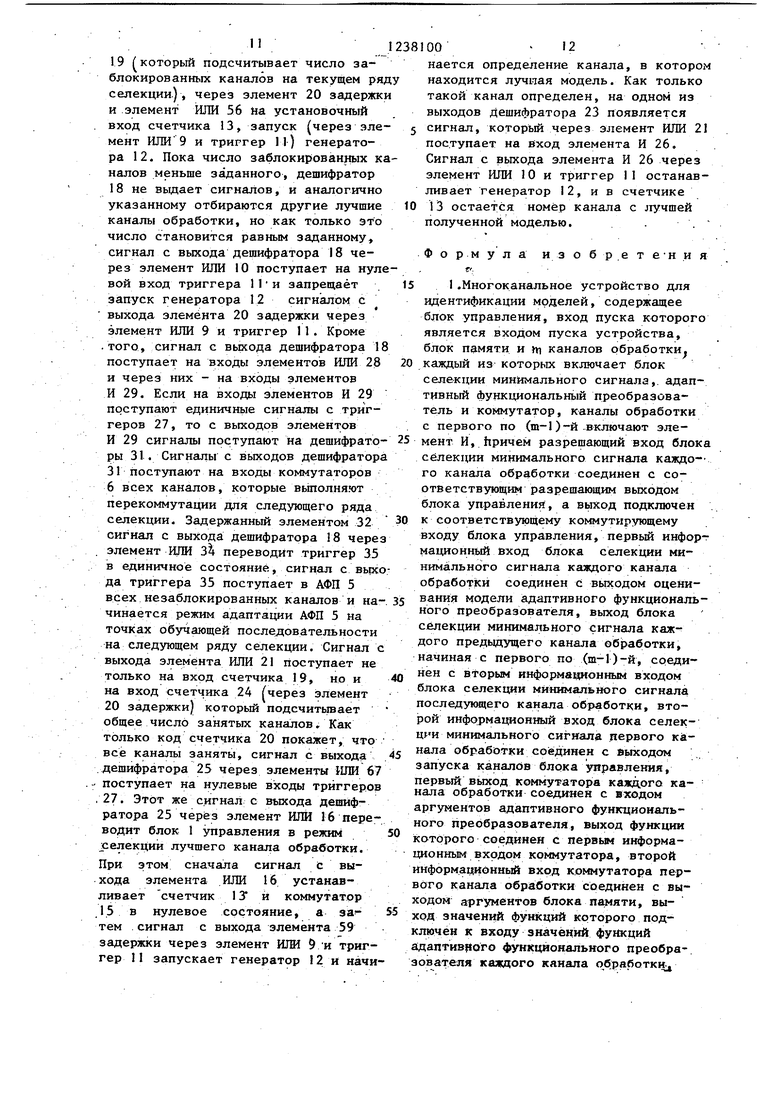

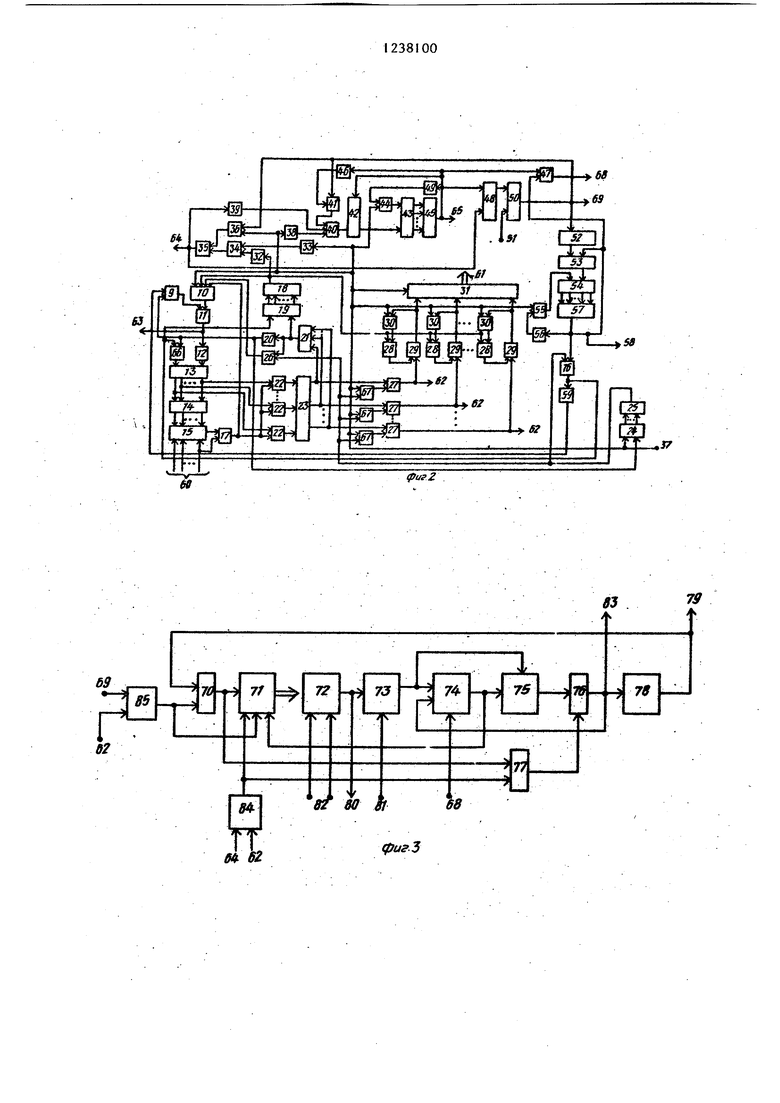

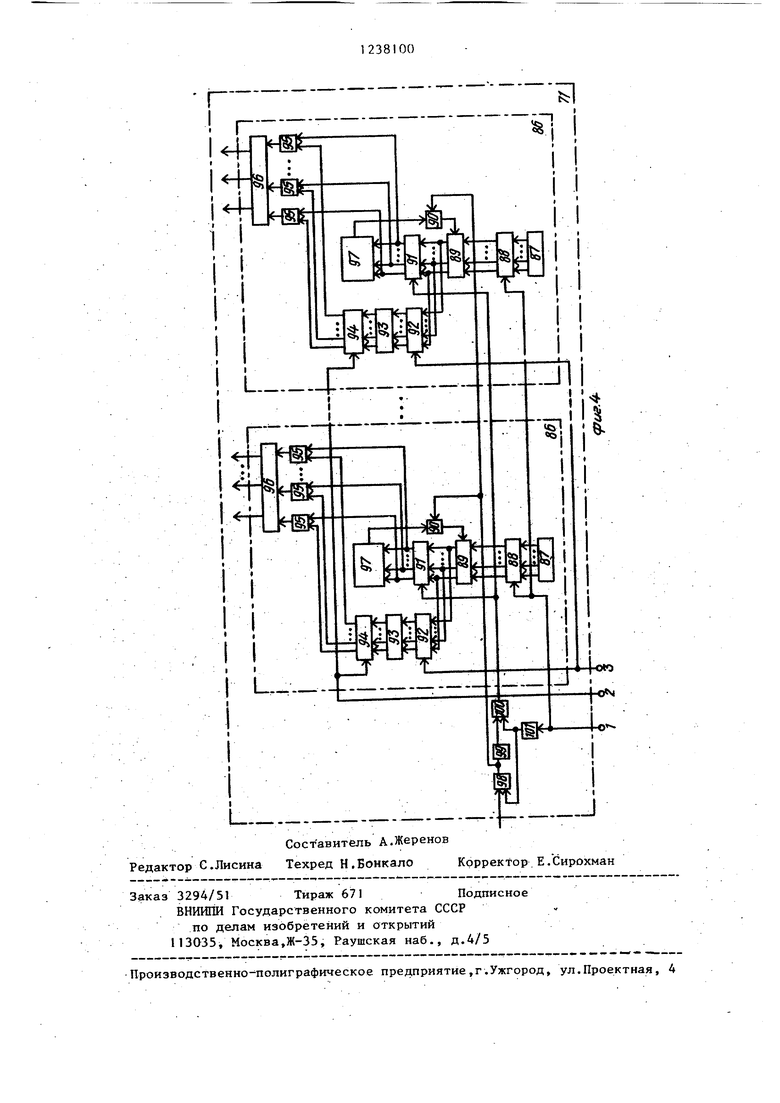

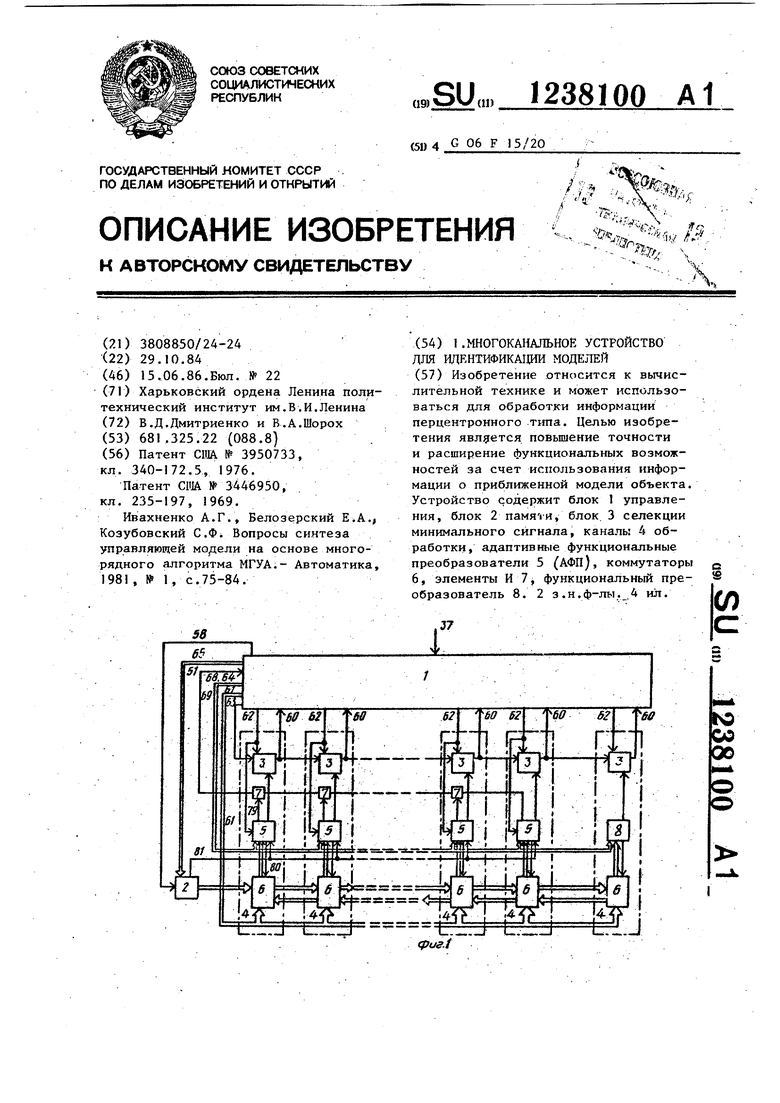

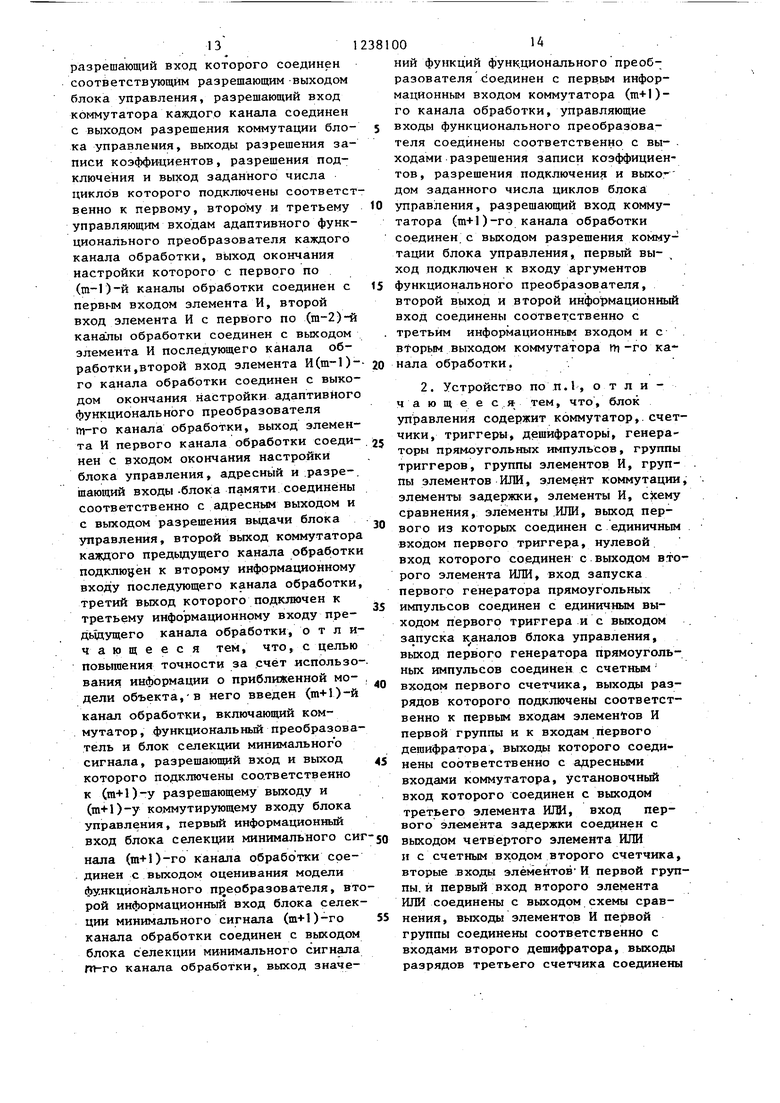

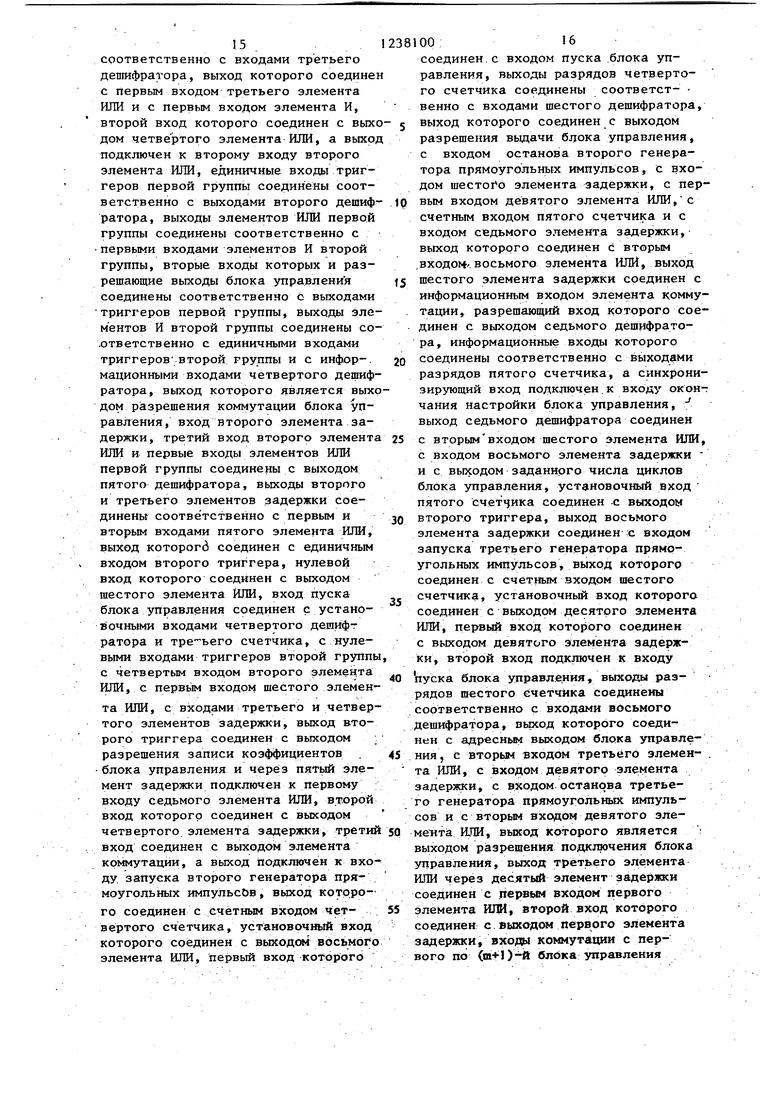

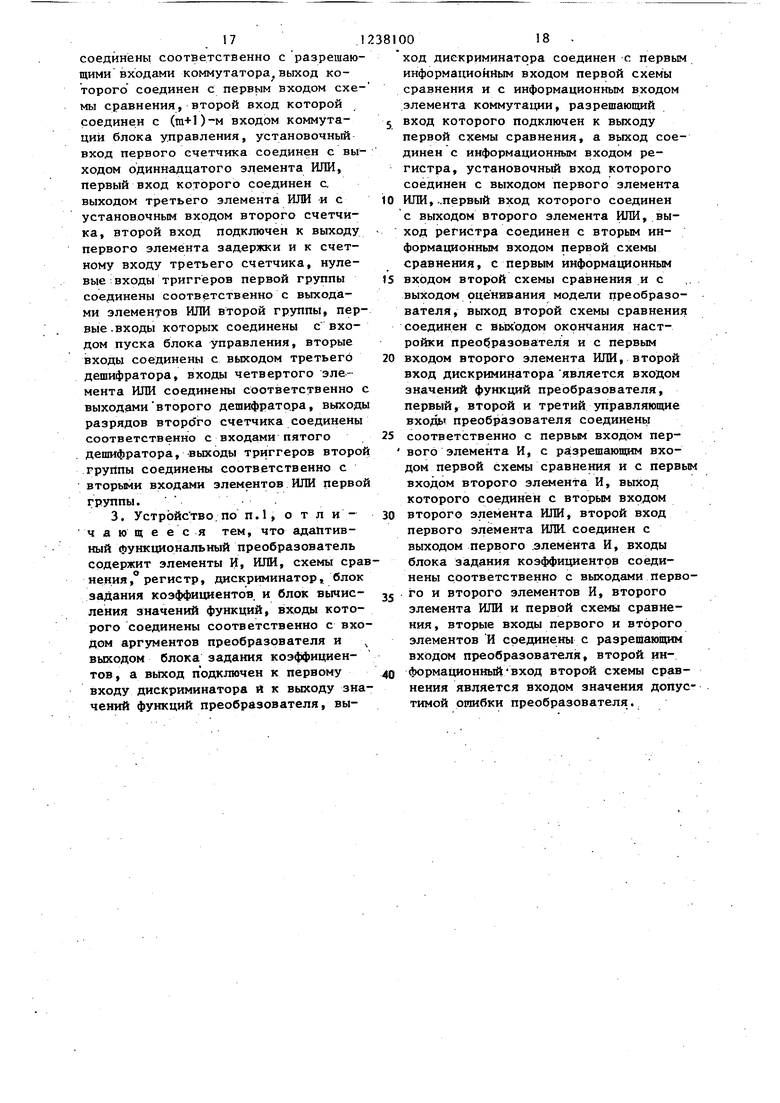

На фиг.1 представлена схема предлагаемого устройства; на фиг.2 - схема блока управления; на фиг.З - схема адаптивного функционального преобразователя; на фиг.4 - схема блока заданий коэффициентов.

I

На фигурах приняты следующие

обозначения: блок 1 управления, блок 2 памяти, блок 3 селекции минимального сигнала, каналы-4 обработки, адаптивные функциональные преобразователи 5 (АФП), коммутаторы 6, элементы И 7, функциональный; преобразователь 8, элементы ИЛИ 9 и 10,

ок L памяти, олок j селекции мини льного сигнала, каналы- 4 обработ- ;, адаптивные функциональные преобзователи 5 ГАФП). коммутаторы 6,

ЛЬНЫЙ: преобразователь о, элементы ИЛИ 9 И 10,

Триггер 1 1 , генера;тор 1 2 прямоугольных импульсов. счетчик I3, дешифратор 14, коммутатор 1-5, элемент ИЛИ 16, схема 17 сравнения, дешифратор 18, счетчик 19, элемент 20 задержки, элемент ИЛИ 21, элементы И 22, дешифратор 23, счетчик 24, дешифратор 25, элемент И 26, триггеры 27, элементы ИЛИ-28, элементы И 29, триггеры 30, дешифратор 31, элементы 32 и 33 .задержки, элемент ИЛИ 34, триггер 35, элемент ШШ 36, вход 37 запуска, элементы 38 и 39 задержки, элемент ИЛИ 40, элемент 41 коммутации, генератор 42 прямоугольных импульсов, счетчик 43,эле- мент ИЛИ 44, дешифратор 45, элемент 46 задержки, элемент ИЛИ 47, счетчик 48, элемент 49 задержки, дешифратор 50, связь 51, элемент 52 задержки, генератор 53 прямоугольных импульсов, счетчик 54, элемент . ИЛИ 55, элемент 56 задержки, дешифратор 57, связь 58, элемент 59 задержки, связи 60-65, элементы ИЛИ 6 67, связи 68,69, элемент ИЛИ 70, блок 71 задания коэффициентов, блок 72 вычисления значений функции, дисриминатор 73, схема 74 сравнения, элемент 75 коммутации, регистр 76 элемент ИЛИ 77, схема 78 сравнения, связи 79-83, элементы И 84, 85, каналы 86 адаптации, регистры 87 конс

002

танты, элементы 88 коммутации, сдвиговые регистры 89, элементы 90 - 92 коммутации, регистры 93, элементы 94 коммутации, элемеяты ИЛИ 95, регистр 96, сумматоры 97 по модулю два, генератор 98 прямоугольных импульсов, элемент 99 задержки, элемент ИЛИ 100, элемент 101 .задержки.

Устройство работает следующим образом.

Исходные данные по идентифицируемому объекту записываются в блоке 2 памяти в виде двух частей: обучающей и проверочной последовательностей. На функцион альном преобразователе 8 реализуется приближенная математическая модель объекта со значением критерия селекции на точках проверочной последовательности. Функциональный преобразователь 8 отличается от АФП 5 классом воспроизводимых функций. АФП 5 предназначен для реализации в общем случае частных моделей весьма ограниченного класса

.4;,; -aota,xii.+c3jX;5, + a,x,x;i , (l)

0

5

0

5

5

где х- , Y, ,

X,- - входные, аргументы; Y, - выходная переменная

частной модели; а.а,а2,а,- коэффициенты частных моделей.

Функциональный преобразователь 8 воспроизводит .широкий класс функций одной, двух и нескольких переменных в виде которых может быть задана приближенная модель объекта.

Блок 1 управления производит начальное подключение коммутаторов 6 m каналов 4 обработки таким образом, чтобы на каждьй канал по связи коммутаторов от блока 2 памяти поступали значения каких-либо двух входных переменных. Эти переменные в каждом из m каналов обработки с выходов коммутаторов 6 поступают на входы аргументов АФП 5, на первые входы которых поступают точки обучающей последовательности из блока 2. Блок 1 управления переводит АФП всех каналов в режим адаптации, после окончания которого в 1 -ом канале (, т-1) обработки с выхода окончания адаптации АФП 5 этого канала выдается сигнал на вход элемента И 7 этого же канала. Но сигнал на вы}4оде элемента И 7 5 -го канала может появиться только в том случае, если на его

3 1238100 - 4 второй вход поступает сигнал с эле- мальный из двух сигналов: сигнал с

мента И 7 (i+l)-ro (,m-2) канала (или сигнал с выхода окончания адаптации АФП-З m-го канала для элемента И (tn-l)-ro канала), что возможно только случае, если кончается- режим адаптации в (i+1),(i+2),,..,m каналах. После окончания режима - адаптации в каждом из m каналов

выхода оценивания АФП 5 i -го канала и сигнал с выхода блока 3 (i-l)-ro канала, т.е. минимальный сигнал из 5 (i-1) сигналов с выходов оценивания АФП 5 первых (i-1) каналов. Таким образом, на выходе блока 3 1-го канала находится минимальный сигнал из 1 Сигналов, а на выходе бло- с выхода элемента И 7 первого канала 10 ка 3 (т+1)-го канала - минимальный в блок 1 управления на вход оконча- сигнал из всего множества сигналов с ния настройки выдается сигнал об выходов -оценивания АФП 5 всех (т+1) окончании настройки АФП всех каналов. каналов. На основании сигналов с вы- По получении этого сигнала блок 1 ходов,йлока 3 всех каналов блок 1 управления переводит АФП всех кана- 15 управления, выполняя сравнение выхоДОН блоков 3 всех каналов с выходом блока 3 (т+1) канала, определяет канал, в котором сигнал на выходе оценивания АФП 5 имеет минимальлов в режим оценивания полученных частных моделей. Сигнал о начале режима оценивания частных моделей бло- ,ком 1 управления выдается в блок 2

памяти, который по своему выходу на 20 f° значение. Таким образом опревходы всех АФП вьщает точки проверочной последовательности.В режиме оценивания в каждом канале АФП рассчитывает на точках проверочной последовательности величи- 25 следующем цикле работы последовательности блоков 3 всех каналов исключить из анализа найденную лучшую . модель. Это выполняется блоком управления путем выдачи на вход соот35

40

ну критерия селекции для полученной частной модели. По окончании режима оценив.ания в каждом из Ун каналов на выходе оцени ания модели АФП 5 появляется сигнал, зо ветствующего блока 3 сигна,па с со- . пропорциональный значению критерия ответствующего разрешающего выхода селекции на точках проверочной последовательности частной модели дан- ного АФП 5. Этот сигнал поступает на вход блока 3 селекции минимального сигнала, на второй вход которого поступает сигнал с выхода блока 3 предьиущего канала. В первом канале обработки на второй вход блока 3 с

выхода блока Г управления в режиме селекции моделей поступает сигнал заведомо больший, чем сигнал с выхода оцейивания любого АФП 5. Поэтому блок 3 первого канала по сигналу, выдаваемому с выхода блока 1 управле- 45 Выбранные ( каналов образу : ния на разрешающий вход блока 3, про- ют модели первого ряда селекции, пускает на свой выход сигнал с выхода оценивания АФП 5 первого канала. В блоке 3 второго канала сравниваются два сигнала: сигнал .с выхода 50 приближенная модель объекта, ко- оценивания АФП 5 первого канала и торая получена на основе уже имею- сигнал с выхода оценивания АФП 5 второго канала. Минимальный (из этих двух сигналов сигнал с выхода блока

3 второго канала поступает на вход 55 хуже частных моделей, полученных блока 3 третьего канала и так далее. на первом ряду селекции, то в В i-OM ( ,in) канапе обработки информации блок 3 селектирует миниблОка 1 управления. Этот сигнал блокирует сигнал с выхода оценивания АФП 5 и поэтому при повторной работе последовательности блоков 3 всех каналов указанный сигнал в с.елекции не участвует и в результате выделяется второй по величине минимальный сигнал. Этот процесс продолжается до тех пор, пока не выделяется заданное число а лучших частных моделей первого ряда селекции. В режиме селекции лучших частных моделей первого ряда селекции участвует (т+1)

которые используются на втором ряду селекции. При этом на втором ряду селекции может использоватьщейся Ъб объекте информахщи и находится в функциональном преобразователе 8 (m+l) канала. Если эта модель

селекции моделей (т+1) канал не включают в число каналов, с помощью

деляется канал обработки, в котором находится лучшая частная модель первого ряда селекции. Для выделения второй лучшей модели необходимо на

ности блоков 3 всех каналов исключить из анализа найденную лучшую . модель. Это выполняется блоком управления путем выдачи на вход соот

ветствующего блока 3 сигна,па с со- ответствующего разрешающего выхода

Выбранные ( каналов образу ют модели первого ряда селекции, приближенная модель объекта, ко- торая получена на основе уже имею-

блОка 1 управления. Этот сигнал блокирует сигнал с выхода оценивания АФП 5 и поэтому при повторной работе последовательности блоков 3 всех каналов указанный сигнал в с.елекции не участвует и в результате выделяется второй по величине минимальный сигнал. Этот процесс продолжается до тех пор, пока не выделяется заданное число а лучших частных моделей первого ряда селекции. В режиме . селекции лучших частных моделей первого ряда селекции участвует (т+1)

Выбранные ( каналов образуют модели первого ряда селекции, приближенная модель объекта, к торая получена на основе уже имею-

которые используются на втором ряду селекции. При этом на втором ряду селекции может использовать Выбранные ( каналов образу ют модели первого ряда селекции, приближенная модель объекта, ко- торая получена на основе уже имею-

хуже частных моделей, полученных на первом ряду селекции, то в

щейся Ъб объекте информахщи и находится в функциональном преобразователе 8 (m+l) канала. Если эта модель

хуже частных моделей, полученных на первом ряду селекции, то в

селекции моделей (т+1) канал не включают в число каналов, с помощью

51

которых образуются модели второго ряда селекции. Если приближенная модель объекта превосходит по точнрсти модели первого ряда селекции, то на втором и последующих рядах селекции получаются модели более точные.

Отобранные блоком 1 управления X каналы и (та+1)-й канал (если он не вошел в число лучших) считаются занятыми и в дальнейшем используют- ся для хранения частных моделей первого ряда селек1р1и. Остальные каналы освобождаются (в дальнейшем они Используются для получения моделей второго ряда селекции). По заверше- НИИ этого режима блок 1 управления выдает управляющие сиг-налы на коммутаторы 6 всех свободных каналов обработки и осуществляется соединение пар выходов каналов первого ряда со входами свободных каналов. После этого все свободные каналы опять переходят в режим адаптации, после него - в режим оценивания, затем - селекция частных моделей второго ряда и так далее. Этот цикл повторяется до тех пор, пока на очередном ряду не остается больше свободных каналов. Канал с минимал1 ным значением критерия селекции и содержит выход модели объекта.

Работа устройства начинается с выдачи сигнала Пуск на вход 37 запуска. По этому сигналу производится установка в исходное состояние триггеров 11.,27,30,35, счетчико 24,43,54, дешифратора 31, и через элемент 39 задержки и элемент ИЛИ 4 запускается генератор 42, импульсы которого поступают на счетчик 43, выход которого соединен с дешифратором 45, определяющим адреса точек . обучающей последовательности в блок 2 памяти. АФП 5 приводится в рабочее состояние сигналом с выхода триггера 35 по связи 64, который появляется на выходе триггера 35 при приходе на его единичный вход сигнала Пуск с входа 37 (через элемент 32 задержки и элемент ИЛИ 34). Этот сигнал приходит на вход элемента

, И 84, на второй вход которого в . каждом канале 4 приходит сигнал с

выхода соответствующего триггера 27 который выдает разрешающий сигнал на элемент И 84 только в том случае когда канал 4 свободен, т.е.соответствующий триггер 27 находится в

j

0 5 0 5 0

,.

5

00 . 6

нулевом состоянии. По сигналу с выхода тригге5 а 35 в каждом АФП 5 в регистры 76 через элементы И 84 и ИЛИ 77 заносится максимально воз ножное число, а в блоках 71 задаются начальные значения коэффициентов а;(,1,2,3) выражения (l). Задание начальных значений коэффициентов выполняется по сигналу на связи 64 (через элемент И 84) , поступающему на управляющие входы элементов 88 ког утации всех каналов 86 адаптации. По этому сигналу содержимое регистров 87, в которьтх хра.нит- ся набор начальных значений коэффициентов а;, передается в сдвиговые регистры 89. Задержанный сигнал с элемента И 84 /через элемент 101 задержки и элемент ШШ 100) поступает на управляющие входы элементов 91 коммутации, через которые происходит передача в каждом канале 86 адаптации содержимого сдвиговых ре- гистров 89 на входы сумматоров 97 по модулю два и через элементы ИЛИ 95 в регистры 96, содержимое которых затем передается в блок 72.Сигнал с выхода элемента 101 задержки пос-; тупает и на запускающий .вход генератора 98, период колебаний. Которого подобран таким образом, чтобы за время между двумя соседними импульсами в АФП 5 можно было оценить полученный в блоке 71 набор коэффициентов .

По сигналам дешифратора 45 блок 2 через коммутаторы 6 выдает в АФП 5 всех каналов -обработки аргументы точек обучакидей последовательности, которые поступают по связи 82 на входы аргументов блока 72. В каждом канале блок 72 по значениям коэффициентов а и аргументов X,; , X по соотношению (1) рассчитьшает значение V;; , 1 .выходной переменной частной модели в i -ой точке. Рассчитанное значение Y,-; , i поступает на вход дискриминатора 73, последовательно вычисляющего критерий У

S |.,;Klr

г - число точек обучающей последовательности;

V;- значение функции в -ой точке обучающей последовательности;

Ч;.- рассчитанное в блоке 72 значение функции в i-ой точке; 1 | символ модуля. После того как дискриминатор 73 рассчитает критерий J , сигнал с его выхода поступает на вход схемы 74 сравнения, на другой вход Которой поступает сигнал с выхода регистра 76, а на разрешающий вход - сигнал со связи 68, соединяющий этот вход и выход элемента ИЛИ 47. Сигнал на выходе элемента ИЛИ 47 поступает с выхода дешифратора 45 после выдачи последнего адреса для точек обучаю10

заданная точность моделей та во всех каналах, дешифратор 5 выдает разрешающий сигнал на эле 41, и сигнал с выхода дешифратор 45, задержанный элементом 46, че элемент 41 запускает генератор 4 Начинается следующий цикл адаптац АФП 5. Время задержки элемента 46 определяется временем, необходимь для сравнения в АФП 5 всех канало полученных на данном цикле адапта частных моделей с лучшими модулям хранящимися в регистрах 93, и з.ан ния в-регистры 93 новых лучших мо

щей последовательности этим дешифра- 5 лей /коэффициентов, если такие

20

25

30

тором. Этот же сигнал с вьпсода дешифратора 45 прекращает колебания генератора 42, через элемент 49 за дёржки и элемент ИЛИ 44 устанавливает счетчик 43 в исходное состояние, поступает на вход счетчика 48, который подсчитывает число циклов адаптации АФП 5. По сигналу на своем . разрешающем входе схема 74 сравнения сравнивает сигналы, поступающие на ее входы. Если значение критерия, рассчитанного дискриминатором 73, меньше числа записанного в регистре 76, то на выходе схемы 74 сравнения появляется сигнал, который поступает на вход элемента 75. По этому сигналу в регистр 76 с выхода дискриминатора 73 записывается новое значение критерия. По сигналу схемы 74, поступающему на вход блока 71 35 управляющие входы элементов 92 ком- мута.ции), происходит запись содержимого сдвиговых регистров 89 в регистры 93. Происходит запоминание значений коэффициентов , которые хранятся до тех пор, пока не находится новый набор коэффициентов, дающий меньшее значение критерия S . Содержимое регистра 76 сравнивается в схеме 79,с заданной, допустимой

.ошибкой. Если содержимое регистра 76 меньше или равно допустимой ошибке, то схема 78 сравнения вьвдает сигнал на вход элемента И 7 своего канала обработки. Этот же сигнал через элемент ИЛИ 70 поступает на заключающий вход останова блока 71.

.Счетчик 48 подсчитывает число циклов адаптации;АФП 5; Пока содеримеются. При этом генератор 98 бл ка 71 выдает сигнал на управляющи вход элементов 90 коммутации, чер которые содержимое сумматоров 97 по модулю два поступает на сдвиго регистры 89. Новое содержимое сдв вых регистров 89 через .элементы 9 коммутацииj управляемые сигналом, который поступает с генератора 98 через элемент 99 задержки и элеме ИЛИ 100, поступает на входы сумма ров 97 по модулю два и через.элем ты ИЛИ 95 на регистры 96 и так дал Этот процесс случайного поиска лу частной модели в каждом канале пр должается до тех пор, пока на вхо останова генератора 98 с выхода эл мента HJDi 70 не поступает сигнал, прекращающий колебания генератора 98. Это происходит в том случае, когда содержимое счетчика 48 превь ет заданное число циклов адаптации АФП 5 или появляется сигнал на вых де элемента И 7 первого канала. По состоянию счетчика 48 или- наличию сигнала на выходе элемента И 7 дешифратор 50 вьщает сигналы через элементы И 85 и ИЛИ,70 на вход уст новки в состояние 1 всех разрядо 45 регистров 76 (т.е. на занесение; в ..память АФП 5 предельно большого чи ли), сигнгут на элементы 94 коммута ции блоков 71 всех свободных канал для занесения коэффициентов лучших частных описаний из регистров 93 в регистры 96, а затем в блоки 72. Сигнал с вьрсода дешифратора 50 чер элемент 52 задержки поступает и на запускающий вход генератора 53, им

40

50

счетчика 48 не превьшает задан-55 пульсы которого поступают на вход

ного числа или пока на выходе-элемента И 7 первого канала не появляется сигнал, говорящий о том, что

заданная точность моделей дост 1гну- та во всех каналах, дешифратор 50 выдает разрешающий сигнал на элемент 41, и сигнал с выхода дешифратора 45, задержанный элементом 46, через элемент 41 запускает генератор 42. Начинается следующий цикл адаптации АФП 5. Время задержки элемента 46 определяется временем, необходимьи для сравнения в АФП 5 всех каналов, полученных на данном цикле адаптации частных моделей с лучшими модулями, хранящимися в регистрах 93, и з.анесе- ния в-регистры 93 новых лучших моде20

25

30

5

имеются. При этом генератор 98 бло- ка 71 выдает сигнал на управляющий вход элементов 90 коммутации, через которые содержимое сумматоров 97 по модулю два поступает на сдвиговые регистры 89. Новое содержимое сдвиговых регистров 89 через .элементы 91 коммутацииj управляемые сигналом, который поступает с генератора 98 через элемент 99 задержки и элемент ИЛИ 100, поступает на входы сумматоров 97 по модулю два и через.элементы ИЛИ 95 на регистры 96 и так далее. Этот процесс случайного поиска лучшей частной модели в каждом канале продолжается до тех пор, пока на вход останова генератора 98 с выхода элемента HJDi 70 не поступает сигнал, прекращающий колебания генератора 98. Это происходит в том случае, когда содержимое счетчика 48 превьш1а- ет заданное число циклов адаптации АФП 5 или появляется сигнал на выходе элемента И 7 первого канала. По состоянию счетчика 48 или- наличию сигнала на выходе элемента И 7 дешифратор 50 вьщает сигналы через элементы И 85 и ИЛИ,70 на вход установки в состояние 1 всех разрядов.. 5 регистров 76 (т.е. на занесение; в ..память АФП 5 предельно большого чис ли), сигнгут на элементы 94 коммута- ции блоков 71 всех свободных каналов для занесения коэффициентов лучших частных описаний из регистров 93 в регистры 96, а затем в блоки 72. Сигнал с вьрсода дешифратора 50 через элемент 52 задержки поступает и на запускающий вход генератора 53, им0

0

счетчика 54. Пока число в счетчике 54 не превышает заданного числа точек проверочной последовательности

ся режим оценивания полученных частных моделей на точках проверочной ;последовательности. Сигнал с выхода дешифратора 57 останавливает генера- 5 тор 53, через элемент 56 задержки и элемент ИЛИ 55 через заданное время устанавливает в исходное состояние с етчак 54. Сигнал с выхода дешифратора 57 поступает через элемент

дешифратор 57 выдает в, блок 2 адреса точек, проверочной последовательности, аргументы которых через коммутаторы 6, а значения функций непосредственно с выхода блока 2 вьща- ются в АФП 5 всех каналов. Блок 72 по наборам коэффициентов а; , выданных, блоком 71, и значению аргументов , Х|(, поступивших по связи 82

с коммутаторов 6, по соотношению (1) 10 ИЛИ 16 на установочные входы счетчи- рассчитьшают значения частных описа- ков 13 (через элемент ИЛИ 66), 19 и НИИ на точках проверочной последова- коммутатора 15. Задержанный элемен- тельности в каждом свободном канале, том 59 сигнал с выхода дешифратора В каждом канапе рассчитанные для 57 через элемент ШШ 9 и триггер 11 каждой точки проверочной последова- 15 запускает генератор 12, импульсы

которого поступают на вход счетчика 13. Сигналы с выхода дешифратора 14 поступают на разрешающие входы коммутатора 15, который в соответстТёльности значения Ч g jf поступают на вход дискриминатора 73, на другой вход которого поступают с блока 2. значения функции в соответствующих

точках проверочной последовательное- 20 вии с числом, имеющимся в счетчике

ти. В каждом канале дискриминатор последовательно вычисляет критерий

8,.|./У,-Ч,е.,„/, ,

где о - число точек проверочной

последовательности; УК -, значение функции в tt-ой

точке проверочной последовательности;

X i;i - рассчитанные в блоке 72 зна- sbiKm.,

чения функции в k -ой точке;

Е,пч- номера аргументов, используемых в выбранном канале.

После того, как дискриминаторы 73 рассчитают критерии 8, , сигналы с их выходов поступают на входы схемы 74 сравнения, на другие входы крто- рых поступают на первом ряду селек- ции максимально возможные сигналы с регистров 76. Схема 74 выполняет сравнение двух сигналов только при наличии управлякадёго сигнала с выхода дешифра тора 57 (через элемент ИЛИ 47 и связи 68), который появляется -тольхо ,в том случае, когда число в счетчике 54 становится равны предельно заданному (определяемому числом точек-проверочной последовательности). При наличии управляющего сигнала на первом ряду селекции схема 74 выдает сигналы на элементы 92 коммутации и управляющие входы элементов 75. Через эти элементы в регистры 76 с выходов дискриминаторов 73 записываются значения критерия S . Этим фактически заканчивает

ся режим оценивания полученных частных моделей на точках проверочной ;последовательности. Сигнал с выхода дешифратора 57 останавливает генера- 5 тор 53, через элемент 56 задержки и элемент ИЛИ 55 через заданное время устанавливает в исходное состояние с етчак 54. Сигнал с выхода дешифратора 57 поступает через элемент

0

5

0

13. пo ycлючaeт к первому входу схемы 17 сравнения заданный канал обработки. На первом ряду селекции по первому импульсу генератора 12 счетчик 13 5 через Дешифратор 14 вьвдает сигнал на подключение к -первому входу схемы 17 сравнения первого канала. В этом случае схема 17 сравнивает выход первого и (т+1)-го каналов 4. Если сигнал на первом входе схемы 17 . сравнения больше сигнала на вторфм входе, то на выходе схемы 17 никакого сигнала не появляется. После этого генератор 12 выдает второй импульс на счетчик 13 и коммутатор 15 по сигналам дешифратора 14 подключает второй канал. Этот процесс повторяется до тех пор, пока коммутатор 15 не подключит к входу схемы 17 срав- нения канал., сигнал на выходе которого равен сигналу на выходе (in+l)-ro канала. При наличии на входах двух одинаковых сигналов схема 17 выдает сигнал на останов генератора 12 .(че- рез элемент ИЛИ 10 и триггер И) и сигнал на входы элементов И 22. Сигналы со счетчика 13 через элементы И 22 поступают на дешифратор 23, который выдает сигнал на триггер 27, соответствующий найденному каналу, номер которого хранится в счетчике

13. Указанный триггер 27 своим сигналом в качестве логической ницы в блок 3 селекции и сигналом в качестве логического нуля на 5 входы элементов И 84 и И 85 выбранного каналаj блокирует этот канал. Сигнал с выхода дешифратора 23 через элемент ИЛИ 21 поступает на счетчик

0

25

19/KOTOpbrti подсчитывает число заблокированных каналов на текущем ряду селекции.), через элемент 20 задержки и элемент ИЛИ 56 на установочный вход счетчика 13, запуск (через элемент ИЛИ 9 и триггер 1|) генератора 12. Пока число заблокированных каналов меньше заданного, дешифратор

18 не вьщает сигналов, и аналогично указанному отбираются другие лучшие каналы обработки, но как только это число становится равным заданному, сигнал с выхода дешифратора I8 через элемент ИЛИ 10 поступает на нулевой вход триггера 1Ги запрещает запуск генератора 12 сигналом с

выхода элемента 20 задержки через элемент ИЛИ 9 и триггер 11. Кроме

.того, сигнал с вькода дешифратора 18 поступает на входы элементов ИЛИ 28 и через них - на входы элементов И 29. Если на входы элементов И 29 поступают единичные сигналы с триггеров 27, то с выходов элементов И 29 сигналы поступают на дешифраторы 31.Сигналы с выходов дешифратора 31 поступают на входы коммутаторов 6 всех каналов, которые вьшолняют перекоммутации для следующего ряда селекции. Задержанный элементом 32 сигнал с выхода дешифратора 18 через

элемент ИЛИ 3 переводит триггер 35 в единичное состояние, сигнал с вьрсо- да триггера 35 поступает в АФП 5 всех незаблокированных каналов и на- 35 чинается режим адаптации АФП 5 на точках обучающей последовательности на следующем ряду селекции. Сигнал с выхода элемента ИЛИ 21 поступает не только на вход счетчика 19, ной на вход счетчика 24 через элемент

20задержки) который подсчитьгоает общее число занятых каналов. Как только код счетчика 20 покажет, что все каналы заняты, сигнал с выхода дешифратора 25 через элементы ИЛИ 67

поступает на нулевые входы триггеров 27. Этот же сигнал с выхода дешифратора 25 через элемент ИЛИ 16 переводит блок 1 управления в режим селекции лучшего канала обработки. При этом сначала сигнал с выхода элемента .ИЛИ 16 устанавливает счетчик 13 и коммутатор 15 в нулевое состояние, а зн - тем сигнал с выхода элемента 59 задержки через элемент ШШ 9 и триггер П запускает генератор 12 и начи30

40

45

50

55

нается определение канала, в котором находится лучшая модель. Как только такой канал определен, на одном из выходов дешифратора 23 появляется сигнал, который через элемент ИЛИ 21 поступает на вход элемента И 26, Сигнал с вьпсода элемента И 26 через элемент ИЛИ 10 и триггер II останавливает генератор 12, ив счетчике 13 остается номер канала с лучшей полученной моделью. . . .

20

25

35

Ф о

из о б р .е т е -н и я

15

30

40

5

0

5

р м у л а

.

1.Многоканальное устройство для идентификации моделей, содержащее блок управления, вход пуска которого является входом пуска устройства, блок памяти и m каналов обработки каждый из которых включает блок- селекции минимального сигнала,, адаптивный функциональный преобразователь и коммутатор, каналы обработки с первого по (т-1)-и-включают элемент И, Ьричем разрешающий вход блока селекции минимального сигнала каждо- го канала обработки соединен с соответствующим разрешающим выходом блока управления, а выход подключен к соответствующему коммутирующему входу блока управления, первый инфор- мационньй вход блока селекции минимального сигнала каждого канала обработки соединен с выходом оценивания модели адаптивного функционального преобразователя, выход блока селекции минимального сигнала каж- дого предыдущего канала об1С)аботки, начиная с первого по (т-1)-й, соединен с вторьм информационным входом блока селекции мй нимального сигнала последующего канала обработки, второй информационшлй вход блока селекции минимального сигнала первого канала обработки соединен с выходом запуска каналов блока управления,

первый выход коммутатора казвд.ого канала обработки соединен с входом

аргументов адаптивного функциоиаль- ного преобразователя, выход функции которого соединен с первьм информационным входом коммутатора, второй информационньй вход коммутатора первого канала обработки соединен с выходом аргументов блока памяти, выход значений функций которого подключен к вкоду значений фугосций адаптивиого функционалыгого преобразователя кал;дого канала оДработки-.

.131

разрешающий вход которого соединен соответствующим разрешающим -выходом блока управления, разрешающий вход коммутатора каждого канала соединен с выходом разрешения коммутации бло- ка управления, выходы разрешения записи коэффициентов, разрешения подключения и выход заданного числа циклов которого подключены соответственно к первому, второму и третьему управляющим входам адаптивного функционального преобразователя каждого канала обработки, выход окончания настройки которого с первого по (т-1)-й каналы обработки соединен с первым входом элемента И, второй вход элемента И с первого по (т-2)-й каналы обработки соединен с выходом элемента И последующего канала обработки, второй вход элемента И(т-1)го канала обработки соединен с выходом окончания настройки адаптивного функционального преобразователя т-го канала обработки, выход элемента И первого канала обработки соеди- нен с входом окончания настройки блока управления, адресный и разре-. шающий входы -блока памяти соединены соответственно с адресным выходом и с выходом разрешения выдачи блока управления, второй выход коммутатора каждого предьщущего канала обработки подключен к второму информационному входу последующего канала обработки, третий выход которого подключен к третьему информационному входу предьщущего канала обработки, отличающееся тем, что, с целью повышения точности за счет использования информации о приближенной мо- дели объекта,-в него введен (т+1)-й канал обработки, включаюш;ий коммутатор, функциональный преобразователь и блок селекции минимального сигнала, разрешающий вход и выход которого подключены соответственно к ()-у разрешающему выходу и (т+1)-у коммутирующему входу блока управления, первый информационный вход блока селекции минимального сиг

нала (т+1)-го канала обработки сре- - динен с выходом оценивания модели функционального П1зеобразователя, второй информационньй вход блока селекции минимального сигнала (т+1)-го канала обработки соединен с выходом блока селекции минимального сигнала т-го канала обработки, выход значе0014.

НИИ функций функционального преобразователя соединен с первым информационным входом коммутатора (m+l)- го канала обработки, управляющие входы функционального преобразователя соединены соответственно с вы- ходами разрешения записи коэффициентов, разрешения подключения и выхо дом заданного числа циклов блока управления, разрешающий вход коммутатора (т-И)-го канала обра&отки соединен; с выходом разрешения коммутации блока управления, первый выход подключен к входу аргументов функционального преобразователя, второй выход и второй информационный вход соединены соответственно с третьим информационным входом и с вторым выходом коммутатора щ -го канала обработки.

2. Устройство по П.1, отличающее с я тем, что, блок управления содержит коммутатор,.счетчики, триггеры, дешифраторы, генераторы прямоугольных импульсов, группы триггеров, группы элементов И, группы элементов ИЛИ, элемент коммутации элементы задержки, элементы И, схему сравнения, элементы ИЛИ, выход первого из которых соединен с единичным входом первого триггера, нулевой вход которого соединен с выходом второго элемента ИЛИ, вход запуска первого генератора прямоугольных импульсов соединен с единичным выходом первого триггера и с выходом запуска к аналов блока управления, выход первого генератора прямоугольных импульсов соединен с счетным входом первого счетчика, выходы разрядов которого подключены соответственно к первым входам элементов И первой группы и к входам первого дешифратора, выходы которого соединены соответственно с адресными входами коммутатора, установочный вход которого соединен с выходом третьего элемента ШШ, вход первого элемента задержки соединен с выходом четвертого элемента ИЛИ и с счетным входом второго счетчика, вторые входы элементов И первой группы, и первый вход второго элемента ИЛИ соединены с выходом схемы сравнения, выходы элементов И первой группы соединены соответственно с входами второго дешифратора, выходы разрядов третьего счетчика соединены

1.5 .

соответственно с входами третьего дешифратора, выход которого соединен с первым входом третьего элемента ИЛИ и с первым входом элемента И, второй вход которого соединен с выхо дом четвертого элемента ИЛИ, а выход подключен к второму входу второго элемента ИЛИ, единичные входы триггеров первой группы соединены соответственно с выходами второго дешифратора, выходы элементов ИЛИ первой группы соединены соответственно с первыми входами элементов И второй группы, вторые входы которых и разрешающие выходы блока управления соединены соответственно с- выходами триггеров первой группы, выходы элементов И второй группы соединены соответственно с единичными входами триггеров второй группы и с инфор-. мационными входами четвертого дешифратора, выход которого является выходом разрешения коммутации блока управления, вход второго элемента задержки, третий вход второго элемента ИЛИ и первые входы элементов ИЛИ первой группы соединены с выходом пятого дешифратора, выходы второго и третьего элементов задержки соединены соответственно с первым и вторым входами пятого элемента ИЛИ, выход которогд соединен с единичным входом второго триггера, нулевой вход которого соединен с выходом шестого элемента ИЛИ, вход пуска блока управления соединен с установочными входами четвертого дешифт ратора и счетчика, с нулевыми входами триггеров второй группы с четвертым входом второго элемента ИЛИ, с первым входом шестого элемента ИЛИ, с входами третьего и четвертого элементов задержки, выход второго триггера соединен с выходом ; разрешения записи коэффициентов блока управления и через пятый элемент задержки подключен к первому входу седьмого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента задержки, третий вход соединен с выходом элемента коммутации, а вьпсод подключён к вхо- ду запуска второго генератора прямоугольных импульсЬв, выход которого соединен с счетным входом чет- вёртого счетчика, установочный вход которого соединен с выходом восьмого элемента ШШ, первый вход которого

It

15

20

25

5 0 5

23810016

соединен.с входом пуска .блока управления, выходы разрядов четвертого счетчика соединены соответст- венно с входами шестого дешифратора, выход которого соединен с выходом разрешения вьщачи блока управления, с входом останова второго генератора прямоугольных импульсов, С входом шестог о элемента задержки, с первым входом девятого элемента ИЛИ, с счетным входом пятого счетчика и с входом седьмого элемента задержки,- выход которого соединен с вторым ,входоЧ восьмого элемента ИЛИ, выход шестого элемента задержки соединен с информационным входом элемента коммутации, разрешающий вход которого соединен с выходом седьмого дешифратора, информационные входы которого соединены соответственно с выходами разрядов пятого счетчика, а синхронизирующий вход подключен . к входу окончания настройки блока управления, выход седьмого дешифратора соединен с вторым входом шестого элемента ИЛИ, с входом восьмого элемента задержки и с выходом заданного числа циклов блока управления, установочный вход пятого счетчика соединен с вьпсодом второго триггера, выход восьмого элемента задержки соединен с входом запуска третьего генератора прямоугольных имцульсов, выход которого соединен с счетным входом шестого счетчика, установочный вход которого соедииен с выходом десятого элемента ИЛИ, первый вход которого соединен с выходом девятого элемента задержки, второй вход подключен к входу 40 пуска блока управления, выходы разрядов шестого счетчика соединены соответственно с входами восьмого дешифратора, выход которого соединен с адресным выходом блока управления, с BTOpbw входом третьего элемен- . та ИЛИ, с 1Входом девятого элемента задержки, с входом останова третье- ; го генератора прямоугольных импульсов и с вторым входом девятого элемента ШШ, выход которого является ; выходом разрешения подключения блока управления, выход третьего элемента ИЛИ через десятый элемент задержки соединен с первом входом первого элемента ШМ, второй вход которого соединен с выход 1 первого элемента задержки, входа коммутации с первого по (m-t-1 )-й блЬка управления

30

35

5

оединены соответственно с разрешаюими входами коммутатора выход которого соединен с первым входом схе- ы сравнения, второй вход которой соединен с (га+1)-м входом коммутаций блока управления, установочный вход первого счетчика соединен с выходом одиннадцатого элемента ИЛИ, первый вход которого соединен с. выходом третьего элемента ИЛИ и с установочным входом второго счетчика, второй вход подключен к выходу - первого элемента задержки и к счетному входу третьего счетчика, нулевые входы триггеров первой группы соединены соответственно с выходами элементов ИЛИ второй группы, первые .входы которых соединены с входом пуска блока управления, вторые входы соединены с выходом третьего дешифратора, входы четвертого элемента ИЛИ соединены соответственно с выходами второго дешифратора, выходы разрядов второго счетчика соединены соответственно с входами пятого дешифратора, вькоды триггеров второй

группы соединены соответственно с вторыми входами элементов.ИЛИ первой группы, .

3. Устройс тво. по П.1, о т л и - чающееся тем, что адаптивный функциональный преобразователь содержит элементы И ИЛИ, схемы сравнения, регистр, дискриминатор, блок задания коэффициентов, и блок вычисления значений функций, входы которого соединены соответственно с входом аргументов преобразователя и выходом блока задания коэффициентов , а вь1ход подключен к первому входу дискриминатора и к выходу значений функций преобразователя, выход дискриминатора соединен с первым информационным входом первой схемы сравнения и с информационным входом элемента коммутации, разрешающий 5 вход которого подключен к выходу первой схемы сравнения, а вькод соединен с информационным входом регистра, установочный вход которого соединен с выходом первого элемента

0 ИЛИ, ..первый вход которого соединен с выходом второго элемента ИЛИ, выход регистра соединен с вторым информационным входом первой схемы сравнения, с первым информационным

5 входом второй схемы сравнения и с выходом оце:нивания модели преобразователя, выход второй схемы сравнения соединен с вькодом окончания настройки преобразователя и с первым

0 входом второго элемента ИЛИ, второй вход дискриминатора является входом значений функций преобразователя, первый, второй и третий з равляющие входы преобразователя соединены

5 соответственно с первым входом пер- вого элемента И, с разрешающим входом первой схемы сравнения и с первым входом второго элемента И, вьпсод которого соединен с вторым входом

0 второго элемента ИЛИ, второй вход первого элемента ИЛИ. соединен с выходом первого .элемента И, входы блока задания коэффициентов соединены соответственно с выходами первого и второго элементов И второго элемента ИЛИ и первой схемы сравнения , вторые входы первого и второго элементов И соединены с разрешающим входом преобразователя, второй ин0 Формационный вход второй схемы сравнения является входом значения допустимой ошибки преобразователя.

5

-IT

69

фиг 2

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для идентификации моделей | 1986 |

|

SU1300491A2 |

| Буферное запоминающее устройство | 1985 |

|

SU1297115A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Устройство для моделирования систем массового обслуживания | 1979 |

|

SU926663A1 |

| Телеметрическая система со сжатием информации | 1991 |

|

SU1837349A1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1525718A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| Устройство для передачи и приема информации | 1984 |

|

SU1185365A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

Изобретение .относится к вычислительной технике и может использоваться для обработки информации перцентронного типа. Целью изобретения является повышение точности и расширение функциональных возможностей за счет использования информации о приближенной модели объекта. Устройство содержит блок 1 управления, блок 2 памяти, блок 3 селекции минимального сигнала, каналы 4 обработки, адаптивные функциональные преобразователи 5 (АФП), коммутаторы 6, элементы И 7, функциональный преобразователь 8. 2 з.н.ф-лы. .4 ил. W C1J i2:J .j GLj (pue.i

tfJ

7S

85

- S-f 7Г

t Ж1ч/ч уi

72

Г

74

79

78

8

V

80 a08

M

(ригЗ

Г

L.-

Редактор С.Лисина

Составитель А.Жеренов

Техред Н.Бонкало Корректор Е.Сирохман

Заказ 3294/51 Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва,Ж-35, Раушская наб., д.4/5

Производственно-полиграфическое предприятие,г.Ужгород, ул.Проектная, 4

| Патент США № 3950733, кл | |||

| Способ отопления гретым воздухом | 1922 |

|

SU340A1 |

| Патент CiiJA № 3446950, кл | |||

| Упругая металлическая шина для велосипедных колес | 1921 |

|

SU235A1 |

| Ивахненко А.Г., Белозерский Е.А., Козубовский С.Ф Вопросы синтеза управляющей на основе многорядного алгоритма МГУА.- Автоматика, 1981, № 1, с.75-84. | |||

Авторы

Даты

1986-06-15—Публикация

1984-10-29—Подача