Изобретение относится к технической кибернетике, в частности к самонастраивающимся устройствам перцеп- тронного типа для обработки информации и является дополнительным к авт.св. № 1238100.

Цель изобретения - повышение точности и расширение области применения устройства путем использования большего числа свободных каналов и рядов селекции.

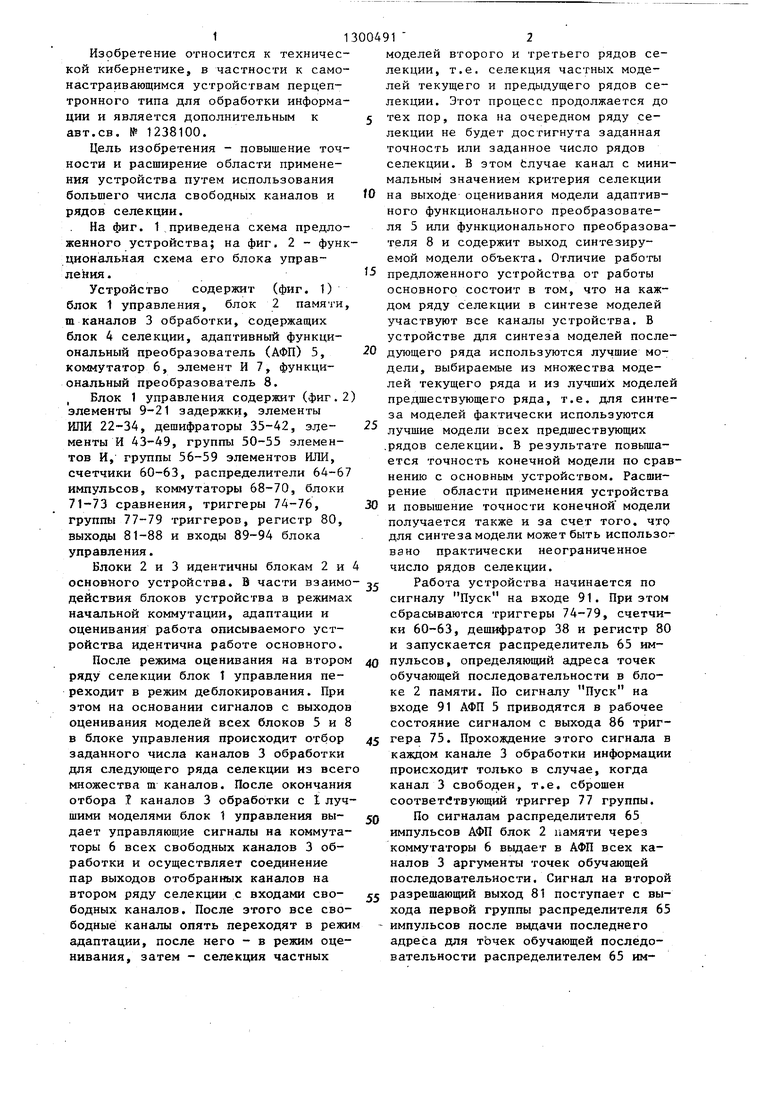

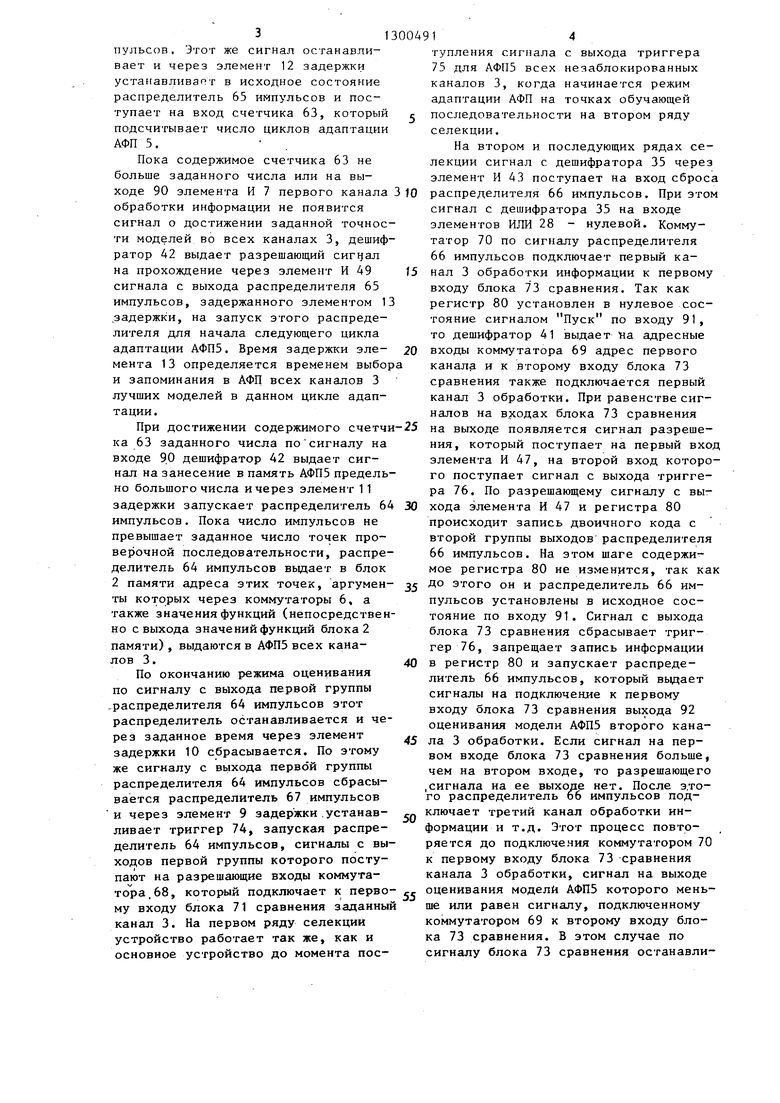

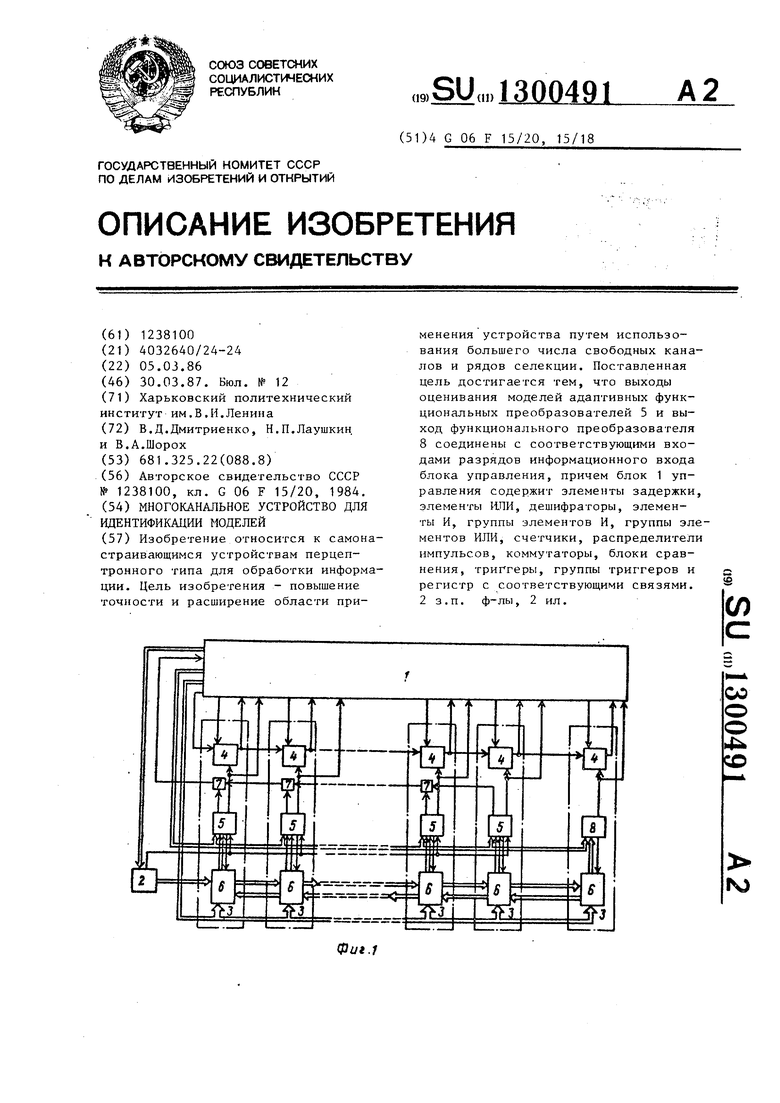

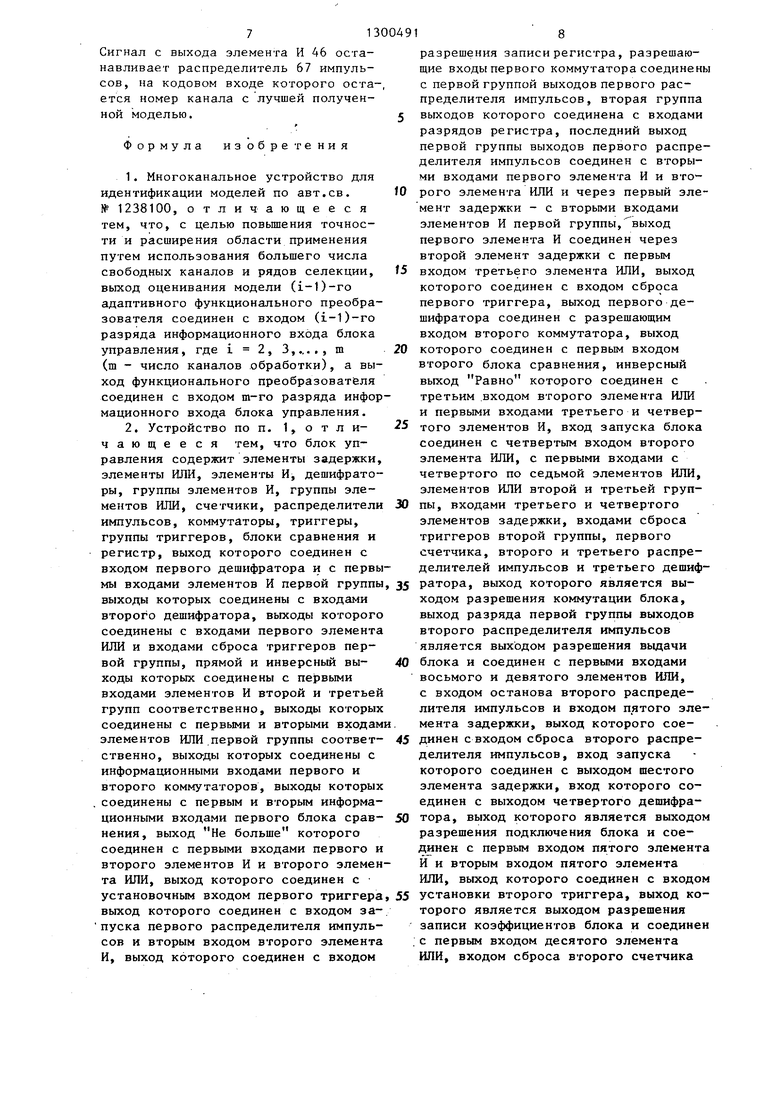

На фиг. 1.приведена схема предложенного устройства; на фиг. 2 - функциональная схема его блока управления.

Устройство содержит (фиг. 1) блок 1 управления, блок 2 памяти, m каналов 3 обработки, содержащих блок 4 селекции, адаптивный функциональный преобразователь (АФП) 5, коммутатор 6, элемент И 7, функциональный преобразователь 8. , Блок 1 управления содержит (фиг.2) элементы 9-21 задержки, элементы ИЛИ 22-34, дешифраторы 35-42, ajje- менты И 43-49, группы 50-55 элементов И, группы 56-59 элементов ИЛИ, счетчики 60-63, распределители 64-67 импульсов, коммутаторы 68-70, блоки 71-73 сравнения, триггеры 74-76, группы 77-79 триггеров, регистр 80, выходы 81-88 и входы 89-94 блока управления.

Блоки 2 и 3 идентичны блокам 2 и основного устройства. В части взаимо действия блоков устройства в режимах начальной коммутации, адаптации и оценивания работа описываемого устройства идентична работе основного.

После режима оценивания на втором ряду селекции блок t управления переходит в режим деблокирования. При этом на основании сигналов с выходов оценивания моделей всех блоков 5 и 8 в блоке управления происходит отбор заданного числа каналов 3 обработки для следующего ряда селекции из всег множества m каналов. После окончания отбора Т каналов 3 обработки с I лучшими моделями блок 1 управления вы- дает управляюш,ие сигналы на коммутаторы 6 всех свободных каналов 3 обработки и осуществляет соединение пар выходов отобранных каналов на втором ряду селекции с входами сво- бодных каналов. После этого все свободные каналы опять переходят в режи адаптации, после него - в режим оценивания, затем - селекция частных

моделей второго и третьего рядов селекции, т.е. селекция частных моделей текущего и предыдущего рядов селекции. Этот процесс продолжается до тех пор, пока на очередном ряду селекции не будет достигнута заданная точность или заданное число рядов селекции. В этом Ьлучае канал с минимальным значением критерия селекции на выходе оценивания модели адаптивного функционального преобразователя 5 или функционального преобразователя 8 и содержит выход синтезируемой модели объекта. Отличие работы предложенного устройства от работы основного состоит в том, что на каждом ряду селекции в синтезе моделей участвуют все каналы устройства. В устройстве для синтеза моделей последующего ряда используются лучшие модели, выбираемые из множества моделей текущего ряда и из лучших моделей предшествующего ряда, т.е. для синтеза моделей фактически используются лучшие модели всех предшествующих .рядов селекции. В результате повьш1а- ется точность конечной модели по сравнению с основным устройством. Расширение области применения устройства и повышение точности конечной модели получается также и за счет того, что для синтеза модели может быть использог вано практически неограниченное число рядов селекции.

Работа устройства начинается по сигналу Пуск на входе 91. При этом сбрасывгиотся триггеры 74-79, счетчики 60-63, дешифратор 38 и регистр 80 и запускается распределитель 65 импульсов , определяющий адреса точек обучающей последовательности в блоке 2 памяти. По сигналу Пуск на входе 91 АФП 5 приводятся в рабочее состояние сигналом с выхода 86 триггера 75. Прохождение этого сигнала в каждом канале 3 обработки информации происходит только в случае, когда канал 3 свободен, т.е. сброшен соответствующий триггер 77 группы.

По сигналам распределителя 65 импульсов АФП блок 2 памяти через коммутаторы 6 выдает в АФП всех каналов 3 аргументы точек обучающей последовательности. Сигнал на второй разрешающий выход 81 поступает с выхода первой группы распределителя 65 импульсов после выдачи последнего адреса для тЬчек обучающей последовательности распределителем 65 им31300

пульсов. Этот же сигнал останавливает и через элемент 12 задержки устанавливает в исходное состояние распределитель 65 иипульсов и поступает на вход счетчика 63, который подсчитывает число циклов адаптации АФП 5. .

Пока содержимое счетчика 63 не больше заданного числа или на выходе 90 элемента И 7 первого канала 3 Ш распределителя 66 импульсов. При этом

15

20

30

обработки информации не появится сигнал о достижении заданной точности моделей во всех каналах 3, дешифратор 42 выдает разрешающий сигцал на прохождение через элемент И 49 сигнала с выхода распределителя 65 импульсов, задержанного элементом 13 .задержки, на запуск этого распределителя для начала следующего цикла адаптации АФП5. Время задержки элемента 13 определяется временем выбора и запоминания в АФП всех каналов 3 лучших моделей в данном цикле адаптации.

При достижении содержимого счетчи-25 ка 63 заданного числа по сигналу на входе 9.0 дешифратор 42 выдает сигнал на занесение в память АФП5 предельно большого числа и через элемент 11 задержки запускает распределитель 64 импульсов. Пока число импульсов не превышает заданное число точек проверочной последовательности, распределитель 64 импульсов выдает в блок 2 памяти адреса этих точек, аргументы которых через коммутаторы 6, а также значения функций (непосредственно с выхода значений функций блока 2 памяти) , выдаются в АФПЗ всех каналов 3.

По окончанию режима оценивания по сигналу с выхода первой группы .распределителя 64 импульсов этот распределитель останавливается и через заданное время через элемент задержки 10 сбрасывается. По этому же сигналу с выхода первой группы распределителя 64 импульсов сбрасывается распределитель 67 импульсов и через элемент 9 задержки.устанавливает триггер 74, запуская распределитель 64 импульсов, сигналы с выходов первой группы которого поступают на разрешающие входы коммута35

40

45

50

сигнал с дешифратора 35 на входе элементов ИЛИ 28 - нулевой. Коммутатор 70 по сигналу распределителя 66 импульсов подключает первый канал 3 обработки информации к первому входу блока 73 сравнения. Так как регистр 80 установлен в нулевое состояние сигналом Пуск по входу 91, то дешифратор 41 выдает «а адресные входы коммутатора 69 адрес первого канала и к второму входу блока 73 сравнения также подключается первый канал 3 обработки. При равенстве сигналов на в.ходах блока 73 сравнения на выходе появляется сигнал разрешения, который поступает на первый вход элемента И 47, на второй вход которого поступает сигнал с выхода триггера 76. По разрешающему сигналу с выхода элемента И 47 и регистра 80 происходит запись двоичного кода с второй группы выходов распределителя 66 импульсов. На этом шаге содержимое регистра 80 не изменится, так как до этого он и распределитель 66 импульсов установлены в исходное состояние по входу 91. Сигнал с выхода блока 73 сравнения сбрасывает триггер 76, запрещает запись информации в регистр 80 и запускает распределитель 66 импульсов, который вьщает сигналы на подключение к первому входу блока 73 сравнения выхода 92 оценивания модели АФП5 второго канала 3 обработки. Если сигнал на первом входе блока 73 сравнения больше, чем на втором входе, то разрешающего

.сигнала на ее выходе нет. После э.то- го распределитель 66 импульсов подключает третий канал обработки информации и т.д. Этот процесс повторяется до подключения коммутатором 70 к первому входу блока 73 сравнения канала 3 обработки, сигнал на выходе

то ра 68, который подключает к перво- „ оценивания модели АФПЗ которого меньму входу блока 71 сравнения заданный канал 3. На первом ряду селекции устройство работает так же, как и основное устройство до момента посше или равен сигналу, подключенному коммутатором 69 к второму входу блока 73 сравнения. В этом случае по сигналу блока 73 сравнения останавлитупления сигнала с выхода триггера 75 для АФП5 всех незаблокированных каналов 3, когда начинается режим адаптации АФП на точках обучающей последовательности на втором ряду селекции.

На втором и последующих рядах селекции сигнал с дешифратора 35 через элемент И 43 поступает на вход сброса

5

0

0

5

5

0

5

0

сигнал с дешифратора 35 на входе элементов ИЛИ 28 - нулевой. Коммутатор 70 по сигналу распределителя 66 импульсов подключает первый канал 3 обработки информации к первому входу блока 73 сравнения. Так как регистр 80 установлен в нулевое состояние сигналом Пуск по входу 91, то дешифратор 41 выдает «а адресные входы коммутатора 69 адрес первого канала и к второму входу блока 73 сравнения также подключается первый канал 3 обработки. При равенстве сигналов на в.ходах блока 73 сравнения на выходе появляется сигнал разрешения, который поступает на первый вход элемента И 47, на второй вход которого поступает сигнал с выхода триггера 76. По разрешающему сигналу с выхода элемента И 47 и регистра 80 происходит запись двоичного кода с второй группы выходов распределителя 66 импульсов. На этом шаге содержимое регистра 80 не изменится, так как до этого он и распределитель 66 импульсов установлены в исходное состояние по входу 91. Сигнал с выхода блока 73 сравнения сбрасывает триггер 76, запрещает запись информации в регистр 80 и запускает распределитель 66 импульсов, который вьщает сигналы на подключение к первому входу блока 73 сравнения выхода 92 оценивания модели АФП5 второго канала 3 обработки. Если сигнал на первом входе блока 73 сравнения больше, чем на втором входе, то разрешающего

.сигнала на ее выходе нет. После э.то- го распределитель 66 импульсов подключает третий канал обработки информации и т.д. Этот процесс повторяется до подключения коммутатором 70 к первому входу блока 73 сравнения канала 3 обработки, сигнал на выходе

ше или равен сигналу, подключенному коммутатором 69 к второму входу блока 73 сравнения. В этом случае по сигналу блока 73 сравнения останавливается распределитель 66 импульсов и с его выхода происходит запись двоичного кода в регистр 80. Коммутатор 69 по сигналу с дешифратора 41 по второму входу блока 73 сравнения подключает канал 3 обработки, адрес которого указан в регистре 80. Таким образом, по второму входу блока 73 сравнения подключается выход оценивания модели АФП5 канала 3, сигнал на выходе которого меньше, чем у предыдущего канала.

Сигнал с выхода блока 73 сравнения сбрасывает триггер 76,запрещает запись информации в регистр 80 и запускает распределитель 66 импульсов. Начинается поиск нового канала 3с меньшим значением сигнала на выходе оценивания модели АФП5. Этот процесс продолжается до тех пор, пока не переберут- 20 версного выхода блока 72 сравнения,

ся все каналы 3 обработки информации В этом случае по импульсу с последнего выхода первой группы распределителя 66 импульсов этот распределитель останавливается и снимается- раз решающий сигнал на запись в регистр 80 на втором входе элемента И 47, а сигнал с первой группы выходов распределителя 66 импульсов.поступает на первые входы элементов И 54 группы. Сигнал с выхода дешифратора 40 устанавливает в единичное состояние один триггер 79 группы, адрес которого указан в регистре 80. Взведенный триггер 79 блокирует на входах коммутаторов 70 и 69 соответствующий канал 3 обработки: по сигналу взведенного триггера 79 через соответствующий элемент И 53 на входе коммутаторов 70 и 69 появляется макси- мальньй сигнал, заведомо больший сигналов с выхода оценивания моделей АФП5.

Сигнал с выхода дешифратора 40 через элемент ИЛИ 32 добавляет единицу в счетчик 62 (счетчик подсчитывает число частных моделей, которые нужно пропустить в следующий ряд селекции), сбрасывает регистр 80, триггер 76 и запускает распределитель 66 импульсов. Процесс повторяется до достижения в счетчике 62 заданного значения числа каналов. После этого на выходе дешифратора 39 появляется

сигнал, который через элемент ИЛИ 30 55 Делении такого канала на выходе дешифратора 36 появляется сигнал, который поступает на вход элемента И 46, на второй вход которого поступает сигнал с выхода дешифратора 35.

и триггер 76 останавливает распределитель 66 импульсов. Сигнал с выхода дешифратора 39 поступает на первые входы элементов И 5 группы, на вто

рыв входы которых поступают сигналы с инверсных выходов триггеров 79 группы. Единичные сигналы на выходах элементов И 51 группы появляются только при сброшенных триггерах 79. Эти выходы соединены с входами сброса 77 группы. При этом происходит разблокировка каналов, которые не хранят лучшие модели текущего и предыдущего рядов селекции.

Задержанньй элементом 19 задержки сигнал с дешифратора 39 сбрасывает счетчик 62 и триггеры 79 группы. Сигналы с инверсных выходов триггеров 79 группы поступают на первые входы элементов И 52 группы. Сигнал с элемента 19 задержки поступает на второй вход элемента И 44, на первый вход которого приходит разрешение с инесли не найдено минимальное значение критерия селекции 8, , т.е. найден канал 3, на выходе оценивания модели АФП5 которого сигнал меньше или равен наперед заданному значению &, , подаваемому на вход 94 задания точности модели блока 1 управления. Если зна

чение о, меньше или равное Од найдено, то сигналом с блока 72 сравнения останавливается.распределитель 66 импульсов и запрещается прохождение сигнала сброса регистра 80 через эле- мемт И 48. При этом в регистре 80 находится адрес модели, значение

1 который меньше или равно , т.е. процесс нахождения лучшей модели и работа устройства закончены (на первом входе элемента И 44 нулевое значение). Если же в текущем ряду селекции не найден канал 3 со значением 8,S а то блок t управления запускается на следующий цикл работы сигналом с выхода элемента И 44.

ошибки 6. 5„

45

50

Сигнал с выхода дешифратора 36 поступает на счетчики 60 и 61. Как только код счетчика 60 показывает, что все каналь заняты, сигнал с выхода дешифратора 35 сбрасывает триггеры 77 группы и переводит через элемент ИЛИ 23 блок 1 управления в режим селекции лучшего канала 3 (последовательно сбрасывает и запускает распределитель 67 импульсов). При опрешифратора 36 появляется сигнал, который поступает на вход элемента И 46, на второй вход которого поступает сигнал с выхода дешифратора 35.

71300491

Сигнал с выхода элемента И 46 останавливает распределитель 67 импульсов, на кодовом входе которого оста-, ется номер канала с лучшей полученной моделью,5

Формула изобретения

1.Многоканальное устройство для идентификации моделей по авт.св. № 1238100, отличающееся тем, что, с целью повышения точности и расширения области применения путем использования большего числа свободных каналов и рядов селекции, выход оценивания модели (i-l)-ro адаптивного функционального преобразователя соединен с входом (i-1)-ro разряда информационного входа блока управления, где ,3,....,т (ш - число каналов .обработки), а выход функционального преобразователя соединен с входом т-го разряда информационного входа блока управления.

2.Устройство по п. 1, о т л и- чающееся тем, что блок управления содержит элементы задержки, элементы ИЛИ, элементы И, дешифраторы, группы элементов И, группы элементов ИЛИ, счетчики, распределители импульсов, коммутаторы, триггеры, группы триггеров, блоки сравнения и регистр, выход которого соединен с входом первого дешифратора и с первы40

мы входами элементов И первой группы, 35 ратора, выход которого является вы- выходы которых соединены с входами второго дешифратора, выходы которого соединены с входами первого элемента ИЛИ и входами сброса триггеров первой группы, прямой и инверсный выходы которых соединены с первыми входами элементов И второй и третьей групп соответственно, выходы которых соединены с первыми и вторыми входами элементов ИЛИ.первой группы соответственно, выходы которых соединены с информационными входами первого и второго коммутаторов, выходы которых соединены с первым и вторым информационными входами первого блока сравнения, выход Не больше которого соединен с первыми входами первого и второго элементов И и второго элемента ИЛИ, выход которого соединен с

ходом разрешения коммутации блока, выход разряда первой группы выходов второго распределителя импульсов является выходом разрешения вьщачи блока и соединен с первыми входами восьмого и девятого элементов ИЛИ, с входом останова второго распределителя импульсов и входом п ятого эле мента задержки, выход которого сое- 45 динен с входом сброса второго распределителя импульсов, вход запуска которого соединен с выходом шестого элемента задержки, вход которого соединен с выходом четвертого дешифратора, выход которого является выходо разрешения подключения блока и соединен с первым входом пятого элемент И и вторым входом пятого элемента ИЛИ, выход которого соединен с входо

50

установочным входом первого триггера, 55 установки второго триггера, выход ковыход которого соединен с входом за-, пуска первого распределителя импульсов и вторым входом второго элемента И, выход которого соединен с входом

разрешения записи регистра, разрешающие входы первого коммутатора соединен с первой группой выходов первого распределителя импульсов, вторая группа выходов которого соединена с входами разрядов регистра, последний выход первой группы выходов первого распределителя импульсов соединен с вторыми входами первого элемента И и второго элемента ИЛИ и через первый элемент задержки - с вторыми входами элементов И первой группы,выход первого элемента И соединен через второй элемент задержки с первым входом третьего элемента ИЛИ, выход которого соединен с входом сброса первого триггера, выход первого дешифратора соединен с разрешающим входом второго коммутатора, выход которого соединен с первым входом второго блока сравнения, инверсный выход Равно которого соединен с третьим .входом второго элемента ИЛИ и первыми входами третьего и четвертого элементов И, вход запуска блока соединен с четвертым входом второго элемента ИЛИ, с первыми входами с четвертого по седьмой элементов ИЛИ, элементов ИЛИ второй и третьей группы, входами третьего и четвертого элементов задержки, входами сброса триггеров второй группы, первого счетчика, второго и третьего распределителей импульсов и третьего дешиф

ратора, выход которого является вы-

ходом разрешения коммутации блока, выход разряда первой группы выходов второго распределителя импульсов является выходом разрешения вьщачи блока и соединен с первыми входами восьмого и девятого элементов ИЛИ, с входом останова второго распределителя импульсов и входом п ятого элемента задержки, выход которого сое- динен с входом сброса второго распределителя импульсов, вход запуска которого соединен с выходом шестого элемента задержки, вход которого соединен с выходом четвертого дешифратора, выход которого является выходом разрешения подключения блока и соединен с первым входом пятого элемента И и вторым входом пятого элемента ИЛИ, выход которого соединен с входом

торого является выходом разрешения записи коэффициентов блока и соединен с первым входом десятого элемента ИЛИ, входом сброса второго счетчика

и входом седьмого элемента задержки, выход которого соединен с первым входом одиннадцатого элемента ИЛИ, второй вход которого соединен с выходом третьего элемента задержки, выход, девятого элемента ИЛИ соединен с входом восьмого элемента задержки, входами сброса четвертого распределител импульсов и третьего счетчика, выход которого соединен с входом пятого дешифратора, выход которого соединен с первыми входами шестого элемента И элементов ИЛИ четвертой группы и вторым входом шестого элемента ИЛИ, выход которого соединен с входом сбро- са четвертого триггера, выход которого является выходом запуска каналов блока и соединен с входом запуск I четвертого распределителя импульсов,

вторад группа выходов которого соединена с первыми входами элементов И четвертой группы, выходы которых соединены с входами шестого дешифратора, выходы которого соединены с входами двенадцатого элемента ИЖ и входами установки триггеров третьей группы, выходы которых образуют разрешающий выход блока и соединены с первыми входами элементов И пятой группы, выходы которых соединены с информационными входами третьего дешифратора и входами установки триггеров второй группы, выходы которых соединены с вторыми входами элементов iiilH четвертой группы, выходы которых соединены с вторыми входами элементов И пятой группы, выход двенадцатого элемента ИЛИ соединен с первым входом седьмого элемента И, счетным входом третьего счетчика и через девятый элемент задержки с первым входом тринадцатого элемента ИЛИ счетным входом первого счетчика и входом сброса четвертого распредели

теля импульсов, первая группа выходов 45 группы, выход четвертого элемента которого соединена с разрешающим входом третьего коммутатора, выход которого соединен с первым входом третьего блока сравнения, выход которого

соединен с вторым входом десятого элемента ИЛИ, третий вход которого соединен с выходом третьего разряд седьмого дешифратора, выход четвер того элемента задержки соединен с четвертым входом десятого элемента ИЛИ, выход которого соединен с вхо сброса второго триггера, выход одинн цатого элемента ИЛИ соединен с входо запуска третьего распределителя им пульсов, выход первой группы котор го является адресным выходом блока соединен с входом останова третьег

соединен с третьим входом шестого элемента ИЛИ и вторыми входами элементов И четвертой группы, коммутирующий вход блока соединен с вторым входом третьего блока сравнения и информационным входом третьего ком- мутатора, выход восьмого элемента задержки соединен с вторым входом тринадцатого элемента ИЛИ, выход

O

5

которого соединен с входом установки четвертого триггера, информационный выход первого счетчика соединен с входом седьмого дешифратора, выход первого разряда которого соединен с вторыми входами элементов ИЛИ третьей группы, девятого элемента ИЛИ и седьмого элемента И, йыход которого соединен с четвертым входом шестого элемента ИЛИ, выход второго разряда седьмого дешифратора соединен с вторым входом шестого элемента И, выход которого соединен с входом сброса первого распределителя импульсов и вторым входом третьего элемента ИЛИ, третий вход которого соединен с выходом десятого элемента задержки и вторым входом третьего элемента И, выход которого соединен с вторым входом четвертого элемента ИЛИ, выход которого соединен с входом сброса регистра, выход первого элемента ИЛИ соединен с входом десятого элемента задержки и счетным входом четвертого счетчика, выход которого соединен с входом восьмого дешифратора, выход которого соединен с входом одиннадцатого элемента задержки, первыми входами элементов И шестой группы, пятым вхо0 дом второго элемента ИЛИ и вторым входом седьмого элемента ИЛИ, выход которого соединен с входом сброса четвертого счетчика, выход одиннадцатого элемента задержки соединен с вторыми входами четвертого элемента И и элементов ИЛИ второй группы, выходы которых соединены с входами установки триггеров первой группы, инверсные выходы которых соединены с

0 вторыми входами элементов И шестой группы, выходы которых соединены с третьими входами элементов ИЛИ третьей группы, выходы которых соединены с входами сброса триггеров третьей

0

5

5

И

группы, выход четвертого элемента

соединен с вторым входом десятого элемента ИЛИ, третий вход которого соединен с выходом третьего разряда седьмого дешифратора, выход четвертого элемента задержки соединен с четвертым входом десятого элемента ИЛИ, выход которого соединен с входом сброса второго триггера, выход одиннадцатого элемента ИЛИ соединен с входом запуска третьего распределителя импульсов, выход первой группы которого является адресным выходом блока и соединен с входом останова третьего

распределителя

11 1

импульсов, входом

двенадцатого элемента задержки, счетным входом второго счетчика, вторым входом восьмого элемента ИЛИ и через тринадцатый элемент задержки - с вторым входом пятого элемента И, выход которого соединен .с третьим входом одиннадцатого элемента ИЛИ, выхо второго счетчика соединен с первым информационным входом четвертого дешифратора, второй информационный вход которого является входом окончания настройки блока, вторые входы элементов И второй и третьей групп и второго блока сравнения образуют информационный вход, вход задания максимальной величины и вход задания точности модели блока соответст ИЛИ

венно, выход восьмого

элемента S2,

81

вторым

12 решающим

входом

3. Устройство по п. 1, отличающее с я тем, что распределитель 5 импульсов содержит генератор тактовых импульсов, счетчик, дешифратор и элемент ИЛИ, которого соединен с входом сброса счетчика, выход которого соединен с входом дешифратора, выходы 10 разрядов которого являются первой группой выходов распределителя, второй группой выходов которого являются выходы разрядов счетчика, счетнь1й вход которого соединен с выходом генератора тактовых импульсов, вход запуска и останова которого являются входами запуска и останова распределителя, входы сброса которого соединены с входами элемента ИЛИ.

15

Редактор М. Келемеш

U9. 2

Составитель Н. Матвеев

Техред М.Ходанич Корректор Л. Патай

1151/49

Тираж 673Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для идентификации моделей | 1984 |

|

SU1238100A1 |

| Устройство для сопряжения дискретных датчиков с электронной вычислительной машиной | 1982 |

|

SU1024898A2 |

| Устройство для дискретизации и передачи сейсмических сигналов | 1980 |

|

SU1096680A1 |

| Устройство для коммутации информационных каналов | 1981 |

|

SU1003123A1 |

| Многоканальный коммутатор | 1981 |

|

SU963046A1 |

| Буферное запоминающее устройство | 1990 |

|

SU1783581A1 |

| Устройство для управления сопряжением процессора с абонентами | 1989 |

|

SU1730629A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Устройство для моделирования систем массового обслуживания | 1981 |

|

SU962970A1 |

| Устройство для селекции изображений объектов | 1987 |

|

SU1525718A1 |

Изобретение относится к самонастраивающимся устройствам перцеп- тронного типа для обработки информации. Цель изобретения - повышение точности и расширение области приФи1.1 менения устройства путем использования большего числа свободных каналов и рядов селекдии. Поставленная цель достигается тем, что выходы оценивания моделей адаптивных функциональных преобразователей 5 и выход функционального преобразователя 8 соединены с соответствующими входами разрядов информационного входа блока управления, причем блок 1 управления содержит элементы задержки, элементы ИПИ, дешифраторы, элементы И, группы элементов И, группы элементов ИЛИ, счетчики, распределители импульсов, коммутаторы, блоки сравнения, триггеры, группы триггеров и регистр с соответствующими связями. 2 3,п. ф-лы, 2 ил. (С (Л 4 СО К)

| Многоканальное устройство для идентификации моделей | 1984 |

|

SU1238100A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-03-30—Публикация

1986-03-05—Подача