112381

Изобретение относится к.технике вязи и может быть использовано в истемах фазовой автоподстройки часоты (ФАПЧ) тракта формирования опорого когерентного сигнала демодуля- ,.. ора однократной фазовой телеграфии.

Цель изобретения - повышение точости при работе с сигналами однократой фазовой телеграфии за счет устраения ошибок, возникающих в извест- j0 ых устройствах, при изменении фазы качком на 180 .

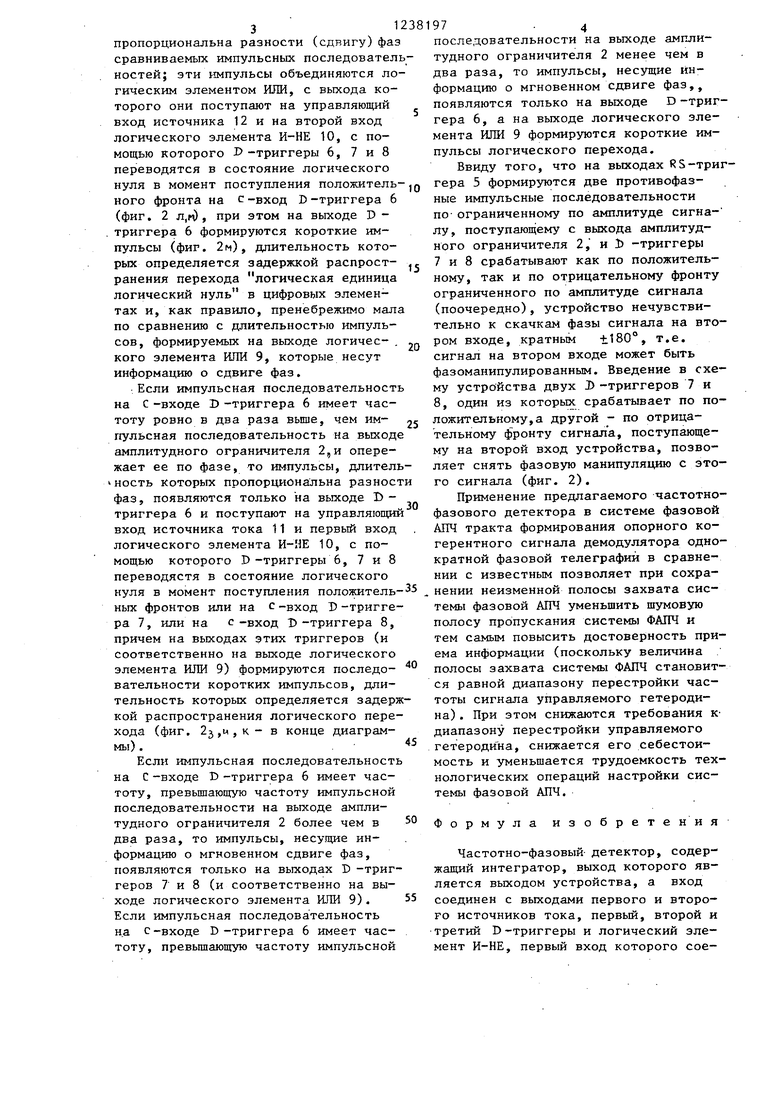

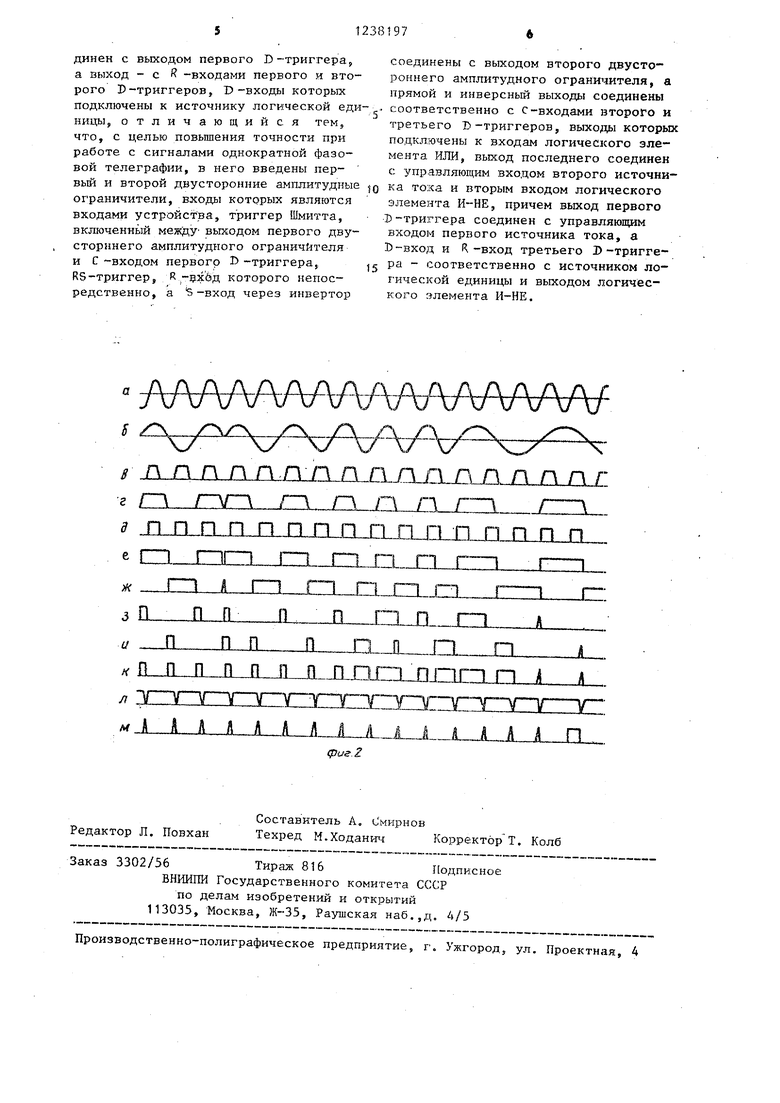

На фиг. 1 показана функдионгшьная хейа устройства; на фиг. 2 - временные диаграммы.tS

Детектор содержит первый и второй двусторонние, огр аничители 1 и 2, триггер 3 Имитта, инвертор 4,RS -триггер 5, первый, второй и третий D - триггеры 6-8, элемент ИЛИ 9, элемент - И-НЕ 10, первый и второй источники 11 и 12 тока, интегратор 13,

Входы первого и второго двусторонних амплитудных ограничителей и 2 являются входами устройстЕ1а. Выход 25 первого ограничителя 1 соединен с входом триггера 3, а выход второго ограничителя 2 соединен непосредственно и через инвертор 4 с -входом и S -входом соответственно Р, 5 -триг- -.jp гера 5. Выход триггера Шмитта 3 и прямой и инверсный выходы R э -триггера 5 соединены соответственно с С-вьгходами первого, второго и третьего D -триггеров 6, 7 и 8, D -входы которых объединены и подключены к источнику логической единицы. Выходы второго и третьего D -триггеров 7 и 8 подключены к входам элемента ИЛИ 9. Выход первого Б -триггера 6 соединен с первым входом элемента И-НЕ 10 и управляющим входом источника 11 о Выход элемента ИЛИ 9 соединен с управляющим входом источника 12 и вторым входом элемента И-НЕ 10, выход которого подключен к R-входам D-триггеров 6, 7 и 8. Выходы источников 11 и 12 соединены с входом интегратора 13, выход которого является выходом устройства.

Устройство работает следующим об- разом.

На первый и второй входы устройства поступают два сигнала произвольной формы, причем частота сигнала, поступающего на первый вход, должна быть в два раза больше частоты сигнала, поступающего на второй вход (фиг. 2a,S). Амплитуды сигналов долж97.1

ны быть не меньше порогов срабатыва- ВИЯ триггера Шмитта 3 и примененных в устройстве цифровых узлов. Ампли-- тудные ограничители 1 и 2 превращают пост у пившие сигналы в последовательность трапеце:ндальных импульсов (фиг. 26,г). Триггер Шмитта 3 из ограниченного по амплитуде сигнала,пос тупшощего с выхода ограничителя 1, формирует последовательность прямоугольных импульсов с крутыми положительными и отрицательными фронтами (фиг. 2д), что необходимо для надежного срабатывания В -триггера 6. RS-триггер 5 вместе с инвертором 4 представляет собой формирователь прямоух ольньп-: импульсов с двумя про- тизофазньми (прямым и инверсным) выходами, при этом сформированные импульсные последовательности имеют крутые положительные и отрицательные С5)ронты и не имеют временного сдвига относительно друг друга (фиг. 2е,ж), который: неизбежно возникает в логических инверторах за счет задержки . распространения при изменении входного уровня логического нуля на уровень логической единицы или наоборот

D-триггеры 6, 7 и 8 формируют на выходах уровень логической единиць в момент поступления положительного фронта на их С -входы (фиг, 2чс, 5,4). Ввиду того, что на с -входы D -триггеров 7 и 8 поступают две противофазные импульсные последовательности а вь/жоды 1)-триггеров 7 и 8 объедине- в:ы с помощью логического элемента V LiTH 9,, на выходе логического элемент 1 1ЛИ 9 формируется уровень логической единицы как в момент поступле- НИИ положительного фронта., так и в момент поступления отрицательного фронта последовательности :импульсов (фи1 2к), сформированных из сигнала, поступающего на второй вход уст1:1ойства5 а.мплитудным ограничителем 2. Это обуславливает необходимость подачи на первый вход устройства сигнала с частотой, в два раза большей частоты сигнала на втором входе,

Если импульсная последовательност на с -сходе D- -триггера 6 :имеет частоту ровно в два раза выше, чем импульсная последовательность на выход амплитудного ограничителя 2, и отстает от нее по фазе, то на выходах р-трпггеров 7 и В поочередно формируются импульсы, длительность KOTopiiix

3123

пропорциональна разности (сдвигу) фаз сравниваемых импульсных последовательностей; эти импульсы объединяются логическим элементом ИЛИ, с выхода которого они поступают на управляющий вход источника 12 и на второй вход логического элемента И-НЕ 10, с помощью которого 1 -триггеры 6, 7 и 8 переводятся в состояние логического нуля в момент поступления положитель-JQ кого фронта на с-вход D-триггера 6 (фиг. 2 л,п), при этом на выходе D - . триггера 6 формируются короткие импульсы (фиг. 2м), длительность которых определяется задержкой распрост- ,, ранения перехода логическая единица логический нуль в цифровых элементах и, как правило, пренебрежимо мала по сравнению с длительностью импульсов, формируемых на выходе логичес- . кого элемента ИЛИ 9, которые несут информацию о сдвиге фаз.

Если импульсная последовательность на С-входе D -триггера 6 имеет частоту ровно в два раза выше, чем им- ,5 ггульсная последовательность на выходе амплитудного ограничителя 2,и опережает ее по фазе, то импульсы, длитель- ность Которых пропорциональна разности фаз, появляются только на выходе 1)- триггера 6 и поступают на управляющий вход источника тока 11 и первый вход логического элемента И-НЕ 10, с помощью которого D -триггеры 6, 7 и 8 переводястя в состояние логического нуля в момент поступления полояштель- ных фронтов или на с-вход Р-триггера 7, или на с-вход Г -триггера 8, причем на выходах этих триггеров (и соответственно на выходе логического элемента ИЛИ 9) формируются последо- вательности коротких импульсов, длительность которых определяется задержкой распространения логического перехода (фиг. 2з,м,к - в конце диаграммы).. «

Если импульсная последовательность на С-входе D -триггера 6 имеет частоту, превьшающую частоту импульсной последовательности на выходе амплитудного ограничителя 2 более чем в 50 два раза, то импульсы, несущие информацию о мгновенном сдвиге фаз, появляются только на выходах D -триггеров 7 и 8 (и соответственно на выходе логического элемента ИЛИ 9). 55 Если импульсная последовательность на с-входе D -триггера 6 имеет частоту, превьппающую частоту импульсной

,30

JQ,,

,5

0 5

0

197. 4

последовательности на выходе амплитудного ограничителя 2 менее чем в два раза, то импульсы, несущие информацию о мгновенном сдвиге фаз,, появляются только на выходе D -триггера 6, а на выходе логического элемента ИЛИ 9 формируются короткие импульсы логического перехода.

Ввиду того, что на выходах RS-триггера 5 формируются две противофазные импульсные последовательности по- ограниченному по амплитуде сигна- лу, поступающему с выхода амплитудного ограничителя 2, и 3) -триггеры 7 и 8 срабатывают как по положительному, так и по отрицательному фронту ограниченного по амплитуде сигнала (поочередно), устройство нечувствительно к скачкам фазы сигнала на втором входе, кратньм ±180°, т.е. сигнал на втором входе может быть фазоманипулированным. Введение в схему устройства двух D -триггеров 7 и 8, один из которых срабатывает по положительному, а другой - по отрицательному фронту сигнала, поступающему на второй вход устройства, позволяет снять фазовую манипуляцию с этого сигнала (фиг. 2).

Применение предлагаемого частотно- фазового детектора в системе фазовой АПЧ тракта формирования опорного когерентного сигнала демодулятора однократной фазовой телеграфии в сравнении с известным позволяет при сохранении неизменной полосы захвата системы фазовой АПЧ уменьшить щумовую полосу пропускания системы ФАПЧ и тем самым повысить достоверность приема информации (поскольку величина полосы захвата системы ФАПЧ становится равной диапазону перестройки частоты сигнала управляемого гетеродина) . При этом снижаются требования к- диапазону перестройки управляемого гетероди на, снижается его себестоимость и уменьшается трудоемкость технологических операций настройки системы фазовой АПЧ.

Формула изобретения

Частотно-фазовый детектор, содержащий интегратор, выход которого является выходом устройства, а вход соединен с выходами первого и второго источников тока, первый, второй и третий D-триггеры и логический элемент И-НЕ, первый вход которого сое-

динен с выходом первого D-триггера, а выход - с -входами первого и второго D-триггеров, D -входы которых подключены к источнику логической единицы, отличающийся тем, что, с целью повьшения точности при работе с сигналами однократной фазовой телеграфии, в него введены пер- вьй и второй двусторонние амплитудные ограничители, входы которых являются входами устройст ва, триггер Шмитта, включенный между выходом первого дву- сторннего амплитудного ограничителя и С -входом первого 1 -триггера, RS-триггер, R -9Хбд которого непосредственно, а S-вход через инвертор

° ДА/ АААА/WVA/WW

S П П П П П-П П П А А Л А П Л А П Г г Г Г- Г Г П Г 3 П П П П П Д П П П П П П П П П П

X

П ГП П

соединены с выходом второго двустороннего амплитудного ограничителя, а прямой и инверсный выходы соединены

соответственно с с-входами второго и третьего 75-триггеров, выхода которых подключены к входам логического элемента ИЛИ, выход последнего соединен с управляющим входом второго источника тока и вторым входом логического элемента И-НЕ, причем выход первого D Триггера соединен с управляющим входом первого источника тока, а С-вход и R-вход третьего D-тригге-

ра - соответственно с источником логической единицы и выходом логического элемента И-НЕ.

m д гпczL-Ji:Li:n jzi.

ILJL

Л

u

CL

u JLJL JLJl JLjQ JlIlJIia JZKIl

ILJI

Л.

л TiT T r-TZTiyi:yi:y:

ГГ

J™.

зс:;

f А А... А а.. А . 1 J А Д П

(риг. 2

Редактор Л. Повхан

Составитель А, Смирнов

Техред М.Ходанич Корректор , Колб

Заказ 3302/56 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб.,д. Л/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Многофазный импульсный синхронно-фазовый демодулятор | 1980 |

|

SU924821A1 |

| УСТРОЙСТВО ДЛЯ УПРАВЛЕНИЯ СИЛОВЫМ ЭЛЕКТРОПРИВОДОМ | 1973 |

|

SU378796A1 |

| Система радиосвязи с однополосной модуляцией сигналов | 1983 |

|

SU1262739A1 |

| ДЕМОДУЛЯТОР СИГНАЛОВ С ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1995 |

|

RU2076458C1 |

| Вибрационный источник сейсмических сигналов | 1983 |

|

SU1138772A1 |

| ОБНАРУЖИТЕЛЬ ПЕРЕОТРАЖЕННЫХ СИГНАЛОВ | 1999 |

|

RU2191400C2 |

| Радиоприемное устройство с защитой от помех | 1990 |

|

SU1786666A1 |

| Демодулятор сигналов частотнойТЕлЕгРАфии | 1979 |

|

SU849528A1 |

| Устройство для приема сигналов амплитудной телеграфии | 1980 |

|

SU926773A1 |

| Устройство для синхронного детектирования фазоманипулированных сигналов | 1984 |

|

SU1223395A1 |

Изобретение относится к технике связи и может быть использовано в системах фазовой автоматической подстройки частоты (АПЧ) тракта формирования опорного когерентного сигнала демодулятора однократной фазовой телеграфии. Цель изобретения - повышение точности при работе с сигналами однократной фазовой телеграфии, достигается путем устранения ошибок, возникающих в известных устройствах при изменении фазы скачком на 180. Устройство содержит инвертор 4,В - триггеры 6, 7 и 8, элементы ИЛИ 9, И-НЕ 10, источники 11 и 12 тока, интегратор 13. Для достижения поставленной цели в него введены двусторонние ограничители 1 и 2, триггер Шмит- та 3, RS -триггер 5. Устройство обеспечивает достоверность приема информации, снижение требований к диапазону перестройки управляемого гетеродина, а также снижение себестоимости и уменьшение трудоемкости технологических операций настройки системы фазой АПЧ. 2 ил. Q СО BiiixoS GO ОО

| Устройство для определения знака разности двух частот | 1980 |

|

SU936375A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Частотно-фазовый детектор | 1981 |

|

SU995302A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-15—Публикация

1984-06-13—Подача