ния, а следовательно, большое время вхождения в синхронизм колец ФАПЧ, особенно при больших частотных расстройках.

Цель изобретения - .увеличение быстродействия частотно-фазового детектора.

Указанная цель достигается за счет того, что в частотно-фазовый детектор, содержащийпервую и вторую входные клеммы устройства, первый и второй D-триггеры, С-входами подключенные к першам и вторым входным клеммам устройства, а D-входами к источнику логической единицы, третий и четвертый D-триггеры, С-входами подключенные к первым и вторым входным клеммам устройства, а D-BXOдгили - к выходам первого и второго D-триггеров,элемент И-НЕ, входы которого подключены к выходам первою и второго D-триггеров, а выход - к . R -входам первого и второго D-триггеров, первый элемент ИЛИ-НЕ, входы которого подключены к выходам первого и третьего D-триггеров, второй элемент ИЛИ-НЕ, входы которого подключёны к выходам второго и четвертого Dтриггеров, источник тока, подключенный к выходу первого элемента ИЛИНЕ, элемент отвода тока, подключенный к выхбду второго элемента ИЛИ-НЕ, и интегратор, к входу которого подключены соединенные между собой выходы источника тока и элемента отвода тока,а к выходу-выходные клеммы устройства, дополнительно введены пятый и шестой D-триггеры и подключенные к их выходам соответственно второй источник тока и второй элемент отвода тока,выходы которых соединены между собой и подключены к второму входу интегратоpa причем С-вход пятого D-триггера co единен с С-входом первого D-триггера, а D-вход - с выходом первого элемента ИЛИ-НЕ, С-вход шестого D-триггера соединен с С-входом второго D-триггера, а D-вход - с выходом второго элемента ИЛИ-НЕ.

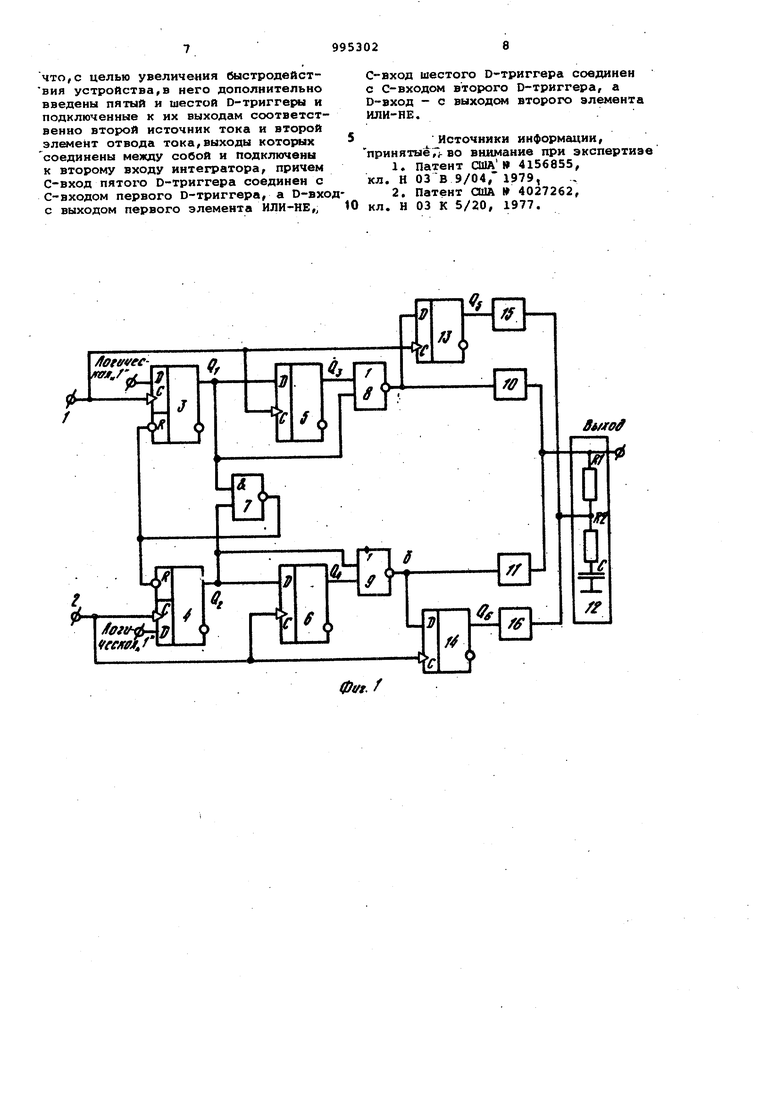

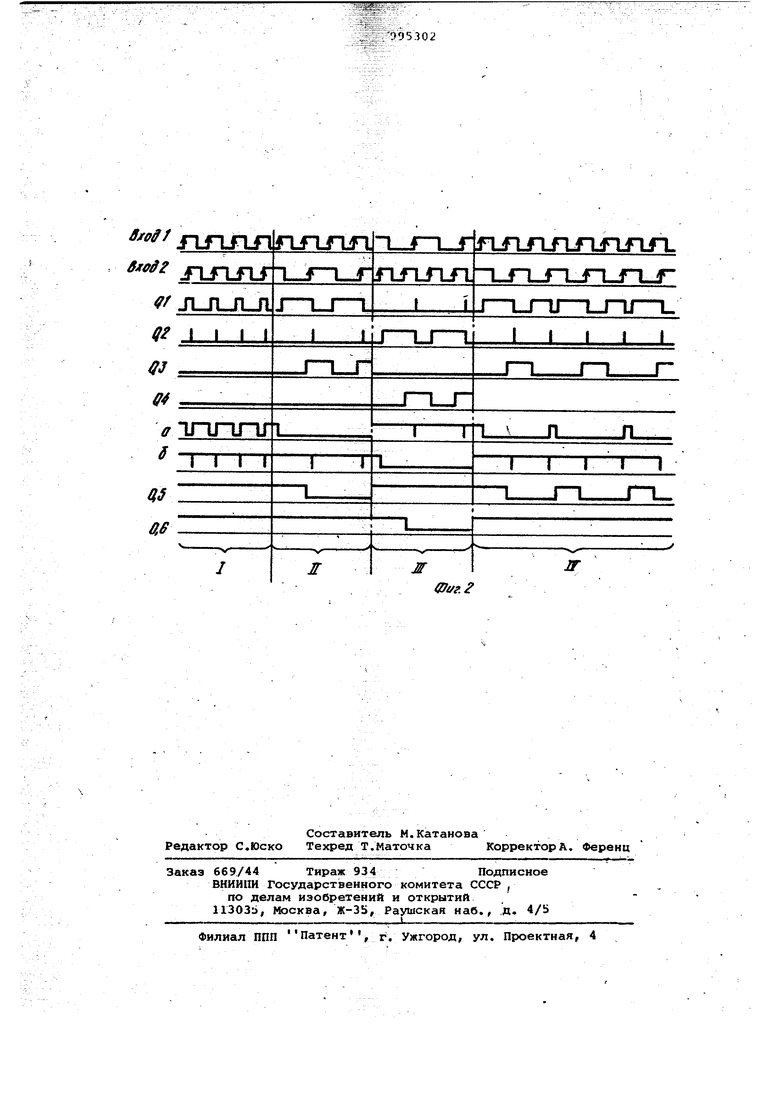

На фиг. 1 приведена структурная электрическая схема частотно-фазового детектора} на фиг. 2 - времен ные диогрс1ммы,: поясняющие работу предлагаемого частотно-Фазового детектора.

. Частотно-Фазовый детектор содержит подключенные к первым и вторым входам 1.И 2 устройства С-входами.первый и второй D-трйггеры 3 и 4, третий и четвертый D-триггеры 5 и 6 соответственно, элемент И-НЕ 7, причем к D-BXOязм первого и второго D-триггеров. 3 и 4 подключен источник логической единицы, а выходы первого и второго D-триггеров 3 и 4 подключены к D-BXOдам соответственно третьего и четвер того D-триггеров 5 и б и к входам эле мента И-НЕ 7, выход которого подключен к входам первого и второго D-TpHr

геров 3 и 4; первый и второй элементы ИЛИ-НЕ 8 и 9, причем входы первого элемента ИЛИ-НЕ 8 подключены к выходам первого и третьего D-триггера 3 и 5, а входа второго элемента ИЛИ-НЕ к выходам второго и четвертого D-триггеров 4 и б, подключенный к выходу первого элемента ИЛИ-НЕ 8 первый .источник 10 токаь и к выходу второго элемента ИЛИ-НЕ 9 - первый элемент 11 отвода тока, выходы которых соединены между собой, подключенный к этой точке своим первым входом интегратор 12, пятый и шестой D-триггеры 13 и 14 и подключенные к их выходс1М соответственно второй источник 15 тока и второй элемент 16 для, отвода тока/ выходы которых соединены между собой и подключены к второму входу интегратора 12, причем С-вход пятого D-триггера 13 соединен с С-входом первого D-триггера, а D-вход с выходом первого элемента ИЛИ-НЕ 8, С-вход шестого D-триггера 14 соединен с входом второго D-триггера, а D-ВХОД - с выходом второго элемента ИЛИ-НЕ 9, выход интегратора 12 подключен к выходным клеммам устройства.

Устройство работает следующим образом.

Пусть сигналы, действующие на входах устройства, имеют одинаковую частоту но между ними имеется фазовый сдвиг, например, сигнал на первом входе 1 опережает сигнал на втором входе 2. Тогда своим передним фронтом (фиг. 2,1, где стрелками обоначены передние фронты действующих на входах сигналов, - зонй Фазовое детектирование при f ) входной сигнал, действующий на входе 1 устройства записывает Логическую i на выход первого D-триггера 3, тот же входной сигнал перезаписывает до его прихода на D-входе третьего D-триггера Ь бывший логический О на его выход и логическую , бывшую на D-входе пятого D-триггера его выход. Пришедший .позже импульс 2 своим передним фронтом записывает логическую i на выход второго D-триггера 4. Две логические 1 на входах элемента И-НЕ 7 дают логический О на его выходе, который устаиавливается по R-входам первый и второй D-..триггеры:3 и 4 в состояние О. На выходах четвертого D- триггера 6 и шестого D-триггера 14 изменения состояний не пройсходит. Таким образом, на выходе первого D- триггера 3 появляется импульс, длительность которого, равна фазовой разности между сигналами на входах .устройства. Импульс проходит через первый -элемент ИЛИ-НЕ 8, где меняет свою полярность. На время своей длительности импульс включает первый источник 10 тока, выходной ток кото рого меняет выходное напряжение интегратора 12, которое при работе ус тройства в замкнутом кольце системы ФАПЧ управляет частотой подстраивае мого генератора в сторону компенсации фазового рассогласования между входншли сигналами устройстйа. Аналогично работает устройство, когда сигнал по входу 2 опережает по фазе ;игнал по вхрду 1, только импульс фазового рассогласования выра батывается на выходе второго D-три гера 4, проходит через второй элеме ИЛИ-НЕ 9, где меняет полярность, включает первый элемент 11 отвода тока, который отводит ток от интегр тора 12, выходное напряжение которо 4 вследствие этого изменяется в другую сторону. . На выходах пятого и шестого Dтриггера 13 и 14 в этом режиме имеют ся логические единицы, и как второй йеточник 15 тока, так и второй элемент 6 отвода тока остаются закрытыми и не влияют на работу устройства. Если сигналы, действующие на входах устройства, имеют разные частоты, например, частота сигнала на входе 1 в два или более раза превыша ет частоту сигнала на входе 2,-устройство работает в режиме частотного детектирования (фиг. 2,1Г - зона Частотное детектирование при ). Тогда первый импульс, действующий на входе 1, записывает логическую 1 на выход первого D-три гера 3, второй импульс перезаписыва ет логическую Ч cD-входа третье го D-триггера 5 на его выходи логи ческий О с выхода первого эле мента ИЛИ-НЕ 8 на выход пятого Dтриггера 13, при этом включаются первый и второй источники 10 и 15 тока. Импульс, действующий на входе 2, записывает логическую i на выход второго D-триггэра 4, тогда срабатывает элемент И-НВ 7 и по входам возвращает первый и второй D-триггеры 3 и 4 в состояние логиОднако логическая ческого . на выходе D-триггера 5 и логи ческий на выходе первого элемента ИЛИ-НЕ 8 и на выходе пятого D-триггера 13 остаются. Первый и второй источники 10 и 15 тока остгио ся включенными и обеспечивают непрерывное изменение выходного напряжения интегратора 12, причем с любой необходимой скоростью, так как второй источник 15 тока подбира ся из расчета необходимой большой величины тока, обеспечивающейнеобходимую скорость заряда конденсатора интегратора 12. Аналогично работает устройство, КОГД1 частота сигнала на входе 2 в два или более раза превышает частоту сигнала на входе 1 (фиг. 2,К зона Частотное детектирование при ) f только сигналы частотного рассогласования вырабатываются аа выходах второго D-триггера 4, четвертого D-триггера 6,второго элемента ИЛИ-НЕ 9 и шестого D-триггера 14. Кроме того, включаются первый и второй элементы 11 и 16 отвода тока. При соотношении частот входных сигналов менее двух (фиг.2, 1У - зона Частотно-фазовое детектирование при fy7f2), ускоряющее действие пятого и шестого О-триггеров 13 и 14, второго источника 15 тока и второго элемента 16 отвода тока в виде тока усредненного по нескольким периодам входного сигнала плавно уменьшается и при равенстве частот пропадает совсем и тем самым не ухудшает подавления побочных колебаний на выходе подстраиваемого генератора при работе . устройства в замкнутом кольце системы ФАПЧ. Положительный эффект достигается за счет того, что дополнительно введенные элементы увеличивают скорость наростания выходного напряжения устройства при неравенстве частот его входных сигналов без ухудшения фильтрующих свойств. Формула изобретения Частотно-фазовый детектор, содержащий первую и вторую входные клеммы устройства, первый и второй D-триггеры, С-входами подключенные соответственно к первым и вторым входным клеммам устройства, а D-входами - к источнику логической единицы, третий и четвертый D-триггеры,С-входами подключенные соответственно к первым и вторым входным клеммам устройства, а D-входами - к выходам первого и второго D-триггеров, элемент И-НЕ, входы которого подключены к выходам первого и второго D-триггеров, а выход - к R-входам первого и второго D-триггеров, первый элемент ИЛИНВ, ВХОДЫ которого подключены к выходам первого и третьего D-триггеров, второй элемент ИЛИ-НВ, входы которого подключены к выходам второго и четвертого D-триггеров, источник тока, подключенный к выходу первого элемента ИЛИ-ЦЕ, элемент отвода тока, подключенный к выходу второго алемента ИЛИ-НЕ, и интегратор, к входу которого подключены выходы -источника тока и элемента для отвода тока, а к выходу - выходные клеммы устройства, отличающийся тем.

что,с целью увеличения быстродействия устройства,в него дополнительно введены пятый и шестой О-тригге ял и подключенные к их выходам соответственно второй источник тока и второй элемент отвода тока,выходы которых соединены между собой и подключены к второму входу интегратора, причем С-вход пятого D-триггера соединен с С-входом первого D-триггера, а D-вхос выходом первого элемента ИЛИ-НЕ,

шестого D-триггера соединен с С-входом второго D-триггера, а D-вход - с выходом второго элемента ИЛИ-НЕ.

Источники информации, принятые ,7 во внимание при экспертиз

1.Патент США 4156855, кл. Н 03 В 9/04, 1979,

2.Патент США I 4027262, кл. Н 03 К 5/20, 1977.

| название | год | авторы | номер документа |

|---|---|---|---|

| Частотно-фазовый детектор | 1981 |

|

SU1014123A1 |

| ИМПУЛЬСНЫЙ ЧАСТОТНО-ФАЗОВЫЙ ДЕТЕКТОР | 1991 |

|

RU2012992C1 |

| Частотно-фазовый детектор | 1985 |

|

SU1287251A1 |

| ЧАСТОТНО-ШИРОТНО-ИМПУЛЬСНЫЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ С РАСПРЕДЕЛЕННОЙ НАГРУЗКОЙ | 2011 |

|

RU2472279C1 |

| ЧАСТОТНО-ШИРОТНО-ИМПУЛЬСНЫЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ С СИММЕТРИРОВАННОЙ НАГРУЗКОЙ | 2012 |

|

RU2490685C1 |

| Частотно-фазовый детектор | 1977 |

|

SU661769A1 |

| Частотно-фазовый детектор | 2019 |

|

RU2721416C1 |

| Цифровой синтезатор частот | 1985 |

|

SU1252940A1 |

| МНОГОЗОННЫЙ ИНТЕГРИРУЮЩИЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ | 2011 |

|

RU2471282C1 |

| ТРЕХФАЗНЫЙ РЕГУЛЯТОР ПЕРЕМЕННОГО НАПРЯЖЕНИЯ С ЗАЩИТОЙ | 2012 |

|

RU2499347C1 |

Авторы

Даты

1983-02-07—Публикация

1981-10-01—Подача