Изобретение относится к импульсной технике и предназначено для использования в системах автоматики и измерительной техники с целью получения разностной частоты импульсов, вычитания импульсных последовательностей и выделения из двух импульсных сигналов сигнала меньшей и большей частот.

Целью изобретения является повышение надежности работы при скачкообразных изменениях частот входных сигналов за счет разделения во времени сигналов разностной ччастоты на выходах устройства.

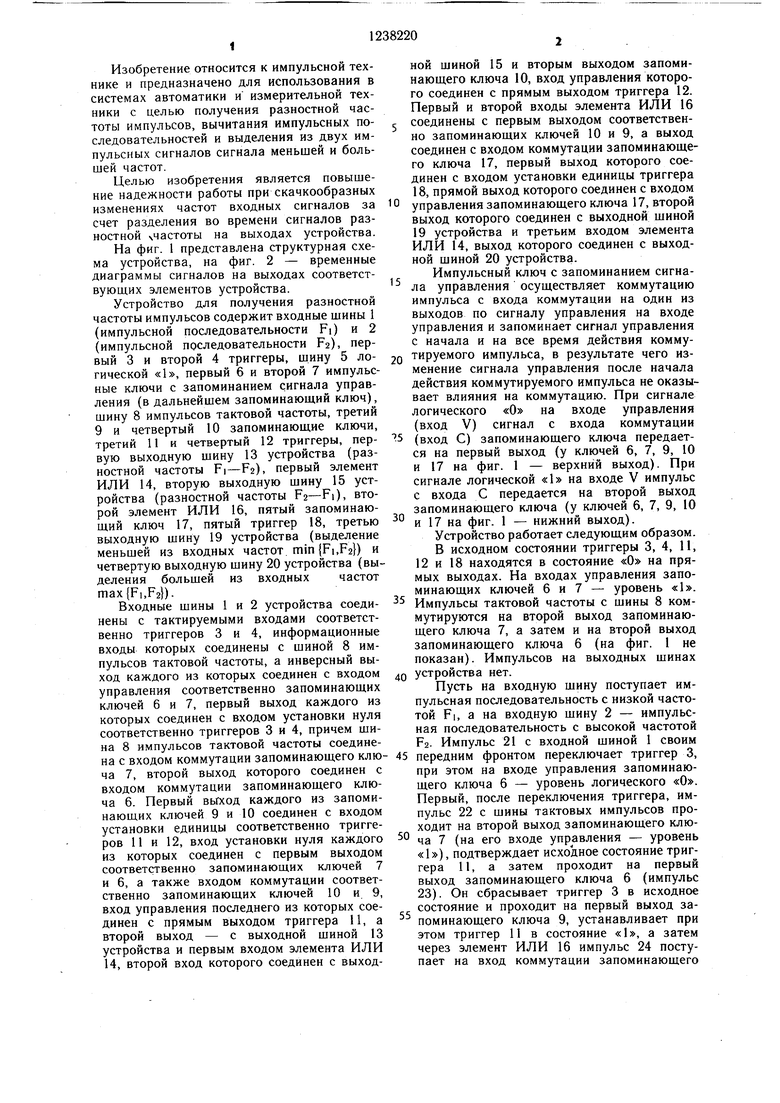

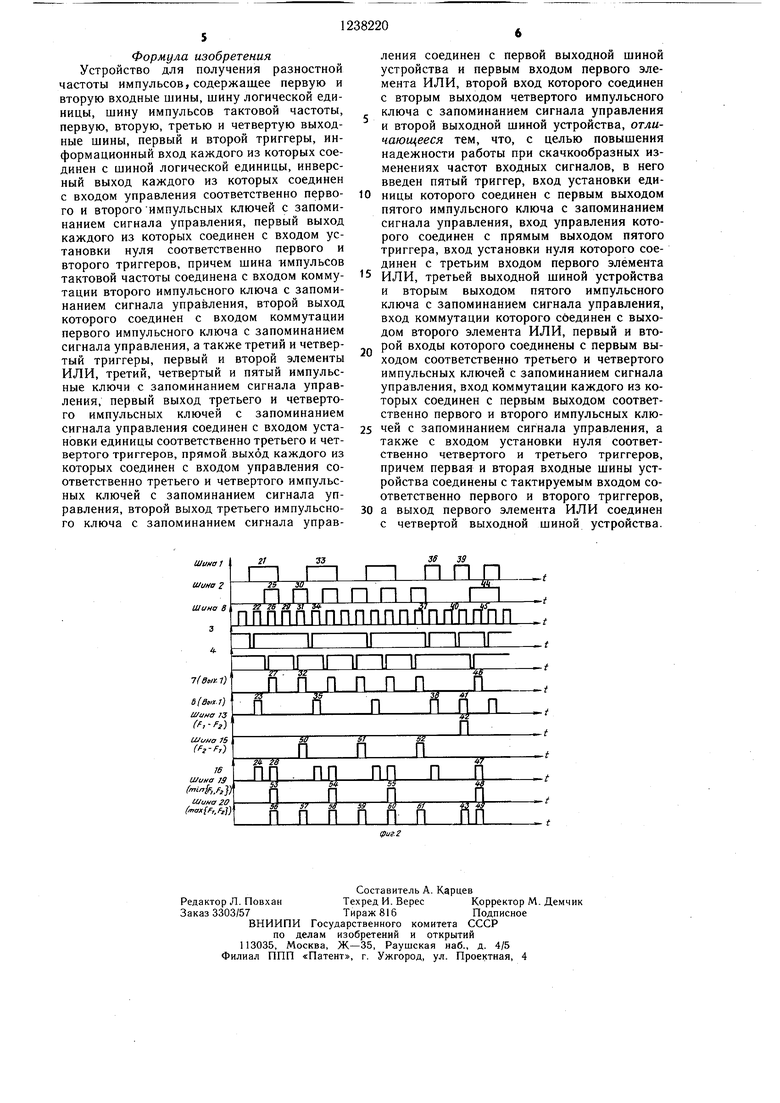

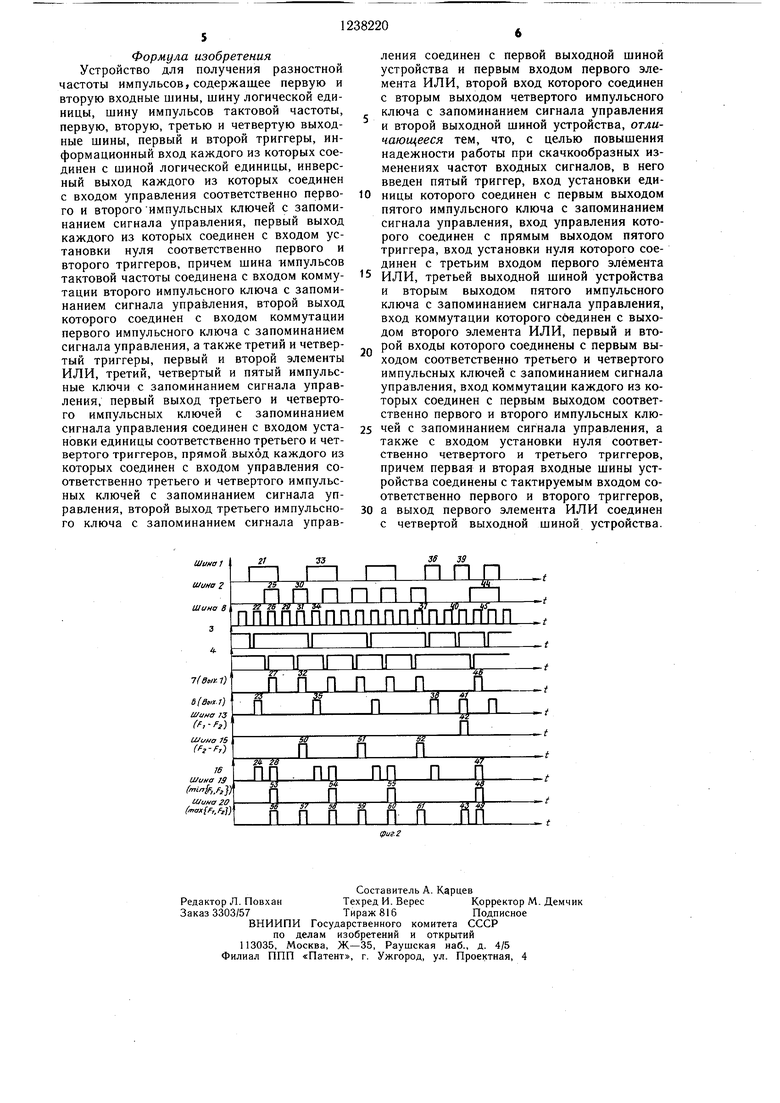

На фиг. 1 представлена структурная схема устройства, на фиг. 2 - временные диаграммы сигналов на выходах соответствующих элементов устройства.

Устройство для получения разностной частоты импульсов содержит входные шины 1 (импульсной последовательности FI) и 2 (импульсной последовательности р2), первый 3 и второй 4 триггеры, шину 5 логической «1, первый 6 и второй 7 импульсные ключи с запоминанием сигнала управления (в дальнейшем запоминающий ключ), шину 8 импульсов тактовой частоты, третий 9 и четвертый 10 запоминающие ключи, третий 11 и четвертый 12 триггеры, первую выходную шину 13 устройства (разностной частоты FI-р2), первый элемент ИЛИ 14, вторую выходную шину 15 устройства (разностной частоты ), второй элемент ИЛИ 16, пятый запоминающий ключ 17, пятый триггер 18, третью выходную шину 19 устройства (выделение меньшей из входных частот, min {Fi,F2}) и четвертую выходную шину 20 устройства (выделения большей из входных частот max{Fi,F2}).

Входные шины 1 и 2 устройства соединены с тактируемыми входами соответственно триггеров 3 и 4, информационные входы которых соединены с шиной 8 импульсов тактовой частоты, а инверсный выход каждого из которых соединен с входом управления соответственно запоминающих ключей 6 и 7, первый выход каждого из которых соединен с входом установки нуля соответственно триггеров 3 и 4, причем шина 8 импульсов тактовой частоты соединена с входом коммутации запоминающего ключа 7, второй выход которого соединен с входом коммутации запоминающего ключа 6. Первый выход каждого из запоминающих ключей 9 и 10 соединен с входом установки единицы соответственно триггеров 11 и 12, вход установки нуля каждого из которых соединен с первым выходом соответственно запоминающих ключей 7 и 6, а также входом коммутации соответственно запоминающих ключей 10 и 9, вход управления последнего из которых соединен с прямым выходом триггера 11, а второй выход - с выходной щнной 13 устройства и первым входом элемента ИЛИ 14, второй вход которого соединен с выход5

НОЙ шиной 15 и вторым выходом запоминающего ключа 10, вход управления которого соединен с прямым выходом триггера 12. Первый и второй входы элемента ИЛИ 16 соединены с первым выходом соответственно запоминающих ключей 10 и 9, а выход соединен с входом коммутации запоминающего ключа 17, первый выход которого соединен с входом установки единицы триггера 18, прямой выход которого соединен с входом

управления запоминающего ключа 17, второй выход которого соединен с выходной щиной 19 устройства и третьим входом элемента ИЛИ 14, выход которого соединен с выходной шиной 20 устройства.

Импульсный ключ с запоминанием сигнала управления осуществляет коммутацию импульса с входа коммутации на один из выходов по сигналу управления на входе управления и запоминает сигиал управления с начала и на все время действия коммуQ тируемого импульса, в результате чего изменение сигнала управления после начала действия коммутируемого импульса не оказывает влияния на коммутацию. При сигнале логического «О на входе управления (вход V) сигнал с входа коммутации

5 (вход С) запоминающего ключа передается на первый выход (у ключей 6, 7, 9, 10 и 17 на фиг. 1 - верхний выход). При сигнале логической «1 на входе V импульс с входа С передается на второй выход запоминающего ключа (у ключей 6, 7, 9, 10 и 17 на фиг. 1 - нижний выход).

Устройство работает следующим образом. В исходном состоянии триггеры 3, 4, 11, 12 и 18 находятся в состояние «О на прямых выходах. На входах управления запоминающих ключей 6 и 7 - уровень «Ь.

Импульсы тактовой частоты с шины 8 коммутируются на второй выход запоминающего ключа 7, а затем и на второй выход запоминающего ключа 6 (на фиг. 1 не показан). Импульсов на выходных шинах

0 устройства нет.

Пусть на входную щину поступает импульсная последовательность с низкой частотой FI, а на входную шину 2 - импульсная последовательность с высокой частотой F2. Импульс 21 с входной шиной 1 своим

5 передним фронтом переключает триггер 3, при этом на входе управления запоминающего ключа 6 - уровень логического «О. Первый, после переключения триггера, импульс 22 с шины тактовых импульсов проходит на второй выход запоминающего клю ча 7 (на его входе управления - уровень «1), подтверждает исходное состояние триггера 11, а затем проходит на первый выход запоминающего ключа 6 (импульс 23). Он сбрасывает триггер 3 в исходное состояние и проходит на первый выход запоминающего ключа 9, устанавливает при этом триггер 11 в состояние «1, а затем через элемент ИЛИ 16 импульс 24 поступает на вход коммутации запоминающего

0

5

ключа 17. Отсюда он проходит на его первый выход и устанавливает триггер 18 в состояние «1. Поступивший затем на входную шину 2 импульс 25 своим фронтом переключает триггер 4, а последующий за этим импульс тактовой частоты 26 проходит на первый выход запоминающего ключа 7, так как на его входе управления уровень «О. Отсюда импульс 27 устанавливает в исходное состояние триггеры 4 и 11 и поступает на первый выход запоминающего ключа 10. При этом триггер 12 устанавливается в состояние «1, а через элемент ИЛИ 16 импульс 28 поступает на запоминающий ключ 17, и, так как на его входе управления уровень «1, то он проходит на его второй выход. Отсюда импульс поступает на выходную щину 19, устанавливает триггер 18 в исходное состояние и через элемент ИЛИ 14 проходит на выходную щину 20. Они сигнализируют, что на входы поступили сигналы низкой и высокой частот.

Так как триггеры 3 и 4 к приходу следующего тактового импульса 29 находятся в исходном состоянии, то он проходит на второй выход запоминающего ключа 7, а затем на второй выход запоминающего ключа 6. Следующий входной импульс высокой частоты 30 снова переключает триггер 4, тогда первый после этого импульс тактовой частоты 31 проходит на первый выход запоминающего ключа 7 (импульс 32), который возвращает триггер 4 в исходное состояние. Так как на входе управления запоминающего ключа 10 уровень «1 с триггера 12, то импульс 32 поступает на второй выход запоминающего ключа 10, а оттуда на выходную щину 15 и через элемент ИЛИ 16, на выходную щину 20. Они сигнализируют о том, что частота последовательности р2 больще частоты Fi. Если затем поступает импульс низкой частоты 33, то он переключает триггер 3, и поэтому импульс тактовой частоты 34 проходит через запоминающие ключи 7 и 6 на первый выход последнего, так как на входе управления запоминающего ключа 7 уровень «1, а на запоминающем ключе 6 уровень «О. Импульс 35 с выхода запоминающего ключа 6 устанавливает в исходное состояние триггеры 3 и 12 и, пройдя на первый выход запоминающего ключа 9, устанавливает триггер 11 в состояние «I, а затем через элемент ИЛИ 16 и запоминающий ключ 17 - триггер 18. После поступления следующего импульса высокой частоты цикл работы устройства повторяется.

Если в какой-то момент происходит резкое изменение входных частот и, например, на входную щину 1 поступают импульсы высокой частоты, а на входную щину 2 - импульсы низкой частоты, то устройство работает следующим образом.

Первый импульс высокой частоты 36 с входной щины 1 переключает триггер 3, а

5

импульс тактовой частоты 37 проходит на первый выход запоминающего ключа 6 (так как на входе управления запоминающего ключа 7 - уровень «1). Импульс 38 устанавливает в исходном состоянии триггеры 3 и 12 и проходит на первый выход запоминающего ключа 9. Здесь он устанавливает триггер 11 в состояние «1, а, затем, через элемент ИЛИ 16 и запоминающий ключ 17 (на его входе управления уро0 вень «О) - триггер 18. Если затем снова поступает импульс высокой частоты 39, то он снова переключает триггер 3, и следующий после этого импульс тактовой частоты 40 опять проходит на первый выход запоминающего ключа 6. Триггер 3 снова возвращается в исходное состояние. Отсюда импульс 41 проходит на второй выход запоминающего ключа 9, так как на его входе управления уровень «1, и поступает на выходные шины 13 (импульс 42),

0 и через элемент ИЛИ 14 - на щину 20 (импульс 43). Они сигнализируют о том, что частота импульсной последовательности FI больще и разностная частота равна FI - Fg. Поступивщий затем с входной шины 2 импульс низкой частоты 44 переключает триг5 гер 4. Импульс тактовой частоты 45 передается на первый выход запоминающего ключа 7 (импульс 46). Он сбрасывает в исходное состояние триггеры 4 и 11, проходит на первый выход запоминающего ключа 10 и далее через элемент ИЛИ 16 (им0 пульс 47) -- на запоминающий ключ 17. Так как на его входе управления уровень «1, то этот импульс проходит на второй выход запоминающего ключа 17. Далее он поступает на выходные шины 19 (импульс 48) и через элемент ИЛИ 14 - на шину 20

(импульс 49). Они сигнализируют о наличии импульсов низкой и высокой частот на входах устройства. Далее цикл работы повторяется.

0 Из временных диаграмм (фиг. 2) видно, что, если импульсная последовательность FI имеет частоту меньше, чем импульсная последовательность F2, то на выходах устройства формируются сигналы разностной частоты р2-FI (импульсы 50, 51 и 52),

5 меньщей FI (импульсы 53, 54, 55) и большей F2 (импульсы 56, 57, 58, ... 61) частот. Если импульсная последовательность FI имеет частоту больше, чем импульсная последовательность F2, то формируются сигналы разностной частоты FI-F2 (импульс 42), мень шей FZ (импульс 48) и большей FI (импульсы 43, 49) частот.

Таким образом, предлагаемое устройство позволяет при скачкообразном изменении частот входных импульсных последовательностей формировать выходные сигналы разностных частот, не совпадающими во времени (в прототипе они могут перекрываться), в результате чего повышается достоверность выделяемых сигналов большей частоты.

Формула изобретения Устройство для получения разностной частоты импульсов, содержащее первую и вторую входные шины, шину логической единицы, шину импульсов тактовой частоты, первую, вторую, третью и четвертую выходные шины, первый и второй триггеры, информационный вход каждого из которых соединен с шиной логической единицы, инверсный выход каждого из которых соединен с входом управления соответственно первого и второго импульсных ключей с запоминанием сигнала управления, первый выход каждого из которых соединен с входом установки нуля соответственно первого и второго триггеров, причем шина импульсов тактовой частоты соединена с входом коммутации второго импульсного ключа с запоминанием сигнала управления, второй выход которого соединен с входом коммутации первого импульсного ключа с запоминанием сигнала управления, а также третий и четвертый триггеры, первый и второй элементы ИЛИ, третий, четвертый и пятый импульсные ключи с запоминанием сигнала управления, первый выход третьего и четвертого импульсных ключей с запоминанием сигнала управления соединен с входом установки единицы соответственно третьего и четвертого триггеров, прямой выход каждого из которых соединен с входом управления соответственно третьего и четвертого импульсных ключей с запоминанием сигнала управления, второй выход третьего импульсного ключа с запоминанием сигнала управления соединен с первой выходной шиной устройства и первым входом первого элемента ИЛИ, второй вход которого соединен с вторым выходом четвертого импульсного ключа с запоминанием сигнала управления и второй выходной шиной устройства, отличающееся тем, что, с целью повышения надежности работы при скачкообразных изменениях частот входных сигналов, в него введен пятый триггер, вход установки единицы которого соединен с первым выходом пятого импульсного ключа с запоминанием сигнала управления, вход управления которого соединен с прямым выходом пятого триггера, вход установки нуля которого соединен с третьим входом первого элемента

5 ИЛИ, третьей выходной шиной устройства и вторым выходом пятого импульсного ключа с запоминанием сигнала управления, вход коммутации которого соединен с выходом второго элемента ИЛИ, первый и вто рой входы которого соединены с первым выходом соответственно третьего и четвертого импульсных ключей с запоминанием сигнала управления, вход коммутации каждого из которых соединен с первым выходом соответственно первого и второго импульсных ключей с запоминанием сигнала управления, а также с входом установки нуля соответственно четвертого и третьего триггеров, причем первая и вторая входные шины устройства соединены с тактируемым входом соответственно первого и второго триггеров,

0 а выход первого элемента ИЛИ соединен с четвертой выходной шиной устройства.

Изобретение относится к импульсной технике. Может использоваться в системах автоматики и измерительной техники для получения разностной частоты импульсов, вычитания импульсных последовательностей и выделения из двух импульсных сигналов сигнала меньшей или большей частоты. Цель изобретения - повышение надежности работы устройства при скачкообразных изменениях частоты входных сигналов - достигается путем разделения во времени сигналов разностной частоты на выходах устройств. Для этого в устройство введен триггер 18. Устройство, кроме того, .содержит входные шнны 1 и 2, триггеры 3, 4, 11 и 12, шину 5 логической единицы, импульсные ключи 6 и 7 с запоминанием сигнала управления, шину 8 импульсов тактовой частоты, запоминающие ключи 9, 10 и 17, выходные шинь 13 и 15, и 19 и 20, логические элементы ИЛИ 14 и 16. Устройство позволяет при скачкообразном изменении частот входных импульсных последовательностей формировать выходные сигналы разностных частот, не совпадаюш.ими во времени. Это повышает достоверность выделяемых сигналов большой частоты. 2 ил. i (Л to со 00 1C to

| Устройство для получения разностнойчАСТОТы иМпульСОВ | 1979 |

|

SU847504A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Устройство для получения разностной частоты импульсов (его варианты) | 1981 |

|

SU978337A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Климов в | |||

| В | |||

| Импульсные ключи в цифровых устройствах, М.: Радио и связь, 1984, с | |||

| Способ обработки медных солей нафтеновых кислот | 1923 |

|

SU30A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

Авторы

Даты

1986-06-15—Публикация

1984-03-22—Подача