1

Изобретение относится вычислительной технике и частности, использовано в

к автоматике и может быть, в цифровой измерительной технике, например, в цифровых во/1ьтметрах.

Цель изобретения - иовьииешш точности преобразования мгновенных значений сигналов нри одновременном обесиеч ении готовности аналого-цифрового преобразователя (АЦП) к работе в любой момент времени по окончании нредыдущего преобразования.

Ца фиг. 1 изображена структурная схема 1федлагае.мо1-о АЦЦ; на фиг. 2 - структурная схема преобразующего каскада,вариант; на фиг. 3 -- структурная схе.ма второго за- номинаюш.его устройства; на фи1 4 - блок управления; на фиг. 5 - временные диаграммы, поясняющие работу АЦП.

Устройство содержит переключатель 1, заноминающее устройство (ЗУ) 2, выход которого соединен с входо.м 3 ЗУ 4, yse. i 5 коррекции, выход которого соединен с входом 6 ЗУ 4, выход которого подключен к входу 7 преобразующего каскада 8 с ана- .логовым выходом 9, нерек. ночатель 10, блок 11 управления с управляющими выхо- да.ми 12-18, цифровым входом 19, подключенным к выходу 20, преобразуюи1его каскада 8, у которого ,ляюпи1Й вход 21 сое- дипен с выходом 18 блока И унравления, а выход 22 ЯЕЗляется выходной 1пиной. Узел 5 коррекции содержит ключи 23 и 24 и конденсатор 25. Преобразующий каскад 8 может быть выполнен как показано па фиг. 2 и содержит вычитающее устройство 26, первый вход которого является входом 7 преобразующего каскада 8, усилитель 27 и блок 28 коррекции дрейфа, выполненный по классической схеме Принца, блок 29 сравнения, циф- роаналоговый преобразователь (ЦАП) 30, последовательно соединенные тактовый генератор 31, управляющий вход которого подключен к тине «Пуск АЦП, и счетчик 32, группа вьгходов которого подключена к входам нрограммируе.мого импульсного блока 33 и является группой выходов 20 преобразующего каскада 8, триггеры 34-37 и эле- ме1ггы И 38-41 (по числу разрядов ЦАГ1 30) первые входы элементов И объединены и подключены к выходу блока 29 сравнения, а выходы подключены к первым входам триггеров, вторые входы которых подключены соответственно к выходам 42--45 блока 33, вторые входы элементов И 38-41 подключены соответственно к выходам 43-46 блока 33, выходы триггеров 34-37 подключены к входам ЦАП i30 и являются групной выходов 22 нреобразуюп1его каскада 8. выходы 47 и 48 блока 33 подключен) соответственно к унрав;1яю цему входу блока 29 сравнения и к входу узла 49 сброса. Програ.ммируе.мый импульсный блок 33 может быть реализован

5

на микросхеме 556РТ5, при этом выводы АО-А .микросхемы соответствуют входам блока 33, а ее выводы DO-D - выходам 42-48 блока 33, а временные диаграммы фиг. 5 лс однозначно определяют алго ритм работы блока 33.

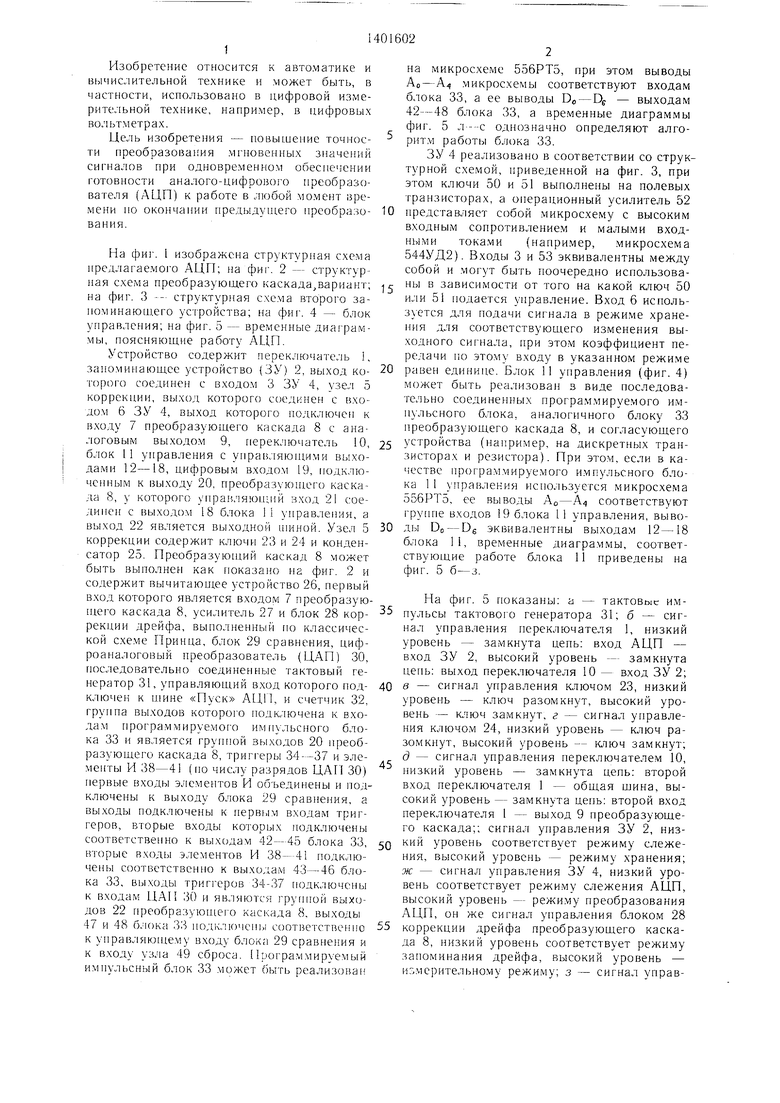

ЗУ 4 реализовано в соответствии со структурной схемой, приведенной на фиг. 3, при этом ключи 50 и 51 выполнены на полевых транзисторах, а операционный усилитель 52

0 представляет собой микросхему с высоким входным сонротивлением и малыми входными токами (например, .микросхема 544УД2). Входы 3 и 53 эквивалентны между собой и .могут быть поочередно использованы в зависимости от того на какой ключ 50 или 51 подается управление. Вход 6 используется для нодачи сигнала в режи.ме хранения для соответствующего изменения выходного сигнала, при этом коэффициент передачи но этому входу в указанном режиме

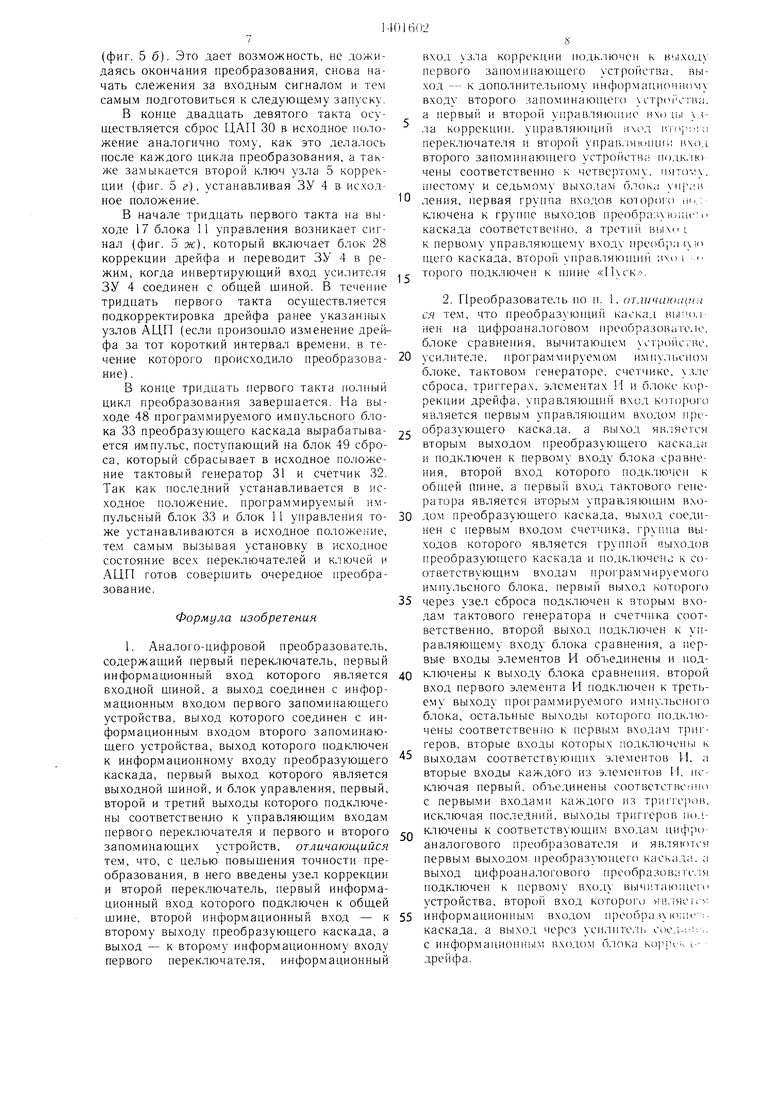

0 равен единице. Блок 11 управления (фиг. 4) может быть реализован в виде последовательно соединенных програ.м.мируемого им- нульсного блока, аналогичного блоку 33 преобразующего каскада 8, и согласующего

5 устройства (например, на дискретных транзисторах и резистора). При это.м, если в качестве программируемого импульсного блока 1 1 управления используется микросхема 556РТ5, ее выводы АО-А соответствуют rpymie входов 19 блока 11 управления, выво0 ды DO - Dg эквивалентны выходам 12-18 блока 11, временные диаграммы, соответствующие работе блока 11 приведены на фиг. 5 б-3.

На фиг. 5 показаны: а - тактовшс и.м- 5 иульсы тактового генератора 31; б - сигнал управления переключателя 1, низкий уровень - замкнута цепь: вход АЦП - вход ЗУ 2, высокий уровень - замкнута цепь: выход переключателя 10 - вход ЗУ 2; 0 в - сигнал управления к„1ючом 23, низкий уровень - ключ разомкнут, высокий уровень - ключ замкнут, г - сигнал управления ключом 24, низкий уровень - ключ разомкнут, высокий уровень - ключ замкнут; д - сигнал управления переключателем 10, низкий уровень - замкнута цепь: второй вход переключателя 1 - общая щина, высокий уровень - замкнута цепь: второй вход переключателя I - выход 9 преобразующего каскада;; сигнал управления ЗУ 2, низкий уровень соответствует режиму слежения, высокий уровень - режиму хранения; ж - сигнал управления ЗУ 4, низкий уровень соответствует режи.му слежения АЦП, высокий уровень - режиму преобразования АЦП, он же сигнал управления блоком 28 5 коррекции дрейфа преобразующего каскада 8, низкий уровень соответствует режиму запоминания дрейфа, высокий уровень - измерительному режиму; з - сигнал управ5

0

3

ления ЗУ 4, низкий р -. Нень соотвсч стнуе режиму слежении но входу 3, высокий уровень - режиму хранения по «оду 3; и выходной сигнал ЗУ 2, соответствующий :iiia- чению аналогового сигнала, равного 3,529 В; /с - выходной сигнал ЗУ 4, соответствующий значению аналоговогт) сигнала, равмсли 3,529 В; л - сигнал включения трип ера 34; м - сигнал выключения триггера 34 и включения триггера 35; н - сигнал выключения триггера 35 и включения триггера 36; о сигнал выключения триггера 36 и включения триггера 37; п - сигнал выключения триггера 37; р - сигнал уиравления бло- ко,м 29 сравнения, обозначающий время, когда он должен определить нолярность входного сигнала (нервый имиульс) и сбросить ЦАП 30 3 исходное состояние последующие имиульсы; с - сигнал на входе узла 49 сброса, иоявление короткого имиульса соответствует моменту сброса,

Уиравляющие сигналы фиг, 5 б-з вырабатывает блок 11 управления, а уиравляю щие сигналы фиг, 5 л-с - программируемый импульсный блок 33 преобразующего каскада 8,

Преобразователь работает следуюни1м об разом.

До прихода импульса запуска с шины «Пуск входной сигнал через переключатель 1 подается на вход ЗУ 2, находящего ся в состоянии слежения за входным сигналом и вырабатывающего на своем выходе напряжение, пропорциональное входному сигналу, В составе вьгходного напряжения ЗУ 2 (фиг, 5 и), кроме указанного по, ;езио- го сигнала, имеется ои нал, 011реде,,1й начальным смещением и дрейфом yKaisaiiuo- го устройства,

В этом же время 3i 4 от выхода ЗУ 2 отключено (ключ 50 разомкну.) и подключено к общей щине (ключ 51 замкнут). Вход 6 ЗУ 4 через замкнутый ключ 24 подключен к общей щине. На вы,ходе ЗУ 4 вь фабатыва- ется напряжение, эквивалентное его началь но,му смещению и дрейфу,

В тоже время (до прихода импул1А а запуска) блок 28 коррекции дрейфа преобразующего каскада 8 включен, В результате чего в нем запоминается суммарньп эквивалентный дрейф (а также начальные смещения) всех узлов, за исключением дрейфа (и начального смещения) ЗУ 2, К числу узлов, охватыаемых коррекцией за счет блока 28 коррекции дрейфа, относятся: ЗУ 4, вычитающее устройство 26, усилитель 27, ЦАП 30, а также сам блок 28 коррекции дрейфа,

В указанном 10,1ожении ,ПГ1 все1 да готов начать процесс преобразования, если придет импульс запуска с тины «Пуск.

Работа АПП ос ществляется по такгам (фиг, 5), число тактов составляет 31 и соот

к)ихи:и1 :iMi.;

ичюхо; ЗЛ 2 к ре/ким хранеi:;: i. ... ;:, и гсче:И1г i;cp:iOi4 гакта (ciiii. 5 el, переход ЛИП в режим преобра- зопания за счет перек, юченпя блока 28 коррекции дрейфа из режима запоминания дрейфа в режим, когда дрейф комиенсируется сигна.юм, по,1ученным в режиме запоминания, этот режим длится 30 тактов, (фи. 5 ж. переход ЗУ 4 в режим слеженпя за на вы.чоде ЗУ 2, дляп1егося в течепие первого такта (фиг. 5 л), переключение переключателя 1 (фиг. 5 б) в полон е- ние, когда вход ЗУ 2 от источника си1 нала отк,1ючается и иодк. почается через переклю- чате, Пз 10 к общей п.п1не, тем самым осуще- ств,тяется подготовка к ио,тучению на выходе ЗУ 2 сигнала, равного дрейфу этого устройства, когда оно перейдет в режим слежения.

30

45

50

К концу первого такта на выходе ЗУ 4 1о, 1учеп сигна,, еодержаший сумму полез- 25 ного с 1гнала и дрейфа ЗУ 2,

В начале второго такта ЗУ 4 переходит в режим хранения (фи.г, 5 :,), а ЗУ 2 - в режим слежения (фиг. 5 е. Наряду с этим BTOpoi i ключ уз, ;а 5 коррекции размыкается (фи 5 г), а er;i первый ключ замыкается (фиг. 5 е). В результате этого дрейф 3N 2 |1одается на конденсатор узла 5 коррекции и одновременно на вход б ЗУ 4, последнее В1,1полнено так, ч(1 сигнал дрейфа (фиг, 3), i o;u HHbui на его вход 6, вычитае, ся 1:3 выходного сигнала это1 о устройства, В резуль тате этого к концу второго такта на вых(хче ЗУ 4 станав,:: 11зается только по, 1езны: 1 си1- нал, iie содержащг дрейф 3,Х 2, К концу BTOpoi o такта 1ервь1Й к, поч зла 5 коррекции размыкается (. 5 в), а его BTopoi i к,тюм

40 остается разомкнутым (фиг. 5 г, конден,са- тор узла 5 коррекции хранит и.нформацик. о дрейфе 3i 2 в течение неоохс дих; ): о кп.щ- чества тактов, те%; самьп сч ра;:;;я oi nxi - димое начальное cocTOHinie J.N . ; . :: тем временем готово выио,1 1ять -..-.- . щие оиерации.

В третьем такте но г;ервом - имг1у,1ьс н, выхо.те 47 ирогра.мир емого им;1у, 1ьс:1ого б, 1ока 33 (фи1 , 5 р) , ;яется нсхтя.р- ность ВЫХОДПО1Ч) сиг нала 4 la , полярность преобразуемого cnnui ia), . чего ЗУ 4, Г1рой;1я вычитак щее устройство 26, усм;;;1те,1ь 27, riocrx iiaeT н;-. б.юк 29 сравнениз:, и котс ром .iec; в.. .ястся. операция oiipc именин 11;). ч;) ; iii; ре- 55 зу, 1 татам опре.чс.;. lio.wipiii-c , n. ic:-. : ч cpaiine iiui пК:: ;а, :; : . .

И()С : Ь Ич ; O : i; : :{ - :- i .V , ,., - :{. X(.lMiUei-iH-5; :i V-:H; г,:;;,, i i : .-

10

В течение четвертого, пятого, шестого и седьмого тактов осуахестатяется поразрядное кодирование для получения первого самого старшего десятичного разряда.

В начале четвертого такта программируемый импульсный блок 33 на выходе 42 вырабатывает сигнал (фиг. 5 л), который включает триггер 34, в результате чего на выходе ЦАП 30 появляется опорное напряжение с весовым коэффициентом, равным 0,8. Это напряжение вычитается из выходного напряжения ЗУ 4 с помошью вычитаюп его устройства 26, и полученная разность усиливается в 10 раз уситителем 27. Блок 29 сравнения оценивает знак этой разности. К концу четвертого такта могут иметь место -, два случая.

Первый случай - опорное напряжение больше преобразуемого напряжения, т. е. разность между сигналом и опорным напряжением отрицательная, тогда блок 29 сравнения вырабатывает сигнал, способствующий возврату триггера 34 в исходное состояние, этот сигнал поступает на один из входов элемента И 38. На второй вход элемента И 38 с выхода 43 программируемого им20

ряемы.м сигналом и совокупностью опорных напряжений с весовыми коэффициентами 0,4; 0,2; 0,1. Соответствующие эпюры приведены на фиг. 5 м-п. К началу восьмого такта образуется некоторая совокупнось состояний триггеров 34-37, являющихся кодом старшего десятичного разряда. Этот код подается на выход АЦП.

В начале восьмого такта, когда уже принято решение оставить нлк не оставить включенным опорное напряжение с последним весовым коэффициентом 0,1, на ЗУ 2 подается сигнал с выхода 9 преобразующего каскада 8 путем переключения переключателя 10 (фиг. 5 d). В конце восьмого такта после достижения установившегося значения на выходе преобразующего каскада 8, имеющего коэффициент усиления 10, образуется усиленная в 10 раз разность между измеряе- мы.м сигналом и совокупностью опорных напряжений. Эта разность записывается в ЗУ 2 (напо.минаем - переключатель 10 находится в нужно.м положении), при этом на выходе ЗУ 2 имеется его дрейф (как и в описанном случае, имеющим место до момента запуска АПП). В начале десятого такпульсного блока 33 в конце четвертого так- 25 та переключатель 10 отключает вход ЗУ 2

та подается сигнал опроса (фиг. 5л}, триггер 34 возвращается в исходное состояние, тем самым снимая выходное напряжение на выходе ЦАП 30, опорное напряжение с ве- совы.м коэффициентом 0,8 отключается от вычитающего устройства 26.

Второй случай - опорное напряжение меньше преобразуемого напряжения, т. е. разность .между сигналом и опорным напряжением положительная, блок 29 сравнения не вырабатывает сигнал, способствующий

от выхода 9 преобразующего каскада 8 и подключает его к общей щине (фиг. 5 д). Одновременно с этим ЗУ 2 переходит в режим хранения (фиг. 5 е), а ЗУ 4 - в режим слежения (фиг. 5 з), осуществляется 30 перезапись разностного сигнала с ЗУ 2 в ЗУ 4 (совместно с дрейфом ЗУ 2). Ключ 24 замкнут (фиг. 5 г) и создает при этом исходное положение ЗУ 4 таки.м, каким оно было до момента запуска АЦП.

В начале десятого такта ЗУ 4 переходит

возврату триггера 34 в ис.ходное положение, 35 в режим хранения (фиг. 5 з), а ЗУ 2 - в поэтому при появлении сигнала опроса срежим слежения (фиг. 5 е). Наряду с этим

выхода 43 программируемого импульсногоключ 24 размыкается (фиг. 5 г), а ключ 23

блока 33 триггер 34 остается во включенномзамыкается (фиг. 5 в). В течение десятого

состоянии, опорное напряжение с весовымтакта осуществляется вычитание дрейфа

коэффициентом 0,8 остается подключенным 40 к вычитающему устройству 26. Сигнал опроса, возникающий в конце четвертого такта на выходе 43 программируемого импульсного блока 33, одновременно является сигналом

45

включения следующего триггера 35, которому предписывается весовой коэффициент опорного 1апряжения, равный 0,4.

В пятом, щесто.м и седьмом тактах осуществляется аналогичная процедура, при это.м в работе участвуют соответственно триггер 35 и элемент И 39, триггер 36 и 50 элемент И 40, триггер 37 и элемент И 41, каждый предыдущий выход программируе- .мого им |ульсного блока 33 осуществляет включение соответствующего триггера, каждый последующий выход - отключение данного триггера, если блок 29 сравнения вы- 55 дает разрешающий сигнал, который в свою очередь имеется или отсутствует в зависимости от пoляp юcти разности между измеЗУ 2 аналогично тому, как это делалось во втором такте. Таким образом, на выходе ЗУ 4 имеется только полезный разностный сигнал (без дрейфа ЗУ 2). Одновременно в начале десятого такта осуществляется сброс в исходное состояние ЦАП 30 путем выработки сигнала на выходах 43-46 програ.м- мируемого импульсного блока 33 и сигнала сброса на выходе блока 29 сравнения, в результате чего через элементы И 38-41, триггеры 34-37 устанавливаются в исходное состояние (фиг. 5 м-р).

Начиная с одиннадцатого такта, осуществляется процесс поразрядного кодирования для получения второго более младшего разряда, затем с 18 такта следующего разряда и с 25 такта последнего самого младшего разряда.

В конце двадцать четвертого такта ЗУ 2 подключается к источнику входного сигнала путем переключения переключателя 1

0

,

0

ряемы.м сигналом и совокупностью опорных напряжений с весовыми коэффициентами 0,4; 0,2; 0,1. Соответствующие эпюры приведены на фиг. 5 м-п. К началу восьмого такта образуется некоторая совокупнось состояний триггеров 34-37, являющихся кодом старшего десятичного разряда. Этот код подается на выход АЦП.

В начале восьмого такта, когда уже принято решение оставить нлк не оставить включенным опорное напряжение с последним весовым коэффициентом 0,1, на ЗУ 2 подается сигнал с выхода 9 преобразующего каскада 8 путем переключения переключателя 10 (фиг. 5 d). В конце восьмого такта после достижения установившегося значения на выходе преобразующего каскада 8, имеющего коэффициент усиления 10, образуется усиленная в 10 раз разность между измеряе- мы.м сигналом и совокупностью опорных напряжений. Эта разность записывается в ЗУ 2 (напо.минаем - переключатель 10 находится в нужно.м положении), при этом на выходе ЗУ 2 имеется его дрейф (как и в описанном случае, имеющим место до момента запуска АПП). В начале десятого так5 та переключатель 10 отключает вход ЗУ 2

та переключатель 10 отключает вход ЗУ 2

от выхода 9 преобразующего каскада 8 и подключает его к общей щине (фиг. 5 д). Одновременно с этим ЗУ 2 переходит в режим хранения (фиг. 5 е), а ЗУ 4 - в режим слежения (фиг. 5 з), осуществляется перезапись разностного сигнала с ЗУ 2 в ЗУ 4 (совместно с дрейфом ЗУ 2). Ключ 24 замкнут (фиг. 5 г) и создает при этом исходное положение ЗУ 4 таки.м, каким оно было до момента запуска АЦП.

В начале десятого такта ЗУ 4 переходит

в режим хранения (фиг. 5 з), а ЗУ 2 - в режим слежения (фиг. 5 е). Наряду с этим

такта осуществляется вычитание дрейфа

0

5

0 5

ЗУ 2 аналогично тому, как это делалось во втором такте. Таким образом, на выходе ЗУ 4 имеется только полезный разностный сигнал (без дрейфа ЗУ 2). Одновременно в начале десятого такта осуществляется сброс в исходное состояние ЦАП 30 путем выработки сигнала на выходах 43-46 програ.м- мируемого импульсного блока 33 и сигнала сброса на выходе блока 29 сравнения, в результате чего через элементы И 38-41, триггеры 34-37 устанавливаются в исходное состояние (фиг. 5 м-р).

Начиная с одиннадцатого такта, осуществляется процесс поразрядного кодирования для получения второго более младшего разряда, затем с 18 такта следующего разряда и с 25 такта последнего самого младшего разряда.

В конце двадцать четвертого такта ЗУ 2 подключается к источнику входного сигнала путем переключения переключателя 1

(фиг. 5 б). Это дает возможность, не дожидаясь окончания преобразования, снова начать слежения за входным сигналом и тем самым подготовиться к следующему запуску.

В конце двадцать девятого такта осуществляется сброс ЦАП 30 в ис.ходное положение аналогично тому, как это делалось после каждого цикла преобразования, а также замыкается второй ключ узла 5 коррекции (фиг. 5 г), устанавливая ЗУ 4 в исходное положение.

В начале тридцать первого такта на выходе 17 блока 11 управления возникает сигнал (фиг. 5 ж), который включает блок 28 коррекции дрейфа и переводит ЗУ 4 в режим, когда инвертирующий вход усилителя ЗУ 4 соединен с общей щиной. В течение тридцать первого такта осуществляется подкорректировка дрейфа ранее указанных узлов АЦП (если произоилло изменение дрейфа за тот короткий интервал времени, в течение которого происходило преобразование) .

В конце тридцать первого такта полный цикл преобразования завершается. На выходе 48 программируемого импульсного блока 33 преобразующего каскада вырабатывается импульс, поступающий на блок 49 сброса, который сбрасывает в исходное положение тактовый генератор 31 и счетчик 32. Так как последний устанавливается в исходное гюложение, программируемый импульсный блок 33 и блок 11 управления тоже устанавливаются в исходное положение, тем самым вызывая установку в исходное состояние всех переключателей и ключей и АЦП готов совершить очередное преобразование.

Формула изобретения

1. Аналого-цифровой преобразователь, содержащий первый переключатель, первый инфор.мационпый вход которого является входной тиной, а выход соединен с информационным входом первого запоминающего устройства, выход которого соединен с ин- формационны.м входом второго запоминающего устройства, выход которого подключен к информационному входу преобразующего каскада, первый выход которого является выходной щипой,и блок управления, первый, второй и третий выходы которого подключены соответственло к управляющим входам первого переключателя и первого и второго запоминающих устройств, отличающийся тем, что, с целью повыщения точности преобразования, в него введены узел коррекции и второй переключатель, первый инфор.ма- ционный вход которого подключен к общей щипе, второй информационный вход - к второ.му выходу преобразующего каскада, а выход - к второму инфор.мационному входу первого переключателя, информационный

0

0

5

0

5

0 Q 5

вход узла коррекции подключен к выходу первого запоминающего устройства, ны- ход - к дополнительному информаписмшому входу второго запоминающего устр(. а первый и второй управляющие нхочы i- ла коррекции, управляющий I /i-dji;; ;; переключателя и второй управ. lixo.i второго запоминаюпгего устройств;- подк. ио чепы соответственно к четвертому, мчто .:. шестому и седьмому выхо;1ам б,1окс1 ления, первая группа входов которого IK..; к.- ючена к группе выходов преобразх кипе: м каскада соответственно, а третш ныхи i к первому управ, 1яющему npeo6jiai o щего каскада, второй управляющпГ ихо i торого подключен к шппе .-.

2. Преобразователь по п. 1, отличакпи.ии ся тем, что преобразующий каскад вы;и).1 нен на цифроаналоговом преобразова 1 ело, блоке сравнения, вычитающем устройстве, усилителе, программируемом .. 1ьспом блоке, тактовом генераторе, счетчике, хз.че сброса, триггерах, элементах II и б. юке коррекции дрейфа, управляющпй вход KOTOpoi o является первым управляющи.м входом преобразующего каскада, а выхол. яв,1яегся вторым выходом преобразующего каскада и подключен к первому входу блока сравнения, второй вход которого подк, 1ючен к обшей , а первый вход тактово1 о I ene- ратора является вторым управляющим входом преобразующего каскада, выход соединен с первым входом счетчика, rpyrina выходов которого является группой аыхо.л,ов преобразующего каскада и подключена к соответствующим входам программируемого импульсного блока, первый выход которО1Ч) через узел сброса подключен к вторым входам тактового генератора и счетчика соответственно, второй выход подключен к управляющему входу блока сравнения, а первые входы элементов И об1 единены и подключены к выходу блока сравнения, второй вход первого элемепта П подключен к третьему выходу прог раммируемого импульсного блока, остальные выходы которого подключены соответственно к первы.м входам триггеров, вторые входы которых подключены к выходам соответствующих элементов П, а вторые входы каждого из эле.ментов 11. исключая первый, об ьединены соответстч спнп с первыми входами каждого из тршч сров. исключая последний, выходы триггеров lio.i- ключены к соответствующим входам цифро- аналогового преобразователя и являются первы.м выходом преобразх ющего каскад;;. ;i выход цифроаналогово1 о прсобразов;1.гс.1я подключен к нервому входу вычитающегс

устройства, второй вход KOTOpOI O Г1 .

информационным входом npeo6p;.yi(i;;ir,. каскада, а выход через усилитель coc/i-;::; .. с информационным входом б.чока Kcu iu-i-, f дрейфа.

3.Преобразователь по п. 1, отличающийся тем, что узел коррекции выполнен па двух ключах и конденсаторе, причем информационный вход первого ключа является информационным входом узла коррекции, информационный вход второго ключа подключен к общей шине и к первому выводу конденсатора, выходы ключей соединены с вторым выводом конденсатора и являются выходом уз/ia коррекции, а управляющие входы первого и второго ключей являются первым и вторым управляющими входами узла коррекции соответственно.

4.Преобразователь по п. 1, отличающийся тем, что второе заноминаюп1ее устройство выпо;п ено па двух ключах, четырех резисторах, конденсаторе н операционном усилителе, выход которого является выходом второго запоминающего устройства и через кон

денсатор соединен с инвертирующим входом операционного усилителя, управляющие входы первого и второго ключей являются первым и вторым управляющими входами второго запоминающего устройства, выход операционного усилителя, через первый и второй резисторы подключен к общей щине, инвертирующий вход через первый ключ подключен к точке соединения первого и второго резисторов и через второй ключ к точке соединения третьего и четвертого резисторов, причем второй вывод третьего резистора является информационным входом второго запоминающего устройства, второй вывод четверто1 о резистора подключен к выходу операциоппого усилителя, неинвертирующий вход которого является дополнительным информационным входом второго запомина- юн1его устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля процесса нанесения покрытий | 1989 |

|

SU1682783A1 |

| Аналого-цифровой преобразователь | 1990 |

|

SU1730722A2 |

| Устройство аналого-цифрового преобразования | 1988 |

|

SU1501268A2 |

| Цифроаналоговая вычислительная система | 1987 |

|

SU1483468A1 |

| Система экстремального регулирования квадрупольного масс-спектрометра | 1989 |

|

SU1795419A1 |

| Электрометрический преобразователь заряда | 1986 |

|

SU1531006A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1559405A2 |

| Ультразвуковой дефектоскоп | 1989 |

|

SU1619169A1 |

| Устройство аналого-цифрового преобразования | 1987 |

|

SU1480127A1 |

| Электрометрический вольтметр | 1986 |

|

SU1413538A1 |

Изобретение относится к цифровой измерительной технике и может быть применено, в частности, в цифровых вольтметрах. Изобретение позволяет с высокой точностью преобразовывать мгновенные значения сигнала при одновременном обеспечении готовности аналого-цифрового преобразователя (АЦП) к работе в любой момент времени. В АЦП реализован принцип поразрядного уравновешивания с рециркуляцией остатка, при этом в процессе преобразования осуществляется компенсация погрешностей, вызванных дрейфом нуля всех узлов, в.чодя- щих в АЦП (в том числе дрейфа нуля за- поминаюш.его устройства, непосредственно связанного с входным сигналом). Работа взад АЦП осуществляется по тактам, полный цикл преобразования составляет, например, для четырех десятичных разрядов преобразуемого сигнала 31 такт. До прихода импульса запуска в узле 5 коррекции дрейфа запоминается суммарный эквивалентный дрейф и начальное смешен11е запоминаю- шего устройства (ЗУ) 4, вычитаюшего устройства, усилителя, цифроаналогового преобразователя (ЦАП) и самого блока 11. К концу первого такта на выходе ЗУ 4 получается суммарный сигнал (полезный и дрейф второго ЗУ 2). Во втором такте дрейф ЗУ 2 запоминается на конденсаторе 25 и подается на вход ЗУ 4, в результате чего на его выходе получается только полезный сигнал (осуществляется вычитание). В третьем такте определяется полярность выходного сигнала ЗУ 4 в блоке сравнения. В последующих тактах осуществляется поразрядное кодирование сигнала. По завершении каждого частного цикла преобразования осу- шествляется фиксация результатов преобразования по мере получения все более младших десятичных разрядов. В конце каждого частного цикла образуется разностный сигнал сравнения, который усиливается в 10 раз и используется как подстановка для преобразования в последующем частном цикле рециркуляции остатка. 3 з. п. ф-лы, 5 ил. € Nfe. о о to nycf

. г

От бых. /7 БУИ От 6ь/х /8 БУП фиг-З

Ъ

фиг.

| Аналого-цифровой преобразователь | 1981 |

|

SU945978A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Микроэлектронные цифроаналоговые и аналого-цифровые преобразователи информации./Под ред | |||

| В | |||

| Б | |||

| Смолова, 1976, с | |||

| Ледорезный аппарат | 1921 |

|

SU322A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1988-06-07—Публикация

1985-07-10—Подача