Изобретение относится к импульсной технике и может быть использовано в системах обработки сигналов частотных измерительных преобразователей.

Цель изобретения - повышение помехоустойчивости устройства.

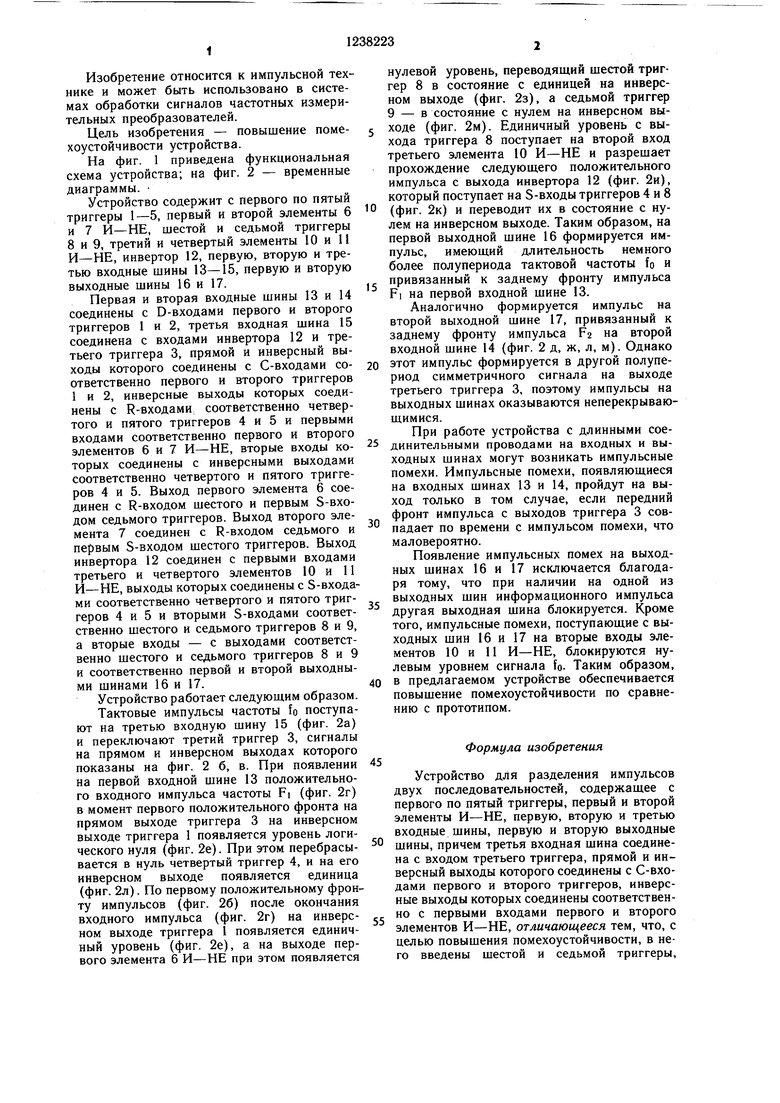

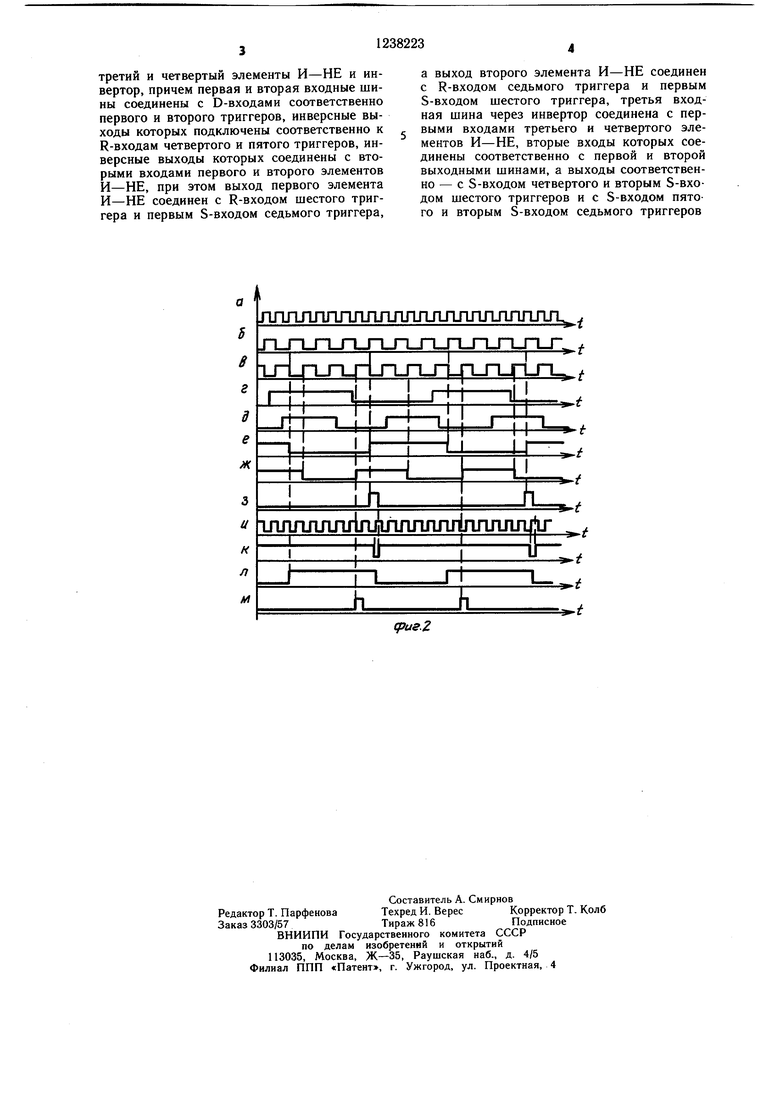

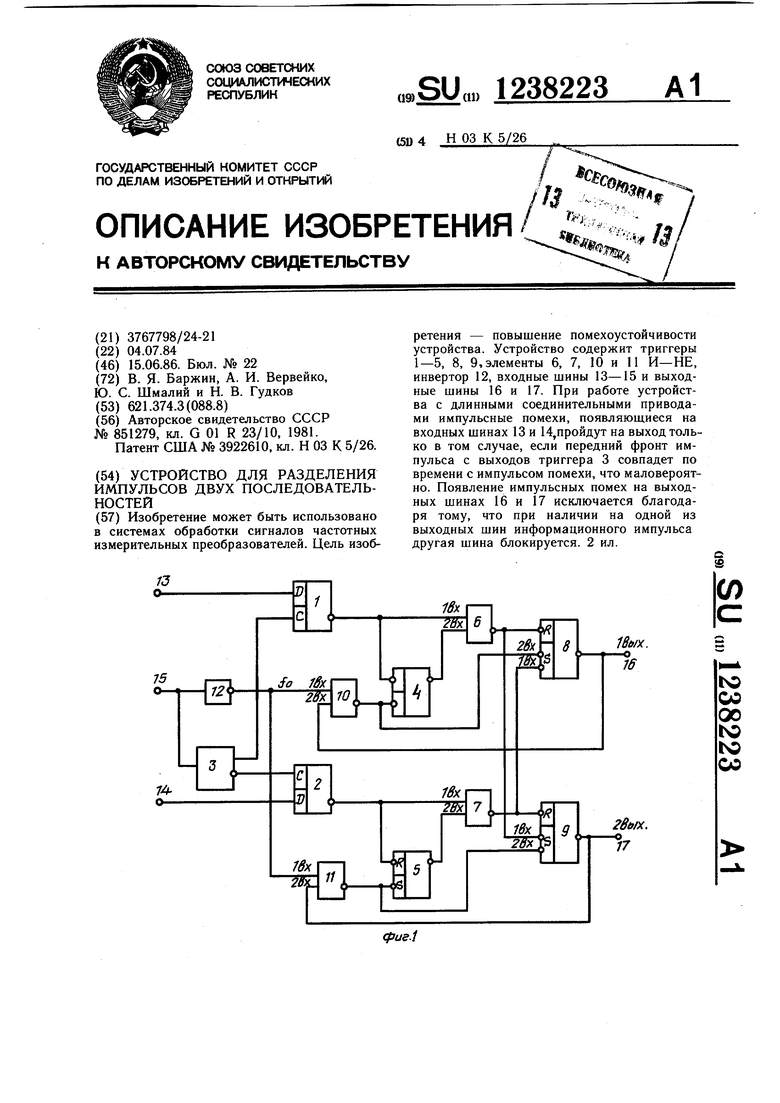

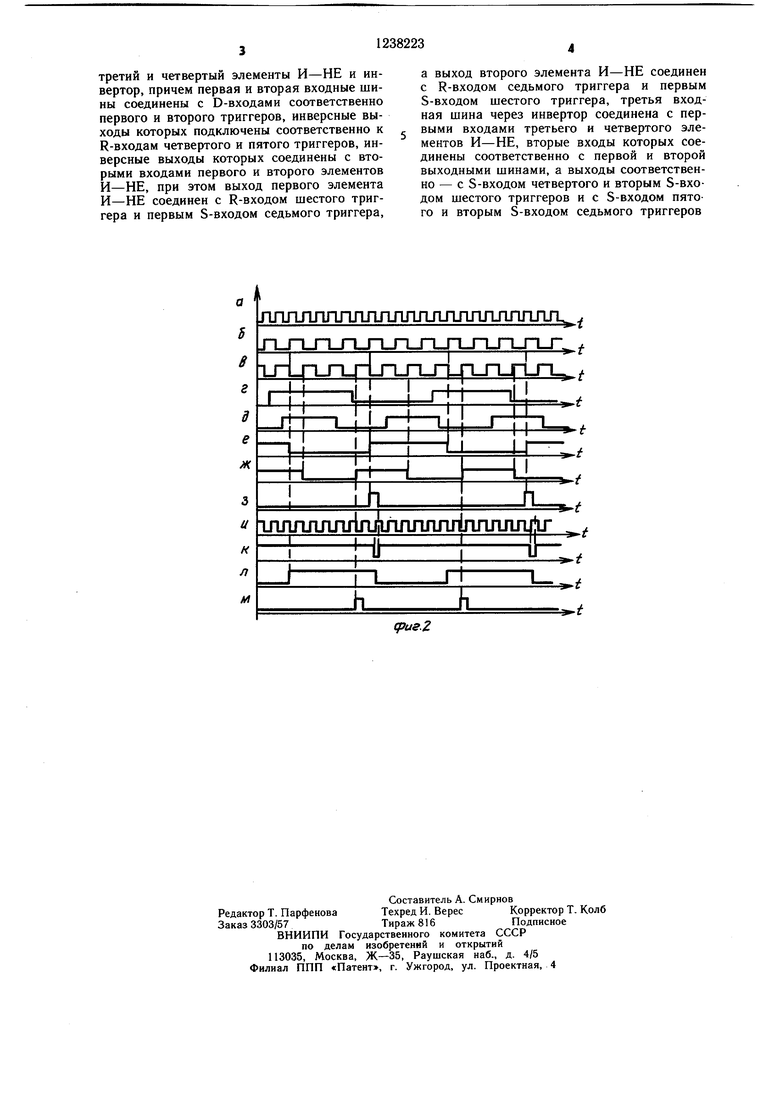

На фиг. 1 приведена функциональная схема устройства; на фиг. 2 - временные диаграммы.

Устройство содержит с первого по пятый триггеры 1-5, первый и второй элементы 6 и 7 И-НЕ, шестой и седьмой триггеры 8 и 9, третий и четвертый элементы 10 и 11 И-НЕ, инвертор 12, первую, вторую и третью входные шины 13-15, первую и вторую выходные шины 16 и 17.

Первая и вторая входные шины 13 и 14 соединены с D-входами первого и второго триггеров 1 и 2, третья входная шина 15 соединена с входами инвертора 12 и третьего триггера 3, прямой и инверсный выходы которого соединены с С-входами соответственно первого и второго триггеров 1 и 2, инверсные выходы которых соединены с R-входами соответственно четвертого и пятого триггеров 4 и 5 и первыми входами соответственно первого и второго элементов 6 и 7 И-НЕ, вторые входы которых соединены с инверсными выходами соответственно четвертого и пятого триггеров 4 и 5. Выход первого элемента 6 соединен с R-входом шестого и первым S-вхо- дом седьмого триггеров. Выход второго элемента 7 соединен с R-входом седьмого и первым S-входом шестого триггеров. Выход инвертора 12 соединен с первыми входами третьего и четвертого элементов 10 и 11 И-НЕ, выходы которых соединены с S-входа- ми соответственно четвертого и пятого триггеров 4 и 5 и вторыми S-входами соответственно шестого и седьмого триггеров 8 и 9, а вторые входы - с выходами соответственно шестого и седьмого триггеров 8 и 9 и соответственно первой и второй выходными шинами 16 и 17.

Устройство работает следуюш,им образом.

Тактовые импульсы частоты fo поступают на третью входную шину 15 (фиг. 2а) и переключают третий триггер 3, сигналы на прямом и инверсном выходах которого показаны на фиг. 2 б, в. При появлении на первой входной шине 13 положительного входного импульса частоты FI (фиг. 2г) в момент первого положительного фронта на прямом выходе триггера 3 на инверсном выходе триггера 1 появляется уровень логического нуля (фиг. 2е). При этом перебрасывается в нуль четвертый триггер 4, и на его инверсном выходе появляется единица (фиг. 2л). По первому положительному фронту импульсов (фиг. 26) после окончания входного импульса (фиг. 2г) на инверсном выходе триггера 1 появляется единичный уровень (фиг. 2е), а на выходе первого элемента 6 И-НЕ при этом появляется

нулевой уровень, переводящий шестой триггер 8 в состояние с единицей на инверсном выходе (фиг. 2з), а седьмой триггер 9 - в состояние с нулем на инверсном вы- 5 ходе (фиг. 2м). Единичный уровень с выхода триггера 8 поступает на второй вход третьего элемента 10 И-НЕ и разрешает прохождение следующего положительного импульса с выхода инвертора 12 (фиг. 2и), который поступает на S-входы триггеров 4 и 8

(фиг. 2к) и переводит их в состояние с нулем на инверсном выходе. Таким образом, на первой выходной шине 16 формируется импульс, имеющий длительность немного более полупериода тактовой частоты fo и

, привязанный к заднему фронту импульса FI на первой входной шине 13.

Аналогично формируется импульс на второй выходной шине 17, привязанный к заднему фронту импульса FZ на второй входной шине 14 (фиг. 2 д, ж, л, м). Однако

0 этот импульс формируется в другой полупериод симметричного сигнала на выходе третьего триггера 3, поэтому импульсы на выходных шинах оказываются неперекрывающимися.

При работе устройства с длинными сое5 динительными проводами на входных и выходных шинах могут возникать импульсные помехи. Импульсные помехи, появляющиеся на входных шинах 13 и 14, пройдут на выход только в том случае, если передний фронт импульса с выходов триггера 3 совпадает по времени с импульсом помехи, что маловероятно.

Появление импульсных помех на выходных шинах 16 и 17 исключается благодаря тому, что при наличии на одной из выходных шин информационного импульса другая выходная шина блокируется. Кроме того, импульсные помехи, поступающие с выходных шин 16 и 17 на вторые входы элементов 10 и 11 И-НЕ, блокируются нулевым уровнем сигнала fo. Таким образом,

в предлагаемом устройстве обеспечивается повышение помехоустойчивости по сравнению с прототипом.

0

45

Формула изобретения

Устройство для разделения импульсов двух последовательностей, содержащее с первого по пятый триггеры, первый и второй элементы И-НЕ, первую, вторую и третью входные шины, первую и вторую выходные щины, причем третья входная щина соединена с входом третьего триггера, прямой и инверсный выходы которого соединены с С-входами первого и второго триггеров, инверсные выходы которых соединены соответственно с первыми входами первого и второго элемеитов И-НЕ, отличающееся тем, что, с целью повышения помехоустойчивости, в него введены шестой и седьмой триггеры.

третий и четвертый элементы И-НЕ и инвертор, причем первая и вторая входные шины соединены с D-входами соответственно первого и второго триггеров, инверсные выходы которых подключены соответственно к R-входам четвертого и пятого триггеров, инверсные выходы которых соединены с вторыми входами первого и второго элементов И-НЕ, при этом выход первого элемента И-НЕ соединен с R-входом шестого триггера и первым S-входом седьмого триггера.

а выход второго элемента И-НЕ соединен с R-входом седьмого триггера и первым S-входом шестого триггера, третья входная шина через инвертор соединена с первыми входами третьего и четвертого элементов И-НЕ, вторые входы которых соединены соответственно с первой и второй выходными шинами, а выходы соответственно - с S-входом четвертого и вторым S-входом шестого триггеров и с S-входом пятого и вторым S-входом седьмого триггеров

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетный элемент с контролем | 1988 |

|

SU1569974A1 |

| Способ формирования частотно-импульсных сигналов датчика перемещения и устройство для его осуществления | 1976 |

|

SU905993A1 |

| Устройство для синхронизации импульсов | 1980 |

|

SU940285A1 |

| Синхронный делитель частоты | 1989 |

|

SU1651374A1 |

| ТРИГГЕРНОЕ УСТРОЙСТВО | 2003 |

|

RU2237969C1 |

| Способ воспроизведения цифровой магнитной записи | 1985 |

|

SU1282194A1 |

| Устройство для формирования импульсов разностной частоты | 1983 |

|

SU1112372A1 |

| Устройство для синхронизации сигналов | 1982 |

|

SU1069144A2 |

| Селектор информационных импульсов | 1985 |

|

SU1309289A1 |

| Кодовый трансмиттер | 1985 |

|

SU1339883A1 |

Изобретение может быть использовано в системах обработки сигналов частотных измерительных преобразователей. Цель изобретения - повышение помехоустойчивости устройства. Устройство содержит триггеры 1-5, 8, 9,элементы 6, 7, 10 и 11 И-НЕ, инвертор 12, входные шины 13-15 и выходные шины 16 и 17. При работе устройства с длинными соединительными приводами импульсные помехи, появляющиеся на входных шинах 13 и 14,пройдут на выход только в том случае, если передний фронт импульса с выходов триггера 3 совпадет по времени с импульсом помехи, что маловероятно. Появление импульсных помех на выходных шинах 16 и 17 исключается благодаря тому, что при наличии на одной из выходных шин информационного импульса другая шина блокируется. 2 ил. СЛ ND СО 00 Ю к 00

лллллллллллплллллллпплл

ггиу1Г1ЛлНп |1пллллДп .

i I К

«JП

н

н

| Цифровое устройство для обработкииНфОРМАции дВуХпАРАМЕТРОВыХ чАСТОТНыХдАТчиКОВ | 1979 |

|

SU851279A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США № 3922610, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-06-15—Публикация

1984-07-04—Подача