1

1В

| название | год | авторы | номер документа |

|---|---|---|---|

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2022 |

|

RU2789722C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2840388C1 |

| ДВОИЧНЫЙ ВЫЧИТАТЕЛЬ | 2024 |

|

RU2829014C1 |

| Устройство для измерения одиночных интервалов времени | 1986 |

|

SU1697052A1 |

| Кодирующее устройство | 1983 |

|

SU1176454A1 |

| Счетчик импульсов с цифровой индикацией | 1987 |

|

SU1478325A1 |

| Синхронный делитель на 12 | 1987 |

|

SU1517129A1 |

| Многофункциональное счетное устройство | 1979 |

|

SU819969A2 |

| Реверсивная счетная декада | 1988 |

|

SU1554141A1 |

| Десятичный счетчик | 1977 |

|

SU692094A1 |

Изобретение относится к импульсной технике и может быть использовано в устройствах автоматики и вычисли-, тельной техники. Цель изобретения - повышение помехоустойчивости за счет исключения внецикловых состояний - достигается введением элемента 12 совпадения и организацией новых структурных связей. Устройство также содержит триггеры 1-5, элементы 6-11 совпадений и входную шину 13. Устройство обеспечивает коэффициент деления, равный 25. 2 ил.

i

rf /

к

fl-mbkhd

Фиг.1

Изобретение относится к импульсной технике и может быть использовано в устройствах для деления частоты следования импульсов.

Цель изобретения - повышение помехоустойчивости за счет исключения вне1щкловых состояний.

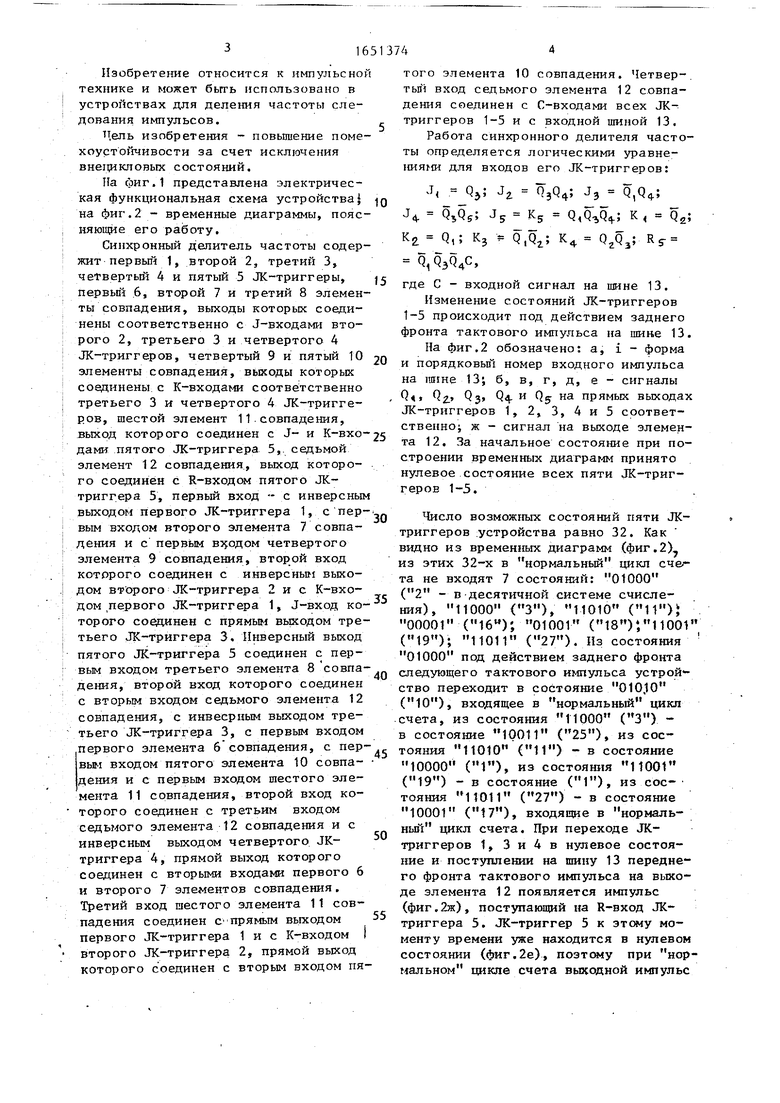

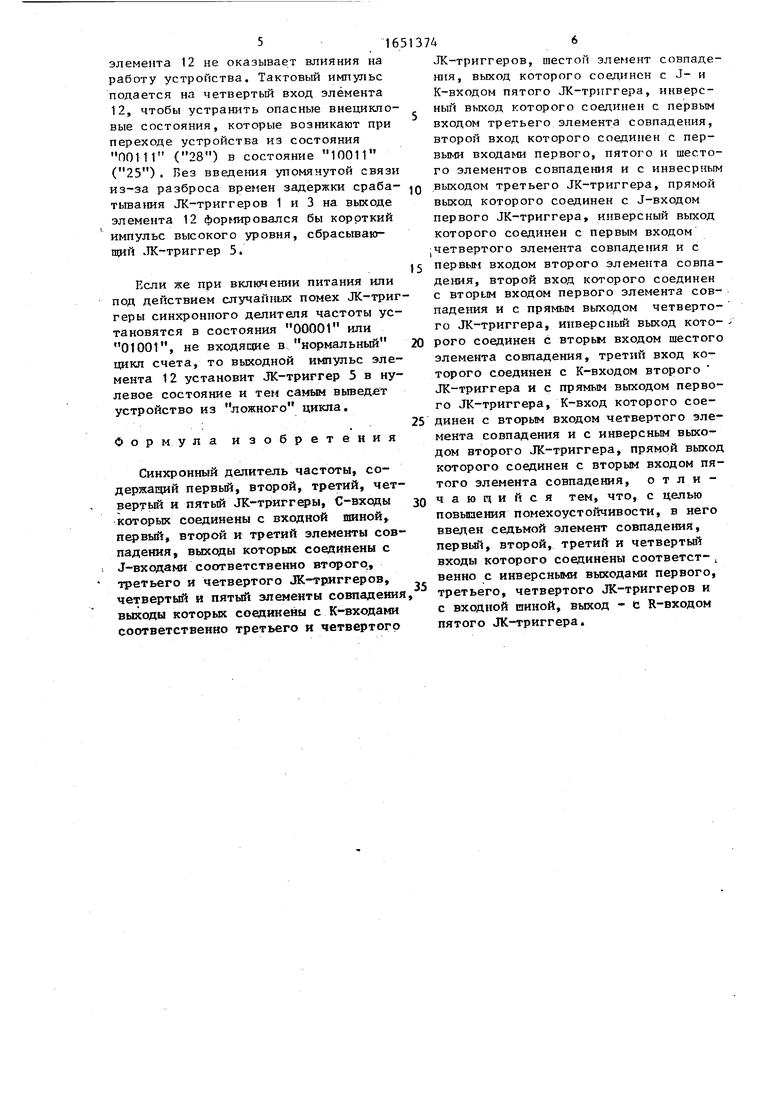

На фиг.1 представлена электрическая функциональная схема устройства} на фиг.2 - временные диаграммы, поясняющие его работу.

Синхронный делитель частоты содержит первый 1, второй 2, третий 3, четвертый 4 и пятый 5 JK-триггеры, первый 6, второй 7 и третий 8 элементы совпадения, выходы которых соединены соответственно с J-входами второго 2, третьего 3 и четвертого 4 JK-триггеров, четвертый 9 и пятый 10 элементы совпадения, выходы которых соединены с К-входами соответственно третьего 3 и четвертого 4 JK-тригге- ров, шестой элемент 11 совпадения, выход которого соединен с J- и К-входами пятого JK-триггера 5, седьмой элемент 12 совпадения, выход которого соединен с R-входом пятого JK- триггера 5, первый вход - с инверсным выходом первого JK-триггера 1, с первым входом второго элемента 7 совпадения и с первым входом четвертого элемента 9 совпадения, второй вход которого соединен с инверсным выходом второго JK-триггера 2 и с К-вхо- дом ервого JK-триггера 1, J-вход которого соединен с прямым выходом третьего JK-триггера З. Инверсный выход пятого JK-триггера 5 соединен с первым входом третьего элемента 8 совпадения, второй вход которого соединен с вторым входом седьмого элемента 12 совпадения, с инвесрным выходом третьего JK-триггера З, с первым входом первого элемента 6 совпадения, с пер- вым входом пятого элемента 10 совпа- дения и с первым входом шестого элемента 11 совпадения, второй вход которого соединен с третьим входом седьмого элемента 12 совпадения и с инверсным выходом четвертого JK- триггера 4, прямой выход которого соединен с вторыми входами первого 6 и второго 7 элементов совпадения. Третий вход шестого элемента 11 совпадения соединен С прямым выходом первого JK-триггера 1 и с К-входом I второго JK-триггера 2, прямой выход которого соединен с вторым входом пя

0

5

0

5

.

0

5

0

0

5

того элемента 10 совпадения. Четвертый вход седьмого элемента 12 совпадения соединен с С-входами всех JK- триггеров 1-5 и с входной шиной 13.

Работа синхронного делителя частоты определяется логическими уравнениями для входов его JK-триггеров:

J, Q5; Зг Q3Q4; J3 Q,

J J5 K5 К Q2; кг Q,; K3 Q,QI; кф QZQ3; Rg-

Q,Q3Q4C

где С - входной сигнал на шине 13.

Изменение состояний JK-триггеров 1-5 происходит под действием заднего фронта тактового импульса на шине 13.

На фиг.2 обозначено; a, i - форма и порядковый номер входного импульса на шине 13; б, в, г, д, е - сигналы Q QЈ 0.3 Qq- и QS на прямых выходах JK-триггеров 1, 2, 3, 4 и 5 соответственно i ж - сигнал на выходе элемента 12. За начальное состояние при построении временных диаграмм принято нулевое состояние всех пяти JK-триггеров 1-5.

Число возможных состояний пяти JK- триггеров устройства равно 32. Как видно из временных диаграмм (Фиг.2)7 из этих 32-х в нормальный цикл та не входят 7 состояний: 01000 (2 - в десятичной системе счисления), Ht1000 (3), 11010 (11)J 00001 (16м); 01001 (18)t l1001 (19); 11011 (27). Из состояния 01000 под действием заднего фронта следующего тактового импульса устройство переходит в состояние 010,10 (10), входящее в нормальный цикл счета, из состояния 11000 (3) - в состояние 10011 (25), из состояния 11010 (11) - в состояние 10000 (1), из состояния 11001 (19) - в состояние (1), из состояния 11011 (27) - в состояние 10001 (17), входящие в нормальный цикл счета. При переходе JK- триггеров 1, 3 и 4 в нулевое состояние и поступлении на шину 13 переднего фронта тактового импульса на выходе элемента 12 появляется импульс (фиг.2ж), поступающий на R-вход JK- триггера 5. JK-триггер 5 к этому моменту времени уже находится в нулевом состоянии (фиг.2е), поэтому при нормальном цикле счета выходной импульс

элемента 12 не оказывает влияния на работу устройства. Тактовый импульс подается на четвертый вход элемента 12, чтобы устранить опасные внецикло- вые состояния, которые возникают при переходе устройства из состояния 00111 (28) в состояние 10011 (25) . Без введения упомянутой связи из-за разброса времен задержки срабатывания JK-триггеров 1 и 3 на выходе элемента 12 формировался бы короткий импульс высокого уровня, сбрасывающий JK-триггер 5.

Если же при включении питания или под действием случайных помех JK-триг геры синхронного делителя частоты установятся в состояния 00001 или 01001, не входящие в. нормальный цикл счета, то выходной импульс элемента 12 установит JK-триггер 5 в нулевое состояние и тем самым выведет устройство из ложного цикла.

Формула изобретения

Синхронный делитель частоты, содержащий первый, второй, третий, четвертый и пятый JK-триггеры, С-входы которых соединены с входной шиной, первый, второй и третий элементы совпадения, выходы которых соединены с J-входами соответственно второго, третьего и четвертого JK-триггеров, четвертый и пятый элементы совпадения выходы которых соединены с К-входами соответственно третьего и четвертого

30

13746

JK-триггеров, шестой элемент совпадения, выход которого соединен с J- и К-входом пятого JK-триггера, инверсный выход которого соединен с первым входом третьего элемента совпадения, второй вход которого соединен с первыми входами первого, пятого и шестого элементов совпадения и с инвесрным

JQ выходом третьего JK-триггера, прямой выход которого соединен с J-входом первого JK-триггера, инверсный выход которого соединен с первым входом (чет в ер тог о элемента совпадения и с

15 первым входом второго элемента совпадения, второй вход которого соединен с вторым входом первого элемента совпадения и с прямым выходом четвертого JK-триггера, инверсный выход кото20 рого соединен с вторым входом шестого элемента совпадения, третий вход которого соединен с К-входом второго JK-триггера и с прямым выходом первого JK-триггера, К-вход которого сое25 динен с вторым входом четвертого элемента совпадения и с инверсным выходом второго JK-триггера, прямой выход которого соединен с вторым входом пятого элемента совпадения, отличающийся тем, что, с целью повышения помехоустойчивости, в него введен седьмой элемент совпадения, первый, второй, третий и четвертый входы которого соединены соответст- . венно с инверсными выходами первого, третьего, четвертого JK-триггеров и с входной шиной, выход - с R-входом пятого JK-триггера.

35

Чз

«V

Составитель А.Соколов Редактор С.Пекарь Техред Л.Сердюкова

Заказ 1610

Тираж 470

ВНЙИПИ Государствечного комитета по изобретениям и открытиям при ГКВТ СССР 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-издательский комбинат Патент, г. Ужгород, ул. Гагарина, 101

Ф

Корректор М.Самборская

Подписное

| Синхронный делитель частоты | 1986 |

|

SU1354415A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1991-05-23—Публикация

1989-05-03—Подача