семь элементов И и пять элементов ИЛИ. Триггер 11 содержит четыре накопителя, четыре выпрямителя, дпа элемента нагрузки, пять элементов И, шесть

Изобретение относится к автоматике и может быть использовано для кодирования рельсовых цепей в числовой кодовой автоблокировке и электричес кой централизации.

Целью изобретения является повышение надежности и помехоустойчивости трансмиттера.

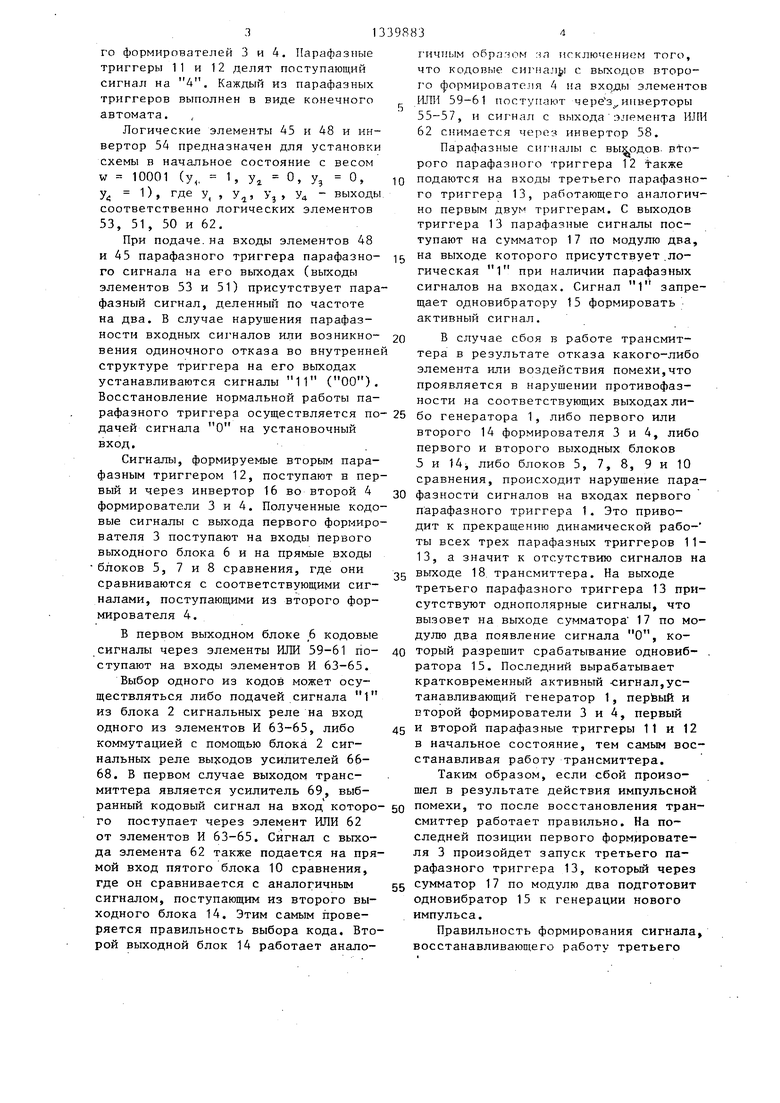

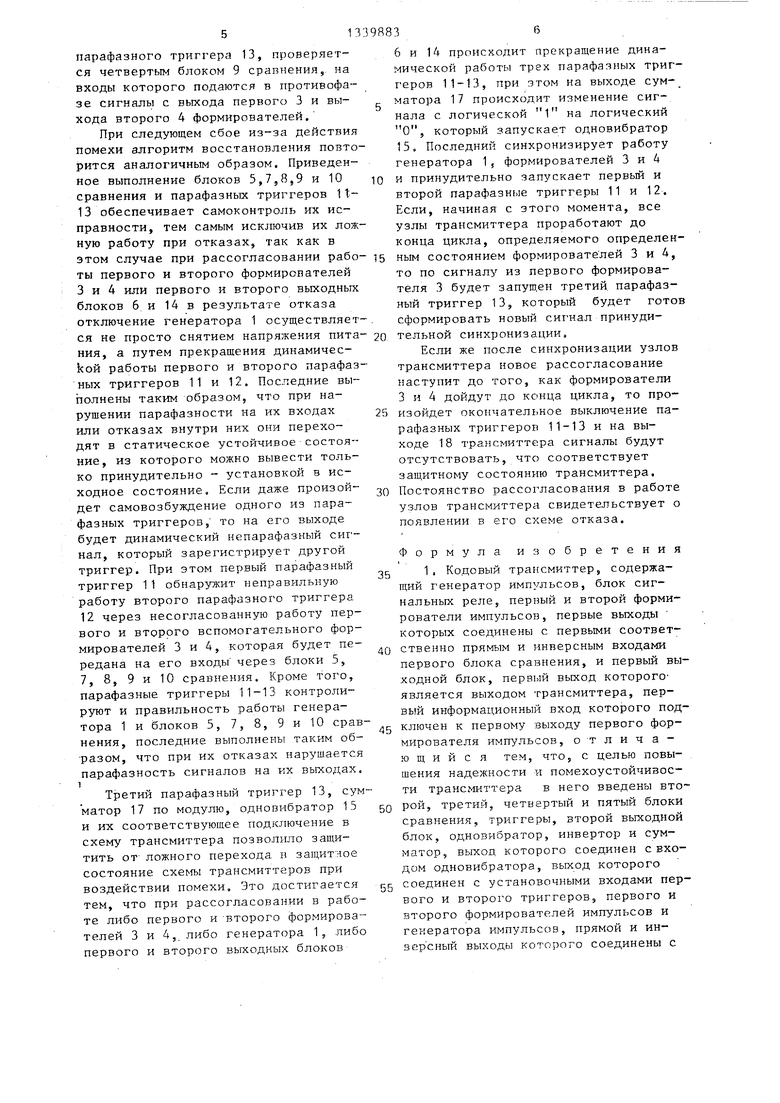

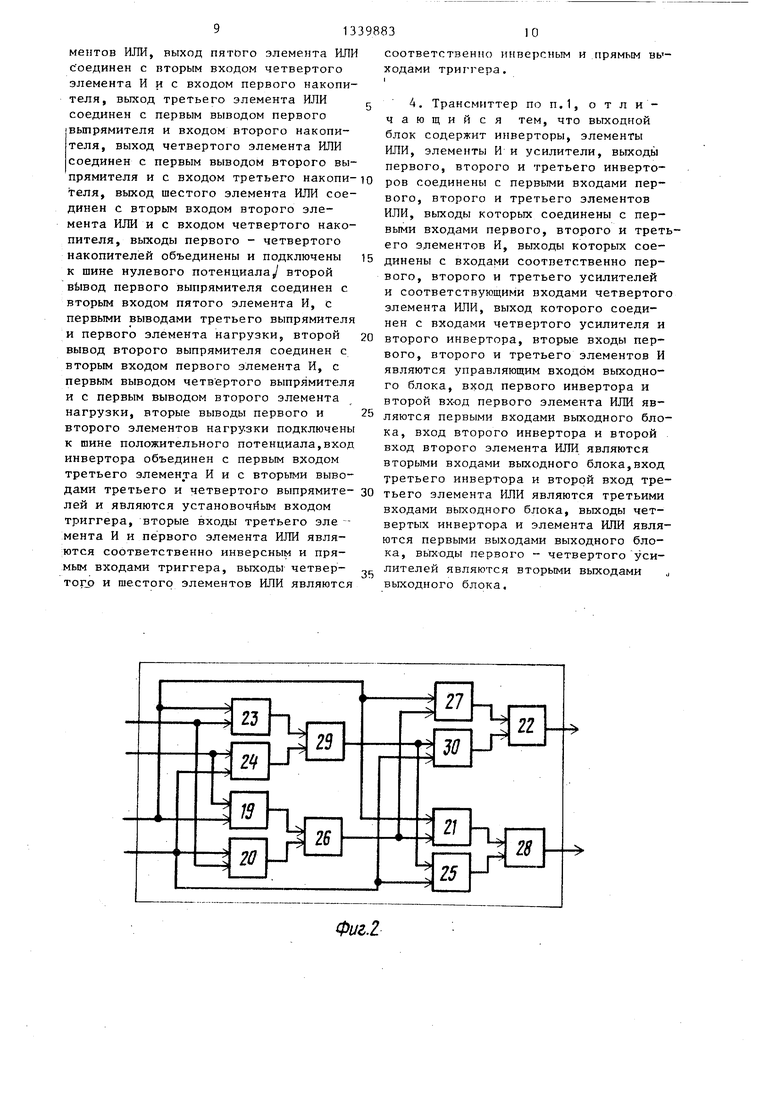

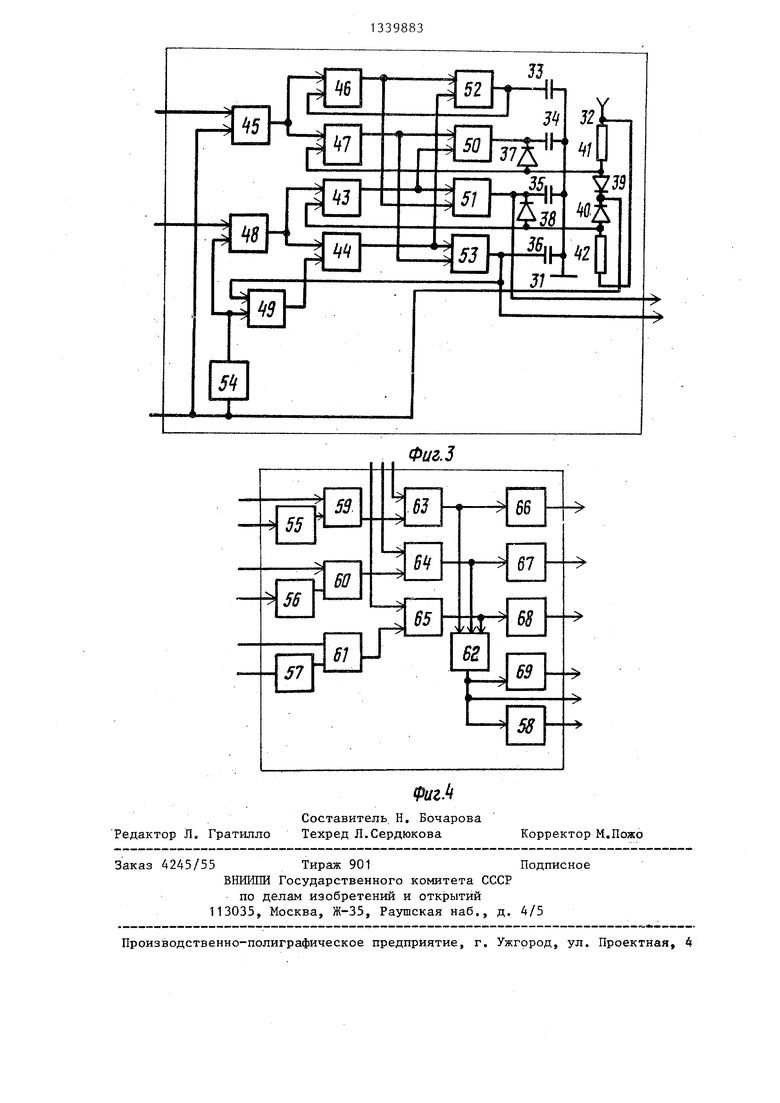

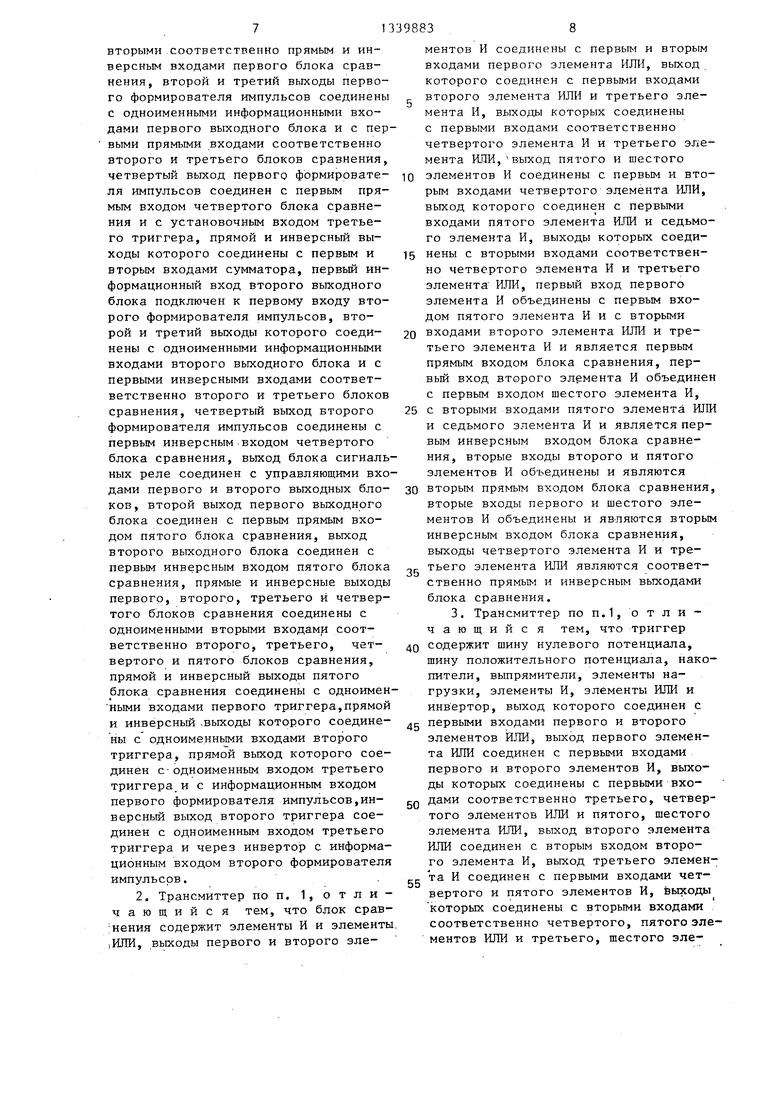

На фиг. 1 представлена блок-схема кодового трансмиттера на фиг. 2 - функциональная схема блока сравнения на фиг. 3 - функциональная схема триггера; на фиг, 4 - функциональная схема выходного блока.

Кодовый.трансмиттер содержит генератор 1 импульсов, блок 2 сигнальных реле, первый и второй формирователи 3 и 4 импульсов, первый блок 5 срав- ейия, первый выходной блок: 6, второй, третий, четвертой и пятьм блоки 7-10 сравнения, первый, второй и третий триггеры 11-13, второй выходной блок 14, одновибратор 15, инвертор 16 и сумматор 17 по модулю два выход 18.

Каждый из. блоков 5,7,8,9 и 10 сравнения содержит первый, второй, трети четвертьй, пятый, шестой и седьмой элементы И 19-25 и первый, второй, третий, четвертый и пятый элементы ИЛИ 26-30.

Каждый из триггеров 11-13 содержит шину 31 нулевого потенциала,шину 32 положительного потенциала, первый второй, третий и четвертый накопите- ли 33-36, первый, второй, третий и четвертый вьшрямители 37-40,, первый и второй элементы 41 и 42 нагрузки, первый, второй, третий, четвертый и пятый элементы И 43-47, первый, второй, .третий, четвертый, пятый и шестой элементы ИЛИ 48-53 и инвертор 54,

Каждый из выходных блоков 6 и 14 содержит первый, второй, третий и четвертый инверторы 55-58, первьй второй, третий и четвертый элементы

элементов ИЛИ и инвертор. Выходной блок 6 содержит четыре инвертора, четыре элемента ИЛИ,три элемента И иче- тьфе усилителя 66-69, 3 з.п.ф-лы,4 ил.

5

0

j

О

5

5

5

0

0

59-62, первый, второй и третий элементы И 63-65 и первый, второй, третий и четвертый усилители 66-69.

Трансмиттер работает следующим образом.

При исправном состоянии и при отсутствии влияния помех на прямом и инверсном выходах генератора 1 формируются импульсы в противофазе, которые поступают на вторые входы блока 5 сравнения, на первые входы которого подаются сигналы с первых выходов формирователя 3 и 4, которые также работают синхронно. Работа блоков 5,7-, 8, 9 и 10 сравнения заключается в том, что на выходах последних сигналы появляются в противофазе только при наличии противофазных сигналов на первых и вторых входах. В случае нарушения противофазности сигналов на входах любого из блоков сравнения противофазность сиг налов нарушается и на выходе. Лишь в одном случае это условие не выполняется,-когда на вторых входах блоков сравнения присутствуют логические нули, а на первых входах - логические единицьиНо данная ситуация предусматривает на- личие двух независимых отказов годин в генераторе 1, другой - в формирователях 3 и 4, что маловероятно. Любой одиночный отказ в любом блоке -сравнения приводит к отсутствию парафаз- ных сигналов на его выходах,

С выходов блока 5 сравнения противофазные сигналы с частотой, аналогичной частоте сигналов генератора 1, проходят через последующие блоки 7- 10 сравнения, где происходит сравнение между собой сигналов, поступающих с выходов формирователей 3 и 4 и выходных блоков 6 и 14.

С выходов пятого блока 10 сравнения парафазные сигналы через парафаз- Hhie тригге эы 1 1 и 12 поступают на информационные в ходы «.первого и в торс-

31339883

го формирователей 3 и 4. Парафазные триггеры 11 и 12 делят поступающий сигнал на 4. Каждый из парафазных триггеров выполнен в виде конечного автомата.

Логические элементы 45 и 48 и инвертор 54 предназначен для установки схемы в начальное состояние с весом W 10001 (у,, 1, у,, О, у, О, 10

Уе. 1) ГД У, У УЗ У выходы. соответственно логических элементов 53, 51, 50 и 62.

При подаче, на входы элементов 48 и 45 парафазного триггера парафазно- 15 го сигнала на его выходах (выходы элементов 53 и 51) присутствует пара- фазный сигнал, деленный по частоте на два. В случае нарушения парафаз- ности входных сигналов или возникно- 20 вения одиночного отказа во внутренней структуре триггера на его выходах устанавливаются сигналы 11 (00). Восстановление нормальной работы парафазного триггера осуществляется по- 25 бо генератора 1, либо первого или дачей сигнала О на установочный второго 14 формирователя 3 и 4, либо

1 ичпым o6parJONf зл исключением того, что кодовые сигналит с выходов второго формирователя 4 на входы элементов ИЛИ 59-61 поступают чере з инверторы 55-57, и сигнал с выхода элемента ИЛИ 62 снимается через инвертор 58.

Парафазные сиг-налы с выходов, второго парафазного триггера 12 также подаются на входы третьего парафазного триггера 13, работающего аналогично первым двум триггерам. С выходов триггера 13 парафазные сигналы поступают на сумматор 17 по модулю два, на выходе которого присутствует .логическая 1 при наличии парафазных сигналов на входах. Сигнал 1 запрещает одновибратору 15 формировать; активный сигнал.

В случае сбоя в работе трансмиттера в результате отказа какого-либо элемента или воздействия помехи,что проявляется в нарушении противофаз- ности на соответствующих выходах ливход.

Сигналы, формируемые вторым пара- фазным триггером 12, поступают в первый и через инвертор 16 во второй 4 зо формирователи 3 и 4. Полученные кодовые сигналы с выхода первого формирователя 3 поступают на входы первого выходного блока 6 и на прямые входы блоков 5, 7 и 8 сравнения, где они сравниваются с соответствующими сигналами, поступающими из второго формирователя 4.

В первом выходном блоке 6 кодовые сигналы через элементы ШМ 59-61 поступают на входы элементов И 63-65.

Выбор одного из кодов может осуществляться либо подачей сигнала 1 из блока 2 сигнальных реле на вход одного из элементов И 63-65, либо коммутацией с помощью блока 2 сигнальных реле ВЫ5СОДОВ усилителей 66- 68. В первом случае выходом транспервого и второго выходных блоков 5 и 14, либо блоков 5, 7, В, 9 и 10 сравнения, происходит нарушение пара- фазности сигналов на входах первого парафазного триггера 1. Это приводит к прекращению динамической рабо- ты всех трех парафазных триггеров 11- 13, а значит к отсутствию сигналов на

35 выходе 18 трансмиттера. На выходе

третьего парафазного триггера 13 присутствуют однополярные сигналы, что вызовет на выходе сумматора 17 по модулю два появление сигнала О, ко40 торый разрешит срабатывание одновиб- . ратора 15. Последний вырабатывает кратковременный активный -сигнал,устанавливающий генератор 1, перЬый и второй формирователи 3 и 4, первый

45 и второй парафазные триггеры 11 и 12

миттера является усилитель 69, выбстанавливая работу трансмиттера.

Таким образом, если сбой произошел в результате действия импульсной ранный кодовый сигнал на вход которо- 50 помехи, то после восстановления тран- го поступает через элемент ИЛИ 62 смиттер работает правильно. На пост элементов И 63-65. Сигнал с выхо- следней позиции первого формировате- да элемента 62 также подается на пря- ля 3 произойдет запуск третьего па-

мой вход пятого блока 10 сравнения, где он сравнивается с аналогичным сигналом, поступающим из второго выходного блока 14. Этим самым проверяется правильность выбора кода. Второй выходной блок 14 работает аналобо генератора 1, либо первого или второго 14 формирователя 3 и 4, либо

1 ичпым o6parJONf зл исключением того, что кодовые сигналит с выходов второго формирователя 4 на входы элементов ИЛИ 59-61 поступают чере з инверторы 55-57, и сигнал с выхода элемента ИЛИ 62 снимается через инвертор 58.

Парафазные сиг-налы с выходов, второго парафазного триггера 12 также подаются на входы третьего парафазного триггера 13, работающего аналогично первым двум триггерам. С выходов триггера 13 парафазные сигналы поступают на сумматор 17 по модулю два, на выходе которого присутствует .логическая 1 при наличии парафазных сигналов на входах. Сигнал 1 запрещает одновибратору 15 формировать; активный сигнал.

В случае сбоя в работе трансмиттера в результате отказа какого-либо элемента или воздействия помехи,что проявляется в нарушении противофаз- ности на соответствующих выходах ли

первого и второго выходных блоков 5 и 14, либо блоков 5, 7, В, 9 и 10 сравнения, происходит нарушение пара- фазности сигналов на входах первого парафазного триггера 1. Это приводит к прекращению динамической рабо- ты всех трех парафазных триггеров 11- 13, а значит к отсутствию сигналов на

выходе 18 трансмиттера. На выходе

третьего парафазного триггера 13 присутствуют однополярные сигналы, что вызовет на выходе сумматора 17 по модулю два появление сигнала О, который разрешит срабатывание одновиб- . ратора 15. Последний вырабатывает кратковременный активный -сигнал,устанавливающий генератор 1, перЬый и второй формирователи 3 и 4, первый

и второй парафазные триггеры 11 и 12

рафазного триггера 13, который через 55 сумматор 17 по модулю два подготовит одновибратор 15 к генерации нового импульса.

Правильность формирования сигнала, восстанавливаюп1его работу третьего

парафазного триггера 13, проверяется четвертым блоком 9 сравнения,, на входы которого подаются в противофа- зе сигналы с выхода первого 3 и выхода второго 4 формирователей,

При следующем сбое из-за действия помехи алгоритм восстановления повторится аналогичным образом. Приведенное выполнение блоков 5,7,8,9 и 10 сравнения и парафазных триггеров 11- 13 обеспечивает самоконтроль их исправности, тем самым исключив их ложную работу при отказах, так как в этом случае при рассогласовании работы первого и второго формирователей 3 и 4 или первого и второго выходных блоков 6 и 14 в результате отказа отключение генератора 1 осуществляется не просто снятием напряжения питания, а путем прекращения динамичес- koй работы первого и второго парафазных триггеров 11 и 12, Последние выполнены таким образом:, что при нарушении парафазности на их входах или отказах внутри них они переходят в статическое устойчивое состояние, из которого можно вывести только принудительно - установкой в исходное состояние. Если даже произойдет самовозбуждение одного из пара- фазных триггеров, то на его выходе будет динамический непарафазный сигнал, который зарегистрирует другой триггер. При этом первый парафазный триггер 11 обнаружит неправильную работу второго парафазного триггера 12 через несогласованную работу первого и второго вспомогательного формирователей 3 и 4, которая будет передана на его входы через блоки 5, 7, 8, 9 и 10 сравнения. Кроме того, парафазные триггеры 11-13 контролируют и правильность работы генератора 1 и блоков 5, 7, 8, 9 и 10 сравнения, последние выполнены таким образом, что при их отказах нарушается

парафазность сигналов на их выходах. 1

Третий парафазный триггер 13, сумматор 17 по модулю, одновибратор 15 и их соответствующее подключение в схему трансмиттера позволило защитить от ложного перехода н защитное состояние схемы трансмиттеров при воздействии помехи. Это достигается тем, что при рассогласовании в работе либо первого и второго формирователей 3 и 4, либо генератора 1, либо первого и второго выходных блоков

6 и 14 происходит прекращение динамической работы трех парафазных триггеров 11-13, при этом на выходе сумматора 17 происходит изменение сигнала с логической 1 на логический О, который запускает одновибратор 15, Последний синхронизирует работу генератора 1, формирователей 3 и 4

0 и принудительно запускает первый и второй парафазные триггеры 11 и 12. Если, начиная с этого момента, все узлы трансмиттера проработают до конпа цикла, определяемого определен5 ным состоянием формировате лей 3 и 4, то по сигналу из первого формирователя 3 будет запут,ен третий, парафазный триггер 13, который будет готов сформировать новый сигнал принуди0 тельной синхронизации.

Если же после синхронизации узлов трансмиттера новое рассогласование наступит до того, как формирователи 3 и 4 дойдут до конца цикла, то про5 изойдет окончательное выключение парафазных триггеров 11-13 и на выходе 18 трансмиттера сигналы будут отсутствовать, что соответствует защитному состоянию трансмиттера,

0 Постоянство рассогласования в работе узлов трансмиттера свидетельствует о появлении в его схеме отказа.

Формула изобретения

5 1. Кодовый трансмиттер, содержащий генератор импульсов, блок сигнальных реле, первый и второй формирователи импульсов, первые выходы которых соединены с первыми соответ0 ственно прямым и инверсным входами первого блока сравнения, и первый выходной блок, первый вьгход которого является выходом трансмиттера, первый информационный вход которого под5 ключен к первому выходу первого формирователя импульсов, отличающийся тем, что, с целью повышения надежности и помехоустойчивости трансмиттера в него введены вто

0 рой, третий, четвертый и пятый блоки сравнения, триггеры, второй выходной блок, одновибратор, инвертор и сумматор, выход которого соединен с входом одновибратора, выход которого

5 соединен с установочными входами первого и второго триггеров, первого и второго формирователей импульсов и генератора импульсов, прямой и ин- зер сный выходы которого соединены с

вторыми соответственно прямым и инверсным входами первого блока сравнения, второй и третий выходы первого формирователя импульсов соединены с одноименными информационными входами первого выходного блока и с пер- выми прямыми входами соответственно второго и третьего блоков сравнения, четвертый выход первого формирователя импульсов соединен с первым прямым входом четвертого блока сравнения и с установочным входом третьего триггера, прямой и инверсный выходы которого соединены с первым и вторым входами сумматора, первый информационный вход второго выходного блока подключен к первому входу второго формирователя импульсов, второй и третий выходы которого соединены с одноименными информационными входами второго выходного блока и с первыми инверсными входами соответ- ветственно второго и третьего блоков сравнения, четвертый выход второго формирователя импульсов соединены с первым инверсным входом четвертого блока сравнения, выход блока сигнальных реле соединен с управляющими входами первого и второго выходных блоков, второй выход первого выходного блока соединен с первым прямым входом пятого блока сравнения, выход второго выходного блока соединен с первым инверсным входом пятого блока сравнения, прямые и инверсные выходы первого, второго, третьего и четвертого блоков сравнения соединены с одноименными вторыми входами соответственно второго, третьего, четвертого и пятого блоков сравнения, прямой и инверсный выходы пятого блока сравнения соединены с одноимен- ными входами первого триггера,прямой и инверсный .выходы которого соединены с одноименными входами второго триггера, прямой выход которого соединен с- одноименным входом третьего триггера и с информационным входом первого формирователя импульсов,инверсный выход второго триггера соединен с одноименным входом третьего триггера и через инвертор с информационным входом второго формирователя импульсов.

2, Трансмиттер по п, 1, отличающийся тем, что блок срав- нения содержит элементы И и элементы, ИЛИ, выходы первого и второго эле

5

0

5

0

5

0

5

0

5

ментов И соединены с первьм и вторым входами первого элемента ИЛИ, выход которого соединен с первыми входами второго элемента ИЛИ и третьего элемента И, выходы которых соединены с первыми входами соответственно четвертого элемента И и третьего элемента ИЛИ,выход пятого и шестого элементов И соединены с первым и вторым входами четвертого элемента ИЛИ, выход которого соединен с первыми входами пятого элемента ИЛИ и седьмого элемента И, выходы которых соединены с вторыми входами соответственно четвертого элемента И и третьего элемента ИЛИ, первый вход первого элемента И объединены с первым входом пятого элемента И и с вторыми входами второго элемента ИЛИ и третьего элемента И и является первым прямым входом блока сравнения, первый вход второго элемента И объединен с первым входом шестого элемента И, с вторыми входами пятого элемента ШШ и седьмого элемента И и является первым инверсным входом блока сравнения, вторые входы второго и пятого элементов И объединены и являются вторым прямым входом блока сравнения, вторые входы первого и шестого элементов И объединены и являются вторым инверсньм входом блока сравнения, выходы четвертого элемента И и третьего элемента ИЛИ являются соответственно прямым и инверсным выходами блока сравнения.

3, Трансмиттер по п.1, о т л и - чающийся тем, что триггер содержит шину нулевого потенциала, шину положительного потенциала, накопители, выпрямители, элементы нагрузки, элементы И, элементы ШШ и инвертор, выход которого соединен с первыми входами первого и второго элементов ИЛИ, выход первого элемента ШШ соединен с первыми входами первого и второго элементов И, выходы которых соединены с первыми входами соответственно третьего, четвертого элементов ИЛИ и пятого, шестого элемента ИЛИ, выход второго элемента ИЛИ соединен с вторым входом второго элемента И, выход третьего элемента И соединен с первыми входами четвертого и пятого элементов И, йыходы которых соединены с вторыми входами соответственно четвертого, пятого элементов ШШ и третьего, шестого элементов ИЛИ, выход пятого элемента ИЛИ Соединен с вторым входом четвертого элемента И и с входом первого накопителя, выход третьего элемента ИЛИ соединен с первым выводом первого (вьтрямителя и входом второго накопителя, выход четвертого элемента ИЛИ соединен с первым выводом второго выпрямителя и с входом третьего накопителя, выход шестого элемента ИЛИ соединен с вторым входом второго элемента ИЛИ и с входом четвертого накопителя, выходы первого - четвертого накопителей объединены и подключены к шине нулевого потенциалаУ второй вЬшод первого выпрямителя соединен с вторым входом пятого элемента И, с первыми выводами третьего выпрямителя и первого элемента нагрузки, второй вывод второго выпрямителя соединен с вторым входом первого элемента И, с первьм выводом четвертого выпрямителя и с первым выводом второго элемента нагрузки, вторые выводы первого и второго элементов нагрузки подключены к шине положительного потенциала,вход инвертора объединен с первьм входом третьего элемента И и с вторыми выводами третьего и четвертого выпрямите- лей и являются установочным входом триггера, вторые входы третьего эле - мента И и первого элемента ИЛИ являются соответственно инверсным и прямым входами триггера, выходы четвер

того и шестого элементов ИЛИ являются

Фиг.г

5 0 5 О

5

соответственно инверсным и прямым вь ходами триггера. I

4. Трансмиттер по п.1, отличающийся тем, что выходной блок содержит инверторы, элементы ИЛИ, элементы И и усилители, выходь первого, второго и третьего инверторов соединены с первыми входами первого, второго и третьего элементов ИЛИ, выходы которьпс соединены с первыми входами первого, второго и третьего элементов И, выходы которых соединены с входами соответственно первого, второго и третьего усилителей и соответствующими входами четвертого элемента ИЛИ, выход которого соединен с входами четвертого усилителя и второго инвертора, вторые входы первого, второго и третьего элементов И являются управляющим входом выходного блока, вход первого инвертора и второй вх-од первого элемента ИЛИ являются первыми входами выходного блока, вход второго инвертора и второй вход второго элемента ИЛИ являются вторыми входами выходного блока,вход третьего инвертора и второй вход третьего элемента ИЛИ являются третьими входами выходного блока, выходы четвертых инвертора и элемента ИЛИ являются первыми выходами выходного блока, выходы первого - четвертого усилителей являются вторыми выходами ,, выходного блока.

Редактор Л, Гратилло

Составитель. Н. Бочарова Техред Л.Сердюкова

Заказ 4245/55 Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг.З

Корректор М.Пожо

| название | год | авторы | номер документа |

|---|---|---|---|

| Счетчик с коэффициентом пересчета шесть | 1986 |

|

SU1322466A1 |

| Устройство деления частоты импульсов с контролем | 1985 |

|

SU1297221A1 |

| Устройство для передачи сигналов точного времени по линиям связи с переменным временем распространения | 1982 |

|

SU1095219A1 |

| Кодовый трансмиттер | 1978 |

|

SU780195A1 |

| Параллельно-последовательный аналого-цифровой преобразователь | 1988 |

|

SU1569983A1 |

| Устройство для ввода информации | 1987 |

|

SU1529231A1 |

| Делитель числа импульсов | 1983 |

|

SU1138945A1 |

| Устройство для управления записью и считыванием информации | 1981 |

|

SU1014028A1 |

| Аналого-цифровой преобразователь с промежуточным преобразованием в частоту | 1989 |

|

SU1644382A1 |

| Голографическое постоянное запоминающее устройство со сменным носителем голограмм | 1990 |

|

SU1691889A1 |

Изобретение относится к автоматике и может быть использовано для кодирования рельсовых цепей в числовой кодовой автоблокировке и .электрической централизации. Изобретение позволяет при сохранении функций кодового трансмиттера повысить его надежность и помехоустойчивость. Кодовый трансмиттер содержит генератор 1 импульсов, блок 2 сигнальных реле, два формирователя 3 и 4 импульсов, пять блоков 5, 7, 8, 9 и 10 сравнения, три триггера 11, 12 и 13, два выходных блока 6 и 14, одновибратор 15, инвертор 16 и сумматор 17 по модулю два. Блок 5 сравнения содержит (Л 00 со со 00 00 00

| Кодовый трансмиттер | 1978 |

|

SU780195A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Кодовый трансмиттер | 1976 |

|

SU632085A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-23—Публикация

1985-07-12—Подача