1

Изобретение относится к вычислительной технике и может быть использовано в стохастических вычислитель- . ных мэшин-ах для моделирования ряда случайных процессов.

Цель изобретения - повышение быстродействия работы.

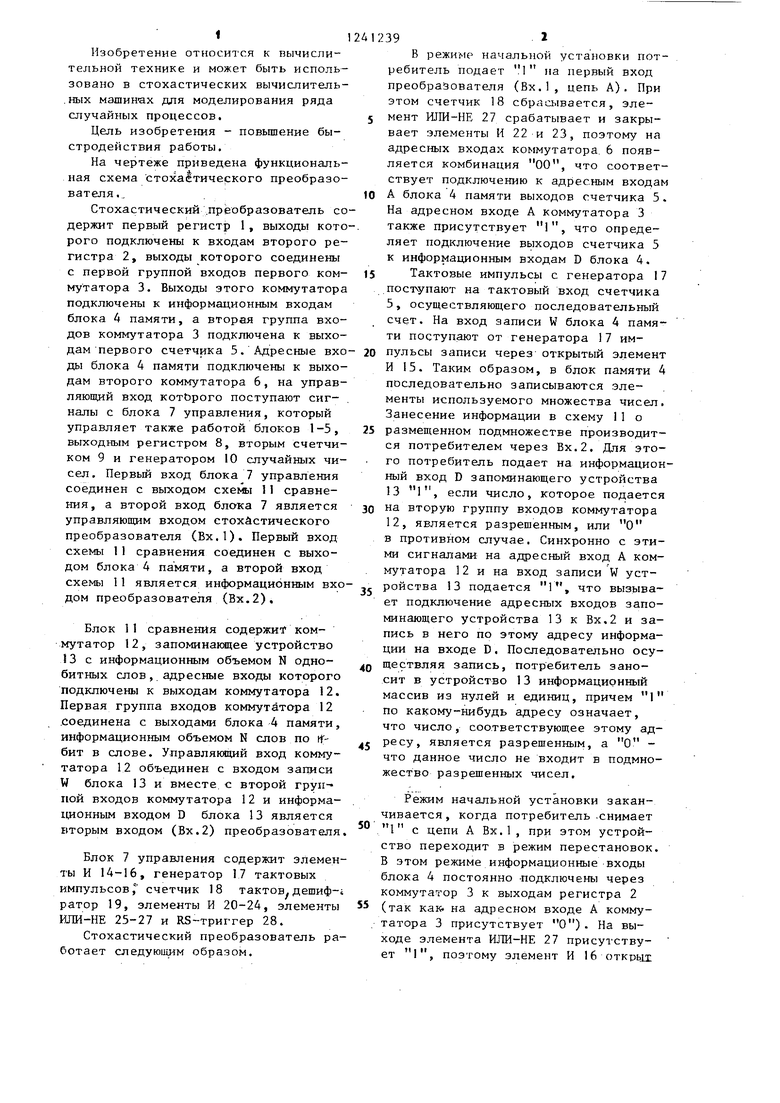

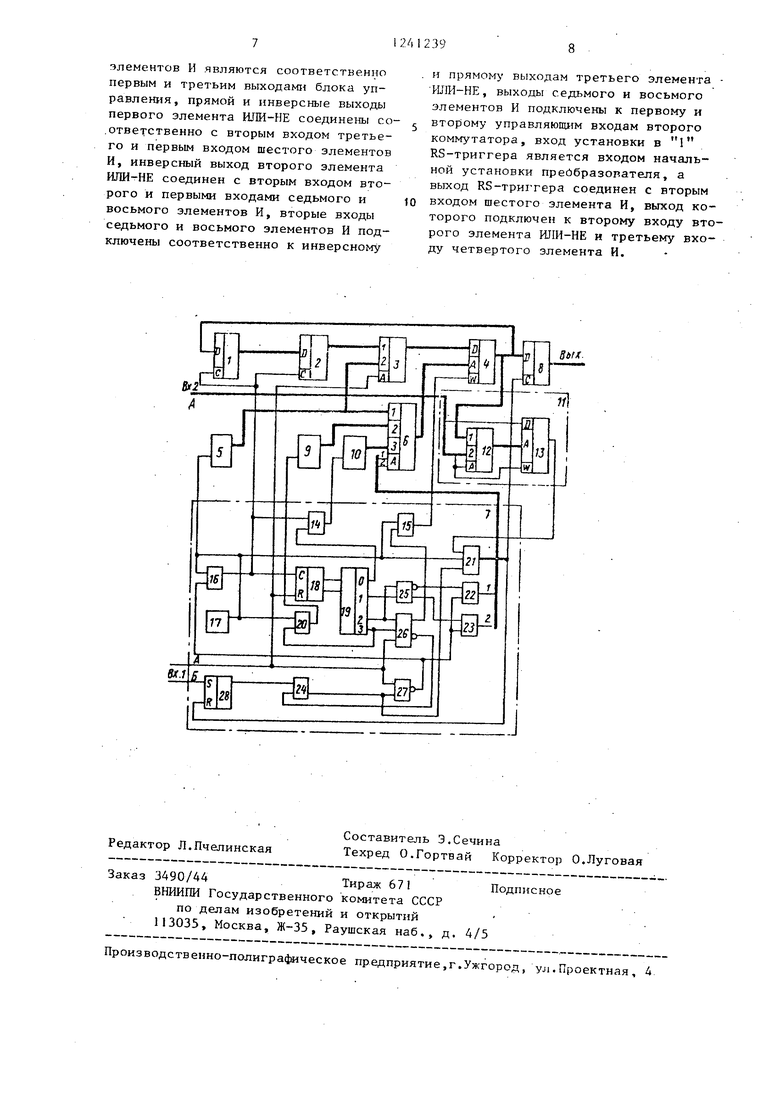

На чертеже приведена функциональная схема стохастического преобразователя..

Стохастический .преобразователь со держит первый регистр 1 , выходы которого подключены к входам второго регистра 2, выходы которого соединены с первой группой входов первого коммутатора 3. Выходы этого коммутатора подключены к информационным входам блока 4 памяти, а вторая группа входов коммутатора 3 подключена к выходам первого счетчика 5. Адресные вхо ды блока 4 памяти подключены к выходам второго коммутатора 6, на управляющий вход которого поступают сигналы с блока 7 управления, который управляет также работой блоков 1-5, выходным регистром 8, вторым счетчиком 9 и генератором 10 случайных чисел . Первый вход блока 7 управления соединен с выходом схены 11 сравнения, а второй вход блока 7 является управляющим входом стохйстического преобразователя (Вх.1). Первый вход схемы 11 сравнения соединен с выходом блока 4 па мяти, а второй вход схемы 11 является информационным входом преобразователя (Вх.2).

Блок 11 сравнения содержит коммутатор 12, запоминающее устройство 13с информационным объемом N однобитных слов, адресные входы которого подключены к выходам коммутатора 12. Первая группа входов коммутатора 12 .соединена с выходами блока 4 памяти, информационным объемом N слов по бит в слове. Управляющий вход коммутатора 12 объединен с входом записи W блока 13 и вместе с второй группой входов коммутатора 12 и информационным входом D блока 13 является вторым входом (Вх.2) преобразователя

Блок 7 управления содержит элементы И 14-16, генератор 17 тактовых импульсов, счетчик 18 тактов дешифратор 19, элементы И 20-24, элементы ИЛИ-НЕ 25-27 и RS-триггер 28.

Стохастический преобразователь работает следующим образом.

41239I

В режиме начальной установки потребитель подает 1 на первый вход преобразователя (Вх.1, цепь А). При этом счетчик 18 сбрасывается, эле5 мент ИЛИ-ИЕ 27 срабатывает и закрывает элементы И 22 и 23, поэтому на адресных входах коммутатора. 6 появляется комбинация 00, что соответствует подключению к адресным входам

10 А блока 4 памяти выходов счетчика 5. На адресном входе А коммутатора 3 также присутствует 1, что определяет подключение выходов счетчика 5 к информационным входам D блока 4.

15 Тактовые импульсы с генератора 17 пост упают на тактовый вход счетчика 5, осуществляющего последовательный счет. На вход записи W блока 4 памяти поступают от генератора 17 им- 20 пульсы записи через открытый элемент И 15. Таким образом, в блок памяти 4 последовательно записываются элементы используемого множества чисел. Занес€ ние информации в схему 1 1 о

25 размещенном подмножестве производится потребителем через Вх.2. Для этого потребитель подает на информационный вход D запоминающего устройства 13 1, если число, которое подается

30 на вторую группу входов коммутатора 12, является разрешенным, или О 3 противном случае. Синхронно с этими сигналами на адресный вход А коммутатора 12 и на вход записи W уст- ,, ройства 13 подается 1, что вызывает подключение адресных входов запоминающего устройства 13 к Вх.2 и запись в него по этому адресу информации на входе D. Последовательно осу40 ществляя запись, потребитель заносит в устройство 13 информационный массив из нулей и единиц, причем 1 по какому-нибудь адресу означает, что число, соответствующее этому ресу, является разрешенным, а О - что данное число не входит в подмножество разрешенных чисел.

Режим начальной установки заканчивается , когда потребитель -снимает

1 с цепи А Вх.1 , при этом устройство переходит в режим перестановок. В этом режиме информационные входы блока 4 постоянно -подключены через коммутатор 3 к выходам регистра 2

55 (так как. на адресном входе А коммутатора 3 присутствует О). На выходе элемента ИЛИ-НЕ 27 присутствует 1, поэтому элемент И 16 открьц

3

для тактовых импульсов с генератора 17. Одна перестановка производится на 4 такта.

В нулевом такте элемент И 22 открыт,так как на инверсном выходе элемента ИЛИ-НЕ 25 присутствует 1, элемент И 23 закрыт и на адресном входе коммутатора 6 пояйляется комбинация 01, что определяет подключение к адресным входам блока 4 памя ти выходов счетчика 9. Элемент И 15 закрыт, поэтому блок 4 памяти находится в режиме чтения. В конце такта считанное по адресу из счетчика 9 число записывается в регистр 1 такто вым импульсом через открытый элемент И 16. Элемент И 14 также открыт, и прошедший через него импульс вызывает выборку очередного п -разрядного числа в генераторе 10 случайных чисел. Нулевой такт заканчивается после того, как двоичный счетчик 18 импульсом, прошедшим через элемент И 16, переводится в состояние 01, что соответствует первому такту.

В первом такте на первом выходе дешифратора 19 появляется 1, поэтому на прямом выходе элемента ИЛИ 25 присутствует 1, а на инверсном - О. Через элементы И 22 и 23 эта комбинация передается на адресный вход коммутатора 6, что вызывает подключение к адресным входам блока 4 памяти выходов генератора 10 случайных чисел. Считанное по этому ад- ресу число из блока 4 записывается в регистр 1 , одновременно с этим информация из регистра 1 переписывается в регистр 2 (так как входы записи с регистров 1 и 2 объединены).

Во втором такте 1 появляется на втором выходе дешифратора 19 и поступает на входы элементов ИЛИ-НЕ 25 и 26f поэтому к адресным входам бло- ка 4 подключены выходы генератора 10. Информационные входы блока 4 подключены через коммутатор 3 к выходам регистра 2. Логическая единица с прямого выхода элемента ИЛИ-НЕ 26 поступает на вход элемента И 15, поэтому тактовый импульс с генератора 17 проходит на вход записи W блока 4 памяти и происходит запись числа с регистра 2 по адресу с генератора 10 случайных чисел. В конце такта информация с регистра 1 переписывается в регистр 2, а счетчик 18 переводится

5 - О- )5 2025

зо ,, 40

2394

тактовым импульсом в состояние 11, что соответствует третьем такту.

В третьем такте на входах элемента ИЛИ-НЕ 27 присутствуют О, поэтому элемент И 22 открыт, а эле. мент И 23 закрыт, значит к адресным входам блока 4 подключаются выходы счетчика 9. На третьем выходе дешифратора 19 присутствует 1, поэтому на прямом выходе элемента ШШ- НЕ 26 также 1, которая открывает элемент И 15 для прохождения импульса записи на блок 4 памяти. Число из регистра 2 записывается в блок 4 по адресу из счетчика 9. В конце такта этот счетчик импульсом с генератора 17 через открытый элемент И 20 переводится в следуюш;ее состояние, на выходах счетчика 18 появляется комбинация 00 и начинается нулевой такт очередного цикла перестановок. В результате одной перестановки меняются адреса двух записанных в блоке- 4 чисел, а после нескольких перестановок в блоке 4 оказывается записанным в случайном порядке множество и з N используемых чисел..

Режим перестановок продолжается до тех пор, пока на управляюш11Й вход (Вх.1,цепь Б) не поступит положительный импульс. Этот импульс переводит триггер 28 в единичное состояние. Если стохастический преобразователь находится в режиме перестановок на втором или третьем такте, то логический элемент И 24 закрыт нулевым логическим уровнем с инверсного выхода элемента ИЛИ-НЕ 26. Режим перестановок не прерывается до тех пор, пока не наступит нулевой или первый такт. При этом на инверсном выходе элемента ИЛИ-НЕ 26 появляется 1, которая открывает элемент И 24, и устройство переходит в режим выбора

-числа, принадлежащего разрешенному подмножеству.

В этом режиме на выходе элемента ИЛИ-НЕ 26 появляется О, который запирает элементы И 16, 22 и 23, поэтому импульсы с генератора 17 не проходят на регистры 1 и 2, счетчик 18 и генератор 10 случайных чисел, а адресные входы блока 4 памяти подключаются к счетчику 5.Считанное по адресу из этого счетчика число поступает через первый вход коммутатора 12 на адресный вход запоминающего устройства 13,которое также находится в режиме считывания. Если число, поступившее На адресные входы устройства 13, не принадлежит к подмножеству разрешенных, то на его выходе присутствует О, который поддерживает элемент И 21 в выключенном состоянии. Тактовый импульс с генератора 17 поступает на вход счетчика 5, что вызывает появление на его выхо- дах следующего числа. Это число через коммутатор 6 поступает на адресный вход блока 4 памяти, а считанное по этому адресу число через коммутатор 2 поступает на адресный вход за поминающего устройства 13. Описанный процесс циклически повторяется, пока на адресные входы устройства 13 не поступит число, принадлежащее к разрешенному подмножеству всего мно- жества используемых чисел, что вызовет появление 1 на выходе устройства 13. Элемент И 21 открывается и через него проходит тактовый импульс с генератора 17, Этот импульс посту- пает на вход записи С выходного регистра 8 и в него записывается .число с блока 4, принадлежащее к разрешен- множеству. Выход элемента И 21 соединен также с входом R триггера 28, поэтому этот триггер сбрасывается,, на его выходе появляется О, который закрывает элемент И 24, и стохастический преобразователь переключается в режим перестановок.V который продолжается до прихода следующего запроса.

Формула изобретения

Стохастический преобразователь, содержащий выходной регистрэ выход которого является выходом преобразователя, блок памяти, выход которого подключен к первому входу схемы срав нения, второй вход которого является информационным входом преобразователя, а выход схемы сравнения соединен с управляющим входом блока управления, первый, второй и третий выхо- ды которого соединены соответственно с входом запуска генератора случайных чисел, управления записью выходного регистра и блока памяти, отличающийся тем, что, с целью повышения быстродействия, он содержит первый и второй регистры первый и второй счетчики, первый и

j tO ts 20 25 зо , 5

0

о 5

второй коммутаторы, причем выходы первого и второго коммутаторов соединены соответственно с информационным и адресным входами блока памяти, выход KOTOpoi o подключен к информационным входам выходного и первого регистров, выход первого регистра соединен с информационным входом второго регистра, выход которого подключен к первому информационному входу первого коммутатора, второй информационный вход которог о объединен с первым информацт-юнным входом второго коммутатора и подключен к выходу,, первого счетчика, выход второго счетчика соединен с вторым информационным входом второго коммутатора, третий информационный вход которого подключен к выходу генератора случай- Hiiix чисел, при этом блок управления содержит генератор тактовых импульсов, счетчик тактов, дешифратор, RS-тригге.р S с первого по восьмой элементы И, первый, второй и третий . элементы ИЛИ-НЕ, вход начальной установки преобразователя соединен с входом сброса счетчика тактов,, первыми входами первого и второго элементов И11И-НЕ и. управляющим входом первого коммутатора, выход генератора тактовых импульсов соединен с первыми входами первого, второго, третьего и четвертого . элементов И и счетным входом первого счетчика, выход второго элемента И подключен к входам управления записью первого и второго регистров ,, первому входу пятого элемента И и счетному входу счетчика тактов, первьм и второй выходы которого соединены с первым и вторым входами дешифратора соответственно, первый, второй, третий и четвертый выходы которого подключены соответственно к второму входу пятого элемента И, к первому входу третьего элемента ШШ-НЕ, к втор . входам первого и третьего элементов ИЛИ-НЕ, к третьему входу первого элемента ИЛИ-НЕ и второму Bxofi;y первого элемента И, выход которого подключен к входу второго счетчика, второй вход четвертого элемента И является управляющим, входом блока управления, а выход четвертого элемента И подключен к входу установки в О RS-триг- гера и является вторым выходом блока управления, выходы пятого и третьего

элементов И являются соответственно первым и третьим выходами блока уп- равлещ1я, прямой и инверсные выходы первого элемента ИЛИ-НЕ соединены со- .ответственно с вторым входом третьего и первым входом шестого элементов И, инверсный выход второго элемента ИЛИ-НЕ соединен с вторым входом второго и первыми входами седьмого и восьмого элементов И, вторые входы седьмого и восьмого элементов И подключены соответственно к инверсному

и прямому выходам третьего элемента ШШ-НЕ, выходы и восьмого элементов И подключены к первому и второму управляющим входам второго коммутатора, вход установки в

Г

RS-триггера является входом начальной установки преОбразорателя, а выход КБ-три1тера соединен с вторым входом шестого элемента И, выход которого подключен к второму входу второго элемента ИЛИ-НЕ и третьему входу четвертого элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для непрерывного экспресс-анализа потоков случайных чисел | 1983 |

|

SU1101839A1 |

| Стохастический преобразователь | 1981 |

|

SU1056191A1 |

| Генератор случайных процессов | 1984 |

|

SU1309021A1 |

| Генератор случайных процессов | 1981 |

|

SU985786A1 |

| Устройство для определения стационарности случайного процесса | 1984 |

|

SU1251120A1 |

| Коррелометр | 1983 |

|

SU1091173A1 |

| Генератор нестационарного случайного импульсного процесса | 1981 |

|

SU1008739A1 |

| Генератор многомерных случайных величин | 1984 |

|

SU1238068A1 |

| Генератор цепей Маркова | 1982 |

|

SU1049903A1 |

| Генератор случайного процесса | 1985 |

|

SU1335991A1 |

Изобретение относится к области вычир1ительной техники. Цель изобретения - повышение быстродействия. С этой целью в устройство введены два счетчика, два коммутатора, два регистра, которые соединены между собой и с остальными блоками схемы соответствующими функ-циональными связями. Изобретение целесообразно использовать в стохастических вычислительных машинах для моделирования и анализа ряда случайных процессов, а также в различных устройствах управления при случайном выборе за ограниченный интервал времени числа из определенного множества в условиях динамического назначения запретов на использование отдельных чисел . Изобретение обеспечивает большее быстродействие, чем известные, и может использоваться Б высоконадежных и быстродействующих системах, ил. с (О (Л N 4 ND Од :&

Редактор Л.Пчелинская

Заказ 3490/44Тираж 671

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие,г.Ужгород, ул.Проектная , 4

Составитель Э.Сечина

Техред О.Гортван Корректор О.Луговая

Подписное

| Датчик случайных чисел | 1976 |

|

SU572824A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Стохастический преобразователь | 1977 |

|

SU734766A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-06-30—Публикация

1984-01-23—Подача