«

Изобретение относится к вычислительной технике и может быть использовано при решении задач моделирования систем с учетом случайных внешних возмущающих факторов и случайных отклонений параметров объектов, а также при создании стохастических вычислительных машин и многоканальных датчиков случайных сигналов.

Цель изобретения - упрощение генератора.

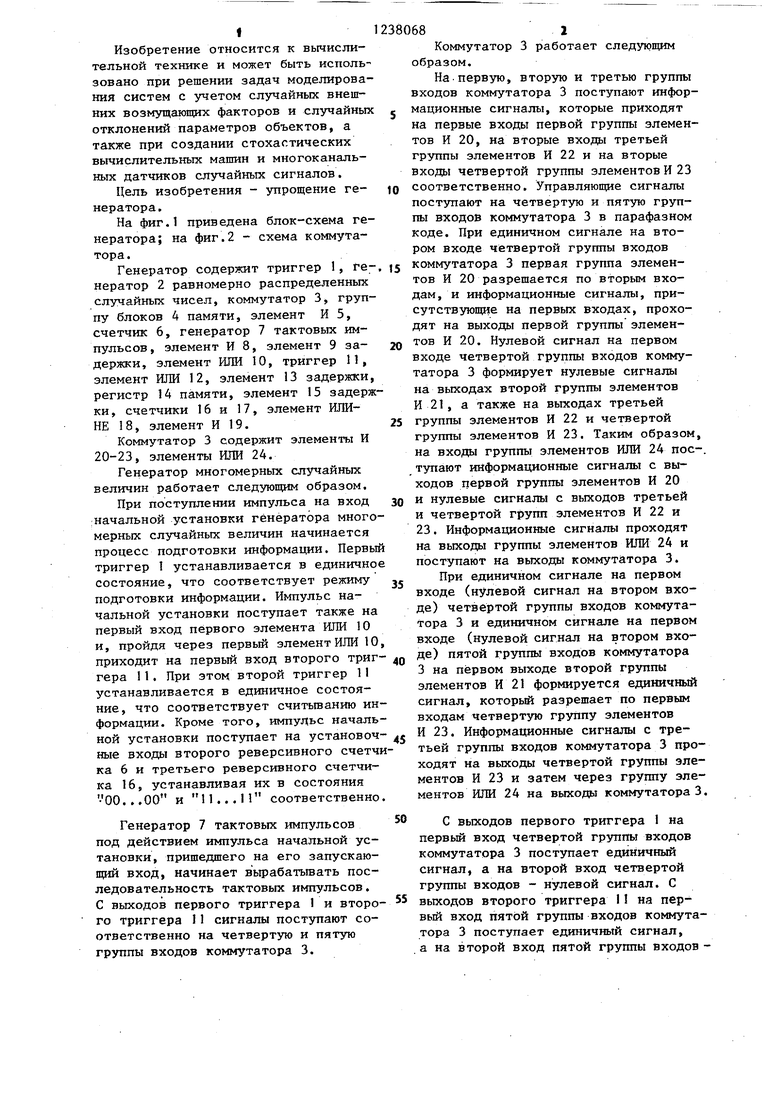

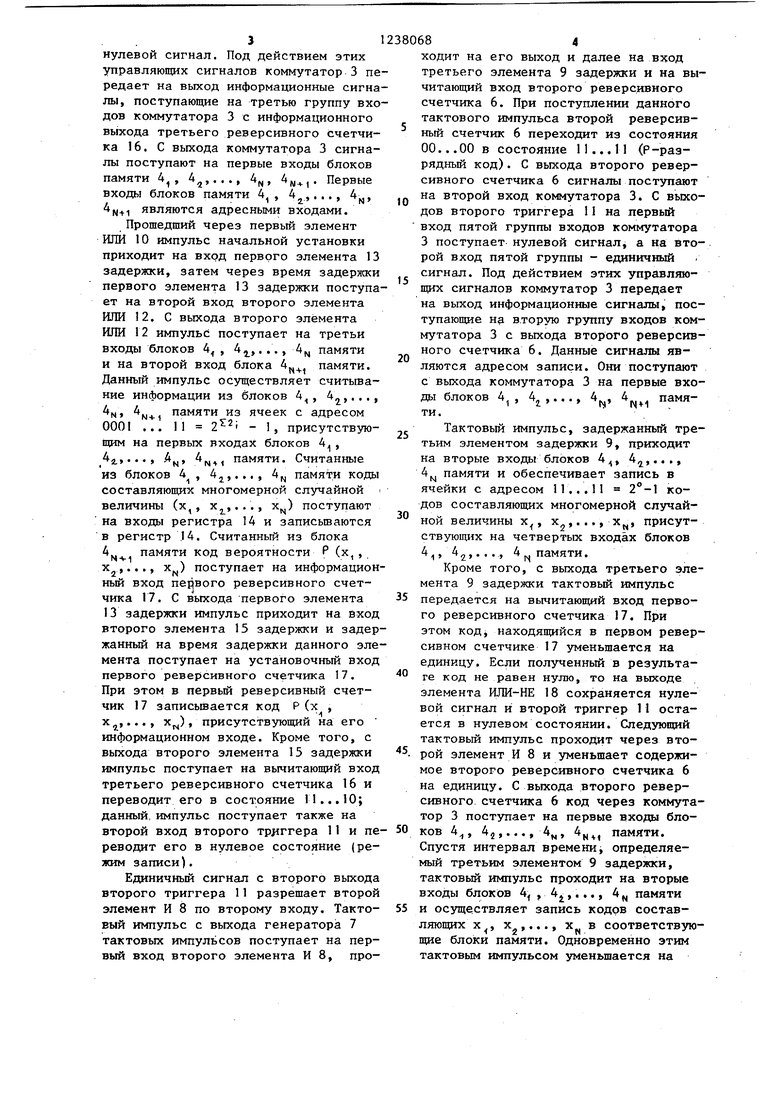

На фиг.1 приведена блок-схема генератора; на фиг.2 - схема коммутатора.

Генератор содержит триггер 1, генератор 2 равномерно распределенных случайных чисел, коммутатор 3, группу блоков А памяти, элемент И 5, счетчик 6, генератор 7 тактовых импульсов, элемент И 8, элемент 9 задержки, элемент РШИ 10, триггер 11, элемент ИЛИ 12, элемент 13 задержки, регистр 14 памяти, элемент 15 задержки, счетчики 16 и 17, элемент ИЛИ- НЕ 18, элемент И 19.

Коммутатор 3 содержит элементы И 20-23, элементы ИЛИ 24.

Генератор многомерных случайных величин работает следующим образом.

При поступлении импульса на вход :Начальной установки генератора многомерных случайных величин начинается процесс подготовки информации. Первы триггер 1 устанавливается в единично состояние, что соответствует режиму подготовки информации. Импульс начальной установки поступает также на первый вход первого элемента ИЛИ 10 и, пройдя через первый элемент ИЛИ 10 приходит на первый вход второго триггера 11. При этом второй триггер 11 устанавливается в единичное состояние, что соответствует считьшанию информации. Кроме того, импул(ьс начальной установки поступает на установочные входы второго реверсивного счетчи ка 6 и третьего реверсивного счетчика 16, устанавливая их в состояния 00...00 и 11...П соответственно

Генератор 7 тактовых импульсов под действием импульса начальной установки, пришедшего на его запускающий вход, начинает вырабатьшать последовательность тактовых импульсов. С выходов первого триггера 1 и второго триггера 11 сигналы поступают соответственно на четвертую и пятую группы входов коммутатора 3.

380682

Коммутатор 3 работает следующим образом.

На первую, вторую и третью группы входов коммутатора 3 поступают инфорJ мационные сигналы, которые приходят на первые входы первой группы элементов И 20, на вторые входы третьей группы элементов И 22 и на вторые входы четвертой группы элементов И 23

O соответственно. Управляющие сигналы поступают на четвертую и пятую группы входов коммутатора 3 в парафазном коде. При единичном сигнале на втором входе четвертой группы входов

5 коммутатора 3 первая группа элементов И 20 разрешается по вторым входам , и информационные сигналы, присутствующие на первых входах, проходят на выходы первой группы элемен0 тов И 20. Нулевой сигнал на первом входе четвертой группы входов коммутатора 3 формирует нулевые сигналы на выходах второй группы элементов И 21, а также на вьтходах третьей

5 группы элементов И 22 к четвертой

группы элементов И 23. Таким образом, на входы группы элементов ИЛИ 24 пос-. тупают информационные сигналы с выходов первой группы элементов И 20

0 и нулевые сигналы с выходов третьей и четвертой групп элементов И 22 к 23. Информационные сигналы проходят на выходы группы элементов ИЛИ 24 и поступают ка выходы коммутатора 3. При единичном сигнале на первом входе (нулевой сигнал на втором входе) четвертой группы входов коммутатора 3 и единичном сигнале на первом входе (нулевой сигнал на втором входе) пятой группы входов коммутатора 3 на первом выходе второй группы элементов И 21 формируется единичный сигнал, который разрешает по первым входам четвертую группу элементов И 23. Информационные сигналы с третьей группы входов коммутатора 3 проходят на выходы четвертой группы элементов И 23 и затем через группу элементов ИЛИ 24 на выходы коммутатора 3.

0 С выходов первого триггера 1 на первый вход четвертой группы входов коммутатора 3 поступает единичный сигнал, а на второй вход четвертой группы входов - нулевой сигнал. С

5 выходов второго триггера I на первый вход пятой группы входов коммутатора 3 поступает единичный сигнал, ,а на второй вход пятой группы входов5

0

5

нулевой сигнал. Под действием этих управляющих сигналов коммутатор 3 передает на выход информационные сигналы, поступающие на третью группу входов коммутатора 3 с информационного выхода третьего реверсивного счетчика 16. С выхода коммутатора 3 сигналы поступают на первые входы блоков памяти 4, А,..., 4,, 4,,. Первые входы блоков памяти 4, 4,..., 4|, 4„. являются адресными входами.

Прошедший через первый элемент ИЛИ 10 импульс начальной установки приходит на вход первого элемента 13 задержки, затем через время задержки первого элемента 13 задержки поступает на второй вход второго элемента ИЛИ 12. С выхода второго элемента ИЛИ 12 импульс поступает на третьи входы блоков 4 , 4,,..., 4, памяти и на второй вход блока 4 памяти. Данный импульс осуществляет считывание информации из блоков 4, 1,,.., N к(+, памяти из ячеек с адресом 0001 ... 11 - 1, присутствующим на первых входах блоков 4, 4,j.,..., А, А, памяти. Считанные из блоков 4 , 4j,..., 4f, памяти коды составляющих многомерной случайной велР1чины (х,, Xj,..., х) поступают на входы регистра 14 и записьшаются в регистр .14. Считанный из блока 4 памяти код вероятности Р (х,, X ,..., х) поступает на информацион- ньй вход первого реверсивного счетчика 17. С выхода первого элемента 13 задержки импульс приходит на вход второго элемента 15 задержки и задержанный на время задержки данного элемента поступает на установочный вход первого реверсивного счетчика 17. При этом в первый реверсивный счетчик 17 записьшается код Р(х , х,..., х), присутствующий на его информационном входе. Кроме того, с выхода второго элемента 15 задержки импульс поступает на вычитающий вход третьего реверсивного счетчика 16 и переводит его в состояние 11... 10; данный, импульс поступает также на второй вход второго триггера 11 и пе реводит его в нулевое состояние (режим записи).

Единичный сигнал с второго выхода второго триггера 11 разрешает второй элемент И 8 по второму входу. Такто- Еый импульс с выхода генератора 7 тактовых импульсов поступает на первый вход второго элемента ИВ, про

0

0

5

0

0

5

ходит на его выход и далее на вход третьего элемента 9 задержки и на вычитающий вход второго реверсивного счетчика 6. При поступлении данного тактового импульса второй реверсивный счетчик 6 переходит из состояния 00...00 в состояние 11... 11 (Р-раз- рядный код). С выхода второго реверсивного счетчика 6 сигналы поступают на второй вход коммутатора 3. С выходов второго триггера 11 на первый вход пятой группы входов коммутатора 3 поступает нулевой сигнал, а на второй вход пятой группы - единичный сигнал. Под действием этих управляющих сигналов коммутатор 3 передает на выход информационные сигналы, поступающие н вторую группу входов коммутатора 3 с выхода второго реверсивного счетчика 6. Данные сигналы являются адресом записи. Они поступают с выхода коммутатора 3 на первые входы блоков 4, 4j,,..., 4j, 4| памяти.

Тактовый импульс, задержанный третьим элементом задержки 9, приходит на вторые входы блоков 4, 4,..., 4 памяти и обеспечивает запись в ячейки с адресом 11... 11 кодов составляющих многомерной слзгчай- ной величины х, х ,..., х, присутствующих на четвертых входах блоков 4, 42,, 4 памяти.

Кроме того, с выхода третьего элемента 9 задержки тактовый импульс передается на вычитающий вход первого реверсивного счетчика 17. При этом код, находящийся в первом реверсивном счетчике 17 уменьшается на единицу. Если полученный в результате код не равен нулю, то на выходе элемента ИЛИ-НЕ 18 сохраняется нулевой сигнал и второй триггер 1I остается в нулевом состоянии. Следующий тактовый импульс проходит через второй элемент И 8 и уменьшает содержимое второго реверсивного счетчика 6 на единицу. С выхода второго реверсивного счетчика 6 код через коммутатор 3 поступает на первые входа блоков 4, 4j,..., 4„, 4j,, памяти. Спустя интервал времениi определяемый третьим элементом 9 задержки, тактовый импульс проходит на вторые входы блоков 4 , 4,,. .., 4 памяти и осуществляет запись кодов составляющих х, х,,..., -к в соответствующие блоки памяти. Одновременно этим тактовым импульсом уменьшается на

единицу содержимое первого реверсивного счетчика 17. Процесс записи продолжается до тех пор, пока содержимое первого реверсивного счетчика 17 не станет равным нулю. При этом на выходе элемента ИЛИ-НЕ 18 формируется единичный сигнал, который проходит через первый элемент ИЛИ 10 на первый вход второго триггера 11 и ус танавливает его в единичное состояние (режим считьшания) .

С выходов второго триггера 11 на первый вход пятой группы входов мутатора 3 поступает единичный сиг- нал, а на второй вход пятой группы входов - нулевой сигнал. Под действием этих управляющих сигналов коммутатор 3 передает на выход сигналы, присутствующие на третьей группе входов коммутатора 3. Данные сигналы (адрес считьшания) поступают на первые входы блоков 4 , 4,..., 4,, f памяти. Прошедший через первый элемент ИЛИ 10 импульс проходит через первый элемент 13 задержки и второй элемент ИЛИ 12 на третьи входы блоков 4 , 4 ,..., 4 памяти и на второй вход блока 4|у памяти. Данный импульс осуществляет считывание информации из ячеек с адресом 0...011...10 блоков 4 , 4,j ,.. ., 4щ, 4., памяти. Считанные из блоков 4 , , 4f памяти коды записьгоаются в регистр -14, код из блока 4, памяти записьшает- ся в первый реверсивный счетчик 17 импульсом, прошедшим через второй элемеят 15 задержки. Кроме того, импульс, прошедший через второй элемент 15 задержки, уменьшает на еди- ницу содержимое третьего реверсивного счетчика 16 и переводит второй триггер 11 в нулевое состояние (режим записи)..

Вновь считанный код составляющих (х , X ,..., Хц) записывается в блоки 4, 4,..., 4 памяти такое коли- tiecTBO раз, которое равно коду, хранящемуся в первом реверсивном счетчике 17. После этого считывается новый код составляющих (к,, Хр,) и код вероятности р (х , х ,..., X ) и повторяется режим записи.

Процесс подготовки данных завершается тогда, когда при коде 00...00 в третьем реверсивном счетчике 16 вырабатьгаается сигнал переноса и с вьпсода перекоса третьего реверсивного счетчика 16 поступает на первый вход третьего элемента И 19, разрешенный по второму входу сигналом с выхода элемента ИЛИ-НЕ 18. С выхода третьего элемента И 19 сигнал проходит на второй вход первого триггера 1 и переводит его в нулевое состояние (режим генерирования кодов многомерной случайной величины).

В режиме генерирования многомерных случайных величин единичный сигнал с второго выхода первого триггера 1 поступает на первый выход устройства, кроме того, этот сигнал поступает на второй вход четвертой группы входов коммутатора 3 и разрешает прохождение сигналов с первой группы входов коммутатора 3 на выход коммутатора 3. Нулевой сигнал с первого выхода первого триггера 1 приходит на первый вход четвертой группы входов коммутатора 3 и запрещает прохождение сигналов, поступающих на вторую и третью группы входов ког-вдута- тора 3. Генератор 2 равновероятных случайных чисел, вьшолненный на базе регистров сдвига, вырабатьшаетР -разрядные двоичные коды равновероятных случайных чисел, которые являются адресами для считьшания кодов составляющих многомерный случайной величины х (х,, X ,..., X ). С выхода генератора 2 равновероятных случайных чисел сигналы поступают на первую группу входов коммутатора 3, проходят на его выход и поступают на первые (адресные) входы блоков 4, 4j,..., 4, 4., памяти.

С выхода генератора 7 тактовых импульсов тактовый импульс приходит на второй вход первого элемента И 5, разрешенный по первому входу единичным сигналом с второго выхода первого триггера 1, и приходит на выход первого элемента И 5. С выхода первого элемента И 5 импульс поступает на первый вход второго элемента ИЛИ 12, проходит на выход второго элемента ИПИ I2 и поступает на третьи входы блоков 4, 4j,..., 4 памяти и на второй вход блока 4, памяти. Данным импульсом производится считывание кодов составляющих (х , х,..., х) из ячеек, адрес которых присутствует на первых входах блоков 4,, 42,..., 4 памяти. С выходов блоков 4, 4 памяти коды составляющих многомерной случайной величины X (х , Xj,..., х) поступают на вторые выходы устройства. После этого вырабатьшается новое равновероятное число (адрес) и новый тактовый импульс для считьшания кодов. Процесс формирования значения многомерный случайной величины х повторяется необходимое количество раз.

Генератор 2 равновероятных случайных, чисел формирует равновероятные числа с частотой большей, чем частота генератора 7 тактовых импульсов, это позволяет не синхронизировать работу данных блоков.

Быстродействие генератора много- мерньк случайных величин при формировании кодов многомерной случайной ве- личины равно времени считьгаания информации из блоков памяти.

Формула ИЗ обр.е тения

Генератор многомерных случайных величин, содержащий группу блоков памяти, регистр памяти, коммутатор, генератор равномерно распределенных случайных чисел, первый счетчик, ге- нератор тактовых импульсов, первый элемент задержки, первый элемент И, отличающийся тем, что, с целью упрощения, он содержит второй и третий счетчики, второй и тре- тий элементы задержки, два триггера, второй и третий элементы И, элемент ИЛИ-НЕ, два элемента ИЛИ, единичный вход первого триггера объединен с входом Пуск генератора тактовых импульсов, с первым входом первого элемента ИЛИ, с установочными входами первого и второго счетчиков и является входом Пуск генератора, выход генератора равномерно распреде- лениых случайных чисел соединен с первым информационным входом коммутатора, выход которого соединен с адресными входами блоков памяти группы, выходы первых N блоков памяти из группы, где (N+1). - число блоков памяти в группе, являются информационными выходами генератора и соединены с группой информационнь1Х входов реQ

5

0

5

0 j ц 5 Q

гистра памяти, выход которого соединен с информационными входами каждого i-ro (i 1,N) блока памяти группы, выход (N + 1)-го блока памяти группы соединен с информационным входом третьего счетчика, вычитающий вход которого подключен к выходу первого элемента задержки и к входам Запись первых N блоков памяти группы, входы Считывание блоков памяти группы соединены с выходом второго элемента ИЛИ, первый вход которого подключен к выходу первого элемента И, первый вход которого подключен к нулевому выходу первого триггера и является выходом Режим генерирования генератора, единичный и нулевой выходы первого триггера соединены соответственно с первым и вторым управляющими входами коммутатора, третий и четвертый управляющие входы которого подключены соответственно к единичному и нулевому выходам второго триггера, а второй и третий информационные входы коммутатора подключены к информационным выходам соответственно первого и второго счетчиков, выход генератора тактовых импульсов соединен с вторым входом первого элемента И и с первым входом второго элемента И, второй вход которого подключен к нулевому выходу второго триггера, а выход второго элемента И соединен с вычитающим входом первого счетчика и с входом первого элемента задержки, выход первого элемента ИЛИ соединен с единичным входом второго триггера и с входом второго элемента задержки, выход которого соединен с вторым входом второго элемента ИЛИ и с входом третьего элемента задержки, выход которого соединен с нулевым входом второго триггера, с установочным входом третьего счетчика и с вы-. читающим входом второго счетчика, выход переполнения которого соединен с первым входом третьего элемента И, выход которого соединен с нулевым входом первого триггера, выходы разрядов третьего счетчика соединены с входами элементов ИШ-НЕ соответственно, выход которого соедииен с вторым входом третьего элемента И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор случайного поля | 1989 |

|

SU1636996A1 |

| Устройство для испытания логичес-КиХ блОКОВ | 1979 |

|

SU832565A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Генератор многомерных случайных величин | 1981 |

|

SU966692A1 |

| Генератор случайного процесса | 1983 |

|

SU1111159A1 |

| Устройство для автоматического контроля параметров | 1982 |

|

SU1111134A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1325501A1 |

| Устройство для моделирования систем управления | 1980 |

|

SU935965A1 |

| Вероятностное устройство для решения краевых задач | 1982 |

|

SU1101838A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1310838A1 |

Изобретение относится к области вычислительной техники и может быть использовано при решении задач моделирования систем с учетом случайных внешних возмущающих факторов и случайных отклонений параметров объектов, а также при создании стохастических вычислительных машин и многоканальных датчиков случайных сигналов. Целью изобретения является упрощение генератора. Генератор содерясит генератор тактовых импульсов, генератор равномерно распределенных случайных чисел, два триггера, три счетчика, элемент ИЛИ-НЕ, три элемента И, два элемента ИЛИ, три элемента задержки, группу блоков памяти, регистр памяти, коммутатор. Технико- экономическая эффективность генератора определяется высоким быстродействием генератора многомерных случайных величин и более широкими по сравнению с известными устройствами функциональными возможностями: моделированием многомерных случайных величин с заданным многомерным законом распределения, аппаратной реализацией процесса предварительной подготовки исходной информации, что необходимо для перспективных вычислительных и управляющих систем, а также более простым решением. 2 ил. О) to оо СХ) Ot) 00

| Устройство для испытания логичес-КиХ блОКОВ | 1979 |

|

SU832565A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Генератор многомерных случайных величин | 1982 |

|

SU1084791A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-06-15—Публикация

1984-11-19—Подача