. f

Изобретение относится к автомати ке и вычислительной технике и может быть использовано при построении различных устройств обработки дискретной информации.

Целью изобретения является сокращение объема оборудования и повьшени быстродействия устройства.

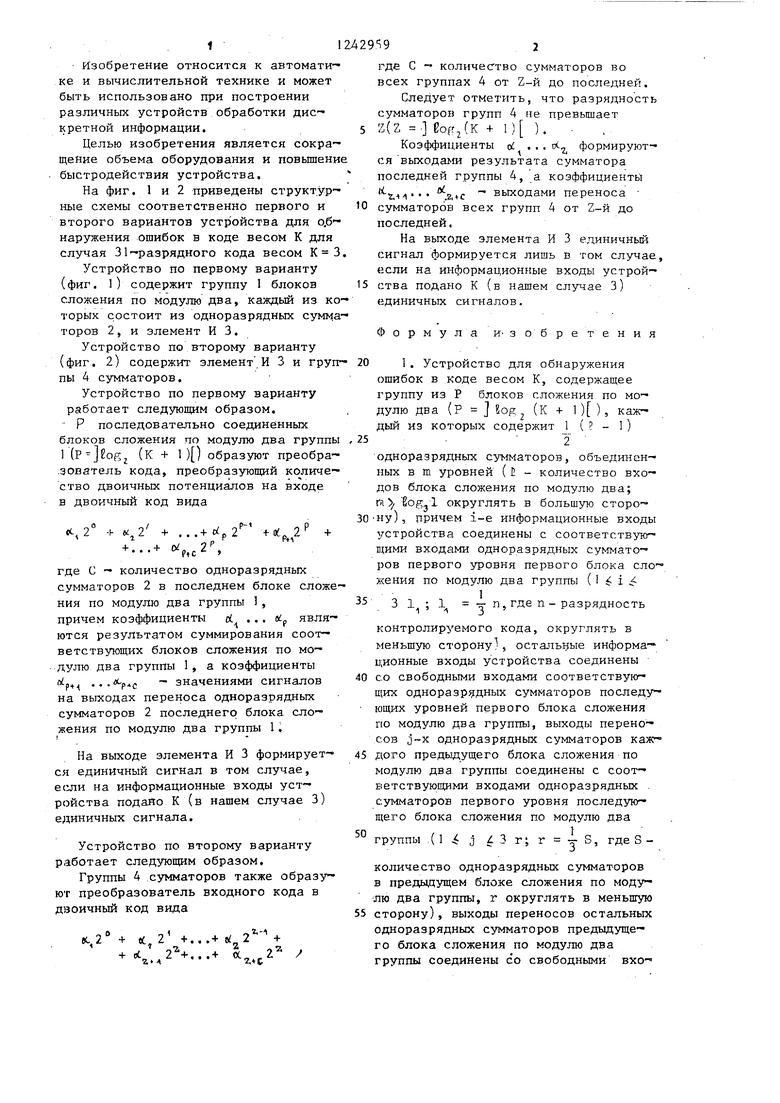

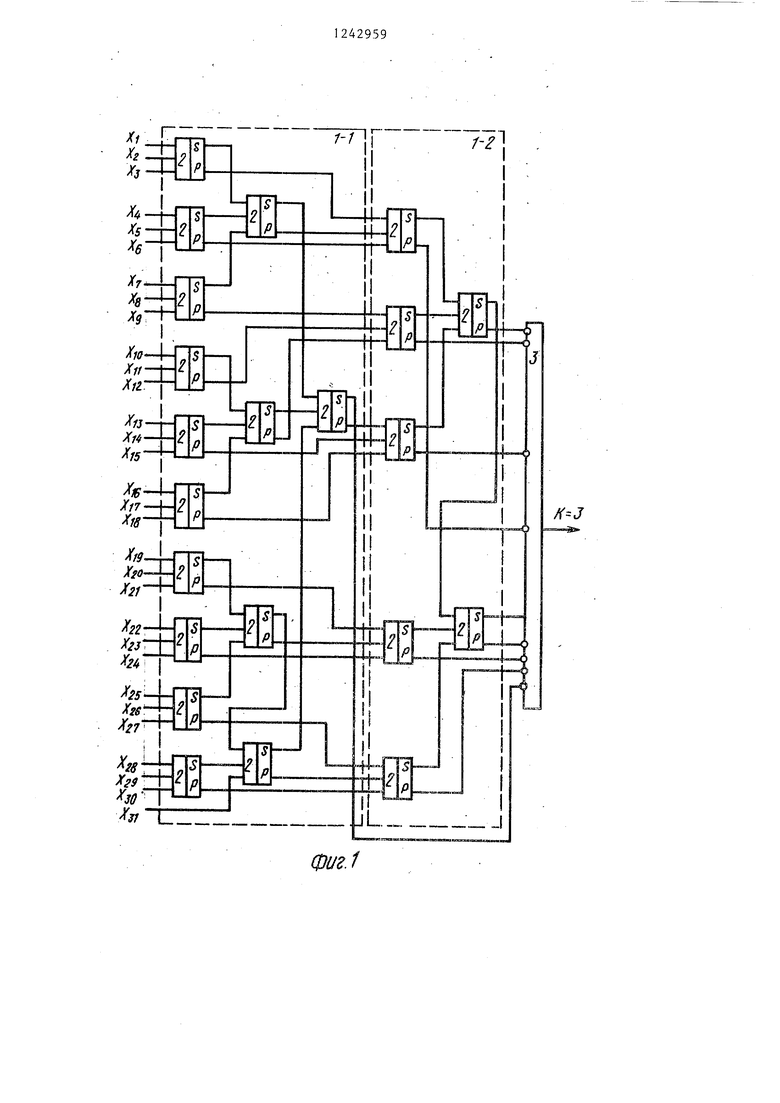

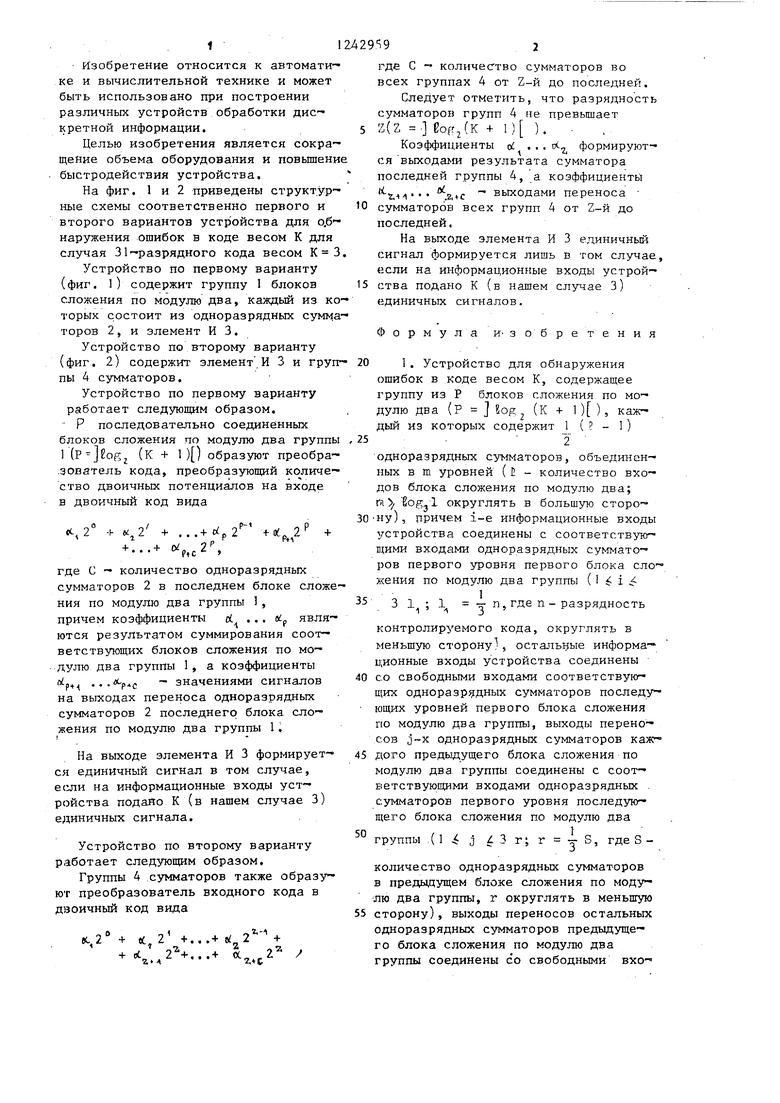

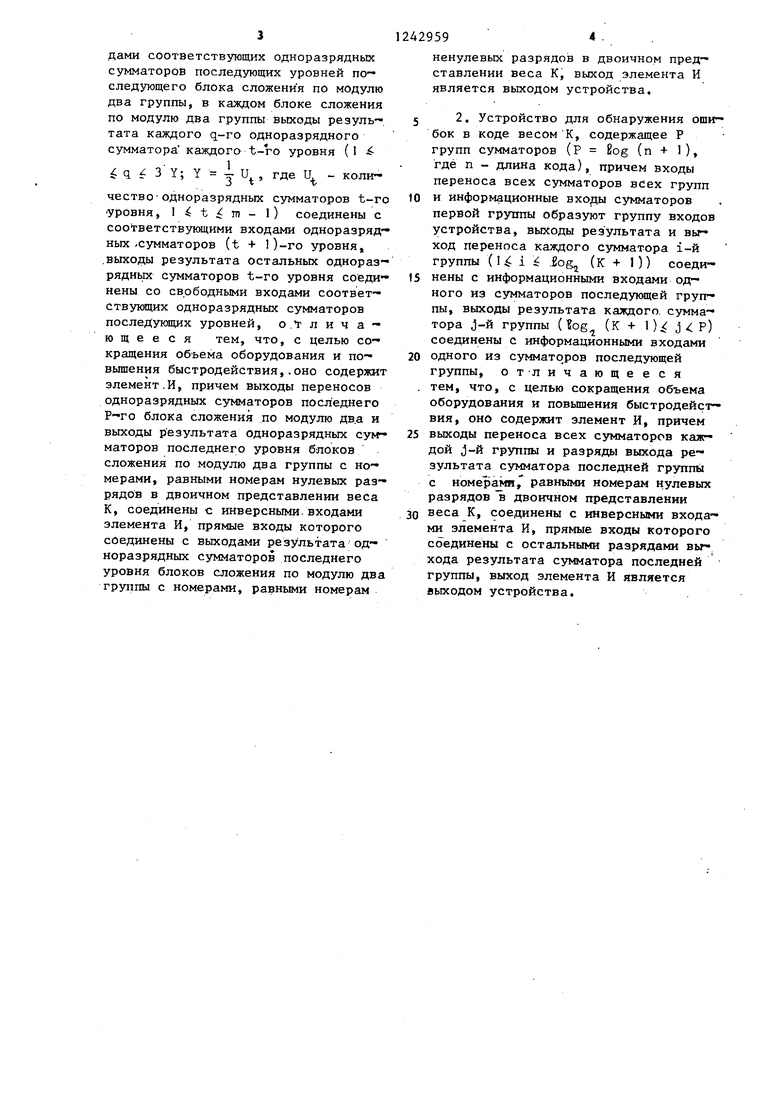

На фиг. 1 и 2 приведены структурные схемы соответственно первого и второго вариантов устр ойства для о.б- наружения ошибок в коде весом К для случая 31-разрядного кода весом

Устройство по первому варианту (фиг. 1) содержит группу 1 блоков сложения по модулю два, каждый из которых состоит из одноразрядньк сумматоров 2, и элемент И 3.

Устройство по второму варианту (фиг. 2) содержит элемент.И 3 и группы 4 сумматоров.

Устройство по первому варианту работает следующим образом.

Р последовательно соединённых блоков сложения по модулю два группы

1 (P-JEogj (к + I )) образуют преобра- .зователь кода, преобразующий количество двоичных потенциалов на входе в двоичный код вида

2

-ь .,2 . + .. .+

...+ 2 .c2%

Р-1

.2

где С - количество одноразрядных сумматоров 2 в последнем блоке сложения по модулю два группы 1, причем коэффициенты d ... являются результатом суммирования соответствующих блоков сложения по модулю два группы 1, а коэффициенты

.,

р-с

- значениями сигналов

на выходах переноса одноразрядных сумматоров 2 последнего блока сложения по модулю два группы 1.

I

На выходе элемента И 3 формируется единичный сигнал в том случае, е(ши на информационные входы устройства подано К (в нашем случае 3) единичных сигнала.

Устройство по второму варианту работает следующим образом.

Группы 4 сумматоров также образуют преобразователь входного кода в дзоичный код вида

. 2 - «.

+ .,2Ч...+ /

где С - количество сумматоров во всех группах 4 от Z-й до последней.

Следует отметить, что разрядность сумматоров групп 4 не превышает Z(Z eofr(K +)).

Коэффициенты oL . . . л, Формируются вьЕХОдами результата сумматора последней группы 4, а коэффициенты г. .E.tc выходами переноса сумматоров всех групп 4 от Z-й до последней.

На выходе элемента И 3 единичный сигнал формируется лишь в том случае, если на информационные входы устрой- ства подано К (в нашем случае З) единичных сигналов.

ормула и-зобретения

1. Устройство для обнаружения ошибок в коде весом К, содержащее группу из Р блоков сложения по модулю два (Р Kog (к + 1 ) ), каждый из которых содержит 1 ( - 1)

2 одноразрядных сумматоров, объединенных в m уровней (Е - количество входов блока сложения по модулю два; округлять в большую сторо- ну), причем i-e информационные входы устройства соединены с соответствующими входами одноразрядных сумматоров первого уровня первого блока сложения по модулю два группы (i i

V п, где п - разрядность

контролируемого кода, округлять в меньшую сторону, остальные информационные входы устройства соединены

со свободными входами соответствую

щих одноразрядных сумматоров последу- ющих уровней первого блока сложения по модулю два группы, выходы переносов одноразрядных сумматоров кая

дого предыдущего блока сложения по модулю два, группы соединены с соот- Е1етствующи:ми входами одноразрядных . сумматоров первого уровня последующего блока сложения по модулю два

1

руппы .(1 j Z. 3 г:

J S, где Sколичество одноразрядных сумматоров в преды,цущем блоке сложения по модулю два группы, г округлять в меньшую 55 сторону), выходы переносов остальных одноразрядных cyivraaTOpOB предыдущего блока сложения по модулю два группы соединены со свободными 3 Y; Y - у U, где .

и. - коли

дами соответствующих одноразрядных сумматоров последующих уровней последующего блока сложения по модулю два группы, в каждом блоке сложения по модулю два группы выходы резуль-. тата каждого q-ro одноразрядного сумматора каждого t-ro уровня (I

3

чество-одноразрядных сумматоров t-ro уровня, 1 t m - 1) соединены с соответствзтощими входами одноразрядных .сумматоров (t + 1)-го уровня, .выходы результата остальных однораз- рядньк сумматоров t-ro уровня соединены со свободными входами соответствующих одноразрядных сумматоров последующих уровней, о.Т л и ч а - ю щ е е с я тем, что, с целью сокращения объема оборудования и повышения быстродействия,.оно содержит элемент.И, причем выходы переносов одноразрядных сумматоров последнего Р-го блока сложения по модулю дв.а и выходы р езультата одноразрядных маторов последнего уровня блоков сложения по модулю два группы с номерами, равными номерам нулевых разрядов в двоичном представлении веса К, соединены с инверсными.входами элемента И, прямые входы которого соединены с выходами результата одноразрядных сумматоров последнего уровня блоков сложения по модулю два группы с номерами, равными номерам

ненулевых разрядов в двоичном представлении веса К, выход элемента И является выходом устройства.

2. Устройство для обнаружения omir- бок в коде весом К, содержащее Р групп сумматоров (Р Bog (п + 1), где п - длина кода), причем входы переноса всех сумматоров вСех групп

и информационные входы сумматоров первой группы образуют группу входов устройства, выходы результата и выход переноса каждого сумматора i-й группы (1 i og (к + 1)) соеди-

нены с информационными входами одного из сумматоров последующей группы, выходы результата каядого. сумматора j-й группы (log (К + 1) ) соединены с информационными входами

одного из суммато.ров последующей группы, от-личающееся тем, что, с целью сокращения объема оборудования и повышения быстродействия, оно содержит злемент И, причем

выходы переноса всех сумматоров каждой J-й группы и разряды выхода результата сумматора последней группы с номерами, равными номерам нулевых разрядов 3 двоичном представлении

веса К, соединены с инверсными входами элемента И, прямые входы которого соединены с остальными разрядами выхода результата сумматора последней группы, выход элемента И является выходом устройства.

Xi Хг 3

/4

/5 6

/.Uj

.,я

///-i//г--|-у I

//J-r-l

//5 .

///H/ЙУ-

//.-. -

X22-

I/ «

.

zr

, |д % ТГ

./

7.71

J

фиг.г

Составитель В. Гречнев . Редактор 0. Юрковецкая Т«хред,О.Гортвай. Корректор С. Шекмар

Заказ 3706/48

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, , Раушская наб,, д. 4/5

Производственно-ттолиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь двоично-десятичного кода в двоичный | 1980 |

|

SU888104A1 |

| Параллельный накапливающий сумматор | 1987 |

|

SU1587496A1 |

| Устройство для формирования остатка по модулю три | 1982 |

|

SU1084799A1 |

| Матричное устройство для умножения чисел по модулю 2 @ -1 | 1985 |

|

SU1254471A1 |

| Устройство для возведения в квадрат и извлечения квадратного корня | 1987 |

|

SU1413627A1 |

| Матричное устройство для возведения в квадрат и извлечения квадратного корня | 1983 |

|

SU1107119A1 |

| Устройство для извлечения квадратного корня | 1984 |

|

SU1180886A1 |

| Устройство для умножения @ -разрядных двоичных чисел | 1990 |

|

SU1783519A1 |

| Арифметическое устройство | 1976 |

|

SU650074A1 |

| Устройство для преобразования по функциям Уолша | 1983 |

|

SU1137479A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано для построения различных устройств обработки дискретной информации. Целью изобретения является сокращение объема оборудования и повышение быстродействия устройства. Первый вариант устройства содержит группу блоков сложения по модулю два, каждьй из которых состоит из одноразрядных сумматоров, и элемент И. Второй вариант содержит элемент И и группы сумматоров. 2 с.п. ф-лы, 2 ил. с to 4 N9 СП

| Многоразрядный счетчик с параллельным переносом | 1976 |

|

SU788388A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фостер К | |||

| Ассоциативные параллельные процессоры | |||

| - М | |||

| Энергия, 1981 | |||

| с | |||

| Способ прикрепления барашков к рогулькам мокрых ватеров | 1922 |

|

SU174A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Фостер К | |||

| Ассоциативные параллельные процессоры.,.- М;: Энергия, 1981 | |||

| с | |||

| Приспособление для удаления таянием снега с железнодорожных путей | 1920 |

|

SU176A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1986-07-07—Публикация

1983-07-15—Подача