ел

00

«

4

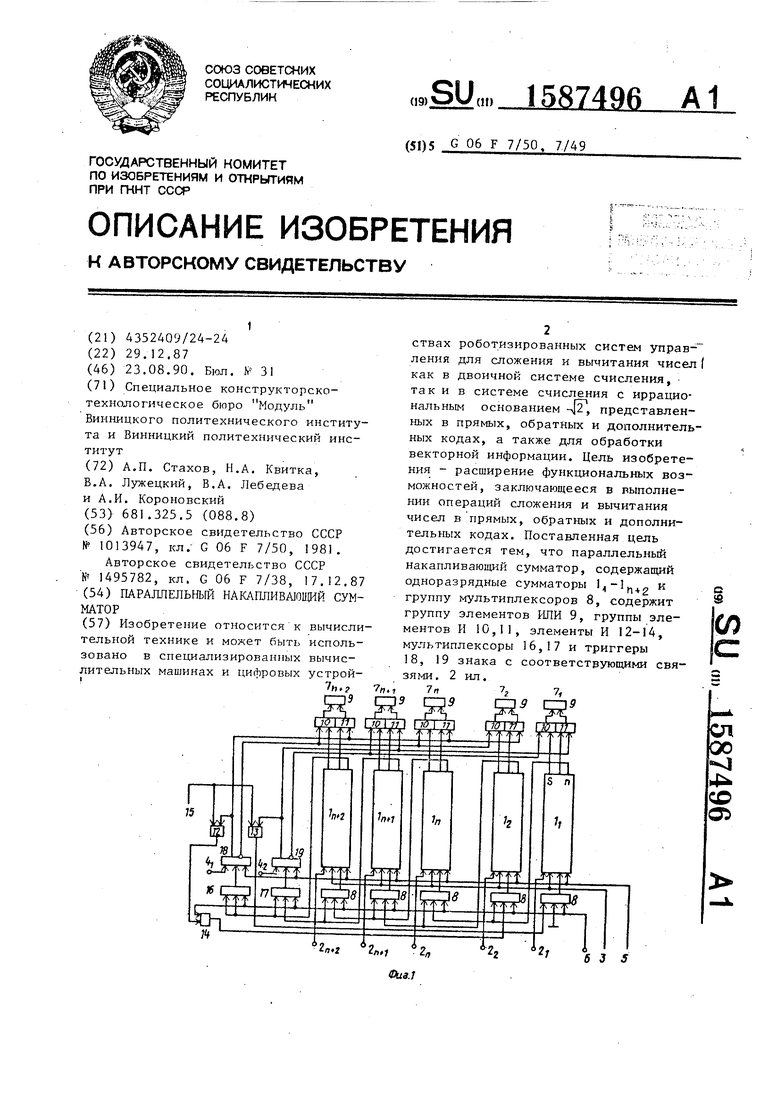

Изобретение относится к Ёычисли- тельной технике и может быть исноль- зовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем уцрав- ления для сложения и вычитания чисел как в двоичной системе счисления, так и в системе .счисления с иррациональным основанием , представ ленных в прямых, обратных и дополнительных кодах, а также для обработки векторной информации.

Цель изобретения - расширение функциональных возможностей за счет выполнения операций сложения и вычитания чисел в прямых, обратных и дополнительных кодах.

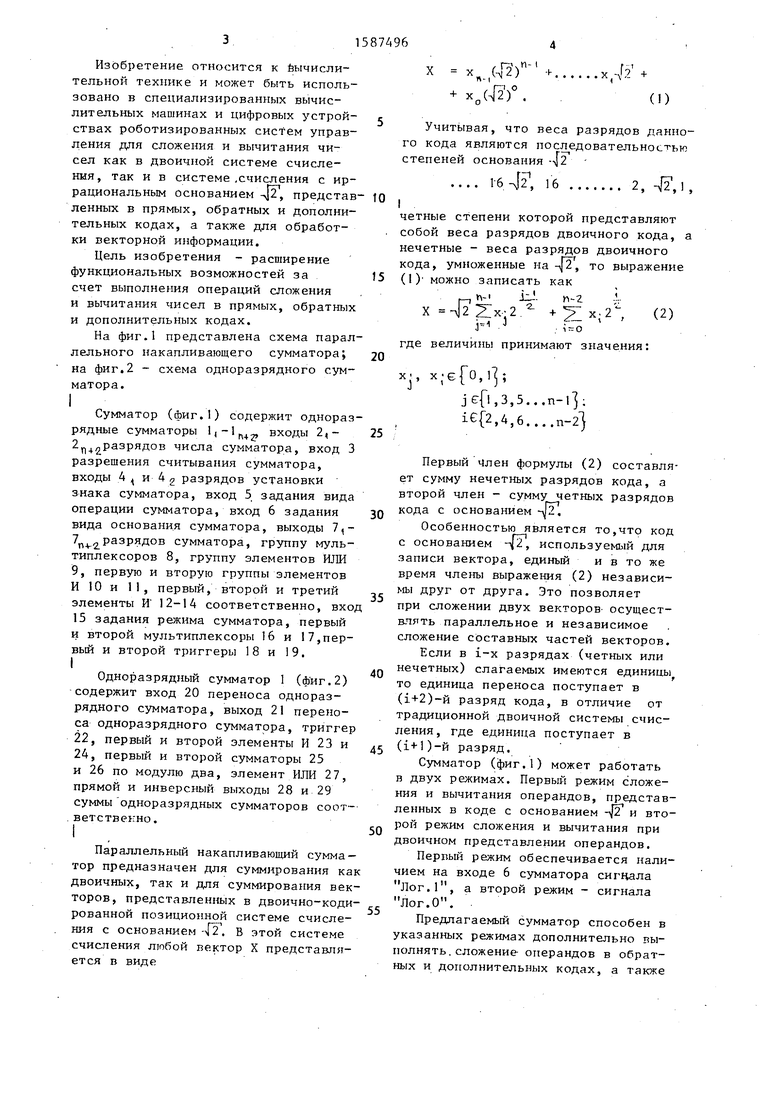

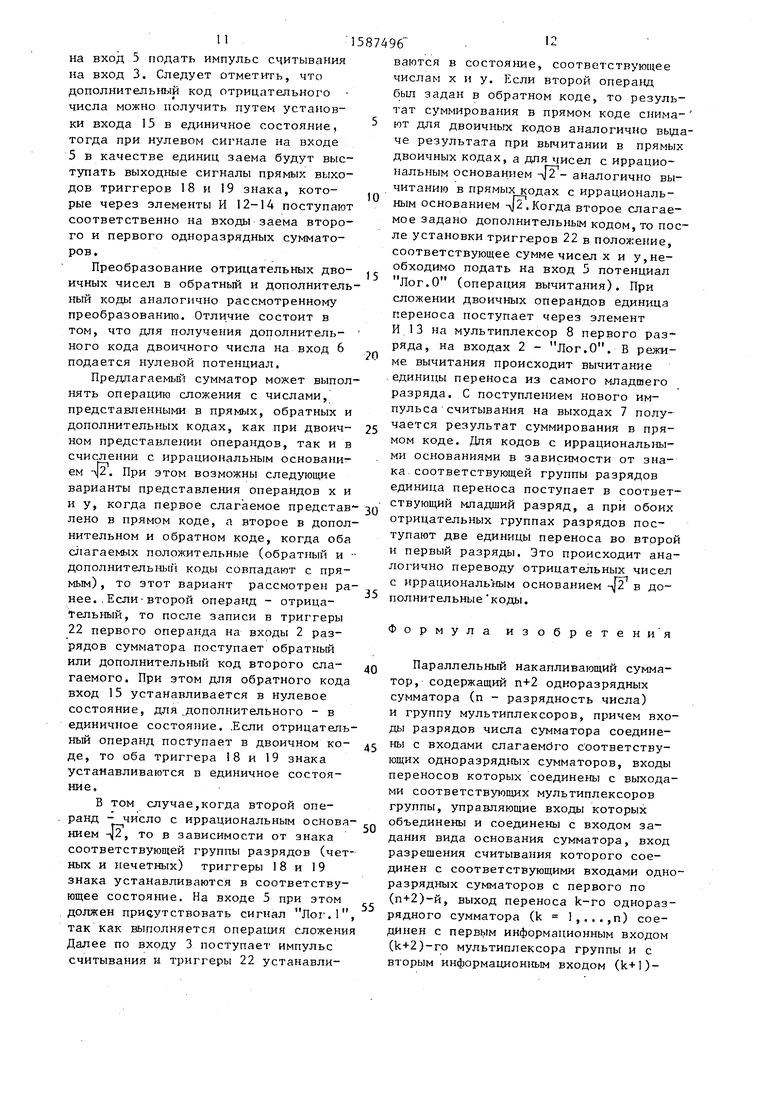

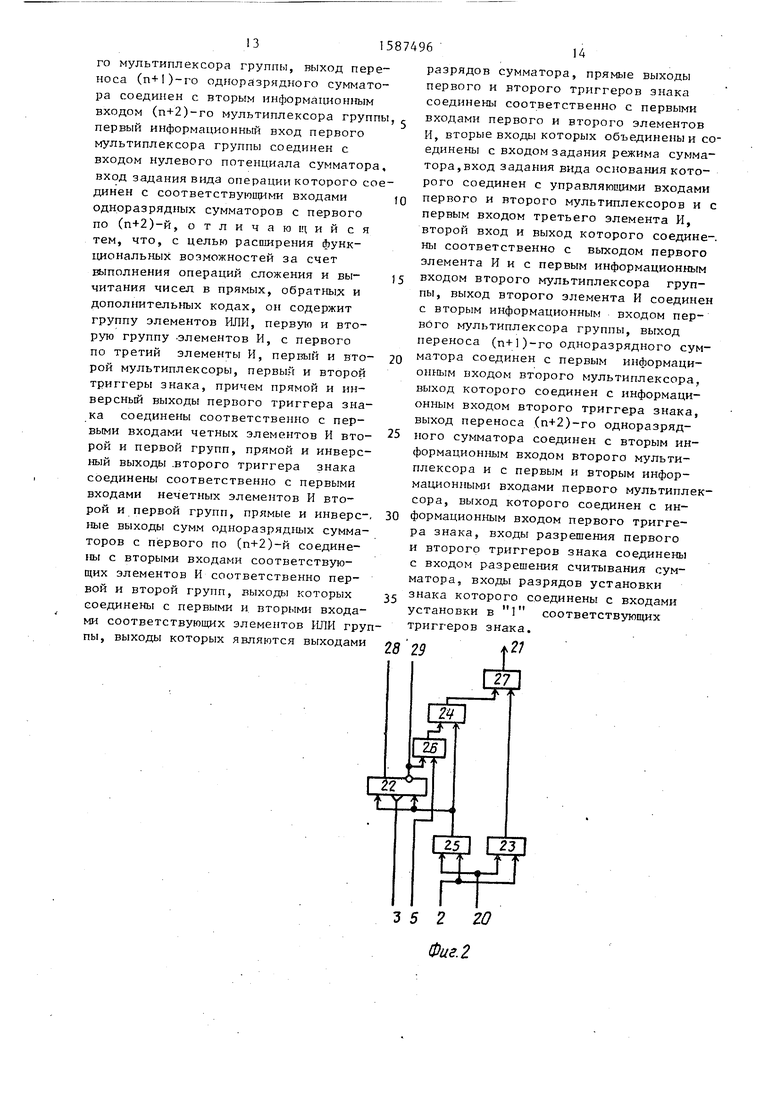

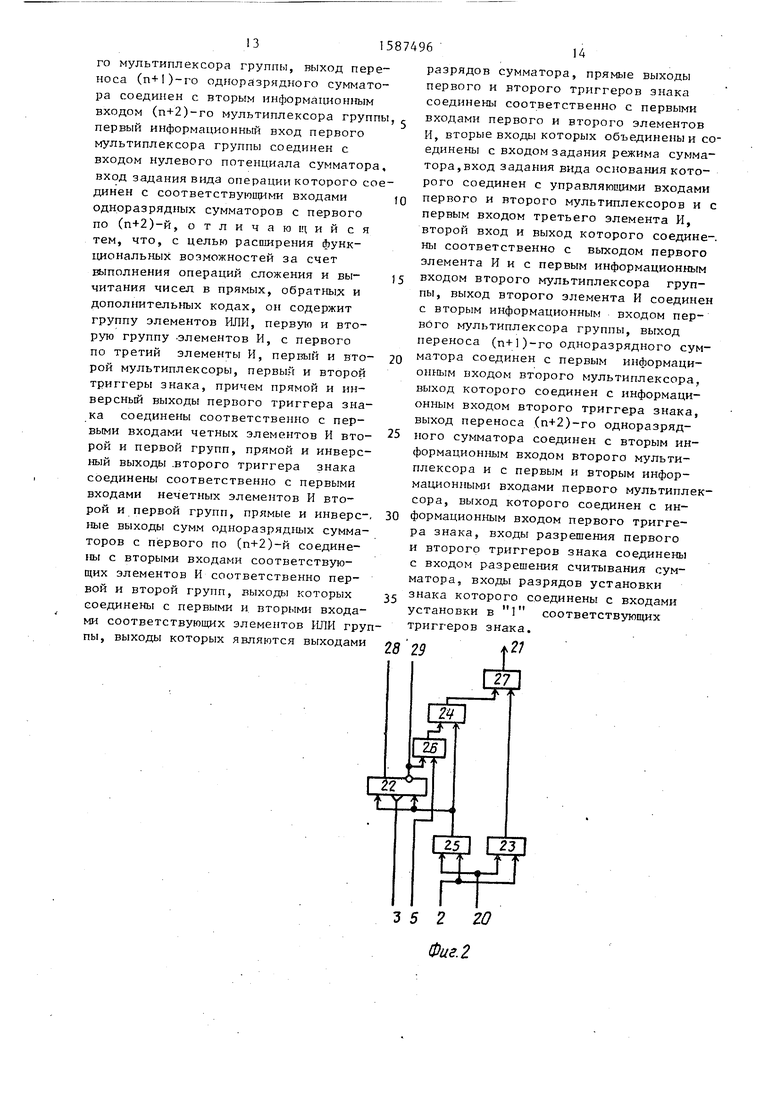

На фиг.1 представлена схема параллельного накапливающего сумматора; на фиг.2 - схема одноразрядного сумматора.

I

Сумматор (фиг.1) содержит одноразрядные сумматоры ,42 входы 2,- 2 разтряр,отз числа сумматора, вход 3 разрешения считывания сумматора, входы 4 и 42 разрядов установки знака сумматора, вход 5 задания вида операции сумматора, вход 6 задания вида основания сумматора, выходы 7,- п Р зряцов сумматора, группу мультиплексоров 8, группу элементов ИЛИ 9, первую и вторую группы элементов И 10 и 11, первый, второй и третий элементы И 12-14 соответственно, вход 15 задания режима сумматора, первый и второй мультиплексоры 16 и 17,первый и второй триггеры 18 и 19.

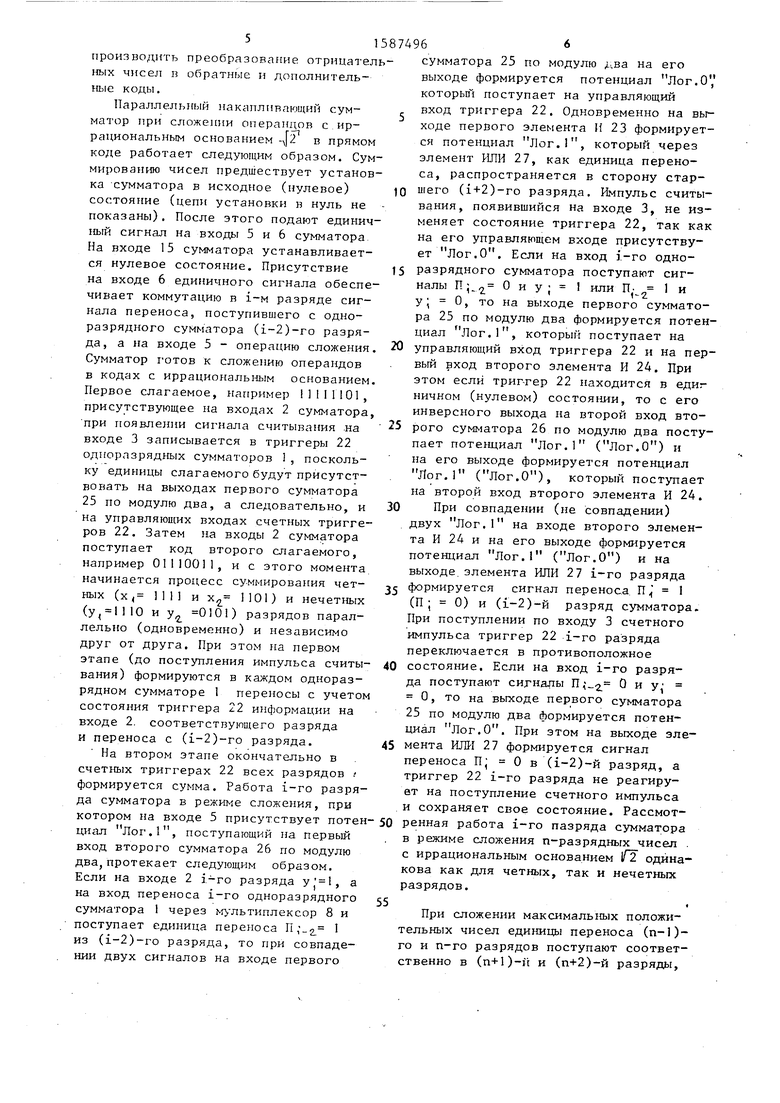

Одноразрядный сумматор 1 (фиг.2) содержит вход 20 переноса одноразрядного сумматора, выход 21 переноса одноразрядного сумматора, триггер 22, первый и второй элементы И 23 и 24, первый и второй сумматоры 25 и 26 по модулю два, элемент ИЛИ 27, прямой и инверсный выходы 28 и 29 суммы одноразрядных сумматоров соот- .ветственно. I

Параллельный накапливающий сумматор предназначен для суммирования как двоичных, так и для суммирования векторов, представленных в двоично-кодированной позиционной системе счисле- ния с основанием . В этой системе счисления любой вектор X представляется в виде

х,(12)- .ь, -X .

.х,-л1

/24(1)

Учитывая, что веса разрядов даннго кода являются последовательность степеней основания -f .. 1-6 л, 16 2, 4,

I

четные степени которой представляют собой веса разрядов двоичного кода, нечетные - веса разрядов двоичного кода, умноженные на , то выражени (1) можно записать как

., л- iJ. ri-г 1 X .-2. (2)

О

где величины принимают значения:

xj, x;efo,

jcfl,3,5... i42,A,6....n-2

Первый Член формулы (2) составляет сумму нечетных разрядов кода, а второй член - сумму четных разрядов кода с основанием ,

Особенностью является то,что код с основанием -(, используемый для записи вектора, единый и в то же время члены выражения (2) независимы друг от друга. Это позволяет при сложении двух векторов- осуществлять параллельное и независимое сложение составных частей векторов. Если в i-x разрядах (четных или нечетных) слагаемых имеются единицы то единица переноса поступает в (1+2)-й разряд кода, в отличие от традиционной двоичной системы счисления, где единица поступает в (1+1)-й разряд.

Сумматор (фиг.1) может работать в двух режимах. Первый режим сложения и вычитания операндов, представленных в коде с основанием - и второй режим сложения и вычитания при двоичном представлении операндов.

Первый режим обеспечивается наличием на входе 6 сумматора сигнала Лог.1, а второй режим - сигнала Лог.О. .

Предлагаемый сумматор способен в указанных режимах дополнительно выполнять, сложение операндов в обратных и дополнительных кодах, а также

производить преобразование отрицательных чисел Б обратные и дополнительные коды,

Параллельнрлй накапливающий сумматор при сложении операндов с.иррациональным основанием 4 в прямом коде работает следующим образом. Суммированию чисел предшествует установка сумматора в исходное (нулевое) состояние (цепи установки в нуль не показаны). После этого подают единичный сигнал на входы 5 и 6 сумматора На входе 15 сумматора устанавливается нулевое состояние. Присутствие на входе 6 единичного сигнала обеспечивает коммутацию в i-м разряде сигнала переноса, поступившего с одноразрядного сумматора (i-2)-ro разряда, а на входе 5 - операцию сложения. Сумматор готов к сложению операндов в кодах с иррациональным основанием. Первое слагаемое, например 1 1 I 1101, присутствующее на входах 2 сумматора, при появлен 1и сигнала считывания .на входе 3 записывается в триггеры 22 одноразрядных сумматоров , поскольку единицы слагаемого будут присутствовать на выходах первого сумматора 25 по модулю два, а следовательно, и на управляющих входах счетных триггеров 22. Затем на входы 2 сумматора поступает код второго слагаемого, например 01110011, и с этого момента начинается процесс суммирования четных (х 111 и х 1101) и нечетных (у,1110 и у 0101) разрядов параллельно (одновременно) и независимо друг от друга. При зтом на первом этапе (до поступления импульса считывания) формируются в каждом одноразрядном сумматоре 1 переносы с учетом состояния триггера 22 информации на входе 2. соответствующего разряда и переноса с (1-2)-го разряда.

На втором этапе окончательно в счетных триггерах 22 всех разрядов .- формируется сумма. Работа i-ro разряда сумматора в режиме сложения, при

1587496

сумматора 25 по модулю два на его выходе формируется потенциал Лог KOTopbrfi поступает на управляющий вход триггера 22. Одновременно на ходе первого элемента И 23 формируе ся потенциал Лог.Г , который через элемент ИЛИ 27, как единица перено- распространяется в сторону стар

у л X

са,

10

15

20

25

щего (i+2)-ro разряда. Кмпульс счит вания, появившийся на входе 3, не и меняет состояние триггера 22, так к на его управляющем входе присутству ет Лог.О. Если на вход i-ro одноразрядного сумматора поступают сигналы П; О и у; 1 или П. 1 и у; О, то на выходе первого суммат ра 25 по модулю два формируется пот циал Лог.1, который поступает на управляющий вход триггера 22 и на п вый вход второго элемента И 24, При этом если триггер 22 находится в еди ничном (нулевом) состоянии, то с его инверсного выхода на второй вход вто рого сумматора 26 по модулю два пост пает потенциал Лог. Г (Лог.О) и на его выходе формируется потенциал Лог.1 (Лог.О), который поступае на второй вход второго элемента И 24

При совпадении (не совпадении) двух Лог.1 на входе второго элемен та И 24 и на его выходе формируется потенциал Лог. Г (Лог.О) и на выходе.элемента ИЛИ 27 i-ro разряда формируется сигнал переноса 1 (П ; 0) и (i-2)-й разряд сумматора При поступлении по входу 3 счетного импульса триггер 22 i-ro разряда переключается в противоположное состояние. Если на вход i-ro разряда поступают сигналы П, О и у 0, то на выходе первого сумматора 25 по модулю два формируется потенциал Лог.О. При этом на выходе эле- 45 мента ИЛИ 27 формируется сигнал

переноса П; О в (i-2)-A разряд, а триггер 22 i-ro разряда не реагирует на поступление счетного импульса и сохраняет свое состояние. Рассмот30

35

40

..1

в режиме сложения п-разрядных чисел с иррациональным основанием iTJ одйнапоступающий на первый вход второго сумматора 26 по модулю два,протекает следующим образом. Если на входе 2 i-ro разряда , а на вход переноса i-ro одноразрядного сумматора 1 через м -льтиплексор 8 и поступает единица переноса . 1 из (i-2)-ro разряда, то при совпадении двух сигналов на входе первого

55

кона как для четных, так и нечетных разрядов.

При сложении максимальных положительных чисел единицы переноса (п-1)- го и п-го разрядов поступают соответственно в (п+1)-й и (п+2)-й разряды.

1587496

сумматора 25 по модулю два на его выходе формируется потенциал Лог.О , KOTopbrfi поступает на управляющий вход триггера 22. Одновременно на выходе первого элемента И 23 формируется потенциал Лог.Г , который через элемент ИЛИ 27, как единица перено- распространяется в сторону стару л X

са,

10

15

20

25

щего (i+2)-ro разряда. Кмпульс считывания, появившийся на входе 3, не изменяет состояние триггера 22, так как на его управляющем входе присутствует Лог.О. Если на вход i-ro одноразрядного сумматора поступают сигналы П; О и у; 1 или П. 1 и у; О, то на выходе первого сумматора 25 по модулю два формируется потенциал Лог.1, который поступает на управляющий вход триггера 22 и на первый вход второго элемента И 24, При этом если триггер 22 находится в едиг- ничном (нулевом) состоянии, то с его инверсного выхода на второй вход второго сумматора 26 по модулю два поступает потенциал Лог. Г (Лог.О) и на его выходе формируется потенциал Лог.1 (Лог.О), который поступает на второй вход второго элемента И 24.

При совпадении (не совпадении) двух Лог.1 на входе второго элемента И 24 и на его выходе формируется потенциал Лог. Г (Лог.О) и на выходе.элемента ИЛИ 27 i-ro разряда формируется сигнал переноса 1 (П ; 0) и (i-2)-й разряд сумматора. При поступлении по входу 3 счетного импульса триггер 22 i-ro разряда переключается в противоположное состояние. Если на вход i-ro разряда поступают сигналы П, О и у 0, то на выходе первого сумматора 25 по модулю два формируется потенциал Лог.О. При этом на выходе эле- 5 мента ИЛИ 27 формируется сигнал

переноса П; О в (i-2)-A разряд, а триггер 22 i-ro разряда не реагирует на поступление счетного импульса и сохраняет свое состояние. Рассмот0

5

0

в режиме сложения п-разрядных чисел с иррациональным основанием iTJ одйна5

кона как для четных, так и нечетных разрядов.

При сложении максимальных положительных чисел единицы переноса (п-1)- го и п-го разрядов поступают соответственно в (п+1)-й и (п+2)-й разряды.

в которых, как и в триггерах 18 и 19 знака, до суммирования записана нулевая информация. Результат суммы с прямых выходов триггеров 22 через элементы И 10,к вторым входам которых подсоединены инверсные выходы триггеров 18 и 19, и через элементы ИЛИ 9 поступает на выходы 7 сумматора.

При сложении двоичных операндов ,д (второй режим работы) в отличие от рассмотренного режима единицы переноса i-x одноразрядных сумматоров поступают на вторые информационные входы (i+l)-x мультиплексоров 8 (а г не на первые информационные входы (i+2)-x мультиплексоров 8). Кроме того, во втором режиме работы к входу 6 прилагается потенциал Лог.О. Разрядность двоичных операндов равна n+l разрядам. В остальном процедура операции сложения на всех этапах аналогична описанной.

Рассмотрим работу параллельного накапливающего сумматора в режиме 25 вычитания в кодах с иррациональным основанием лГ. В этом режиме сумматор перед операцией также устанавливается в исходное состояние (нулевое состояние), после чего на вход 5 по- ЗО дается нулевой потенциал, а на вход 6 - единичный потенциал и на входе 15 устанавливается единичное состояние. Затем в триггеры 22 сумматора записывается п+2 разрядное уменьшаемое путем Подачи на его входы 2с последующим приложением импульса считывания на вход 3. Процесс вычитания, как и сложения, происходит одновременно, независимо и одинако- 0 во среди четных и нечетных разрядов и начинается в момент приложения к входам 2 сумматора n+2-разрядного вычитаемого. Уменьшаемое и вычитаеое представлены в прямых кодах. По 45 аналогии со сложением вычитание удоб-. о рассматривать на основе работы i-ro разряда сумматора.

Если при подаче на вход 2 i-ro

разряда у; 1 по входу переноса поступает сигнал заема из (i-2)-ro разряда, то при совпадении двух сигналов на входе первого сумматора 25 j по модулю два на его выходе формируется потенциал Лог.О, который поступает на управляющий вход триггера 22. Одновременно на выходе первого элемента И 23 форми8

,д г

25 О0 5

0

руется потенциал Лог.1, который через элемент ИЛИ 27 по выходу переноса как единица заема z расЦространяется в сторону (i+2)-ro разряда. Триггер 22; сохраняет свое состояние. Если на вход i-ro разряда поступают сигналы Z; О и у 1 или z; 1 „у. 5, то на выходе первого сумматора 25; по модулю два формируется потенциал Лог.Г , которьй поступает на управляющий вход триггера 22; и первый вход второго элемента И 24; j Если триггер находится в единичном (нулевом) состоянии, то с его инверсного выхода на второй вход второго сумматора 26; по модулю два поступает потенциал Лог.О (Лог.1) и на его выходе формируется потенциал Лог-.О (Лог. I), который поступает на второй вход второго элемента И . При несовпадении (совпадении) двух Лог.Г на входе второго элемента И 24; на его выходе формируется потенциал Лог.О (Лог.1) и.на шине переноса формируется сигнал заема z ; О (z; 1). В момент поступления по входу 3 счетного импульса триггер 22; переключается в противоположное сос- тояние.

При вычитании в прямом коде, в случае, когда уменьшаемое меньше вычитаемого, возникают заемы в триггеры

18и 19 знака, предварительно установленные в нулевое состояние, которые в виде единиц заема распространяются в мультиплексоры 16 и,17.

С их помощью триггеры 18 и 19 устанавливаются в единичное состояние, которое означает, что соответствую- пще разряды отрицательные. Возможны случаи, когда единица заема в знаковые триггеры возникает только в нечетных или только в четных разрядах, тогда соответственно только триггер

19знака или только триггер 18 знака устанавливаются в единичное состояние. Дпя получения результата вычитания на выходах 7 в прямом коде, поскольку в триггерах 22 фиксируется в данном случае разность чисел

X и у в дополнительном коде, необходимо вычесть единицу из самого младхиего нечетного (первого) разряда сумматора при отрицательных чет- Hi.ix разрядах, или из самого младшего четного (второго) разряда при отрицательных четных разрядах и вместе из нечетного и четного (первого и второго) разрядов при отрицательном результате. Ввиду того, что вхо 15 в режиме вычитания находится в единичном состоянии, то единичные сигналы триггеров 18 и 19 знака поступают соответственно на первый и второй информационные мультиплексоры 8 второго и.первого разрядов, в первом случае через последовательно соединенные элементы И 12 и 14, а во втором случае - через элементы И 13. А затем происходит вычитание из записанного в триггерах 22 дополнительного кода результата единицы заема четных и нечетных разрядов или двух еди . ниц заема для обеих групп разрядов после подачи на вход 3 импульса считывания.

Результат вычитания снимают с инверсных входов триггеров 22, если все разряды отрицательные, или с прямых выходов - если все разряды положительные. В том случае, когда одна группа разрядов -отрицательная, а-другая - полол ительная, отрицательные разряды снимаются с инверсных выходов, а положительшзш - с прямых выходов триггеров 22. При вычитании двоичных п+2 разрядных операндов заем единицы i-ro разряда сумматора делается в (1+1)-м разряде, т.е. слева стоящем. Дпя обеспечения этого мультиплексоры 8 подключают к входу переноса i-ro одноразрядного сумматора выход переноса из (i-l)-ro разряда.

Отличие операции вычитания двоичных операндов состоит в том, что всегда оба триггера 18 и 19 знака устанав ливаются в единичное состояние (когда уменьшаемое меньше вычитаемого) и в том, что на входе 6 присутствует сигнал Лог.О. Для получения результата вычитания в прямом коде необходимо вычесть единицу заема из самого младшего разряда. Так как на первом входе элемента И 14 присутствует потенциал Лог.О, то единица заема с выхода триггера 19 знака через элемент И 13 распространится только в первый разряд сумматора. В остальном процесс вычитания ничем не отличается от ранее рассмотренного; При этом если результат вычитания отрицательный, то его прямой код снимается с инверсных выходов

1587496

10

триггеров 22 сумматора, в противном случае - с прямых выходов тех же триггеров.

Параллельный сумматор можно использовать для преобразования прямых кодов отрицательных чисел в обратные и дополнительные коды. Для получения обратного кода отрицательного числа JO в счислении с иррациональным основа- кием необходимо триггеры 18 и 19 знака установить в единичное состояние, а на входы 2 (п+2)-х разрядов подать прямой код числа, на входы 15 5 и 6 сигнал Лог.Г и через время срабатывания сумматора 25 по модулю два подать на вход 3 импульс считы-, вания. При этом на выходах 7 сумматора будет присутствовать обратный 0 код исходного операнда. Преобразование отрицательного числа в дополнительный код состоит в том, что после записи числа в сумматор необходимо на вход 5 подать нулевой сигнал, 5 а к входам 2 первого и вторрго разрядов (к младшему нечетному и четному разрядам) сумматора приложить дв е единигда заема. После чего через промежуток времени, равный или больше 0 времени задержки информации на первом сумматоре 25 по модулю два, на вход 3 подать импульс считывания.

По истечении времени заема на входах 7 параллельного накапливающего сумматора будет присутствовать дополнительный код отрицательного чис- 4 ла. В том случае, когда нечетные раз- : ряды отрицательные, а четные - поло- жительные и наоборот, то в единичное состояние устанавливается триггер i 19 знака, а триггер 18 знака - в нулевое и наоборот: триггер 19 знака- устанавливается в нулевое состояние а триггер 18 знака - в единичное. В данном случае процесс получения обратного кода числа аналогичен ранее рассмотренному. Отличие состоит в том, что обратный код положитель- ных разрядов снимается с прямых выходов триггеров 22, а отрицательных - с инверсных выходов тех же триггеров.

Дпя образования дополнительного кода в этом случае необходимо приложить единицу заема ко входу 2 первого или второго разрядов сумматора в зависимости от состояния триггеров 18 и 19 знака и при нулевом сигнале

10

15

11 1587496

на вход 5 подать импульс считывания на вход 3. Следует отметить, что дополнительшяи код отрицательного числа можно получить путем установки входа 15 в единичное состояние, тогда при нулевом сигнале на входе 5 в качестве единиц заема будут выступать выходные сигналы прямых выходов триггеров 18 и 19 знака, которые через элементы И 12-14 поступают соответственно на входы заема второго и первого одноразрядных сумматоров .

Преобразование отрицательных двоичных чисел в обратный и дополнительный коды аналогично рассмотренному преобразованию. Отличие состоит в том, что для получения дополнитель- ного кода двоичного числа на вход 6 подается нулевой потенциал,

Предлагаемьй сумматор может выполнять операцию сложения с числами, представленными в прямых, обратных и дополнительных кодах, как при двоичном представлении операндов, так и в счислении с иррациональным основанием -л|2. При этом возможны следующие варианты представления операндов х и и у, когда первое слагаемое представ- зо лено в прямом коде, а второе в дополнительном и обратном коде, когда оба cJiaraeMbix положительные (обратный и - дополнительный коды совпадают с прямым), то зтот вариант рассмотрен ранее. . Если второй операнд - отрицательный, то после записи в триггеры 22 первого операнда на входы 2 разрядов сумматора поступает обратный или дополнительный код второго слагаемого. При этом для обратного кода вход 15 устанавливается в нулевое состояние, для дополнительного - в единичное состояние. .Если отрицатель- ньй операнд поступает в двоичном ковачи бы та ют че дв на чи ны мо ле со об Л сл пе И ря ме ед ра пу ча мо ми ка ед ст от ту н ло с пол

Ф

20

25

40

де, то оба триггера 18 и 19 знака устанавливаются в единичное состояние,

В том случае,когда второй опе- ранд -число с иррациональным основанием -J2, то в зависимости от знака соответствующей группы разрядов (четных и нечетных) триггеры 18 и 19 знака устанавливаются в соответствующее состояние. На входе 5 при этом должен присутствовать сигнал Лог.1, так как выполняется оператшя сложения Далее по входу 3 поступает импульс считывания и триггеры 22 устанавли45

50

55

то су и ды ны ющ пе ми гру объ дан раз дин раз (пряддин (k+ вто

0

5

7496

о

12

ваются в состояние, соответствующее числам X и у. Если второй операнд был задан в обратном коде, то результат суммирования в прямом коде снима- ют для двоичных кодов аналогично выдаче результата при вычитании в прямых двоичных кодах, а для чисел с иррациональным основанием аналогично вычитанию в прямых кодах с иррациональным основанием л|2. Когда второе слагаемое задано дополнительным кодом, то после установки триггеров 22 в положение, соответствующее сумме чисел X и у,необходимо подать на вход 5 потенциал Лог.О (операция вычитания). При сложении двоичных операндов единица переноса поступает через элемент И 13 на мультиплексор 8 первого разряда, на входах 2 - Лог.О. В режиме вычитания происходит вычитание единицы переноса из самого младшего разряда. С поступлением нового импульса считывания на выходах 7 получается результат суммирования в прямом коде. Для кодов с иррациональными основаниями в зависимости от знака соответствующей группы разрядов единица переноса поступает в соответствующий младший разряд, а при обоих отрицательных группах разрядов поступают две единицы переноса во второй н первый разряды. Это происходит аналогично переводу отрицательных чисел с иррациональ ным основанием - в до- 5 полнительные коды.

Формула изобретен и я

0

5

зо

0

5

0

5

Параллельный накапливающий сумматор, содержащий п+2 одноразрядных сумматора (п - разрядность числа) и группу мультиплексоров, причем входы разрядов числа сумматора соединены с входами слагаембго соответствующих одноразрядных сумматоров, входы переносов которых соединены с выходами соответствующих мультиплексоров группы, управляющие входы которых объединены и соединены с входом задания вида основания сумматора, вход разрешения считывания которого соединен с соответствующими входами одноразрядных сумматоров с первого по ()-й, выход переноса k-ro одноразрядного сумматора (k 1,...,п) соединен с первым информационным входом (k+2)-rp мультиплексора группы и с вторым информационным входом (k+1)го мультиплексора группы, выход переноса (п+1)-го одноразрядного сумматора соединен с вторым информационным входом (п+2)-го мультиплексора группы, первый информационный вход первого мультиплексора группы соединен с входом нулевого потенциала сумматора, вход задания вида операции которого соединен с соответствуюищми входами одноразрядных сумматоров с первого по (п+2)-й, отличающийся тем, что, с целью распшрения функ- 1Ц1Ональных возможностей за счет выполнения операций сложения и вычитания чисел в прямых, обратных и дополнительных кодах, он содержит группу элементов ИЛИ, первую и вторую группу .элементов И, с первого по третий элементы И, первый и второй мультиплексоры, первый и второй триггеры знака, причем прямой и инверсный выходы первого триггера знака соединены соответственно с пер- вьми входами четных элементов И второй и первой групп, прямой и инверсный выходы .второго триггера знака соединены соответственно с первыми входами нечетных элементов И вто10

20

25

разрядов сумматора, прямые выходы первого и второго триггеров знака соединены соответственно с первым входами первого и второго элемент И, вторые входы которых объединены единены с входом задания режима сум тора, вход задания вида основания кот рого соединен с управляюп1ими входа первого и второго мультиплексоров первым входом третьего элемента И, второй вход и выход которого соед ны соответственно с выходом перво элемента И и с первым информационн входом второго мультиплексора гру пы, выход второго элемента И соеди с вторым информационным входом пе вого fyльтиплeкcopa группы, выход переноса (п+1)-го одноразрядного су матора соединен с первым информаци онным входом второго мультиплексора выход которого соединен с информаци онным входом второго триггера знака выход переноса (п+2)-го одноразрядного сумматора соединен с вторым ин формационным входом второго мультиплексора и с первым и вторым информационными входами первого мультипл сора, выход которого соединен с ин .uiJci, выход которого соединен с ин- L°e выхо пы ° Формационнь,м входом первого триггеНЫе ВЫХОПЫ fVMM ПГТИППООПГГТТТГ, ,,, ffii I

ные выходы сумм одноразрядных сумматоров с первого по (п+2)-й соединены с вторыми входами соответствующих элементов И соответственно первой и второй групп, выходы которых соединены с первыми и вторыми входами соответствующих элементов РШИ группы

выходы которых являются выходами /70 «л

со 29

ра знака, входы разрешения первого и второго триггеров знака соединены с входом разрешения считывания сумматора, входы разрядов установки 35 знака которого соединены с входами установки в I соответствующих триггеров знака.

2;

, 10

20

5

разрядов сумматора, прямые выходы первого и второго триггеров знака соединены соответственно с первыми входами первого и второго элементов И, вторые входы которых объединены и соединены с входом задания режима сумматора, вход задания вида основания которого соединен с управляюп1ими входами первого и второго мультиплексоров и с первым входом третьего элемента И, второй вход и выход которого ны соответственно с выходом первого элемента И и с первым информационным входом второго мультиплексора группы, выход второго элемента И соединен с вторым информационным входом первого fyльтиплeкcopa группы, выход переноса (п+1)-го одноразрядного сумматора соединен с первым информационным входом второго мультиплексора, выход которого соединен с информационным входом второго триггера знака выход переноса (п+2)-го одноразряд ного сумматора соединен с вторым информационным входом второго мультиплексора и с первым и вторым информационными входами первого мультиплексора, выход которого соединен с ин.uiJci, выход которого соединен с ин- ° Формационнь,м входом первого тригге.uiJci, выход которого соединен с ин- Формационнь,м входом первого тригге ffii I

«л

29

ра знака, входы разрешения первого и второго триггеров знака соединены с входом разрешения считывания сумматора, входы разрядов установки знака которого соединены с входами установки в I соответствующих триггеров знака.

2;

| название | год | авторы | номер документа |

|---|---|---|---|

| Параллельный накапливающий сумматор | 1988 |

|

SU1578710A2 |

| Конвейерный сумматор | 1989 |

|

SU1714588A1 |

| Параллельный накапливающий сумматор | 1986 |

|

SU1399726A1 |

| ПАРАЛЛЕЛЬНЫЙ СУММАТОР-ВЫЧИТАТЕЛЬ НА НЕЙРОНАХ СО СКВОЗНЫМ ПЕРЕНОСОМ | 2012 |

|

RU2523942C2 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Одноразрядный сумматор-вычитатель | 1986 |

|

SU1368875A1 |

| Параллельный накапливающий сумматор | 1988 |

|

SU1564614A1 |

| Сумматор последовательного действия | 1989 |

|

SU1689945A2 |

| Накапливающий сумматор | 1989 |

|

SU1702375A1 |

| Последовательный сумматор кодов с иррациональными основаниями | 1987 |

|

SU1439577A1 |

Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и цифровых устройствах роботизированных систем управления для сложения и вычитания чисел как в двоичной системе счисления, так и в системе счисления с иррациональными основанием √2, представленных в прямых, обратных и дополнительных кодах, а также для обработки векторной информации. Целью изобретения является расширение функциональных возможностей, заключающееся в выполнении операций сложения и вычитания чисел в прямых, обратных и дополнительных кодах. Поставленная цель достигается тем, что параллельный накапливающий сумматор, содержащий одноразрядные сумматоры 1 1 - 1 N+2 и группу мультиплексоров 8, содержит группу элементов ИЛИ 9, группы элементов И 10, 11, элементы И 12 - 14, мультиплексоры 16, 17 и триггеры 18, 19 знака с соответствующими связями. 2 ил.

| Накапливающий сумматор | 1981 |

|

SU1013947A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1495782A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-08-23—Публикация

1987-12-29—Подача