Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств для моделирования сетевых задач опера:щонного управления.

Цель изобретения - расширение функциональных возможностей за счет нахождения максимального пути между начальным и конечным узлами сети, ранних сроков начала и окончания ветвей, ранних сроков свершения узлов и свободных резервов ветвей.

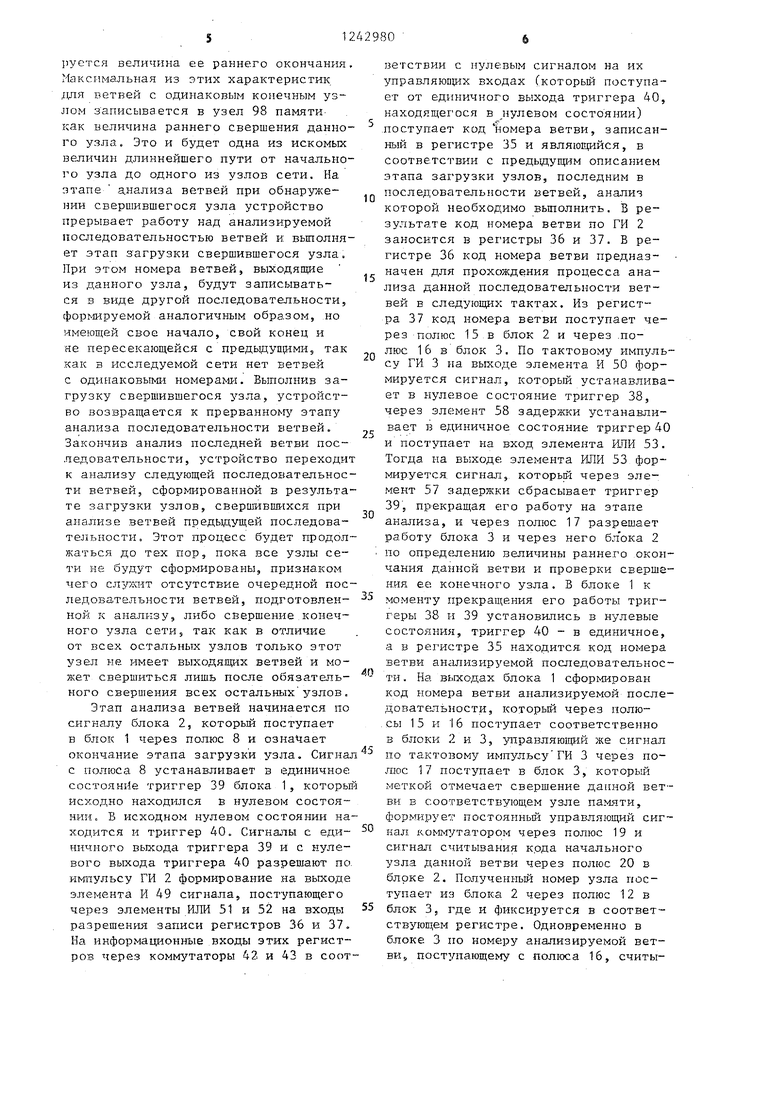

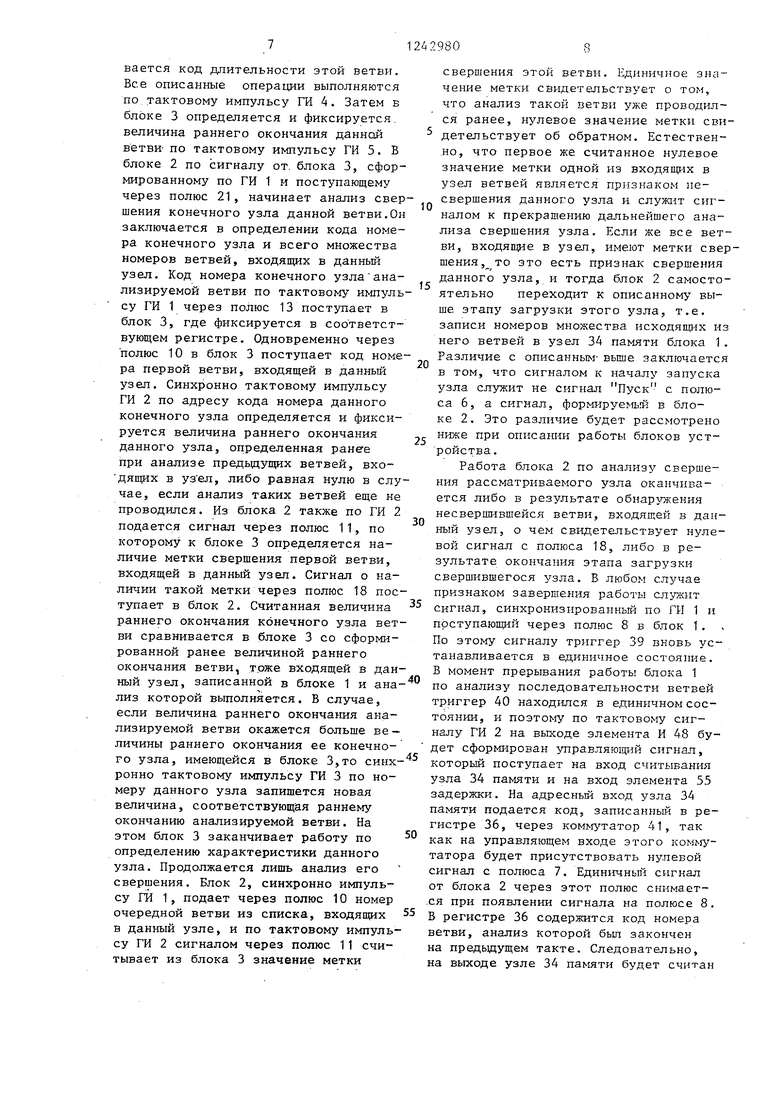

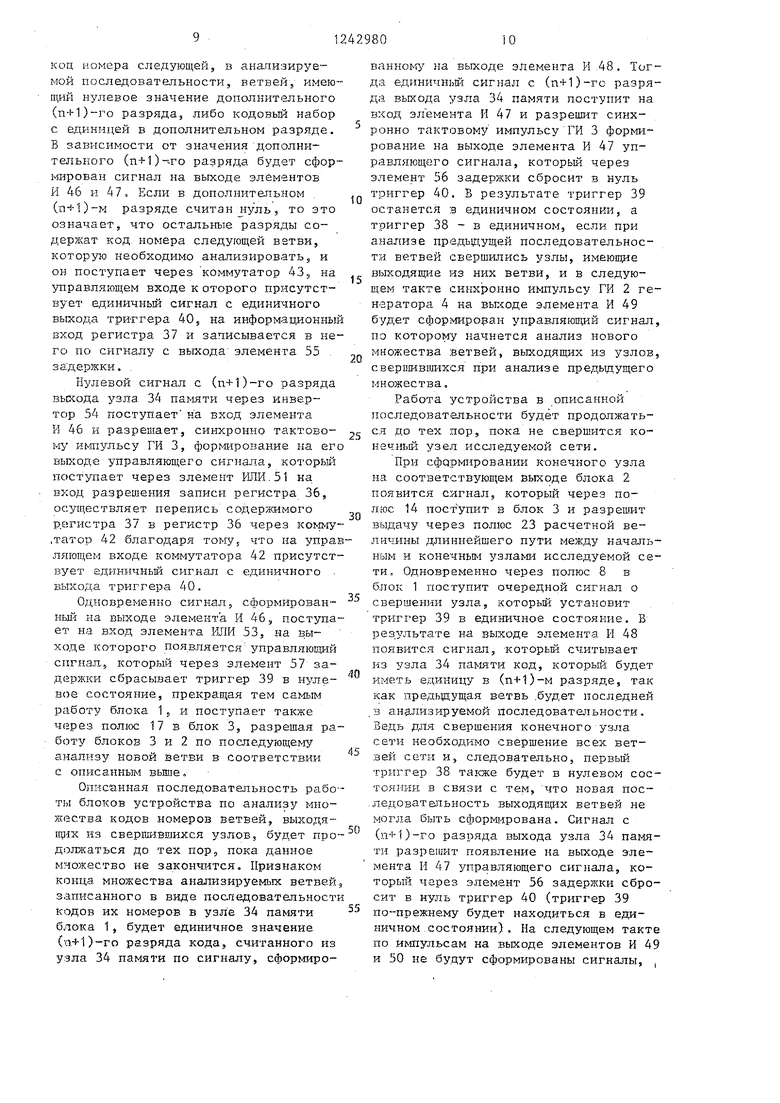

На фиг, 1 представлена блок-схема устройства и функциональная схема блока управления; на фиг-. 2 - функциональная схема блока моделирования топологии сети , на фиг. 3 - функциональная схема блока расчета характеристик сети.

Устройство содержит блок 1 управления, блок 2 моделирования топологии сети, блок 3 расчета характеристик сети, генератор 4 тактовых импульсов, полюса 5-33.

Блок 1 содержит узел 34 памяти номеров свершившихся ветвей, регистр 35 номера первой ветви, регистр 36 номера обрабатываемой ветви, регистр 37 номера анализируемой ветви, три триггера 38-40, три коммутатора 41- 43, семь элементов И 44-50, три элемента ИЛИ 51-53, элемент НЕ 54, четыре элемента 55-58 задержки.

Блок 2 содержит узел 59 памяти номеров начальных узлов ветвей сети, узел 60 памяти номеров конечных узлов ветвей сети, узел 61 памяти номеров выходящих из узлов ветвей,узел 62 памяти номеров входящих в узлы ветвей, узел 63 памяти номеров первых выходящих из узлов ветвей, узел 64 памяти номеров первых входящих в узлы ветвей, регистр 65 номера выходящей ветви, регистр 66 номера входящей ветви, регистр 67 номера конечного узла ветви, регистр 68 номера конечного узла сети, первый 69 и второй 70 триггеры управления, первый 7 второй 72 и третий 73 триггеры управления коммутаторами, четыре коммутатора 74-77, первый 78 и второй 79 дешифраторы, схему 80 сравнения, первый 81 и второй 82 элементы задержки, элемент ИЛИ 83, элемент И 84, элементы ИЛИ 85-89, эл ементы И 90-94 элемент НЕ 95.

Блок 3 содержит узел 96, памяти меток свершенияветвей,узел 97 памяти кодов длительностей ветвей, узел 9В

5

0

5

памяти характеристик узлов, регистр 99 длительности ветви, регистр 100 вспомогательный, регистр 101 характеристики узла, сумматор 102, регистр 103 суммы, схему 104 сравнения, три коммутатора 105-107, два триггера 108 и 109, шесть элементов И 110- 115, два элемента ИЛИ 116 и 117, седьмой элемент И 118, три элемента 119-121 задержки.

Для определения характеристик ветвей сети необходимо иметь множество величин ранних.окончаний всех узлов сети, т.е. множество величин длинней- UMX путей до каждого узла исследуемой сети, множество величин длительностей .всех ветвей сети и топологическую информацию о начальных и конечных узлах ветвей сети.,Последние две составляющие присутствуют в качестве исходных данных. Требуется определить первую составляющую - множество вел:ичин длиннейших путей от начального до каждого узла сети.

Устройство работает следуюш тм образом.

На входной полюс 5 подается код номера ветви, выходящей, из начального узла. По сигналу Пуск, поступа- ющему через входной полюс 6, начинает работу блок 2, который последова тельно определяет номера ветвей, выходящих из начального узла сети. Генератор 4 стробирует работу всех блоков устройства набором тактовых импульсов ГИ 1 - ГИ 5, сдвинутых относительно друг друга. Работа блока 2 осуществляется по импульсам ГИ 1 и ГИ 2. По импульсу ГИ 1 блок 2 определяет номер ветви, выходящей из начального узла, и подает код этого номера через .полюс 9 в блок 1. Через полюс 7 в блок 1 поступает сигнал, разрешающей работу блока по записи номеров ветвей, начальные узлы которых сверщкшись. Ветви необходимо записать в виде последовательности их номеров в узел 34 памяти с тем, чтобы в последующем можно было провести анализ свершения их конечных узлов. Код номера ветви через полюс 9 пос- .тупает на инфомационный вход регистра 35 и через коммутатор 41 (так как на.управляющий вход этого коммутатора подается с полюса 7 единичный 5 сигнал) на адресньй вход узла 34 па- ютти. Регистр 35 исходно бьш обнулен, также как и триггер 38. С выхода регистра 35 информация поступает на

5

0

5

0

3

информационный вход узла 34 памяти.

Дополнительный n+1-й разряд информационного входа узла 34 памяти соединен с инверсным выходом триггера 38 При записи номера первой ветви, выходящей из начального узла сети, на n+1-й разряд поступает единица, так как триггер 38 находится в нулевом состоянии. По тактовому импульсу ГИ в блоке 2 выполняется определение номера следующей ветви, выходящей из начального узла, но с выхода блока на полюс 9 по-прежнему поступает код номера первой ветви. По следующму сигналу ГИ 3 выполняется запись содержимого регистра 35 и сигнала с инверсного выхода триггера 38 в узел 34 памяти по адресу первой ветви. Сигнал записи формируется на вы ходе элемента И 44, на входы которого подается постоянный сигнал разрешения с полюса 7 и тактовый сигнал ГИ 3, и он поступает на вход разрешния записи узла 34 памяти. Затем по сигналу, сформированному на выходе элемента И 45 и поступающему на вход разрешения записи регистра 35 и единичный вход триггера 38, в регистр 35 записывается номер первой

ветви, и триггер 38 устанавливается в единичное состояние. На входы элемента И 45 подается сигнал разрешения с полюса 7 и тактовьй сигнал ГИ 4. По тактовому импульсу ГИ 5 на данном этапе вычислений никаких действий не выполняется. На следующем такте по импульсу ГИ 1 блок 2 вьща- ет код номера следующей ветви, выходящей из начального узла сети, который через полюс 9 поступает в блок 1. По импульсу ГИ 3 на выходе элемента И 44 формируется сигнал, который разрешает запись в узел 34 памяти содержимого регистра 35 и значения сигнала с инверсного выхода триггера 38 по адресу кода номера но вой ветви, выходящей из начального узла сети. В регистре 35 в данный момент времени содержится код номера первой ветви, выходящей из начального узла, а с инверсного выхода триггера 38 будет поступать нулевой сигнал, так как триггер 38 находится уже в нулевом состоянии. По сигналу ГИ 4 с генератора 4 на выходе эле

мента 45 формируется сигнал, по кото-55 данных ветвей. Узел считается сверрому в регистр 35 будет занесен код номера второй ветви, выходящей из начального узла. В результате второго

0

2980

4

паыят;

такта в узле 34 паыят; но адресу второй ветви, выходящей из начального узла, будет записан код первой ветви, по адресу которой на первом такте был записан нулевой код и метка в виде единицы в дополнительном п+1 разряде.

В регистре 35 будет записан код номера второй ветви, а триггер 38 останется в едиличном состоянии, так как сигнал с выхода элемента И 45 повторит его установку в единичное состояние. На третьем такте устройство выполнит те же действия, что и на втором такте. В результате в узле 34 памяти по адресу кода третьей ветви будет записан код второй ветви, по адресу кода второй ветви будет храниться код первой, а по адресу кода первой - метка в -дополнительном п+1 разряде слова. В регистре 35 будет записан код третьей ветви. Аналогичным образом запись в узел 34 памяти будет осуществляться и в последующих тактах, т.е. в узле 34 памяти по адресу кода последующей ветви будет храниться код предьщущей, по адресу первой - метка, а в регистре 35 - код последней ветви.

0

5

Когда все ветви, выходяпще из начального узла сети, будт записаны в узле 34 памяти блока 1, и блок 2 оп--, ределит, что список ветвей, выходящих из начального узла, закончен, то по очередному импульсу ГИ 1 блок 2 снимет постоянньй сигнал разрешения на полюсе 7 и сформирует импульсньм сигнал окончания списка выходящих из рассматриваемого узла ветвей, которьй через полюс 8 поступит в блок 1. Этим сигналом заканчивается первый этап работы устройства, призванньй обеспечить загрузку кодов номеров выходящих из начального узла сети ветвей в виде некоторой последовательности в узел 34 памяти блока 1. Этот этап загрузки узла будет неоднократно повторяться при последующем функцио- нирован1Ш.

Следующий этап заключается в анализе ветвей, номера которых записаны в виде последовательности в узле 34 памяти блока 1. Суть анализа состоит в оценке свершения конечных узлов

шившимся только в том случае, когда проанализированы все ветви, входящие в него. На этапе анализа ветви формируется величина ее раннего окончания. Максимальная из этих характеристик ;щя ветвей с одинаковым конечным узлом записывается в узел 98 памяти- как величина раннего свершения данного узла. Это и будет одна из искомых величин длиннейшего нути от начального узла до одного из узлов сети. На зтапе анализа ветвей при обнаружении свершившегося узла устройство прерывает работу над анализируемой последовательностью ветвей и выполняет этап з агрузки свершившегося узла. При этом номера ветвей, выходяш;ие из данного узла, будут записываться в виде другой последовательности, формируемой аналогичным образом, но имеющей свое начало, свой конец и не пересекающейся с предыдущими, так как в исследуемой сети нет ветве: с одинаковыми номерами. Выполнив загрузку свершившегося узла, устройство возвращается к прерванному этапу анализа последовательности ветвей. Закончив анализ последней ветви последовательности, устройство переходит к анализу следующей последовательности ветвей, сформированной в результате загрузки узлов, свершившихся при анализе ветвей предьщущей последовательности. Этот процесс будет продолжаться до тех пор, пока все узлы сети не будут сформированы, признаком чего слзокит отсутствие очередной последовательности ветвей, подготовленной к анализу, либо свершение конечного узла сети, так как в отличие от всех остальных узлов только этот узел не. имеет выходящих ветвей и может свершиться лишь после обязательного свершения всех остальных узлов. Этап анализа ветвей начинается по сигналу блока 2, которьй поступает в блок 1 через полюс 8 и окончание этапа загрузки узла. Сигнал с похпоса 8 устанавливает в единичное состояние триггер 39 блока 1, которьш исходно находился в нулевом состоянии. В исходном нулевом состоянии находится и триггер 40. Сигналы с единичного выхода триггера 39 и с нулевого выхода триггера 40 разрешают по. импульсу ГИ 2 формирование на выходе элемента И 49 сигнала, поступающего через элементы ШШ 51 и 52 на входы разрешения записи регистров 36 и 37. На информационные входы этих регистров через коммутаторы 42 и 43 в соот0

5

0

5

0

5

0

0

5

ветствии с нулевым сигналом на их управляюпщх входах (который поступает от единичного выхода триггера 40, находящегося в нулевом состоянии) .поступает код йомера ветви, записан- в регистре 35 и являющийся, в соответствии с предыдущим описанием этапа загрузки узлов, последним в последовательности ветвей, анализ которой необходимо выполнить. В результате код номера ветви по ГИ 2 заносится в регистры 36 и 37. В регистре 36 код номера ветви предназначен для прохожде.ния процесса анализа данной последовательности ветвей в следующих тактах. Из регистра 37 код номера ветви поступает через полюс 15 в блок 2 и через .полюс 16 в блок 3. По тактовому импульсу ГИ 3 на выходе элемента И 50 формируется сигнах, которьш устанавливает в нулевое состояние триггер 38, через элемент 58 задержки устанавливает в единичное состояние триггер 40 и поступает на вход элемента ИЛИ 53. Тогда на выходе элемента ИЛИ 53 фор- мир.уется. сигнал, которьй через элемент 57 задержки сбрасывает триггер 39, прекращая е;го работу на этапе анализа, и через полюс 17 разрешает работу блока 3 и через него бл ока 2 по опредЕшению величины раннего окончания данной ветви и проверки свершения ее. конечного узла. В блоке 1 к моменту прекращения его работы триггеры 38 и 39 установились в нулевые состояния, триггер 40 - в единичное, а в регистре 35 находится код номера ветви ансшизируемой последовательности. На вЕ.гходах блока 1 сформирован код номера ветви анализируемой после- довательзюсти, когорьй через полю- .сы 15 и 16 поступает соответственно в блоки 2 и 3, управляющий же сигнал по тактовому импульсу ГИ 3 через полюс 17 поступает в блок 3, который меткой отмечает свершение данной ветви в соответствующем узле памяти, формирует постоянньй управляющий сиг- кал коммутатором через полюс 19 и сигнал считывания кода начального узла данной ветви через полюс 20 в блоке 2. Получ ;нньй номер узла поступает из блока 2 через полюс 12 в блок 3, где и фиксируется в соответ- cтвyюи: eм регистре. Одновременно в блоке 3 по номеру анализируемой ветви,, поступающему с полюса 16, считывается код длительности этой ветви. Все описанные операции выполняются по тактовому импульсу ГИ 4. Затем в блоке 3 определяется и фиксируется, величина раннего окончания даннай ветви- по тактовому импульсу ГИ 5. В блоке 2 по сигналу от. блока 3, сформированному по ГИ 1 и поступающему через полюс 21, начинает анализ свер шения конечного узла данной ветви.Он заключается в определении кода номера конечного узла и всего множества номеров ветвей, входящих в данный узел. Код номера конечного узла анализируемой ветви по тактовому импуль су ГИ 1 через полюс 13 поступает в блок 3, где фиксируется в соответствующем регистре. Одновременно через полюс 10 в блок 3 поступает код номера первой ветви, входящей в данный узел. Синхронно тактовому импульсу ГИ 2 по адресу кода номера данного конечного узла определяется и фиксируется величина раннего окончания данного узла, определенная ранее при анализе предьщущих ветвей, вко- дящих в уз ел, либо равная нулю в случае, если анализ таких ветвей еще не проводился. Из блока 2 также по ГИ 2 подается сигнал через полюс 11, по которому к блоке 3 определяется наличие метки сверщения первой ветви, входящей в данный узел. Сигнал о на- лигчии такой метки через полюс 18 поступает в блок 2. Считанная величина раннего окончания конечного узла ветви сравнивается в блоке 3 со сформированной ранее величиной раннего окончания ветви, т.оже входящей в дан ный узел, записанной в блоке 1 и ана ЛИЗ которой выполняется. В случае, если величина раннего окончания анализируемой ветви окажется больше величины раннего окончания ее конечного узла, имеющейся в блоке 3,то синх ронно тактовому импульсу ГИ 3 по номеру данного узла запишется новая величина, соответствующая раннему окончанию анализируемой ветви. На этом блок 3 заканчивает работу по определению характеристики данного узла. Продолжается лишь анализ его свершения. Блок 2, синхронно импульсу ЛИ 1 , подает через полюс 10 номер очередной ветви из списка, входящих в данный узле, и по тактовому импульсу ГИ 2 сигналом через полюс 11 считывает из блока 3 значение метки

10

t5

20

свершения этой ветви. Единичное значение метки свидетельствует о том, что анализ такой ветви уже проводился ранее, нулевое значение метки сви- детельствует об обратном. Естественно, что первое же считанное нулевое значение метки одной из входящих в узел ветвей является признаком пе- свершения данного узла и служит сигналом к прекрашению дальнейшего анализа свершения узла. Если же все ветви, входяпще в узел, имеют метки свершения, то зто есть признак свершения данного узла, и тогда блок 2 самостоятельно переходит к описанному выше этапу загрузки этого узла, т.е. записи номеров множества исходящих из него ветвей в узел 34 памяти блока 1 . Различие с описанным- выше заключается в том, что сигналом к началу запуска узла служит не сигнал Пуск с полюса 6, а сигнал, формируемьй в блоке 2. Это различие будет рассмотрено ниже при описании работы блоков уст30

40

25

ройства.

Работа блока 2 по анализу свершения рассматриваемого узла оканчивается либо в результате обнаружения несвершившейся ветви, входящей в данный узел, о чем свидетельствует нулевой сигнал с полюса 18, либо в результате окончания этапа загрузки свершившегося узла. В любом случае признаком завершения работы служит

5 сигнал, синхронизированный по ГИ 1 и поступающий через полюс 8 в блок 1. По этому сигналу триггер 39 вновь устанавливается в единичное состояние. В момент прерывания работы блока 1 по анализу последовательности ветвей триггер 40 находипся в единичном состоянии, и поэтому по тактовому сигналу ГИ 2 на выходе элемента И 48 будет сформирован зт равляю ций сигнал, который поступает на вход считывания узла 34 памяти и на вход элемента 55 задержки. На адресный вход узла 34 памяти подается код, записанный в регистре 36, через комм татор 41, так как на управляющем входе этого KOMNry- татора будет присутствовать нулевой сигнал с полюса 7. Единичньш сигнал от блока 2 через этот полюс снимает- .ся при появлении сигнала на полюсе 8,

В регистре 36 содержится код номера ветви, анализ которой бьш закончен на предьщущем такте. Следовательно, на выходе узле 34 памяти будет считан

45

50

код номера следующей, в анапизируе- мой последовательности, ветвей, имеющий нулевое значение дополнительного (п+1)-го разряда, либо кодовьм набор с единицей в дополнительном разряде. Б зависимости от значения дополнительного (п+1)- Го разряда будет сформирован сигнал на выходе элементов И 46 и kl, Если в дополнительном (n-i-1)M разряде считан 1уль , то это означает, что остальные разряды содержат код номера следующей ветви, которую необходимо анализировать, и он поступает через коммутатор 43, на управляющем входе к оторого присутствует единичньй сигнал с единичного выхода триггера 40, на информационный вход регистра 37 и записывается в него по сигналу с выхода элемента 55 . за держки, .

Нулевой сигнал с (п+1)-го разряда вькода узла 34 памяти через инвертор 54 поступает на вход элемента И 46 и разреатает, синхронно тактовому иь-шульсу ГИ 3, фop иpoвaниe на ег выходе управляющего сигнахш., которьй поступает через элемент 1 ШИ.51 на вход разрешения записи регистра 36, осуществляет перепись содержимого р.егистра 37 в регистр 36 через ко№гу ,татор 42 благодаря тому; что на упраляющем входе коммутатора 42 присутствует единичньй сигнал с единичного . выхода триггера 40,

Одновременно сигнал, сформирован- ньш на выходе элемента И 46, поступает на вход элемента ИЛИ 53, на выходе которого появляется управляющий сигнал, который через элемент 57 задержки сбрасывает триггер 39 в нулевое состояние, прекращая тем самым работу блока 1 ., и постзшает также через полюс 17 в блок 3, разрешая работу блоков 3 и 2 по пocлeдyющe ry анализу новой ветви в соответствии с описанным вьт1в«

Описанная последовательность рабо ты блоков устройства по анализу множества кодов номеров ветвей, выходящих нз свершившихся узлов, будет продолжаться до тех пор, пока данное множество не закончится. Признаком конца множества анализируемых ветвей записанного в виде поспедовательност кодов их номеров в узле 34 памяти блока 1, будет единичное значение ()-го разряда кода, считанного из узла 34 памяти по сигналу, сформиро0

5

0

0

5

0

5

0

5

ванног-г;, на выходе элемента И.48. Тогда единичньй сигнал с (п+1)-го разряда вькода узла 34 памяти поступит на вход элемента И 47 и разрешит синхронно тактовому импульсу ГИ 3 формирование на выходе элемента И 47 управляющего сигнала, который через элемент 56 задержки сбросит в нуль триггер 40. В результате триггер 39 останется з единичном состоянии, а триггер 38 - в единичном, если при анализе предыдущей последовательности ветвей свершились узлы, имеющие выходящие из них ветви, и в следующем такте синхронно импульсу ГИ 2 генератора 4 на вькоде элемента И 49 будет сфор ушроран управляющий сигнал, по которому начнется анализ нового множества ветвей, выходящих из узлов, свершившихся при анализе предыдущего множества.

Работа устройства в описанной последовательности будет продолжаться до тех пор, пока не свершится конечный узел исследуемой сети.

При сформировании конечного узла на соответствующем выходе блока 2 появится сигнал, который через полюс 14 поступит в блок 3 и разрешит выдачу через полюс 23 расчетной величины длиннейшего пути между начальным и конечным узлами исследуемой сети. Одновременно через полюс 8 в блок 1 поступит очередной сигнал о свершении узла, который установит триггер 39 в еди:яичное состояние. В рез.ультате на выходе элемента И 48 появится сигнал, которьй считывает из узла 34 памяти код, которьй будет иметь единицу в (п+1)-м разряде, так как предьщущая ветвь .будет последней ,3 анд.лизируемой последовательности. Ведь для свершения конечного узла сети необходимо свершение всех ветвей сети и, следовательно, первый триггер 38 также будет в нулевом состоянии в связи с тем, что новая пос- ,ледовательность выходящих ветвей не могла быть сформ :-1рована. Сигнал с (n-i-l)-ro разряда выхода узла 34 памяти разрвш ит появление на выходе элемента И 47 управляющего сигнала, который через элемент 56 задержки сбросит в нуль триггер 40 (триггер 39 по-прежнему будет находиться в единичном .состоянии) . На следующем такте по импульсам на выходе элементов И 49 и 50 не будут сформированы сигналы.

так как нуль на единичном выходе триггера 38 запретит это. На этом закончится работа устройства. В блоке будут храниться требуемые характеристики узлов сети, составляющие совместно с величинами .длительностей ветвей функционально полный набор исходных данных, необходимых для получения характеритсик ветвей.

Теперь рассмотрим отдельно работу блоков 2 и 3.

Блок 2 предназначен для определения кодов номеров ветвей, выходящих из свершившегося узла, определения кодов номеров ветвей, входящих в узел, и оценки его свершения, а также для формирования сигнала о свершении конечного узла сети. Множества входящих (как.и выходящих) в узел ветвей записьшаются в виде последовательности, которая заключается в том что по номеру предыдущей ветви последовательности записан номер последующей, а по номерам последних ветвей - код X. Таким образом, в узлах 59-64 памяти хранится полная информация о топологии исследуемой сети. Регистры 65-67 предварительно обнуляются, а в регистр 68 заносится код номера конечного узла сети. Триггеры 69 и 70 находятся первоначально в нулевом состоянии. После начального установа на полюс 5 блока 2 подается код номера ветви, вьгходящей из начального узла. В некоторый момент времени сигнал Пуск, поступающий через полюс 6, проходит через элемент ИЛИ 89 и устанавливает в единичное состояние триггер 70. Единичное состояние триггера 70 разрешает прохождение импульсов ГИ 1 (полюс 24) и ГИ 2 (полюс 27) через элементы И .93 и 94. Кроме того, сигнал Пуск поступает на единичный вход триггера 71, на вход элемента 81 задержки, а также через элемент ИЛИ 85 на вход считывания узла 59 памяти. На адресный вход данного узла памяти через коммутатор 74 поступит с полюса 5 код номера ветви, выходящей из начального узла. Это будет возможно,так как в исходном состоянии с полюса 19 на управляющий вход коммутатора 74 поступает нулевой сигнал. По адресу номера ветви из узла 59 памяти считывается код нома начального узла сети, который поступает на вход коммутатора 75. Так как триггер 71, управ

10

ts

20

5

ляющий коммутатором 75, установлен пусковым сигналом в единичное состояние, то код номера начального узла поступит на адресный вход узла 63 памяти. На вход считывания узла 63 памяти с выхода элемента 81 задержки через элемент ИЛИ 83 поступит задержанный на время срабатывания узла 59 сигнал пуска, каторый выполнит считывание кода номера первой ветви, выходящей из начального узла сети.Этот же сигнал установит в единичное сос- тояние триггер 72, управляющий коммутатором 76, на вход которого поступит считанная из узла 63 памяти информация. Единичное состояние триггера 72 разрешит поступление кода номера первой выходящей из начального узла сети ветви на информационный вход регистра 65, куда и запишется по импульсу ГИ 1, поступившему с выхода элемента И 93 на управляющий вход регистра 65. С выхода регистра 65 через полюс 9 полученный код номера первой выходящей из начального узла ветви поступит в блок 1 для последуюг- ющей обработки. Туда же с единичного выхода триггера 70 через полюс 7 поступает управляющий сигнал. Одновременно код номера ветви с выхода регистра 65 поступает на адресный вход узла 61 памяти. По тактовому импульсу ГИ 2 -на выходе элемента И 94 будет сформирован управляющий сигнал, которьм сбросит в нуль триггер 72 и выполнит считывание из узла 61 памяти кода номера следующей из множества выходящих из начального узла ветви. Так как триггер 72 находится теперь в нулевом состоянии, то код номера следующей ветви через коммутатор 76 поступит на информационный вход регистра 65, но запищатся туда только по импульсу ГИ 1, приходящему с выхода элемента И 93. Таким образом, в течение всего такта на выходе регистра 65 код номера выходящей ветви изменяться не будет, так как изменение производится по тактовому импульсу ГИ 1. Одновременно содержимое регистра 65 поступает на вход дешифратора 78, где сравнивается с кодом состояния X. По адресу номера последней ветви, выходящей из начального узла, будет считан и записан в регистр 63 код X. Тогда на выходе дешифратора 78 будет сформирован сигнал, который поступит на нулевой

0

0

5

0

вход триггера 70, сбросит его в нуль и тем самым прекратит поступление через полюс 7 управляющего сигнала в блок 1. Одновременно сигнал с дешифратора 78 через элемент ИЛИ 87 и по- люс 8 поступит в блок 1, что будет свидетельствовать об окончании этапа запуска узла. На этапе анализа вет-- вей блок 2 выполняет операцию анализа свершения конечного узла ветви. Через полюс 15 с блока 1 поступает код номера анализируемой ветви. Чере коммутатор 74, на управляющем входе которого присутствует с полюса 19 единичный сигнал, код поступает на адресньй вход узла 59 памяти, из соответствующей ячейки которого по сигналу блока 3 через полюс 20 считывается код номера конечного узла данной ветви, который поступает через полюс,12 в блок 3. Одновременно код номера ветви поступает на адресный вход узла 60 памяти, из соответству

ющеи .ячейки которого по сигналу с по

люса 21 блока 3 считывается код номера конечного узла данной ветви,который через полюс 13 поступа.ет обратно в блок 3. Эти данные необходимы для работы блока 3, Анализ свершения т онечного узла данной ветви начинается по сигналу блока 3 через полюс 22, который, синхронно импульсу ГИ 3, устанавливает в единичные состояния триггеры 69 и 73, Единичное состояние триггера 69 разрешает формирование управляющих сигналов на выходе элементов И 91 и 92. Одновременно сигнал с полюса. 22 поступает на вход элемента 82 задержки и на вход считывания узла 60 памяти (через элемент ИЛИ 86), На выходе узла 60 памяти появляется считанньш код номера конечного узла данной ветви, который поступает на информационные входы регистра 67 и узла 64 памяти. Сигнал с выхода элемента 82 задержки поступает наг управляющие входы репшстра 67 и узла 64 памяти. В регистр 67 записывается код номера конечного узла

анализируемой ветви, а из узла 64 памяти по коду номера узла считывается код номера первой из множества входящих в данный узел ветвей. С выхода узла 64 памяти код номера первой входящей в узел ветви через коммута- тор 77 (так как триггер 73, управляющий коммутатором 77, находится в единичном состоянии) поступает на

0

5

0

5

0

f

5

информационный вход регистра 66. Далее по сигналу ГИ 1 с выхода элемента И 91 этот код записывается в регистр 66 и поступает через полюс 10 в блок 3 для считывания метки свершения ветви. Одновременно код ветви с выхода регистра 66 поступает на информавдонный вход узла 62 и на вход деашфратора 79. По тактовому импульсу ГИ 2 на выходе элемента И 92 фор- 1 шруется сигнал,, который поступает через полюс 11 в блок 3, где считывается значение метки сверщения ветви, код которой находится в регистре 66.

Если считанное значение метки равно единице, то единичный сигнал с полюса 18 поступает на вход элемента. И 84 и разрешает прохождение через него управляющего сигнала с элемента И 92. Сигнал с выхода элемента И 84 сбрасывает в нуль триггер 73 и считывает код номера следующей входящей в узел ветви из узла 62 памяти. Считанная информация через коммутатор 77 (так как управляющий им триггер 73 находится в нулевом состоянии) , поступает на информационный вход регистра 66, куда и записывается в следуюй ем такте по ,yльcy ГИ 1 с элемента И 91. Если же считанное значение метки свершения равно нулю, то нулевой сигнал с полюса 18 через элемент НЕ 95 и элемент ИЛИ 88 сбрасывает т.риггер 69 и поступает на вход элемента ИЛИ 87, на выходе которого формируется управляющий сигнал, который через полюс 8 поступает в блок 1. .

Если при анализе свершения ветвей, входящих в узел, нулевого сигнала о значении метки свершения не приходит, то по адресу последней считывается из узла 62 памяти ,код состояния X в, регистр 66, По коду дешифратор 79 вырабатьгоает сигнал, который сбрасьгоает в нуль триггер 69, устанавливает в единицу триггер 70 и .поступает на первый вход элемента И 90, на второй вход которого пос- . тулает сигнал с блока 80, который вырабатывает сигнал в случае совпадения кода свершенного узла, записанного в регистре 67, и кода конечного узла сети, записанного в регистре 68. С выхода элемента И 90 сигнал о свершении конечного узла сети поступает в блок 3, и устройство прекращает работу, как описывалось вьше. Если

же свершился не конечный узел, то сигнал с- выхода дешифратора 79 сбрасывает в нуль триггер 71, который разрешает поступление через коммутатор 75 кода Свершившегося узла, записанного в регистре 67, на адресный вход узла 63 памяти. Сигнал с выхода дешифратора 79 через элемент ИЛИ 83 поступает на вход считывания узла 63 памяти. Далее вновь выполняется, этап запуска узла.

Блок 3 в процессе функционирования устройства определяет величину раннего окончания анализируемой ветви, сравнивает ее с имеющейся величиной раннего окончания конечного узла этой ветви, полученной в результате предьщущих анализов входящих в этот узел ветвей, и если полученная характеристика ветви больше имеющейся характеристики ее конечного узла, то присваивает данному узлу величину полученной характеритиски, В результате в момент свершения данного узла 25 элемент 120 задержки поступает на

в блоке 3 по номеру узла будет записана величина раннего окончания входящей в него ветви, имеющей наибольшее значение, т.е. величина раннего свершения узла. Блок 3 работает следующим образом. Предварительно узеп 96 памяти меток свершения и узел 98 ранних окончаний узлов очищаются от всякой информации. Триггеры 108 и 109 находятся в нулевом состоянии.

В процессе анализа ветви блок 1 подает через полюс 16 иблок 3 код номера анализируемой ветви. Работа блока 3 начинается с момента получения от блока 1 сигнала запуска, синхронизированного по тактовому импульсу ГИ 3, через полюс 17. Сигнал с полюса 17 поступает на единичные входы первого и второго триггеров 108 и 109 и устанавливает их в единичные состояния. Единичный сигнал с выхода триггера 109 разрешает формирование на выходах элементов И 110-114 управляющих сигналов по соответствующим тактовым импульсам ГИ 4, ГИ 5, ГИ 1, ГИ 2 и ГИ .3. Одновременно единичный сигнал с выхода т оиггера 109 через полюс 19 поступает в блок 2 и на управляющий вход коммутатора 105, разрешая прохождение через него кода номера анализируемой ветви с полюса 16. Этот код с выхода коммутатора 105 поступает на адресный вход узла 96 памяти, на информационном входе кото30

35

40

45

50

55

вход разрешения записи регистра 10 куда заносргтся код номера начально узла анализируемой ветви. По такто му импульсу ГИ 5 сигнал с выхода э мента И 111 поступает на управляющ вход регистра 99, куда записываетс считанный ранее код длительности а лизируемой ветви. Одновременно сиг с выхода элемента И 111 через элемент ИЛИ 116 поступает на вход счи вания узла 98 памяти и на вход эле мента 119 задержки. По адресу номе ра начального узла, которьй поступ ет на адресный вход с выхода регис ра 100, из узла 98 памяти считывае ся величина раннего окончания этог узла, которая по сигналу с выхода элемента 119 задержки записывается в регистр 101 . Величргаа р,аннего ок чания начального узла анализируемой ветви поступает на вход комбинацион ного сумматора 102, на второй вход которого подается из регистра 99 ве личина длительности данной ветви, н выходе сумматора 102 будет получена величина раннего окончания данной ветви. Код величины раннего окончания ветви поступает на информационн вход регистра 103, куда и записыва- . ется по сигналу с выхода элемента И 112, синхронно тактовому и iпyльcy ГИ 1. Одновременно зтим же сигналом сбрасывается в нулевое состояние триггер 108, и через полюс 21 в бло

0

0

рого постоянно присутствует единич- . сигнал. По следующему тактовому импульсу ГИ 4 сигнал с выхода элемента И 110 поступает на вход записи узла 96 памяти и зайисывает по номеру анализируемой ветви единичное значение метки свершения. Этим же сигналом из узла 97 памяти кодов длительностей ветвей по адресу номера анализируемой ветви считывается код ее длительности, который поступает на информационный вход регистра 99. Одновременно сигнал с элемента И 110 через полюс 20 поступает в блок 2, где считывается код номера начального узла анализируемой ветви. Считанный код узла через полюс 12 поступает через коммутатор 106 (так как на его управляющем входе присутствует единичный сигнал с выхода триггера 108) на информационньй вход регистра 100. Одновременно сигнал с элемента И 110 через элемент ИЛИ 117 и

5

25 элемент 120 задержки поступает на

0

5

0

5

0

вход разрешения записи регистра 100, куда заносргтся код номера начального узла анализируемой ветви. По тактовому импульсу ГИ 5 сигнал с выхода элемента И 111 поступает на управляющий вход регистра 99, куда записывается считанный ранее код длительности анализируемой ветви. Одновременно сигнал с выхода элемента И 111 через элемент ИЛИ 116 поступает на вход считывания узла 98 памяти и на вход элемента 119 задержки. По адресу номера начального узла, которьй поступает на адресный вход с выхода регистра 100, из узла 98 памяти считывается величина раннего окончания этого узла, которая по сигналу с выхода элемента 119 задержки записывается в регистр 101 . Величргаа р,аннего окончания начального узла анализируемой ветви поступает на вход комбинационного сумматора 102, на второй вход которого подается из регистра 99 величина длительности данной ветви, на выходе сумматора 102 будет получена величина раннего окончания данной ветви. Код величины раннего окончания ветви поступает на информационный вход регистра 103, куда и записыва- . ется по сигналу с выхода элемента И 112, синхронно тактовому и iпyльcy ГИ 1. Одновременно зтим же сигналом сбрасывается в нулевое состояние триггер 108, и через полюс 21 в блоке 2 считьшается код номера конечного узла анализируемой ветви. Считан- тгй код узла из блока 2 через полюс 13 поступает на вход коммутатора 106 и (так как управляющий им триггер 108 находится в нулевом состоянии) с выхода коммутатора 106 код номера конечного узла поступит на информационный вход регистра 100, куда и будет записан по сигналу с выхода элемента 102 задержки, на вход которой через элемент ИЛИ 117 приходит сигнал с выхода элемента И 112. С выхода регистра 100 код номера конечного узла анализируемой ветви поступает на адресньш вход узла 98 памяти. По тактовому сигналу ГИ 2 на выходе элемента И 113 формируется сигнал, который через элемент ИЛИ 116 поступает на вход считывания узла 98 памяти и на вход элемента 119 задержки. По этому сигналу из узла 98 памяти считывается величина раннего окончания, соответствующая в данный момент конечному узлу анализируемой ветви, и по сигналу с выхода элемента 119 задержки записывается в регистр 101. Полученный код имеющейся величины раннего окончания конечного узла анализируемой ветви с выхода регистра 101 и код величины раннего окончания анапизируемой ветви с выхода регистра 103 поступают соответственно на первьш и второй входы блока 104, Единичный -сигнал на выходе блока 104 появится лишь в том случае, когда код на втором входе будет больше кода на первом входе, т.е. когда величина раннего окончания анализируемой ветви больше имеющейся к данному моменту величины раннего окончания конечного узла этой ветви. Такая ситуация означает , что величину раннего окончания конечного узла необходимо.привести в соответствие с величиной раннего окончания входящей в него ветви, т.е. записать в узел 98 памяти по имеющемуся в регистре 100 номеру конечного узла ветви код новой величины его раннего окончания, полученньш в регистре 103, выход которого соединяется в информационным входом узла 98 памяти. Сигнал разрешения записи поступает с выхода элемента И 115, на один вход которого приходит, единичны сигнал с выхода блока 104, а на второй - управляющий сигнал, синхронный тактовому импульсу ГИ 3, с выхода

элемента И 114;, больший код, .который на данный момент соответствует величине раннего окончания узла, поступит ни. вход элемента И 118. При свершении конечного узла сети сигнал от блока - 2 через полюс 14 разрешит поступление кода величины раннего окончания конечного узла через элемент И 118 на полюс 23 устройства. Величина раннего свершения конечного узла сети равна величине длиннейшего пути между ее начальным и конечным узлами.

15

Формула изо

р е т е н и я

0

5

0

0

5

0

5

Устройство для определения характеристик сетей., содержащее генератор тактовых импульсов и блок моделирования топологии сети, состоящий из узла памяти номеров начальных узлов ветвей сети, узла памяти номеров- конечных узлов ветвей сети, узла памяти номеров выходяшрх из узлов ветвей, узла памят-и номеров, входящих в узлы ветвей, узла памяти номероЪ первых выходящих, из узлов ветвей, узла памяти номеров первых входящих в узлы ветвей, регистра номера выходящей ветви, регистра номера входящей ветви, регистра номера конечного узла ветви, регистра номера конечного узла, сети, первого и второго триггеров управления, двух дешифраторов, схемы ср.авнения, двух элементов задержки, шести элементов ИЛИ, шести элементов И и элемента НЕ, причем в блоке моделирования топологии сети выход первого элемента задержки соединен с первым входом первого элемента ИЛИ, выход которого подключен к входу считывания узла памяти номеров первых выходящк/х из узлов ветвей, выход первого элемента И подключен к входу считывания узла памяти номеров входящих в узлы ветвей, выход регистра номера вькодящей ветви подключен к адресному входу узла памяти номеров выходящих из узлов ветвей и входу первого дешифратора, выходы регистров номера конечного узла ветви и номера конечного узла сети соединены-соответственно с первым и вторым входами схемы сравнения, выход которой подключен к первому входу второго элемента. Hj выход первого дешифратора соединен с первым входом второго элемента ИЛИ и с нулевьпч входом второго триггер 1 управления, выход элемента

НЕ подключен к второму входу второго элемента ИЛИ и первому входу третьего элемента ИЛИ, выход которого соединен с нулевым входом первого триггера управления, выход которого подключен к первым входам третьего и четвертого элементов И, выход второго дешифратора соединен с вторыми входами первого элемента ИЛИ, второго элемента И, третьего элемента ИЛИ и первым входом четвертого элемента ИЛИ, выход которого подключен к единичному входу второго триггера управления, выход которого соединен с первыми входами пятого и шестого элементов И, выходы которых подключены соответственно к входу разрешения записи регистра номера выходящей ветви и входу считывания узда памяти номеров выходящих из узлов ветвей, выход регистра номера входящей ветви соединен с входом второго дешифратора и адресным входом узла памяти номеров входящих в узлы ветвей, выход второго элемента задержки подключен к входу считывания узла,памяти номеров первых входящих в узлы ветвей и входу разрешешия записи регистра номера конечного узла ветви, выход узла памяти номеров конечных узлов ветвей сети соединен с адресным входом узла памяти номеров первых входящих в узлы ветвей и информационным входом регистра номера конечного узла ветви, выходы третьего и четвертого элементов И подключены соответственно к входу разрешения записи регистра номера входящей ветви и первому входу первого элемента И, пер- вьой выход генератора тактовых импульсов соединен с вторыми входами третьего и пятого элементов И, второй выход генератора тактовых импульсов подключен к вторым входам четвертого и шестого элементов И, а вход первого элемента задержки объединен с вторым входом четвертого элемента ИЛИ и является пусковым входом устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет нахождения максимального пути между начальным и конечным узлами сети, ранних сроков начала и окончания ветвей, ранних сроков свершения узлов и свободных резервов ветвей, в устройство введе ны блок управления, состоящий из узла памяти номеров свершившихся вет10

15

20

25

0

5

0

5

0

5

вей, регистра номера первой ветви, регистра.номера обрабатываемой ветви, регистра номера анализируемой ветви, первого, второго и третьего триггеров, первого, второго и третьего коммутаторов, семи элементов И, первого, второго и третьего элементов ИЛИ, элемента НЕ, первого, второго, третьего и четвертого элементов задержки, блок расчета характеристик сети,состоящий из узла памяти меток свершения ветвей, узла памяти кодов длительностей ветвей, узла памяти характеристик узлов, регистра длительности ветви, вспомогательного регистра, регистра характеристики узла, сумматора, регистра , схемы сравнения, первого, второго и третьего коммутаторов, первого и второго триггеров, семи элементов И, первого и второго элементов РШИ, первого, второго и третьего элементов задержки, в блок моделирования топологии сети введены первый, второй и третий триггеры управления коммутаторами, первый, второй, третий и четвертьй коммутаторы, причем в блоке управления выход первого элемента И соединен с входом записи узла памяти номеров свершившихся ветвей, выход второго элемента И подключен к единичному входу первого триггера и к входу разрешения, записи регистра номера первой ветви, единичньй выход второго триггера соединен с первыми входами третьего, четвертого, пятого, шестого и седьмого элементов И, единичный выход третьего триггера подключен к вторым входам третьего, четвертого и пятого элементов И и к управляющим входам второго и третьего коммутаторов, выход регистра номера первой ветви соединен с первыми информационными входами второго и третьего коммутаторов и первыми п разрядами (п - число ветвей сети) информационного входа узла памяти номеров свершившихся ветвей, (п+1)-й разряд информационного входа которого подключен к нулевому выходу первого триггера, а адресный вход - к выходу первого коммутатора, выход регистра номера обрабатываемой ветви соединен с .первым информационным входом первого коммутатора, выход третьего коммутатора подключен к информационному входу регистра номера анализируемой ветви, выход которого соединен с уп

равляюпщм входом STOpoi o коммутэ-тора выход которого подключен к информационному входу регистра номера обрабатываемой ветви, выход третьего элемента И соединен с первыми входами первого и третьего элементов ИЛИ, выход пятого элемента И подключен к входу первого элемента задержки и к входу считывания узла памяти номеров свершившихся ветвей, выход четвертого элемента И через второй элемент задержки подключен к нулевому входу третьего триггера, нулевой выход которого соединен с вторыми входам - njecToro элемента И и седьмого элемента И, выход которого подключен к нулевому входу первого триггера, второму входу третьего элемента ИЛИ и к входу четвертого элемента задержки, выход которого соединен с единичным входом третьего триггера, выход третьего элемента ИЛИ через третий элемент задерлски соединен с нулевым входом второго триггера, еди ничньш выход первого триггера подключен к третьим входам aiecToro и седьмого элементов И, выход шестого элемента И соединен с вторьм входом первого элемента ИЛИ ипервым входом второго элемента ИЛИ, выход которого подключен к входу разрешения записи регистра номера анализируемой ветви, выход первого элемента ИЛИ соединен с входом разрешения записи регистра номера, обрабатываемой ветви, выход первого элемента задержки подключен к второму входу второго ЭоТемента ИЛИ первые п разрядов выхода, узла памят номеров свершившихся ветвей соединены с вторым информационным входом третьего коммутатора, а (п+1)-й разряд выхода соединен с третьим входом четвертого элемента И и с входом элемента НЕ, выход которого подключе к третьему входу третьего элемента И в блоке расчета характеристик сети выход первого коммутатора соединен с адресным входом узла памяти меток свершения ветвей, выход первого триггера подключен к управляющему входу второго коммутатора, выход которого соединен с информационным входом вспомогательного регистра, выход которого подключен к адресному входу узла памяти характеристик узлов, вы ход которого соединен с информационным входом регистра характеристики узла, выход которого подключен к пер

.

15

20

, ,„ js, и н , 30

40

50

55

зым входам сумматора и схемы сравнения и первому информационног-iy входу третьего коммутатора, выход второго триггера соединен с первыми входами первого, второго, третьего, четвертого и пятого элементов И и управляющим входом первого коммутатора, выход второго элемента И подключен к первому входу первого элемента ИЛИ и входу разрешения записи регистра д.пительности ветви, выход третьего элемента И соединен с нулевым входом первого триггера, входом разрешения записи регистра суммы и первым входом второго элемента ИЛИ, вьпсод четвертого элемента И подключен к второму входу первого элемента ИЛИ., выход, которого соединен с входом разрешения записи узла памяти характеристик узлов и входом первого элемента задб;рж1си, выход которого подключен к входу разрешения записи регистра характеристики узла, выход первого элемента И соединен с входом записи узла памяти меток свершения ветвей, вторым входом второго элемента ИПИ и входом считывания узла памяти кодов длительностей ветвей, выход которого подключен к информационному входу регистра длительности ветви, выход которого соединен с вторым входом сумматора, выход которого подключен к информационному входу регистра сум- мы, выход которого соединен с информационным входом узла памяти характеристик узлов, вторым информаидон- ньм входом третьего коммутатора и вторым входом схемы сравнения, выход которой подключен к первому входу шестого элемента И и управляющему входу третьего коммутатора, выход которого соединен с- первым входом седьмого элемента И, выход второго элемента ИЛИ через второй элемент задержки подключен к входу разрешения записи вспомогательного регистра, выход пятого элемента И соединен с вторьм входом шестого элемента И и входом третьего элемента задержки, выход которого подключен к нулевоь у входу второго триггера, выход шестого элемента И подключен к входу записи узла памяти характеристик узлов, в блоке моделирования топологии сети выход первого коммутатора соединен с адресным входом узла памяти номеров начальных узлон ветвей сети,вход считывания и выход которого подключены соответственно к выходу пятого элемента ИЛИ и к первому информационому входу второго коммутатора, вых которого соединен с адресным входом узла памяти номеров первых выходящи из узлов ветвей, выход которого подключен к первому информационному вхду третьего коммутатора, выход которого соединен с информационным входом регистра номера выходящей ветви выход шестого элемента ИЛИ подключе к входу считывания узла памяти номеров конечных узлов ветвей сети, выход узла памяти номеров выходящих из узлов ветвей соединен с вторым информационным входом третьего коммтатора, выход второго дешифратора подключен к нулевому входу первого триггера управления коммутаторами, выход которого соединен с управляющим входом второго коммутатора,второй информационный вход которого подключен к выходу регистра номера конечного узла ветви, выход первого элемента ИЛИ соединен с единичным, а выход шестого элемента И - с нулевыми входаж второго триггера управления коммутаторами, выход которого подключен к управляющему входу третьего коммутатора, выход первого элемента И подключен к нулевому входу третьего триггера управления коммутаторами, выход которого соединен с управляющим входом четвертого коммутатора, первьй и второй информационные входы и выход которого подключены соответственно к выходу узла памяти номеров первых входяа их в узлы ветвей, выходу узла памяти номеров входящих в узлы ветвей и информационному входу регистра номера входящей ветви, первый вход пятого элемента ИЛИ и единичный вход первог триггера управления коммутаторами блока моделирования топологии сети объединены и являются пусковым входом устройства, информационный вход первого коммутатора является входом задания номера выходящей из начального узла ветви устройства, выход второго триггера управления блока моделирования топологии сети соеди- нен с первыми входами первого, второго элементов И и 5Т1равляющим входом первого коммутатора блока управления, выход второго элемента ИЛИ блока моделирования топологии сети подключен к единичному входу второго

10

15

20

25

30

5

0

5

0

5

триггера блока управления, выход регистра номера выходящей ветви блока моделирования топологии сети соединен с информационным входом регистра 1омера первой ветви и вторым информационным входом первого коммутатора блока управления, выход регистра номера входящей ветви блока моделирования топологии сети подключен к первому информационному входу первого коммутатора блока расчета характеристик сети, выход четвертого элемента И блока моделирования топологиии сети соединен с входом считывания узла памяти меток свершения ветвей блока расчета характеристик сети, выход уз ла памяти номеров начальных узлов ветвей сети блока моделирования топологии сети подключен к первому информационному входу второго коммутатора блока расчета характеристик сети,выход узла номеров конечньк уз-- лов ветвей сети блока моделирования топологии сети соединен с вторым информационным входом второго коммутатора блока расчета характеристик сети, выход второго элемента И блока моделирования топологии сети подключен к второму входу седьмого элемента И блока расчета х;арактеристик сети, выход регистра номера анализируемой ветви блока управления соединен с вторым информационным входом первого коммутатора и адресным входом узла памяти номеров конечных узлов ветвей сети блока моделирования топологии сети и вторым информационным входом первого коммутатора и адресным входом узла памяти кодов длительностей ветвей блока расчета характеристик сети, выход третьего элемента ИЛИ блока управления подключен к единичным входам первого и второго триггеров блока расчета характеристик сети, выход узла памяти меток свершения ветвей блока расчета характеристик сети соединен с входом элемента НЕ и вторым входом первого элемента И блока моделирования топологии сети, выход второго триггера блока расчета характеристик сети подключен к управляющему входу первого коммутатора блока моделирования топологии сети, выход первого элемента И блока расчета характеристик сети соединен с вторым входом пятого элемента И.ГП1 блока моделирования топологии сети, выход третьего элемента И блока расчета

характеристик сети подключен к первому входу шестого элемента ИЛИ блока моделирования топологии сети, выход пятого элемента И блока расчета характеристик сети соединен с вторым входом шестого элемента Ш1И, входом второго элемента задержки и единич- ньм входом третьего триггера управления коммутаторами блока моделирования топологии сети, первый выход генератора тактовых импульсов подключен к второму входу третьего элемента И блока расчета характеристик сети, второй выход генератора тактовых импульсов соединен с третьим входом пятого элемента И и четвертым входом шестого элемента И блока управления и вторым входом четвертого элемента И блока расчета характеристик се

д

ти, третий выход генератора тактовых импульсов подключен к второму входу nepBOi o элемента И, четвертым входам третьего,, четвертого и седьмого элементов И блока управления и к BTopoNry входу пятого элемента И блока расчета характеристик сети, четвертый выход генератора тактовых импульсов ) соединен с вторым входом второго элемента И блока управления и вторым входом первого элемента И блока расчета характеристик сети, пятый выход генератора тактовых импульсов подключен к второму входу второго элемента И блока расчета характеристик сети , выход седьмого элемента И блока расчета характеристик сети является выходом устройства.

0

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для решения сетевых задач | 1988 |

|

SU1564643A1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для решения задачи поиска длиннейшего пути | 1983 |

|

SU1206791A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

Изобретение относится к вычислительной технике и может быть использовано при построении вычислительных устройств для моделирования сетевых задач операционного управления. Цель изобретения состоит в расширении функциональных возможностей за счет нахождения максимального пути между начальным и конечньм узлами сети, ранних сроков начала и окончания ветвей, ранних сроков свершения узлов и свободных резервов ветвей. Устройство содержит блок управления, блок моделирования топологии сети, блок расчета характеристик сети, генератор импульсов. Блок управления содержит узел памяти номеров свершившихся ветвей, регистр номера первой ветви, регистр номера обрабатываемой ветви. регистр номера анализируемой ветви, триггеры, коммутаторы, элементы И, элементы ИЛИ, элемент НЕ, элементы задержки. Блок моделирования тополо- гии сети содержит узел памяти номеров начальных узлов ветвей сети, узел памяти номеров конечных узлов ветвей сети, узел номеров выходящих из узлов ветвей, узел памяти номеров, входящих в узлы ветвей, узел памяти номеров первьк выходящих из узлов ветвей, уз памяти номеров первых входящих в узлы ветвей, регистр номера выходящей ветви, регистр номера входящей ветви, регистр номера конечного узла ветви, регистр номера конечного узла сети, триггеры управления, триггеры управления коммутаторами, коммутаторы, дешифраторы, схему сравнения, элементы задержки, элементы ИЛИ, элементы И, элемент НЕ. Блок расчета характеристик сети содержит узел памяти меток свершения ветвей, узел памяти кодов длительностей вет- Beic, узел памяти характеристик узлов, регистр длительности ветви, регистры, сумматор, схему сравнения, коммутаторы, триггеры, элементы И, элементы ИЛИ, элементы задержки.Ма кси-- мальный путь между начальным и конечным узлами сети и другие ее характеристики определяются на основе поя- русного моделирования сети. 3 ил. и сл го 4 t со 00

фиг I

(pus.J ВНИИГШ Заказ 3707/49 Тираж 671Подписное

Произв.-полигр. пр-тие, г. Ужгород, ул. Проектная, 4

| ВСЕООЮЗНАЯ ПАТ?Г^О-ТСШ"КНАЯ'Б!'1БЛИОТ1'НА | 0 |

|

SU305484A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

Авторы

Даты

1986-07-07—Публикация

1984-09-22—Подача