Изобретение относится к вычислительной технике и может быть использовано в многопроцессорных ЭВМ для распределения задач между процессорами.

Цель изобретения - повьшзение быстродействия устройства при обслуживании срочных заявок.

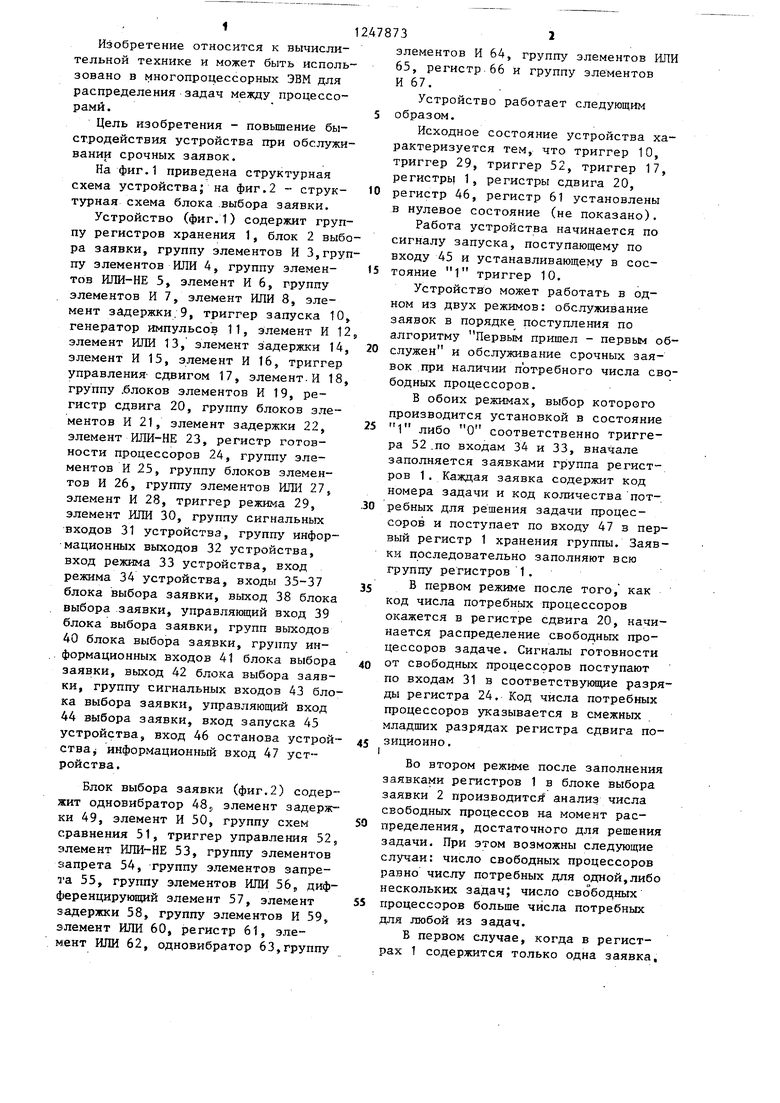

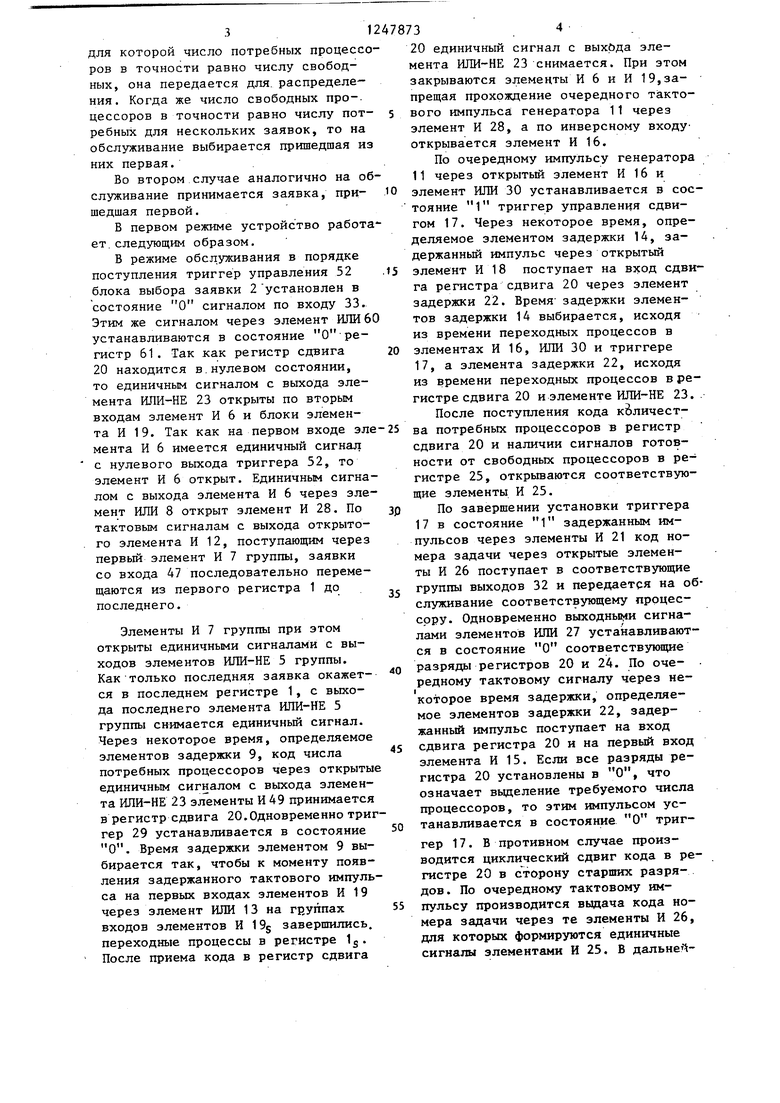

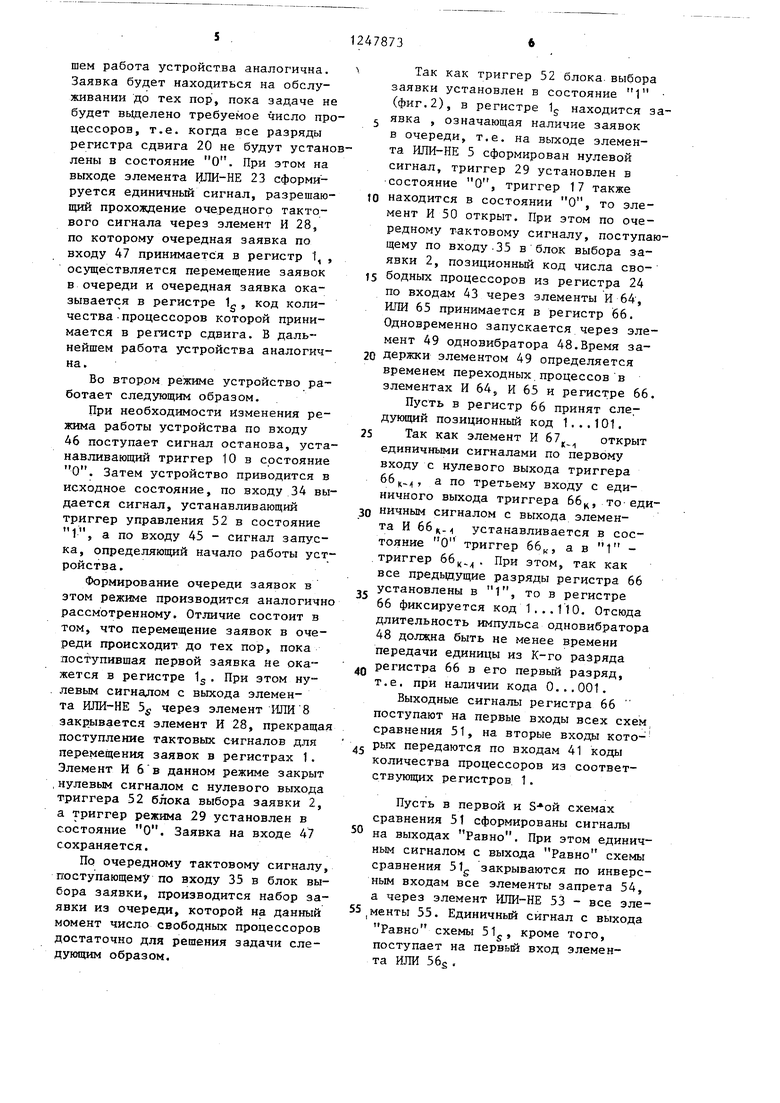

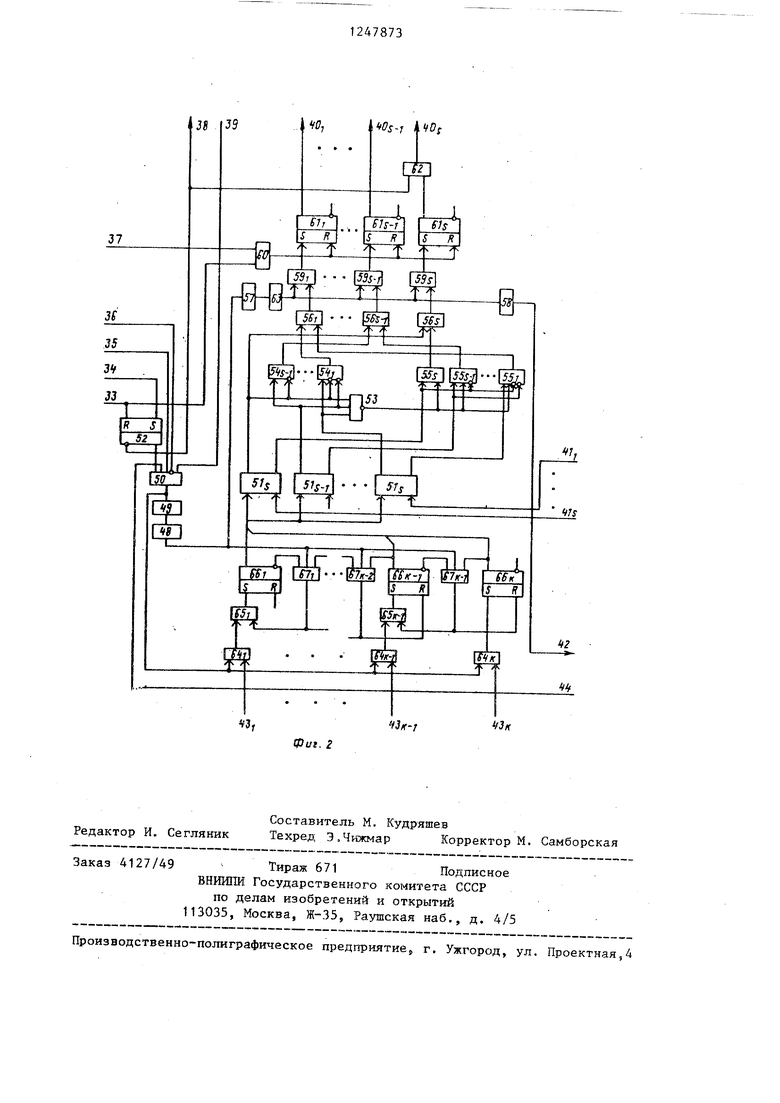

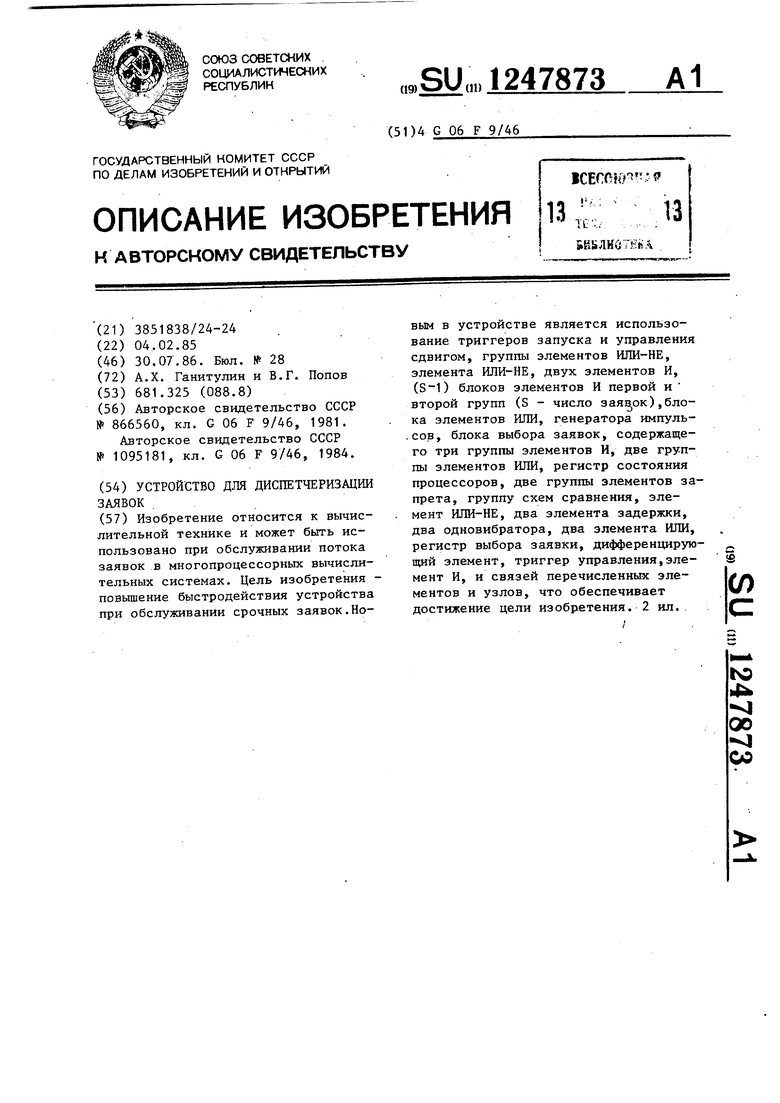

На фиг.1 приведена структурная схема устройства; на фиг.2 - структурная схема блока .выбора заявки.

Устройство (фиг.1) содержит группу регистров хранения 1, блок 2 выбора заявки, группу элементов И 3,группу элементов ИЛИ 4, группу элементов ИЛИ-НЕ 5, элемент И 6, группу элементов И 7, элемент ИЛИ 8, элемент задержки.9, триггер запуска 10 генератор импульсов 11, элемент И 12 элемент ИЛИ 13, элемент задержки 14, элемент И 15, элемент И 16, триггер управления- сдвигом 17, элемент. И 18, группу .блоков элементов И 19, регистр сдвига 20, группу блоков элементов И 21, элемент задержки 22, элемент ИЛИ-НЕ 23, регистр готовности процессоров 24, группу элементов И 25, группу блоков элементов И 26, группу элементов ИЛИ 27, элемент И 28, триггер режима 29, элемент ИЛИ 30, группу сигнальных входов 31 устройства, групщ информационных выходов 32 устройства, вход режима 33 устройства, вход режима 34 устройства, входы 35-37 блока выбора заявки, выход 38 блока выбора заявки, управляющий вход 39 блока выбора заявки, групп выходов 40 блока выбора заявки, группу информационных входов 41 блока выбора заявки, выход 42 блока выбора заявки, группу сигнальных входов 43 блока выбора заявки, управляющий вход 44 выбора заявки, вход запуска 45 устройства, вход 46 останова устройства информационный вход 47 устройства.

Блок выбора заявки (фиг.2) содержит одновибратор 48., элемент задержки 49, элемент И 50, группу схем сравнения 51, триггер управления 52, элемент 53, группу элементов запрета 54, группу элементов запрета 55, группу элементов ИЛИ 56, дифференцирующий элемент 57, элемент задержки 58, группу элементов И 59, элемент ИЛИ 60, регистр 61, элемент ИЛИ 62, одновибратор 63,группу

элементов И 64, группу элементов ИЛИ 65, регистр 66 и группу элементов И 67.

Устройство работает следующим

образом.

Исходное состояние устройства характеризуется тем, что триггер 10, триггер 29, триггер 52, триггер 17, регистры 1, регистры сдвига 20,

регистр 46, регистр 61 установлены

в нулевое состояние (не показано).

Работа устройства начинается по

сигналу запуска, поступающему по

входу 45 и устанавливающему в состояние 1 триггер 10.

Устройство может работать в одном из двух режимов: обслуживание заявок в порядке поступления по алгоритму Первым пришел - первым обслужен и обслуживание срочных заявок при наличии потребного числа свободных процессоров.

В обоих режимах, выбор которого производится установкой в состояние

1 либо О соответственно триггера 52 .по входам 34 и 33, вначале заполняется заявками rpiynna регистров 1. Каждая заявка содержит код номера задачи и код количества потребных для решения задачи процессоров и поступает по входу 47 в первый регистр 1 хранения группы. Заявки последовательно заполняют всю группу регистров 1.

В первом режиме после того, как код числа потребных процессоров окажется в регистре сдвига 20, начинается распределение свободных процессоров задаче. Сигналы готовности

от свободных процессоров поступают по входам 31 в соответствующие разряды регистра 24. Код числа потребных процессоров указывается в смежных младших разрядах регистра сдвига позиционно.

Во втором режиме после заполнения заявками регистров 1 в блоке выбора заявки 2 производите. анализ числа свободных процессов на момент распределения, достаточного для решения задачи. При этом возможны следующие случаи: число свободных процессоров равно числу потребных для одной,либо нескольких задач; число свободных

процессоров больше числа потребных для любой из задач.

В первом случае, когда в регистрах 1 содержится только одна заявка.

для которой число потребных процессоров в точности равно числу свободных, она передается для. распределения. Когда же число свободных про-, цессоров в точности равно числу пот- ребных для нескольких заявок, то на обслуживание выбирается пришедшая из них первая.

Во втором случае аналогично на обслуживание принимается заявка, при- шедшая первой.

В первом режиме устройство работает, следующим образом.

В режиме обслуживания в порядке поступления триггер управления 52 блока выбора заявки 2 установлен в состояние О сигналом по входу 33. Этим же сигналом через элемент ШШ 60 устанавливаются в состояние О регистр 61. Так как регистр сдвига 20 находится в.нулевом состоянии, то единичным сигналом с выхода элемента ИЛИ-НЕ 23 открыты по вторым входам элемент И 6 и блоки элемента И 19. Так как на первом входе эле мента И 6 имеется единичный сигнал с нулевого выхода триггера 52, то элемент И 6 открыт. Единичным сигналом с выхода элемента И 6 через элемент ИЛИ 8 открыт элемент И 28. По тактовым сигналам с выхЬда открытого элемента И 12, поступающим через первый элемент И 7 группы, заявки со входа 47 последовательно перемещаются из первого регистра 1 до последнего.

Элементы И 7 группы при этом открыты единичными сигналами с выходов элементов ИЛИ-НЕ 5 группы. Как только последняя заявка окажет- ся в последнем регистре 1, с выхода последнего элемента ИЛИ-НЕ 5 группы снимается единичный сигнал. Через некоторое время, определяемое элементов задержки 9, код числа потребных процессоров через открыты единичным сигналом с выхода элемента ИЛИ-НЕ 23 элементы И 49 принимается в регистр сдвига 20.Одновременно триггер 29 устанавливается в состояние О. Время задержки элементом 9 выбирается так, чтобы к моменту появления задержанного тактового импульса на первых входах элементов И 19 через элемент ИЛИ 13 на группах входов элементов И 195 завершились, переходные процессы в регистре 1. После приема кода в регистр сдвига

s

О

5 0 5 р

5

5 0 5

20 единичный сигнал с выхйда элемента ИЛИ-НЕ 23 снимается. При этом закрываются элементы И 6 и И 19,запрещая прохождение очередного тактового импульса генератора 11 через элемент И 28, а по инверсному входу- открывается элемент И 16.

По очередному импульсу генератора 11 через открытый элемент И 16 и элемент ШШ 30 устанавливается в состояние 1 триггер управления сдвигом 17. Через некоторое время, определяемое элементом задержки 14, задержанный импульс через открытый элемент И 18 поступает на вход сдвига регистра сдвига 20 через элемент задержки 22. Время задержки элементов задержки 14 выбирается, исходя из времени переходных процессов в элементах И 16, ИЛИ 30 и триггере 17, а элемента задержки 22, исходя из времени переходных процессов в регистре сдвига 20 и элементе ИЛИ-НЕ 23. .

После поступления кода кбличест- ва потребных процессоров в регистр сдвига 20 и наличии сигналов готовности от свободных процессоров в регистре 25, открываются соответствующие элементы И 25.

По завершении установки триггера 17 в состояние 1 задержанным импульсов через элементы И 21 код номера задачи через открытые элементы И 26 поступает в соответствующие группы выходов 32 и передается на обслуживание соответствующему процессору. Одновременно выходны1 «и сигналами элементов ШШ 27 устанавливаются в состояние О соответствующие разряды регистров 20 и 24. По оче- . редному тактовому сигналу через некоторое время задержки, определяемое элементов задержки 22, задержанный импульс поступает на вход сдвига регистра 20 и на первый вход элемента И 15. Если все разряды регистра 20 установлены в О, что означает выделение требуемого числа процессоров, то этим импульсом устанавливается в состояние О триггер 17. В противном случае производится циклический сдвиг кода в регистре 20 в сторону старших разрядов . По очередному тактовому импульсу производится выдача кода номера задачи через те элементы И 26, для которых формируются единичные сигналы элементами И 25. В дальнегошем работа устройства аналогична. Заявка будет находиться на обслуживании до тех пор, пока задаче не будет вцделено требуемое число процессоров, т.е. когда все разряды регистра сдвига 20 не будут устанолены в состояние О. При этом на выходе элемента ИЛИ-НЕ 23 сформируется единичный сигнал, разрешающий прохождение очередного тактового сигнала через элемент И 28,, по которому очередная заявка по входу 47 принимается в регистр I, , осуществляется перемещение заявок в очереди и очередная заявка оказывается в регистре 1g , код количества-процессоров которой принимается в регистр сдвига. В дальнейшем работа устройства аналогична.

Во втор.ом режиме устройство работает следующим образом.

Цри необходимости изменения режима работы устройства по входу 46 поступает сигнал останова, устанавливающий триггер 10 в состояние О. Затем устройство приводится в исходное состояние, по входу 34 выдается сигнал, устанавливающий триггер управления 52 в состояние 1, а по входу 45 - сигнал запуска, определяющий начало работы устройства.

Формирование очереди заявок в этом режиме производится аналогичн рассмотренному. Отличие состоит в том, что перемещение заявок в очереди происходит до тех пор, пока поступившая первой заявка не окажется в регистре Ig. При этом ну левым сигналом с выхода элемента ИЛИ-НЕ 5 через элемент 1ШИ 8 закрывается элемент И 28, прекраща поступление тактовых сигналов для перемещения заявок в регистрах 1. Элемент И 6 в данном режиме закрыт ,нулевым сигналом с нулевого выхода триггера 52 блока выбора заявки 2, а триггер режима 29 установлен в состояние О. Заявка на входе 47 сохраняется.

По очередному тактовому сигналу поступающему по входу 35 в блок выбора заявки, производится набор заявки из очереди, которой на данный момент число свободных процессоров достаточно для решения задачи следующим образом.

Так как триггер 52 блока, выбора заявки установлен в состояние 1 (фиг. 2), в регистре Ig. находится за- 5 явка , означающая наличие заявок в очереди, т.е. на выходе элемента ИЛИ-НЕ 5 сформирован нулевой сигнал, триггер 29 установлен в состояние О, триггер 17 также

JO находится в состоянии О, то элемент И 50 открыт. При этом по очередному т-актовому сигналу, поступающему по входу.35 в блок выбора заявки 2, позиционный код числа сво15 бодных процессоров из регистра 24 по входам 43 через элементы И 64, ИЛИ 65 принимается в регистр 66. Одновременно запускается через элемент 49 одновибратора 48.Время за20 держки элементом 49 определяется временем переходных процессов в элементах И 64, И 65 и регистре 66.

Пусть в регистр 66 принят следующий позиционный код 1...101.

25 Так как элемент И 67, открыт единичными сигналами по первому входу с нулевого выхода триггера 66, а по третьему входу с единичного выхода триггера 66, то еди30 ничным сигналом с выхода элемента И 66 ,4. устанавливается в состояние О триггер 66, а в 1 - триггер 66|( . При этом, так как все предьщущие разряды регистра 66 установлены в 1, то в регистре 66 фиксируется код 1...110. Отсюда длительность импульса одновибратора 48 должна быть не менее времени передачи единицы из К-го разряда

Q регистра 66 в его первый разряд, т.е. при наличии кода 0...001.

Выходные сигналы регистра 66 поступают на первые входы всех схем сравнения 51, на вторые входы кото рых передаются по входам 41 коды количества процессоров из соответствующих регистров 1.

Пусть в первой и схемах сравнения 51 сформированы сигналы

50 на выходах Равно. При этом единичным сигналом с выхода Равно схемы сравнения 51 закрываются по инверсным входам все элементы запрета 54, а через элемент ИЛИ-НЕ 53 - все эле55 менты 55. Единичный сигнал с выхода Равно схемы 51, кроме того, поступает на первьй вход элемента ИЛИ 56s

35

По заднему фронту импульса од- новибратора 48 дифференцирующий элемент 57 формирует сигнал, запускающий одновибратор 63, длительност выходного сигнала которого устанавливается в пределах надежного срабатывания триггера регистра 61,

По импульсу одновибратрра 63 триггер 61g устанавливается в сос- 1 через открытый элемент И 59g. Единичным сигналом чере элемент ГШИ 62 по выходу AOg открываются элементы И 19g, И 21g, а по первому входу - элемент И 3.

Через некоторое время, определяемое элементом задержки 58 и устанавливаемому по времени переходных процессов в элементах И 59, регистре 61, элементе ИЛИ 62, код количества процессоров из регистра 1g через элементы И 19 передается в регистр сдвига 20. Одновременно сигналом с выхода элемента задержки 58 через элемент ИЛИ 30 устанавливается в состояние 1 триггер 17, тем самым блокируется воздействие очередного тактового импульса по входу 35 блока выбора заявки 2.

По очередному тактовому сигналу через элемент И 18 производится передача кода номера задачи из регистра Ig через открытые элементы И 21 и сосэтветствующие элементы И 26 на выходы 32. Одновре- .менно производится установка.в состояние О одноименных возбужденных разрядов регистра 20 и 24.

Так как после сброса разрядов регистра сдвига для рассматриваемого примера К-ый разряд регистра сдвига 20 остается в состоянии 1, то триггер 17 остается в состоянии 1, а в регистре 20 производится циклический сдвиг кода в строку старших разрядов. При этом после сдвига происходит совпадение единичных значений на элементе И 25 разрешающее передачу кода номера задачи на выходы 32 и устанавливающее в состояние О К-ые разряды регистров 20 и 24.

По очередному тактовому сигналу устанавливается в О триггер 17 через элемент И 15. При этом одновременно с установкой в О триг- гера 17 устанавливается в состояние

О регистр 1s а триггер 29 - в состояние 1.

Таким образом, из двух заявок, 5 для которых требуемое число процессоров оказалось равным, на обслу- ,живание выбирается заявка, поступившая первой из них.

Если выходные сигналы с выходов 0 Равно всех схем сравнения 51 равны нулю, то разрешается выбор заявки, для которой число процессоров меньше числа свободных на момент распределения. При этом выбор заявки 5 обеспечивается аналогично, но элементами запрета 55 так, что на обслуживание выбирается заявка, поступившая первой.

После завершения распределения 0 процессоров по очередному тактовому импульсу производится перемещение заявки в очереди включительно до того регистра, состояние которого после распределения оказалась ну- 5 левым.

Пусть после обслуживания очеред- ной заявки регистр Ig. установлен в состояние О.

Так как по окончании распределе- 0 ния процессоров триггер 29 установлен в состояние 1 сигналом с выхода элемента И 15, то сигналом с единичного его выхода через элемент ИЛИ 8 открывается элемент И 28, - а сигналом с нулевого выхода блокируется работа блока выбора з аяв- ки 2 по входу 39. Одновременно устанавливается в О регист р IjПо очередному тактовому сигналу 0 происходит перемещение заявок до регистр 1g, включительно, а в регистре 1g сохраняется его прежнее значение, так как элемент И 7g закрыт нулевыми сигналами с выходов г элемента ШШ-НЕ 5g и элемента И 6. ,

Так как через элемент задержки 9 триггер 29 устанавливается в О, то по очередному тактовому сигналу запускается блок выбора заявки и Q работа устройства в дальнейшем аналогична рассмотренной.

Формула изобретения

Устройство для диспетчеризации заявок, содержащее группу регистров хранения, три группы элементов И, регистр сдвига, триггер режима, четыре элемента И, группу элементов ИЛИ три элемента задержки, первую группу блоков элементов И, вторую групп блоков элементов И, три элемента ИЛИ и регистр готовности процессоров, группа информационных входов которого соединена с группой входов готовности устройства, тактовый вход каждого регистра хранения группы, кроме последнего, соединен с вы ходом одноименного элемента И первой группы, первая и вторая группы информационных выходов каждого регистра хранения группы, кроме последнего, соединены с первой и второй группами информационных входов последующего регистра хранения группы, первый вход каждого элемента И первой группы, кроме первого и последнего,соединен с выходом последующего элемента И этой группы,выходы блоков элементов И первой группы соединены с группой информационных выходов устройства, каждый выход регистра сдвига соединен с первым входом одноименного элемента И второй группы, выход первого элемента И.ПИ соединен с первыми входами блоков элементов И второй группы, первая группа выходов последнего регистра хранения группы соединена, с группой входов первого блока элементов И третьей группы, вторая группа выходов последнего регистра хранения группы соединена с группой входов первого блока элементов И второй группы, единичный выход триггера режима подключен к первому входу второго элемента ИЛИ, первый вход первого элемента И соединен с инверсным входом второго элемента И, выход которого подключен к первому входу третьего элемента ИЛИ, отличающееся тем, что, с целью повышения быстродействия при обслуживании срочных заявок, в него введены триггер запуска, группа элементов ИЛИ-НЕ, третья группа блоков элементов И, триггер управления сдвигом,, элемент ИЛИ-НЕ, вторая группа элементов ИЛИ, блок выбора заявки, пятый и шестой элементы И, генератор импульсов, выход которого подключен к первому входу третьего элемента И второй вход которого соедииек с единичным выходом триггера запускаj,

5

единичный и.нулевые входы которого являются соответственно входом запуска и останова устройства, выход третьего элемента И соединен с первым входом четвертого элемента И, с прямым входом второго элемента И, через второй элемент задержки с первым входом пятого элемента И и не0 посредственно с первым входом разрешения приема информации блока выбора заявки, группа выходов кода количества процессоров 1-го регистра хранения группы, где i 1,2,

5 ,. ..,S (где S - количество регистров хранения группы) подключена к входам i-ro элемента ИЛИ-НЕ группы, j- й вход j-ro элемента ИЛИ перв ой группы, где j 1,2,,.,,S-1, j

0 S - j + 1,...25l, подключен к выходу j-го элемента ИЛИ-НЕ группы, выход S-ro элемента ИЛИ-НЕ группы соединен с входом запрета приема информации блока выбора заявки, с первым входом S-ro элемента ИЛИ первой группы и с вторым входом второго элемента ИЛИ, третий вход которого соединен с вторым входом S-ro элемента ИЛИ первой группы и

0 с выходом шестого элемента И, выход второго элемента ИЛИ соединен с вторым входом четвертого элемента И, вьпгод которого подключен через второй элемент задержки к нуле5 вому входу триггера режима и первому входу первого элемента ИЛИ и непосредственно к первому входу первого элемента И первой грудпы и к первому входу последнего элемен0 та И первой группы, выход которого соединен с тактовым входом последнего регистра хранения группы, выход i-ro элемента ИЛИ-НЕ группы подключен к второму входу i-ro

5 элемента И второй группы,, вторая группа выходов j-ro регистра хранения группы подключена к группе входов t-Po блока элементов И второй группы, где t S - j + 1, первая

0 группа, выходов j-ro регистра хранения группы подключена к группе входов t-ro блока элементов И третьей группы, выходы блоков элементов И третьей группы объединены и подклю5 чены к группам входов- блоков элементов И первой группы, выходы элементов И первой группы соединены с вторьми входами соответствующих злементов И первой группы, выходы блб- ков элементов И второй группы объе- динены и подключены к информационным входам регистра сдвига, выходы которого соединены с входами элемента ИЛИ-НЕ, выход которого подключен к инверсному входу второго элемента И, к первому входу шестого элемента И, к вторым управляющим входам блоков элементов И второй группы, вход регистра сдвига соединен с выходом третьего элемента задержки и с вторым входом первого элемента И, выход которого подклю- чен к единичному входу триггера ре- жима, к первым и вторым входам элементов И третьей группы, к входу сброса выходной информации блока выбора заявки и к нулевому входу.триг гера управления сдвигом, единичный вход которого соединен с выходсм третьего элемента ИЖ, единичный вход которого соединен с выходом третьего элемента ИЛИ, единичный выход триггера управления сдвигом соединен с вторым входом пятого элемента И, выход которого подключен к первым управляющим входам элементов И всех блоков третьей группы и к входу третьего элемента задержки, нулевой выход триггера режима подключен к второму входу разрешения приема информации блока выбора заявки, нулевой выход тригге ра управления сдвигом соединен с вторым входом разрешения приема информации блока выбора заявки, выход 1-го блока элементов И первой группы, где 1 1,2,...,К (к - количест во процессоров), подключены к входам 1-го элемента ИЛИ второй группы выходы которых соединены с входами

установки в О 1-х разрядов регистра сдвига и регистра готовности процессоров, выход 1-го разряда регистра готовности процессоров соединен с вторым входом 1-го элемента И второй группы и с 1-м входом группы кодовых входов блока выбор- ки заявки, второй вход первого элемента ИЛИ подключен ко второму вход третьего элемента ИЛИ и к первому выходу блока выбора заявки,второй выход которого подключен ко второму входу шестого элемента И, L-Й выход группы выходов блока выбора заявки соединен с третьими управляющими входами (S-i+1)-го блока второй группы с вторыми управляющими входами (S-i+1)-го блока третьей группы и со вторым входом i-ro элемента И третьей группы, выход которого подключен к входу установки в О i-ro регистра хранения группы, первая группа выходов i-ro регистра хранения группы соединена с i-ой группой информационных входов блока выбора заявки, группы информационных входов первого регистра хранения группы подключены к информационному входу устройства, входы запуска и останова блока выбора заявки являются первым и вторым входами режима устройства соответственно, выход каждого элемента И второй группы содинен с управляющим входом одноименного блока элементов И первой группы, причем блок выбора заявки содержит три группы элементов И, две группы элементов ИЛИ, первый регистр, группу схем сравнения, элемент ИЛИ-НЕ, две группы элементов запрета, два элемента задержки,два одновибратора, два элемента ИЛИ, второй регистр, дифференцирующий элемент, триггер управления и элемент И, первый прямой вход которого подключен к единичному вь1ходу триггера управления, единичный и нулевой входы которого являются шестым и седьмым управляющими входами блока, нулевой выход триггера управления подключен к первому входу первого элемента ИЛИ и являемся вторым выходом блока, второй прямой вход элемента И является управляющим входом блока, третий прямой выход элемента И является первым управляющим входом блока, инверсный вход элемента И является вторым управляющим входом блока, четвертый прямой вход элемента И является четвертым управляющим входом блока, выход элемента И соединен с первыми входами элементов И первой группы и через первый элемент задержки - с входом первого одновибратора, выход которого подключен через дифференцирующий элемент к входу второго одновибратора и к первым входам элементов И второй группы, вторые входы элементов И первой группы подключены к со- Ьтветствующим входам группы сигнальных входов блока, выход Р-го элемента И первой группы, где Р 1, 2,...,К-1, соединен с первьм входом Р-го элемента ИЛИ первой группы, выход которого подключен к единичному входу Р-го триггера первого регистра, выход К-го элемента И первой группы подключен к единичному входу триггера первого регистра, нулевой выход Р-го триггера первого регистра соединен с первым входом Р-го элемента И второй группы, третий вход которого соединен с единичным выходом (P-bl)-ro триггера первого регистра, выход j-ro элемента И первой группы соединен с вторым входом j-ro элемента ИЛИ первой группы и с нулевым входом (j+1)-ro триггера первого регистра, единичные выходы первого регистра подключены к первым группам входов схем сравнения группы, вторая группа входов i.-й схемы сравнения группы подключены к i-й группе информационных входов блока, выход Равно схемы сравнения соединен с прямым входом j-ro элемента запрета первой группы, 2-й инверсный вход j-ro элемента запрета первой группы, где 2 1,2,...,S-j, соединен с выходом Равно 2.-и схемы сравнения группы, выход схем сравнения группы подключены к входам элемента ИЛИ-НЕ, выход которого соединен с управляющими входами элементов запрета второй группы, выход Больше i-й схемы сравнения группы

соединен с прямым входом i--ro элемента запрета второй группы, т-й инверсный вход j-ro элемента запрета второй группы, где m 1,2

S-j, подключен к выходу Больше т-й схемы сравнения, выход Равно S-й схемы сравнения соединен с первым входом S-ro элемента ИЛИ второй группы, выход j-ro элемента запрета первой группы соединен с первым входом j-ro элемента ИЛИ второй группы, выход i-ro элемента запрета второй группы соединен с вторым входом i-ro элемента ИЛИ второй группы, выход которого подключен к первому входу i-ro элемента И третьей группы, вторые входы элементов И третьей группы Подключены к выходу второго

однрвибратора и через второй элемент задерлжи - к первому выходу блока, выход i-ro элемента И третьей группы соединен с единичным входом i-rp триггера второго регистра, нулевые

,входы триггеров второго регистра под- 1ключены к выходу второго элемента ИЛИ, |первьй вход которого соединен с третьим управлякицим входом блока, единичный выход j-ro триггера второго регистра подключен к j-му выходу группы выходов блока, единичный выход S-ro триггера второго регистра соединен с вторым входом первого элемента ИЛИ, выход которого подключен к S-му выходу группы выходов блока.

а &

13

7f

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для распределения заявок по процессорам | 1990 |

|

SU1798782A1 |

| Устройство для распределения групповых заявок по процессорам | 1985 |

|

SU1254485A1 |

| Устройство для моделирования систем массового обслуживания | 1986 |

|

SU1319043A1 |

| Устройство для организации доступа к ресурсам | 1988 |

|

SU1608663A1 |

| Устройство для моделирования систем массового обслуживания | 1988 |

|

SU1532943A1 |

| Устройство для распределения заданий процессорам | 1984 |

|

SU1246096A1 |

| Устройство для приоритетного обслуживания заявок | 1989 |

|

SU1709313A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для моделирования систем массового обслуживания | 1982 |

|

SU1067508A1 |

| Устройство для организации очереди | 1988 |

|

SU1575184A2 |

Изобретение относится к вычислительной технике и может быть использовано при обслуживании потока заявок в многопроцессорных вычислительных системах. Цель изобретения - повышение быстродействия устройства при обслуживании срочных заявок.Новым в устройстве является использование триггеров запуска и управления сдвигом, группы элементов ИЛИ-НЕ, элемента ИЛИ-НЕ, двух элементов И, (S-1) блоков элементов И первой и второй групп (S - число заяа,ок),блока элементов ИЛИ, генератора импуль- .сов, блока выбора заявок, содержащего три группы элементов И, две группы элементов ИЛИ, регистр состояния процессоров, две группы элементов запрета, группу схем сравнения, элемент ИЛИ-НЕ, два элемента задержки, два одновибратора, два элемента ИЛИ, регистр выбора заявки, дифференцирующий элемент, триггер управления,элемент И, и связей перечисленных элементов и узлов, что обеспечивает достижение цели изобретения. 2 ил. i (Л ю 4;аь 00 « 00

Редактор И, Сегляник

Составитель М. Кудряшев

Техред Э.Чкжмар Корректор М. Самборская

Заказ 4127/49Тираж 671Подписное

ВНИШШ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие г. Ужгород, ул. Проектная,4

| Устройство для распределения заявок по процессорам | 1979 |

|

SU866560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для распределения заданий процессорам | 1983 |

|

SU1095181A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-07-30—Публикация

1985-02-04—Подача