Изобретение относится к вычислительной технике.

Цель изобретения - повышение достоверности работы.

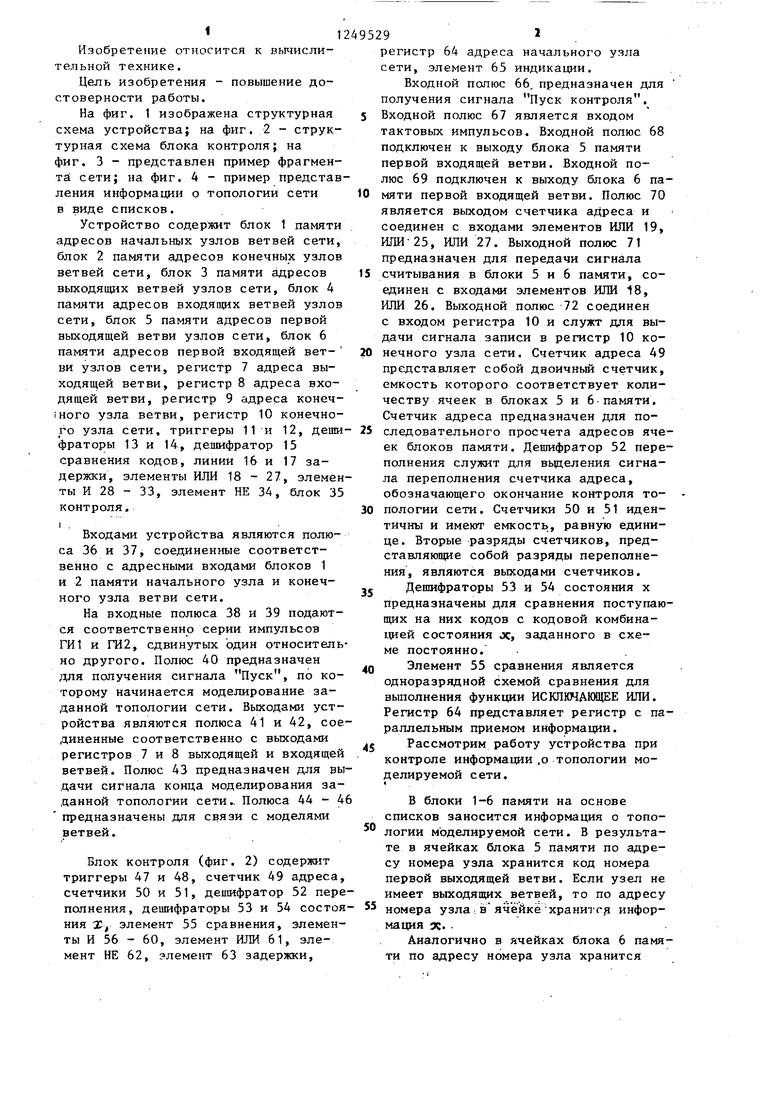

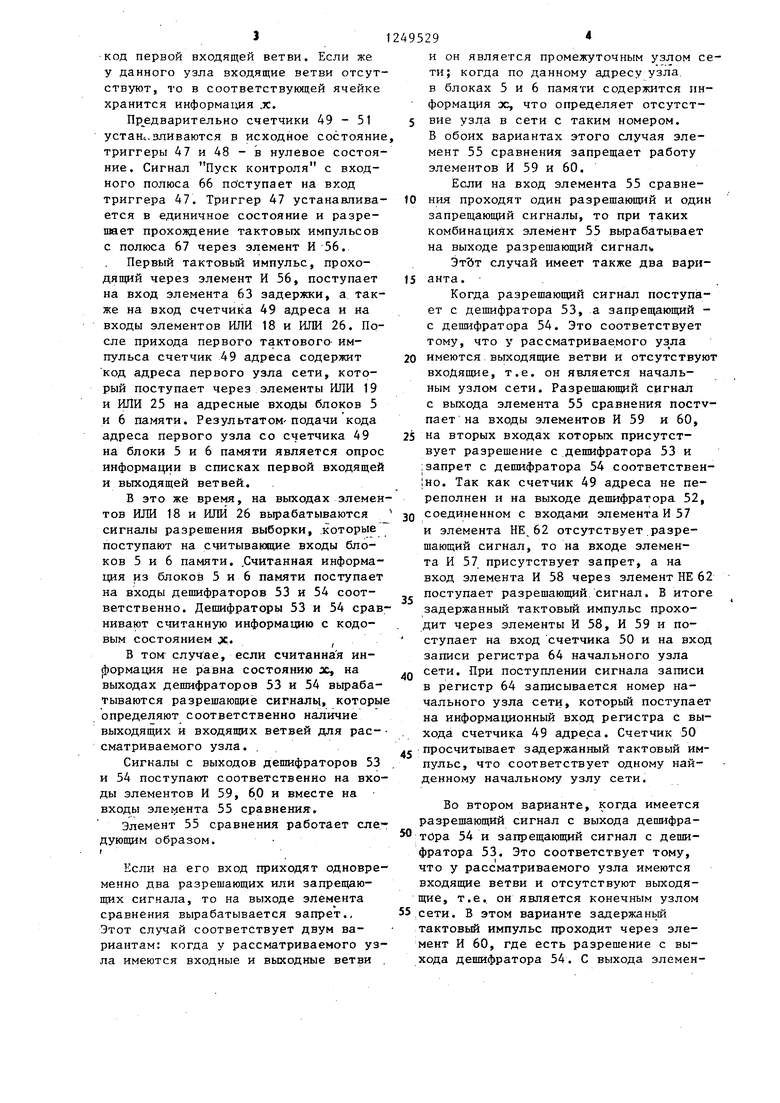

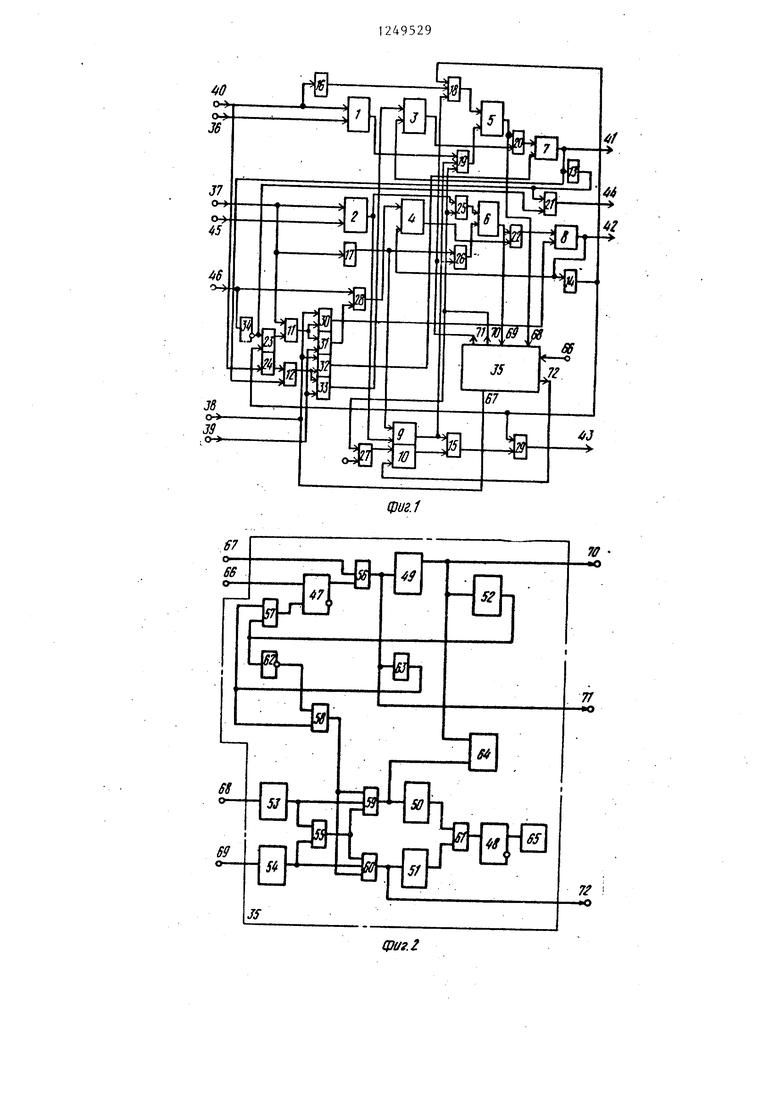

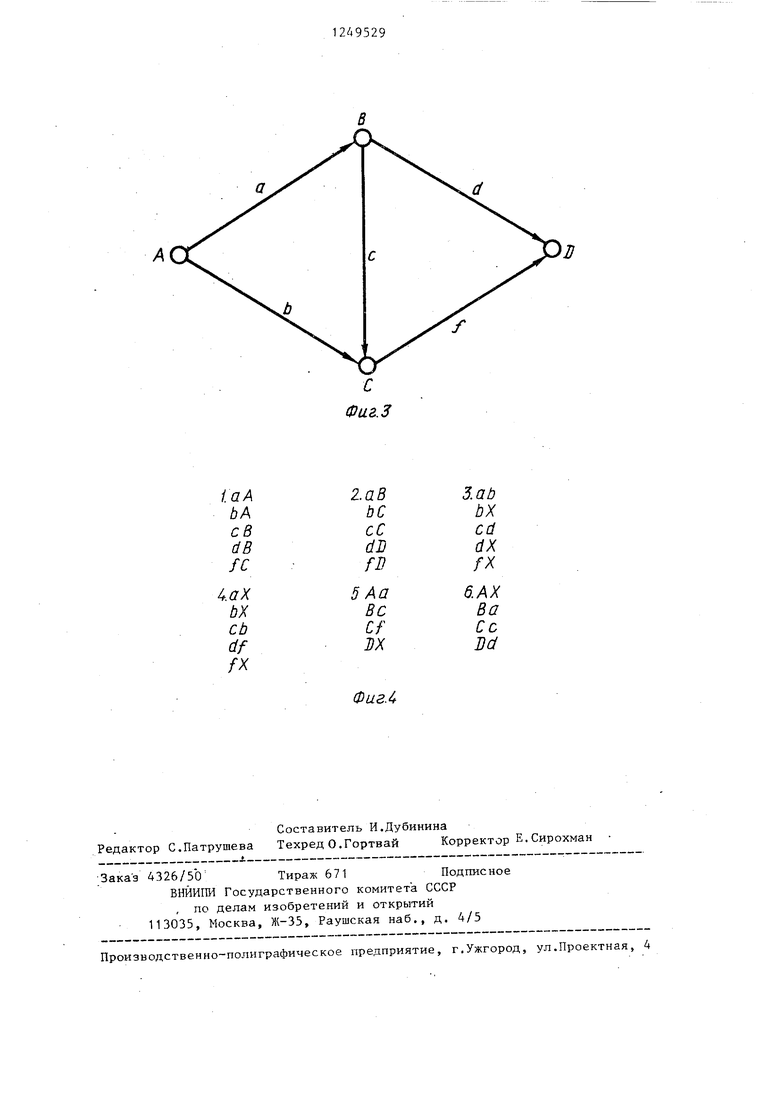

На фиг. 1 изображена структурная схема устройства; на фиг. 2 - структурная схема блока контроля; на фиг. 3 - представлен пример фрагмента; сети; на фиг. 4 - пример представления информации о топологии сети в виде списков.

Устройство содержит блок 1 памяти адресов начальных узлов ветвей сети, блок 2 памяти адресов конечных узлов ветвей сети, блок 3 памяти адресов выходящих ветвей узлов сети, блок 4 памяти адресов входящих ветвей узлов сети, блок 5 памяти адресов первой выходящей ветви узлов сети, блок 6 памяти адресов первой входящей вет- ни узлов сети, регистр 7 адреса выходящей ветви, регистр 8 адреса входящей ветви, регистр 9 адреса конеч- iHoro узла ветви, регистр 10 конечного узла сети, триггеры 11 и 12, дешифраторы 13 и 14, дешифратор 15 сравнения кодов, линии 16 и 17 задержки, элементы ИЛИ 18 - 27, элементы И 28 - 33, элемент НЕ 34, блок 35 контроля.

I .

Входами устройства являются полюса 36 и 37, соединенные соответственно с адресными входами блоков 1 и 2 памяти начального узла и конечного узла ветви сети.

На входные полюса 38 и 39 подаются соответственно серии импульсов ГИ1 и ГИ2, сдвинутых один относительно другого. Полюс 40 предназначен для получения сигнала Пуск, по которому начинается моделирование заданной топологии сети. Выходами устройства являются полюса 41 и 42, соединенные соответственно с выходами регистров 7 и 8 выходящей и входящей ветвей. Полюс 43 предназначен для выдачи сигнала конца моделирования заданной топологии сети.. Полюса 44 - 4 предназначены для связи с моделями ветвей.

В блоки 1-6 памяти на основе списков заносится информация о топологии моделируемой сети. В результате в ячейках блока 5 памяти по адресу номера узла хранится код номера первой выходящей ветви. Если узел не имеет выходящих ветвей, то по адресу

Блок контроля (фиг. 2) содержит триггеры 47 и 48, счетчик 49 адреса, счетчики 50 и 51, дешифратор 52 переполнения, дешифраторы 53 и 54 состоя- 55 номера узла. в яч ейкё хранитсэ инфор- ния jC, элемент 55 сравнения, элемен- мация эс.

ты И 56 - 60, элемент ИЛИ 61, эле- . Аналогично в ячейках блока 6 памя мент НЕ 62, элемент 63 задержки, ти по адресу номера узла хранится

5

0

5

0

5

0

5

50

регистр 64 адреса начального узла сети, элемент 65 индикации.

Входной полюс 66, предназначен для получения сигнала Пуск контроля. Входной полюс 67 является входом тактовых импульсов. Входной полюс 68 подключен к выходу блока 5 памяти первой входящей ветви. Входной полюс 69 подключен к выходу блока 6 памяти первой входящей ветви. Полюс 70 является выходом счетчика адреса и соединен с входами элементов ИЛИ 19, ИЛИ-25, ИЛИ 27. Выходной полюс 71 предназначен для передачи сигнала считывания в блоки 5 и 6 памяти, соединен с входами элементов ИЛИ 18, ИЛИ 26. Выходной полюс 72 соединен с входом регистра 10 и служт для выдачи сигнала записи в регистр 10 конечного узла сети. Счетчик адреса 49 представляет собой двоичньй счетчик, емкость которого соответствует количеству ячеек в блоках 5 и 6 памяти. Счетчик адреса предназначен для последовательного просчета адресов ячеек блоков памяти. Дешифратор 52 переполнения служит для вьделения сигнала переполнения счетчика адреса, обозначающего окончание контроля топологии сети. Счетчики 50 и 51 идентичны и имеют емкость, равную единице. Вторые разряды счетчиков, представляющие собой разряды переполнения, являются выходами счетчиков.

Дешифраторы 53 и 54 состояния х предназначены для сравнения поступающих на них кодов с кодовой комбинацией состояния ос, заданного в схеме постоянно.

Элемент 55 сравнения является одноразрядной схемой сравнения для выполнения функции ИСКЛКНАЩЕЕ ИЛИ. Регистр 64 представляет регистр с параллельным приемом информации.

Рассмотрим работу устройства при контроле информации .о топологии моделируемой сети.

В блоки 1-6 памяти на основе списков заносится информация о топологии моделируемой сети. В результате в ячейках блока 5 памяти по адресу номера узла хранится код номера первой выходящей ветви. Если узел не имеет выходящих ветвей, то по адресу

55 номера узла. в яч ейкё хранитсэ инфор- мация эс.

3

код первой входящей ветви. Если же

у данного узла входящие ветви отсутствуют, то в соответствующей ячейке хранится инфopмaIl я ж.

Пр едварительно счетчики 49-51 устанс.вливаются в исходное состояни триггеры 47 и 48 - в нулевое состояние. Сигнал Пуск контроля с входного полюса 66 поступает на вход триггера 47. Триггер 47 устанавливается в единичное состояние и разрешает прохождение тактовых импульсов с полюса 67 через элемент И 56.

Первый тактовьй импульс, проходящий через элемент И 56, поступает на вход элемента 63 задержки, а также на вход счетчика 49 адреса и на входы элементов ИЛИ 18 и ИЛИ 26. После прихода первого тактового- импульса счетчик 49 адреса содержит код адреса первого узла сети, который поступает через элементы ИЛИ 19 и ИЛИ 25 на адресные входы блоков 5 и 6 памяти. Результатом-подачи кода адреса первого узла со счетчика 49 на блоки 5 и 6 памяти является опро информации в списках первой входяще и вьпсодящей ветвей.

В это же время, на выходах элеметов ИЛИ 18 и ИЖ 26 вьфабатываются сигналы разрешения выборки, которые поступают на считывающие входы блоков 5 и 6 памяти. .Считанная информация из блоков 5 и 6 памяти поступает на входы дешифраторов 53 и 54 соответственно. Депзифраторы 53 и 54 сравнивают считанную информацию с кодовым состоянием х.

В том , если считанна я информация не равна состоянию зс, на выходах дешифраторов 53 и 54 вырабатываются разрешающие сигналы, которы определяют соответственно наличие выходящих и входящих ветвей для рассматриваемого узла. .

Сигналы с выходов дешифраторов 53 и 54 поступают соответственно на входы элементов И 59, 60 и вместе на входы элемента 55 сравнения.

Элемент 55 сравнения работает еле дующим образом.

Если на его вход приходят одновременно два разрешающих или запрещаю- щк к. сигнала, то на выходе элемента сравнения вырабатывается запрет., Этот случай соответствует двум вариантам: когда у рассматриваемого узла имеются входные и выходные ветви ,

0

5

0

и он

5

0

5

0

5

является промежуточным узлом сети; когда по данному адресу узла, в блоках 5 и 6 памяти содержится информация зс, что определяет отсутствие узда в сети с таким номером. В обоих вариантах этого случая элемент 55 сравнения запрещает работу элементов И 59 и 60.

Если на вход элемента 55 сравнения проходят один разрешающий и один запрещающий сигналы, то при таких комбинациях элемент 55 вьфабатывает на выходе разрешающий сигналу

Этйт случай имеет также два варианта.

Когда разрешающий сигнал поступает с дешифратора 53, а запрещающий - с дешифратора 54. Это соответствует тому, что у рассматриваемого узла имеются выходящие ветви и отсутствуют входящие, т.е. он является начальным узлом сети. Разрешающий сигнал с выхода элемента 55 сравнения поступает на входы элементов И 59 и 60, на вторых входах которых присутствует разрешение с дешифратора 53 и ;запрет с дешифратора 54 соответствен- ;но. Так как счетчик 49 адреса не переполнен и на выходе дешифратора 52, соединенном с входами элемента И 57 и элемента НЕ,62 отсутствует.разрешающий сигнал, то на входе элемента И 57 присутствует запрет, а на вход элемента И 58 через элемент НЕ 62 поступает разрешающий сигнал. В итоге задержанный тактовый импульс проходит через элементы И 58, И 59 и поступает на вход счетчика 50 и на вход записи регистра 64 начального узла сети. При поступлении сигнала записи в регистр 64 записывается номер начального узла сети, который поступает на информационный вход регистра с выхода счетчика 49 адреса. Счетчик 50 просчитывает задержанный тактовый импульс, что соответствует одному найденному начальному узлу сети.

Во втором варианте, когда имеется разрешающий сигнал с выхода дешифра50 тора 54 и запрещающий сигнал с дешифратора 53. Это соответствует тому, что у рассматриваемого узла имеются входяш ие ветви и отсутствуют выходящие, т.е. он является конечным узлом

55 сети. В этом варианте задержаньй тактовьй импульс проходит через элемент И 60, где есть разрешение с выхода дешифратора 54. С выхода элемента И 60 импульс поступает на вход счетчика 51 и через полюс 72 на вход записи регистра 10 конечного узла сети. При поступлении сигнала записи в регистр 10 записывается номер конечного узла сети, которьм через элемент ИЛИ 27 поступает на информационный вход регистра с выхода счетчика 49 адреса. Соответственно счетчик 31 просчитывает задержаный тактовьй импульс, что определяет один найденный конечный узел сети.

На следующем такте проходит следующий (второй) тактовьй импульс на полюс 67, который поступа ет на счетный вход счетчика 49 адреса. Счетчик адреса увеличивает свое содержимое на единицу. Это соответст- вуе.т формированию адреса следующего узла, для которого просматривается наличие входящих и выходящих ветвей. В случае определения второго начального или второго конечного узла сети на выходе счетчиков 50 или 51 соответственно вьфабатывается сигнал переполнения. Сигнал переполнения проходит через элемент ИЛИ 61 и устанавливает триггер 48 в единичное состояние, -что соответствует некоррект- ности сети. Элемент 65 индикации, соединенный с выходом триггера 48, отображает в данном случае информацию о некорректности сети. Так опрос адресов номеров узлов сети осуществляет- , ся до тех пор, пока не будут просмотрены все ячейки блоков 5 и 6 памяти. Это соответствует тому, что счетчик 49 адреса будет содержат.ь код переполнения..-

Дешифратор 52 дещифрирует состояние переполнения счетчика адреса и вырабатывает сигнал разрешения, который поступает на вход элемента И 57. Сигнал с выхода дешифратора 52 также по- ступает через элемент НЕ 62 на элемент И 58 и запрещает прохояздение задержаного тактового импульса с выхода элемента 63 задержки. В этом случае задержаный тактовый импульс прохо ходит через элемент И 58 и устанавливает триггер 47 в нулевое состояние. В итоге нулевое состояние триггера 47 запрещает прохождение тактовых им- Лульсов через элемент И 56 и работа устройства контроля на этом заканчивается. Если сеть корректна, то в регистрах 64 и 10 хранятся соответственно коды номеров начального и конечного узлов сети. В случае некорректности сети триггер 48 находится в единичном состоянии и элемент индикации- отображает аварийной состояние устройства. /

В устройстве обеспечивается поступление необходимых сигналов предварительного установа, которые на фиг. 1, 2 не показаны.

Решение задачи контроля заключается в проверке корректности заданной топологии сети, которая хранится в шести блоках памяти устройства. При этом опшбки в топологии могут допускаться как при записи информации в блоки памяти, так и при неправильном задании топологии сети оператором.

Контроль информации о топологии позволяет исключить неправильную коммутацию решающих элементов в процессе моделирования исследуемой сети.

Формула изобретения

Устройство для моделирования топологии сетей,- содержащее блок памяти адресов первой выходящей ветви узлов сети, блок памяти адресов первой входящей ветви узлов сети, ,регистр адреса выходящей ветви, регистр адреса входящей ветви, выходы регистров адреса выходящей и входящей ветвей соединены, с адресными входами соответственно блока памяти адресов выходящих ветвей узлов сети и блока памяти адресов входящих ветвей узлов сети, блоки памяти адресов начальных и конечных узлов ветвей сети, регистры адреса конечного узла ветви и конечного узла сети, первый и второй триггеры, первый и второй дешифраторы, дешифратор сравнения кодов, первую и вторую линии задержки, семь элементов ИЛИ, шесть элементов И и элемент НЕ, причем адресный вход блока памяти адресов начальных узлов ветвей сети является входом задания адреса начальной ветви устройства, вход считывания блока памяти адресов начальных узлов ветвей сети является пусковы входом устройства и соедине с входом первой линии задержки и первым входом первого элемента ИЛИ, адресный вход блока памяти адресов конечных узлов ветвей сети является входом задания адреса конечного узла

ветви устройства, вход прерывания блока памяти адресов конечных узлов ветвей сети является входом прерывания работы устройства и соединен с входом второй линии задержки и единичным входом первого триггера, первый вход первого элемента И соединен с входом элемента. НЕ и является входом приема сигналов окончания работы моделей ветвей устройства, ннформа-. Щ1ОННЫЙ вход регистра адреса конечного узла ветви соединен с выходом блока памяти адресов конечных узлов ветвей сети, вход разрешения записи ре- гистра адреса конечного узла ветви соединен с выходом второй лийии задержки, выход регистра адреса конеч- .ного узла сети соединен с первым входом дешифратора сравне ния -кодов, вто рой вход которого соединен с выходом регистра адреса конечного ветви и первым входом второго элемента ШШ второй вход второго элемента ИЛИ соединен с выходом блока памяти адре сов начальных узлог ветвей сети, а выход - с адресным входом блока памяти адресов первой выходящей ветви узлов сети, вход считывания которого соединен с выходом третьего элемен- та ИЛИ, первый вход которого соединен с выходом первой линии задержки, выходы блоков памяти адресов выходящих ветвей и первой выходящей ветви узлов сети соединены с входами четвертого элемента ИЛИ, выход которого соединен с информационным входом регистра адреса выходящей ветви, выход которого является выходом адреса входящей ветви устройства и соедииен с входом первого дешифратора, выход которого подключен к нулевому , входу второго триггера и первому входу пятого элемента ИЛИ, -второй вход которого соединен с выходом элемента НЕ и первым входом шестого элемента ИЛИ, выход пятого элемента ИЛИ является выходом сигналов включения моделей ветвей устройства выход регистра адреса входящей вет- ви является выходом адреса входящей ветви устройства и соединен с входом второго дешифратора,.выхоп которого соединен с вторым входом третьего элемента ИЛИ, вторыми входами первого и шестого элементов ШШ и первым входом второго элемента И, второй которого подключен к выходу дешифратора сравнения кодов, выход первого элемента И является выходом сигнала окончания работы устройства, выход первого элемента ИЛИ соединен с единичным входом второго триппера, выхо которого соединен с первыми входами третьего и четвертого элементов И, выход первого триггера соединен с первыми входами пятого и шестого элементов И, вторые входы третьего и пятого элементов И соединены с первым . входом тактовых импульсов устройства вторые- входы четвертого и шестого элементов И соединены с вторым входом тактовых импульсов устройства, рыходы третьего и четвертого элементов И соединены соответственно с входом считывания блока, памяти адресов выходящих ветвей узлов сети и входом ;разрешения записи регистра адреса выходящей ветви, выход шестого элемента И соединен с вторым входом первого элемента И, выход которого соединен с входом считывания блока памяти адресов входящих ветвей узлов сети, выход которого подключен к первому входу седьмого элемента ИЛИ, второй вход которого соединен с выходом блока памяти адресов первой входящей ветви узлов сети, выход седьмого элемента ИЛИ подключен к информационному входу регистра адреса входящей ветви, вход.разрешения записи которого соединен с выходом пятого элемента И, выход шестого элемента ИЛИ подключен к нулевому входу первого триггера, отличающееся тем, что, G цегхью повышения достоверности, в него введены восьмой, девятый, десятый элементы ИЛИ и блок контроляi содержащий счетчик адреса, первый и второй счетчики, дешифратор переполнения,, первый и второй дешифраторы, зле- мент сравнения, регистр адреса начального узла сети, первый и второй триггеры, с первого по пятый элементы И, элемент ИЛИ, элемент НЕ, элемент задержки и элемент индикации, единичый вход первого триггера блока контроля является входом пуска контроля устройства, единичный выход первого триггера блока контроля соединен с первым входом первого элемента И блока контроля, второй вход которого соединен с вторым входом тактовых импульсов устройства, выход первого

элемента И блока контроля соединен с входами счетчика адреса и элемента задержки блока контроля с третьим рходом третьего элемента ИЛИ и первым входом восьм ого элемента ИЛИ, выход которого соединен с входом считывания блока памяти адресов входящих ветвей узлов сети,.выход счетчика адреса блока контроля соединен с ин- формационным входом регистра адреса начального узла сети блока контроля, с входом дешифратора переполнения блока контроля, с третьим входом второго элемента ИЛИ, с первым входом девятого элемента ИЛИ, с первым вхо- дом десятого элемента ИЖ, выход которого соединен с информационным входом регистра адреса конечного узла сети, выход дешифратора переполнения блока контроля подключен к первому входу второго элемента И и через элемент НЕ .соединен с первым входом третьего элемента И блока контроле, выход элемента задержки подключен к вторым входам второго и третьего эле1 1ентов И блока контроля, выход второго элемента И блока контроля соединен с нулевым входом первого триггера блока контроля, выход третьего элемента И блока контроля соединен с первыми входами четвертого и пятого элементов И блока контроля, вторые входы которых объединены и соединены с рыходом элементов сравнения, выходы первого и второго депп€фраторов блока контроля подключены к соответствующим входам -эле- ; мента сравнения и соединены с третьими входами четвертого и пятого элементов И блока контроля соответственно, выход блока памяти адресов первой выходящей ветви узлов сети подключен к входу первого дешифратора блока контроля, выход блока памяти адресов первой входящей ветви узлов сети соединен с входом второго дешифратора блока контроля, выход пятого элемента И блока контроля соединен с входом первого счетчика блока контроля и входом разрешения записи регистра адреса конечного узла сети, а выход четвертого элемента И блока контроля соединен с вхо- ,.дом разрешения записи регистра адреса начального узла сети и входом второго счетчика блока контррля, выход которого соединен с первым входом элемента ИЛИ блока контроля, второй вход которого соединен с выходом первого счетчика блока контроля, выход элемента ИЛИ блока контроля соединен с единичным входом второго триггера этого блока, единичный выход которого соединен с входом элемента индикации, выход девятого элемента ИЛИ подключен к адресному входу блока памяти адресов входяшдх ветвей узлов сети, выход второй линии задержки соединен с вторым входом восьмого элемента ИЛИ, выход блока памяти адресов конечных узлов ветвей сети подключен к второму входу девятого элемента ИЛИ, второй- - вход десятого | эле7мента ИЛИ является входом задания адреса конечного узла сети устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для моделирования задач о длиннейшем пути в сетях | 1983 |

|

SU1161951A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1986 |

|

SU1374239A2 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Устройство для анализа параметров сети | 1986 |

|

SU1548793A1 |

| Устройство для решения сетевых задач | 1988 |

|

SU1564643A1 |

| Устройство для моделирования направленных графов | 1986 |

|

SU1322304A1 |

| Устройство для моделирования сетей в реальном времени | 1987 |

|

SU1509926A1 |

| Устройство для определения длиннейшего пути в сетях | 1986 |

|

SU1339581A1 |

| Устройство для моделирования задач о длиннейшем пути в сетях | 1987 |

|

SU1509925A2 |

| Устройство для определения характеристик сетей | 1984 |

|

SU1282151A1 |

Изобретение относится к вычислительной технике и может быть использовано при построении, специализированных вычислительных устройств для параллельного моделирования различных систем, имеющих сетевую структуру с учетом контроля Корректности топологии исследуемой сети. Цель изобретения - повышение достоверности работы. Для этого в устройство для моделирования топологии сетей дополнительно введены восьмой, девятый, десятый элементы ИЛИ и блок контроля, причем последний содержит счетчик адреса, первый и второй счетчики-, дешифратор переполнения, первый и второй дешифраторы, элемент сравнения, регистр адреса начального узла сети, первый и второй триггеры, с первого по пятый.элементы И, элемент ИЛИ. элемент НЕ, элемент задержки и элемент индикации. i СЛ С сд hO

67

iaA ЬА сВ dB fC

Фиг4

| Устройство для моделирования сетевого графика | 1977 |

|

SU686033A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для моделирования топологии сетей | 1982 |

|

SU1024930A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1984-12-26—Подача