i

Иаобретение относится к аналоговой и контрольно-измерительной технике, в частности к области аналогового пре образования временных параметров одиночных или периодических импульсов напряжения, и может быть использовано в качестве времязадающего элемента, имеющего большую постоянную времени.

Цель изобретения - повышение точности интегрирования.

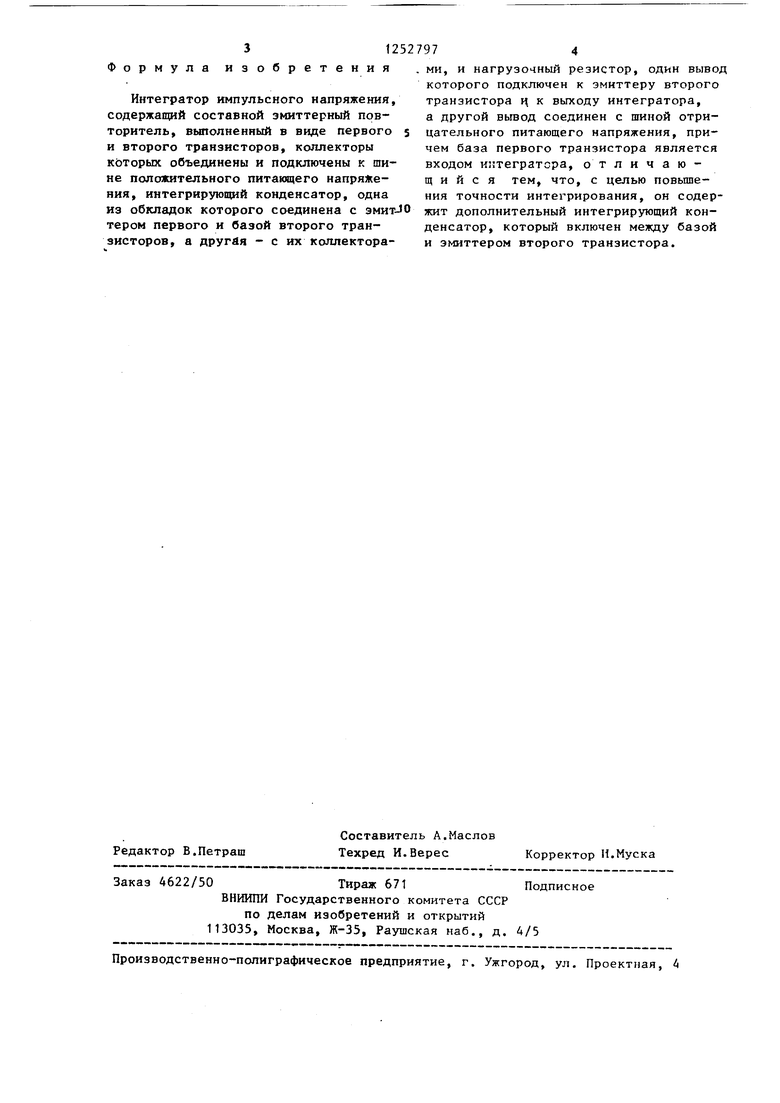

На чертеже приведена схема интегратора.

Интегратор содержит составной эмит-20

своего прежнего напряжения заряда, окажется зашуптированной значитель возросшим сопротивлением перехода, что увеличит постоянную времени эт звена.

30

терный повторитель, выполненный в ви- 5 эмиттер транзистора 1, не изменяя де двух транзисторов 1 и 2, основной

и дополнительный интегрирующие конденсаторы 3 и 4, один из которых 3 }зкл1очен параллельно коллекторно-базо- вому переходу транзистора 2, а другой - параллельно его базо-эмиттерно- му переходу, с Э№1ттером которого соединен )1агрузочный резистор 5,

Интегратор работает следующим образом.

В исходном состоянии транзисторы 1 и 2 находятся в активном режиме, . интегрируюпц1й конденсатор 3 заряжен до напряжения (, s-s интег- рируощий конденсатор 4 - до напряжеНИН Ujfg ,

С приходом положительного входного импульса транзистор 1 переходит в режим насыщения, при котором увеличивается его коллекторныГ: ток, сильно нас1.1цаю11Ц1й транзистор 2. Этому состоянию транзисторов 1 и 2 соответствует уменьшение падения напряжения на переходе коллектор - эмиттер транзистора и уБелмче П 1е на переходе база - эмиттер транзистора 2, а также накопление Избыточного заряда неосновных носителей п базе транзистора 2, Поскольку переход н это состояние происходит под воздействием увеличенных токов, изменение напряжения на конденсаторах 3 и А происходит сравнительно быстро и положительный форонт выходного импульса формируется на на- 1 рузочном резисторе 5 практически без задержки.

35

Но уменьшение коллекторного ток транзистора 1 означает и уменьшени базового тока транзистора 2, вслед 25 ствие чего емкость конденсатора А, фиксирующая падение, напряжения на реходе баз а - эмиттер .транзистора не изменяя своего прежнего напряже ния, окажется зашуптированной все лее возрастающим сопротивлением пе хода, что увеличит постоянную врем ни этого звена.

Таким образом, по мере рассасыв ния избыточного заряда потенциалы эмиттеров транзисторов 1 и 2 будут изменяться в сторону уменьшения со скоростью, задаваемой постоянными мени указанных звеньев и практичес без влияния нижнего звена, которым является нагрузочный резистор 5, д тех пор, пока не закончится перехо ный процесс, обеспечивая тем самым зависимость постоянной времени инт рирования от величины поминала это резистора, В этом состоит суть фун онирования схемы. Следует отметить что работа схемы будет происходить соответствии с описанием при услов что постоянная времени ценя нагруз будет оставаться достаточно малой сравнению с постоянными времени зв ньев: коллектор - эмиттер транзист 1 и база - эмиттер транзистора 2,

40

45

50

Фиксация положения рабочих точек транзисторов 1 и 2, соответствующих болыпим токаи коллекторов и меньшим сопротиБленипм переходов коллектор - эмиттер и база - эмиттер, продолжается в течение действия входного импульса. После его окончания база

972

транзистора 1 мгновенно приобретает нулевой потенциал, однако-его эмиттер не сможет также быстро отследить это изменение, ибо накопленный в базе вы- ходного транзистора 2 избыточный заряд окажет на переход база - эмиттер транзистора 1 запирающее действие, в результате чего его рабочая точка окажется в области отсечки и одновре- 1менно с уменьшением коллекторного тока увеличится сопротивление перехо- |да коллектор - эмиттер. Емкость кон- |денсатора 3, фиксирующая падение напряжения на переходе коллектор -

своего прежнего напряжения заряда, окажется зашуптированной значительно возросшим сопротивлением перехода, что увеличит постоянную времени этого звена.

эмиттер транзистора 1, не изменяя

Но уменьшение коллекторного тока транзистора 1 означает и уменьшение базового тока транзистора 2, вслед- ствие чего емкость конденсатора А, фиксирующая падение, напряжения на переходе баз а - эмиттер .транзистора 2, не изменяя своего прежнего напряжения, окажется зашуптированной все более возрастающим сопротивлением перехода, что увеличит постоянную времени этого звена.

Таким образом, по мере рассасывания избыточного заряда потенциалы эмиттеров транзисторов 1 и 2 будут изменяться в сторону уменьшения со , скоростью, задаваемой постоянными вре - мени указанных звеньев и практически без влияния нижнего звена, которым является нагрузочный резистор 5, до тех пор, пока не закончится переходный процесс, обеспечивая тем самым независимость постоянной времени интегрирования от величины поминала этого резистора, В этом состоит суть функционирования схемы. Следует отметить, что работа схемы будет происходить в соответствии с описанием при условии, что постоянная времени ценя нагрузки будет оставаться достаточно малой по сравнению с постоянными времени звеньев: коллектор - эмиттер транзистора 1 и база - эмиттер транзистора 2,

Таким образом, в предлагаемом ин- теграторе обеспечивается ппг.тоянство постоянной интегрирования лри изменении величины нагрузки в широких пределах.

31252

Формула изобретения

Интегратор импульсного напряжения, содержащий составной эмиттерный повторитель, выполненный в виде первого s и второго транзисторов, коллекторы которых объединены и подключены к шине положительного питающего напряжения, интегрирующий конденсатор, одна из обкладок которого соединена с эмит-JO тером первого и базой второго транзисторов, а другая - с их коллектораор В.Петраш 4622/50

Составитель А.Маслов Техред И.Верес

Ко По

Тираж 671 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

7974

. ми, и нагрузочный резистор, один вывод которого подключен к эмиттеру второго транзистора ц к выходу интегратора, а другой вьгоод соединен с шиной отрицательного питающего напряжения, причем база первого транзистора является входом интегратора, отличающийся тем, что, с целью повышения точности интегрирования, он содержит дополнительный интегрирующий конденсатор, который включен между базой и змиттером второго транзистора.

Корректор И.Муска Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| НТЙО- .^Т"^^КИЧЕС1:АЯ ^ | 1969 |

|

SU250989A1 |

| Устройство автоматической подстройки частоты | 1974 |

|

SU640415A1 |

| Устройство для защиты электроустановки от аварийных режимов | 1988 |

|

SU1582252A1 |

| Формирователь импульсов | 1982 |

|

SU1246349A1 |

| Интегратор | 1985 |

|

SU1287195A1 |

| Осветительное устройство | 1991 |

|

SU1826146A1 |

| Интегратор | 1979 |

|

SU824226A1 |

| ФОРМИРОВАТЕЛЬ ПИЛООБРАЗНЫХ ИМПУЛЬСОВ УДВОЕННОЙ ЧАСТОТЫ | 1991 |

|

RU2028724C1 |

| Частотно-импульсный модулятор | 1989 |

|

SU1725377A1 |

| Однотактный преобразователь напряжения постоянного тока | 1985 |

|

SU1274088A1 |

Изобретение относится к контрольно-измерительной технике, в частности, к области аналогового преобразования временных параметров одиночных или периодических импульсов напряжения, а также может быть использовано в качестве времязадайщего элемента, имеющего большую постояннук) вpe(eнп. Целью изобретег ия япляетсл попышеиие точности интегрирования. Интегратор содержит составной эш1ттериы 1 повторитель на двух транзисторах 1, 2, основной и дополнительный интегрируюп;ие конденсаторы 3 и А, один из которьк

| Шило В.Л | |||

| Функциональные аналоговые интегральные микросхемы.- М.: Советское радио, 1982, с | |||

| Способ подготовки рафинадного сахара к высушиванию | 0 |

|

SU73A1 |

| Устройство для устранения мешающего действия зажигательной электрической системы двигателей внутреннего сгорания на радиоприем | 1922 |

|

SU52A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Способ получения фтористых солей | 1914 |

|

SU1980A1 |

Авторы

Даты

1986-08-23—Публикация

1985-01-07—Подача