1

Изобретение относится к аналоговой вычислительной технике и втома- тике.

Uej:b изобретения - повышение быстродействия усилителя-ограничителя.

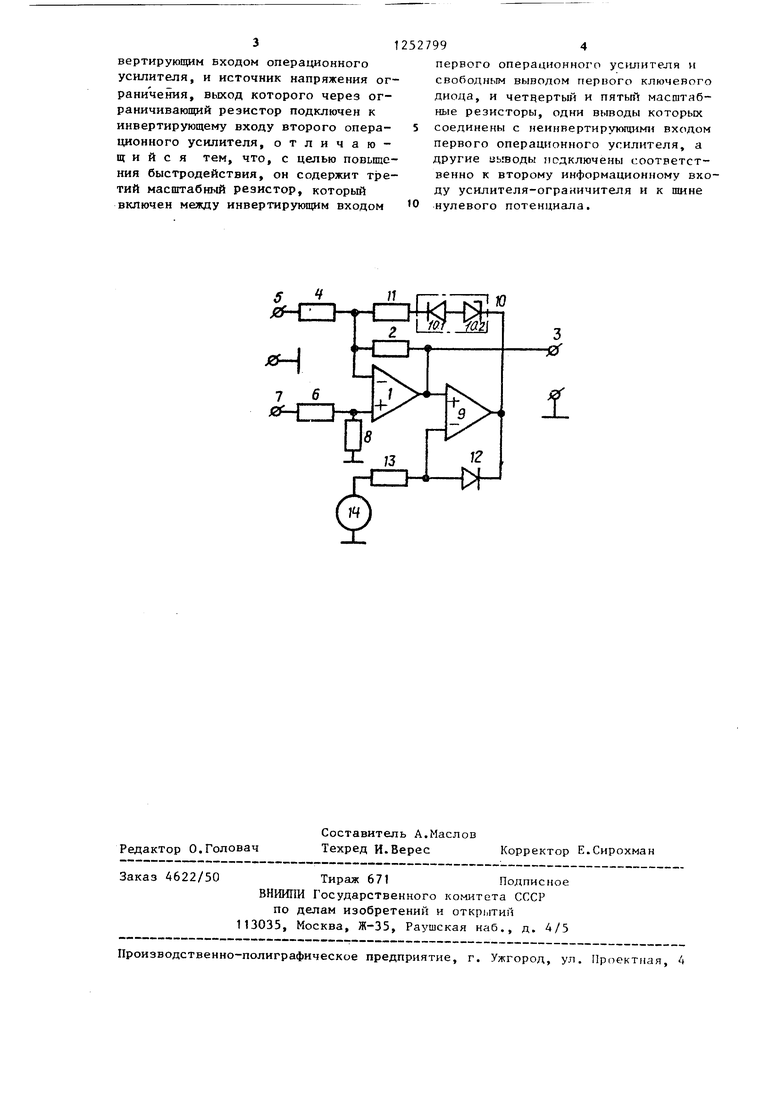

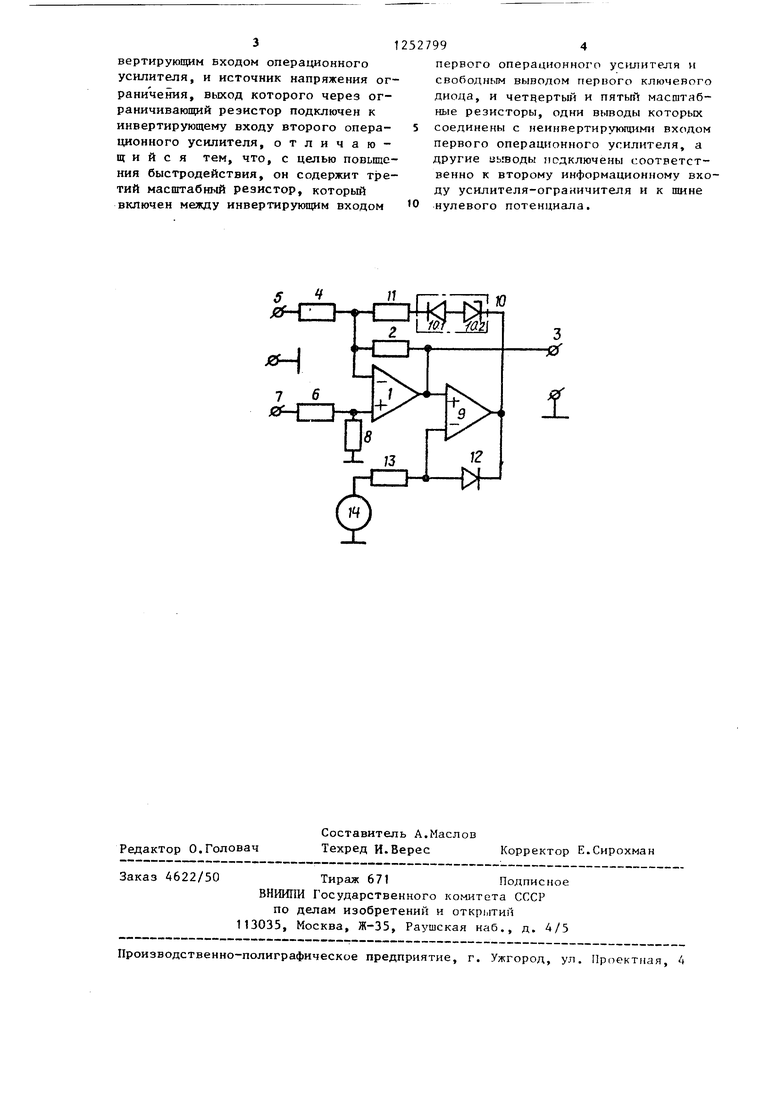

На чертеже показана электрическая схема усилителя-ограничителя.

Усилитель-ограничитель содержит первьй операционный усилитель 1, инвертирующий вход которого через первый масштабный резистор 2 соединен с его выходом, являющимся выходом 3 усилителя-ограничителя, и через второй масштабный резистор 4 - с его информационным входом 5, неинвертирующий вход операционного усилителя 1 через третий масштабный резистор

6связан с вторым информащюнным входом 7 усилителя-огранищггеля и через четвертый масштабный резистор 8 с шиной нулевого потенщ{апа, второй операционный усилитель 9, выход которого через ключ 10, выполненный в виде последовательно и встречно вклюг1ениьк первого ключевого диода 10.1 и стабилитрона 10.2 и пятый масштабный резистор 11 подключен к инвертирующему входу операционного усшпп вля 1 и через второй ключевой Л.иод 12 - к его инвертирующему входу, между которым и Ш1пюй нулевого потенциала включены последовательно ограничивающий резистор 13 и источник 14 напряжения отграничения, а не- иивертирующий вход подключен к выходу операционного усилителя 1 и выходу 3 усилителя-ограничителя.

Полярность включения полупроводниковых элементов соответствует ограничению положительного выходного напряжения сверху. При ограничении отрицатель 1ого напряжения снизу по- Ьярность включения всех элементов изменяется на протчвоположную.

В случае отрицательного напряжения сверху стаби.11итрон исключается из схемы, а при ограничении положительного напряжения снизу полярность включения диодов изменяется.

Усилитель-ограничитель работает следующим образом.

При выполнении условия (U, - Uy) и R,/R-7 на выходе операционного

У Л L

усилителя 1 поягзляется напряжение, меньшее относительного опорного (U(/U,, и, - напряжения на входах

7и 5; R, сопротивление масштабных резисторов 4 и 6; Rj - сопротивление

527992

масштабных резисторов 2 и 8).- Это приводит к появлению на вьтх одр операционного усилителя 9 отрицательного напряжения. Ключ 10 закрывается

5 и опера1Ц1онный усилитель 9 не влияет на работу дисЗ)ференциального усилителя на операционном усилителе 1.

Ключевой диод 12 открывается замыкая петлю отрицательной обратной

10 связи операционного усилителя 9 и предотвращая его насыщение.

Усилитель-ограничитель работает при этом в режиме усиления входного дифференциального сигнала U, U. с

15 коэффициентом, определяемым масштабными резисторами 2, 4, 6 и 8.

При возрастании входного дифференциального сигнала, как только будет выполняться (и, - 11,) , вы20 ходное напряжение усилителя-ограничителя, большее относительно опорного напряжения U. приводит к появлению на выходе усилителя 9 положительного напряжения, пробою стабилитрона

25 10.2 ключа 10 и замыканию петли

100%-ной отрицательной обратной связи, включающей усилители 1 и 9, тшюч 10 и резистор 11.

Напряжение пробоя стабилитрона

30 10.2 выбирается несколько большим максимально возможного напряжения ограничения, что необходимо для надежного запирания ключевого диода 12.

На выходе усилителя-ограничителя в режиме ограничения поддерживается папряжеиие источника 14.

Формула изобретения

Усилитель-огранигщтель, содержа- Г1,ий первьй операционный усилитель, между вых(здом и инвертирующим входом которого включен первьш масштабный резистор, второй машстабный резистор,

Бключепный между инвертирующим входом первого oriepaipioHHoro усилителя и первым информационным входом усилителя-ограничителя, второй опера- усилитель, подсоединенный неинвертирующим входом к выходу первого операционного усилителя, который является вьпсодом усилителя-ограничителя, последовательно и встречно включенные первый ключевой диод и

стабилитрон, подсоединенный свободным выводом к выходу второго операционного усилителя, второй ключевой диод, который включен между выходом и инвертирующим входом операционного усилителя, и источник напряжения ог раничения, выход которого через ограничивающий резистор подключен к инвертирующему входу второго операционного усилителя, отличающийся тем, что, с целью повыщс- НИН быстродействия, он содержит третий масштабный резистор, который включен между инвертирующим входом

2527994

первого операционного усилителя и свободным выводом первого ключевого диода, и четвертый и пятьй масштяб- ные резисторы, одни выводы которьк 5 соединены с неинвертирукйцим входом первого операционного усилителя, а другие выводы подключены соответственно к второму информационному входу усилителя-ограничителя и к шине О нулевого потенциала.

| название | год | авторы | номер документа |

|---|---|---|---|

| Усилитель-ограничитель | 1983 |

|

SU1124334A1 |

| Трехканальный мажоритарный элемент | 1987 |

|

SU1584101A1 |

| Дифференциальный усилитель-ограничитель | 1984 |

|

SU1179385A1 |

| Устройство для решения дифференциальных уравнений | 1980 |

|

SU1339594A1 |

| Устройство для выделения модуля | 1981 |

|

SU980102A1 |

| Устройство для определения абсолютного значения разности двух напряжений | 1989 |

|

SU1619319A1 |

| Перемножающее устройство | 1983 |

|

SU1168971A1 |

| Устройство для перемножения сигналов переменного тока | 1982 |

|

SU1037277A1 |

| Устройство для гальваническогоРАздЕлЕНия цЕпЕй пОСТОяННОгО TOKA | 1979 |

|

SU840939A1 |

| Устройство для извлечения квадратного корня | 1981 |

|

SU1005082A1 |

Изобретение относится к аналоговой вычислительной технике и автоматике. Целью изобретения является повышение быстродействия усилителя-ограничителя. Усилитель-ограничитель содержит первый операционный усилитель, инвертирующий вход которого через первьй масштабньй резистор соединен с его выходом, являющимся выходом усилителя-ограничителя, и через второй масштабный резистор - с его информационным входом, неинвертирую ции ВХОД первого операционного усилителя через третий масштабный I e- зистор связан с вторым ннформацгюпным входом усилителя-ограничителя л через четвертый масштабный резистор - с шиной нулевого потенциала, второй операционный усилитель, выход которого через ключ, выполненный в виде последовательно и встречно включенных первого ключевого диода и стабнлит- рога, и пятый маси табный резистор подключен к инвертирую цему входу первого операционного усилителя ti через второй ключевой диод - к его инвертирующему входу, между которым и ти- Г10Й нулевого пoтeнuИ(лa включены последовательно ограш чпванмций резистор и ncTO4jniK напряжения ограничения. Введение в усилитель-ограничитель третьего, четвертого и пятого масштабных резисторов и Hoot,rx связей -Между элементами позволяет умены;п ть постоянную времени усилителя ограничителя при работе- в режиме ограничения и тем самым достичь поставленной цели. 1 ил. Q , kf. v,fo i

б 1

Редактор О.Головач

Составитель А.Маслов Техред И.Верес

А622/50

Тираж 671Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и откр|,1тии 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор Е.Сирохман

| Ограничитель | 1979 |

|

SU826365A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 913405, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-23—Публикация

1985-02-11—Подача